##

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VDFN Exposed Pad                                                       |

| Supplier Device Package    | 8-DFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f609-e-md |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Addr   | Name                     | Bit 7              | Bit 6                                                | Bit 5            | Bit 4          | Bit 3                  | Bit 2           | Bit 1         | Bit 0               | Value on<br>POR, BOR | Page    |

|--------|--------------------------|--------------------|------------------------------------------------------|------------------|----------------|------------------------|-----------------|---------------|---------------------|----------------------|---------|

| Bank 1 |                          |                    |                                                      |                  |                |                        |                 |               |                     |                      |         |

| 80h    | INDF                     | Addressing         | this location                                        | uses content     | ts of FSR to a | address data i         | memory (not     | a physical re | gister)             | xxxx xxxx            | 25, 116 |

| 81h    | OPTION_REG               | GPPU               | INTEDG                                               | TOCS             | T0SE           | PSA                    | PS2             | PS1           | PS0                 | 1111 1111            | 19, 116 |

| 82h    | PCL                      | Program Co         | ounter's (PC)                                        | Least Signifi    | icant Byte     |                        |                 |               |                     | 0000 0000            | 25, 116 |

| 83h    | STATUS                   | IRP <sup>(1)</sup> | RP1 <sup>(1)</sup>                                   | RP0              | TO             | PD                     | Z               | DC            | С                   | 0001 1xxx            | 18, 116 |

| 84h    | FSR                      | Indirect Data      | a Memory Ac                                          | Idress Pointe    | er             |                        |                 |               |                     | xxxx xxxx            | 25, 116 |

| 85h    | TRISIO                   |                    |                                                      | TRISIO5          | TRISIO4        | TRISIO3 <sup>(4)</sup> | TRISIO2         | TRISIO1       | TRISIO0             | 11 1111              | 44, 116 |

| 86h    | _                        | Unimplemen         | Jnimplemented                                        |                  |                |                        |                 |               |                     |                      | _       |

| 87h    | _                        | Unimplemen         | Jnimplemented                                        |                  |                |                        |                 |               |                     | _                    | _       |

| 88h    | _                        | Unimplemen         | nted                                                 |                  |                |                        |                 |               |                     | _                    | _       |

| 89h    | _                        | Unimplemen         | Inimplemented                                        |                  |                |                        |                 |               |                     | —                    | —       |

| 8Ah    | PCLATH                   | _                  | — — Write Buffer for upper 5 bits of Program Counter |                  |                |                        |                 |               |                     | 0 0000               | 25, 116 |

| 8Bh    | INTCON                   | GIE                | PEIE                                                 | T0IE             | INTE           | GPIE                   | T0IF            | INTF          | GPIF <sup>(3)</sup> | 0000 0000            | 20, 116 |

| 8Ch    | PIE1                     | _                  | ADIE                                                 | CCP1IE           | _              | CMIE                   | _               | TMR2IE        | TMR1IE              | -00- 0-00            | 21, 116 |

| 8Dh    | _                        | Unimplemented      |                                                      |                  |                |                        |                 |               | —                   | —                    |         |

| 8Eh    | PCON                     | _                  | —                                                    | —                | —              | _                      | —               | POR           | BOR                 | dd                   | 23, 116 |

| 8Fh    | _                        | Unimplemen         | nted                                                 |                  |                |                        |                 |               |                     | _                    | _       |

| 90h    | OSCTUNE                  | _                  | _                                                    | _                | TUN4           | TUN3                   | TUN2            | TUN1          | TUN0                | 0 0000               | 41, 116 |

| 91h    | _                        | Unimplemen         | nted                                                 |                  |                |                        |                 |               |                     | _                    | _       |

| 92h    | PR2                      | Timer2 Mod         | ule Period R                                         | egister          |                |                        |                 |               |                     | 1111 1111            | 65, 116 |

| 93h    | APFCON                   | _                  | _                                                    | _                | T1GSEL         | _                      | _               | P1BSEL        | P1ASEL              | 000                  | 21, 116 |

| 94h    | _                        | Unimplemen         | nted                                                 |                  |                |                        |                 |               |                     | _                    | _       |

| 95h    | WPU <sup>(2)</sup>       | _                  | _                                                    | WPU5             | WPU4           | _                      | WPU2            | WPU1          | WPU0                | 11 -111              | 46, 116 |

| 96h    | IOC                      | _                  | _                                                    | IOC5             | IOC4           | IOC3                   | IOC2            | IOC1          | IOC0                | 00 0000              | 46, 116 |

| 97h    | _                        | Unimplemen         | nted                                                 |                  |                |                        |                 |               |                     | _                    | _       |

| 98h    | PMCON1 <sup>(7)</sup>    | _                  | —                                                    | —                | —              | _                      | WREN            | WR            | RD                  | 000                  | 29      |

| 99h    | PMCON2 <sup>(7)</sup>    | Program Me         | emory Contro                                         | l Register 2     | (not a physic  | al register).          |                 |               |                     |                      | —       |

| 9Ah    | PMADRL <sup>(7)</sup>    | PMADRL7            | PMADRL6                                              | PMADRL5          | PMADRL4        | PMADRL3                | PMADRL2         | PMADRL1       | PMADRL0             | 0000 0000            | 28      |

| 9Bh    | PMADRH <sup>(7)</sup>    | _                  | _                                                    | _                | —              | _                      | PMADRH2         | PMADRH1       | PMADRH0             | 000                  | 28      |

| 9Ch    | PMDATL <sup>(7)</sup>    | PMDATL7            | PMDATL6                                              | PMDATL5          | PMDATL4        | PMDATL3                | PMDATL2         | PMDATL1       | PMDATL0             | 0000 0000            | 28      |

| 9Dh    | PMDATH <sup>(7)</sup>    | —                  | —                                                    | Program M        | emory Data F   | Register High          | Byte.           |               |                     | 00 0000              | 28      |

| 9Eh    | ADRESL <sup>(5, 6)</sup> | Least Signif       | icant 2 bits o                                       | f the left shift | ed result or 8 | bits of the rig        | ght shifted res | sult          |                     | xxxx xxxx            | 85, 117 |

| 9Fh    | ANSEL                    | —                  | ADCS2                                                | ADCS1            | ADCS0          | ANS3                   | ANS2            | ANS1          | ANS0                | -000 1111            | 45, 117 |

| Logon  |                          |                    | sations road :                                       |                  |                | l                      |                 | l             | 1                   | 1                    | ·       |

#### **TABLE 2-4:** PIC12F615/617/HV615 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

- = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented IRP and RP1 bits are reserved, always maintain these bits clear. GP3 pull-up is enabled when MCLRE is '1' in the Configuration Word register. Legend: Note 1:

2:

MCLR and WDT Reset does not affect the previous value data latch. The GPIF bit will clear upon Reset but will set again if the mismatch 3: exists.

TRISIO3 always reads as '1' since it is an input only pin. 4:

Read only register. 5:

PIC12F615/617/HV615 only. 6:

7: PIC12F617 only.

## 3.0 FLASH PROGRAM MEMORY SELF READ/SELF WRITE CONTROL (FOR PIC12F617 ONLY)

The Flash program memory is readable and writable during normal operation (full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers (see Registers 3-1 to 3-5). There are six SFRs used to read and write this memory:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When interfacing the program memory block, the PMDATL and PMDATH registers form a two-byte word which holds the 14-bit data for read/write, and the PMADRL and PMADRH registers form a two-byte word which holds the 13-bit address of the Flash location being accessed. These devices have 2K words of program Flash with an address range from 0000h to 07FFh.

The program memory allows single word read and a by four word write. A four word write automatically erases the row of the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

When the device is code-protected, the CPU may continue to read and write the Flash program memory.

Depending on the settings of the Flash Program Memory Enable (WRT<1:0>) bits, the device may or may not be able to write certain blocks of the program memory, however, reads of the program memory are allowed.

When the Flash program memory Code Protection  $(\overline{CP})$  bit in the Configuration Word register is enabled, the program memory is code-protected, and the device programmer (ICSP<sup>TM</sup>) cannot access data or program memory.

#### 3.1 PMADRH and PMADRL Registers

The PMADRH and PMADRL registers can address up to a maximum of 8K words of program memory.

When selecting a program address value, the Most Significant Byte (MSB) of the address is written to the PMADRH register and the Least Significant Byte (LSB) is written to the PMADRL register.

## 3.2 PMCON1 and PMCON2 Registers

PMCON1 is the control register for the data program memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear.

PMCON2 is not a physical register. Reading PMCON2 will read all '0's. The PMCON2 register is used exclusively in the Flash memory write sequence.

| U-0       | U-0 | U-0 | U-0 | R/W-1 | U-0 | R/W-1 | R/W-1 |  |  |

|-----------|-----|-----|-----|-------|-----|-------|-------|--|--|

| —         | —   | —   | —   | ANS3  | —   | ANS1  | ANS0  |  |  |

| bit 7 bit |     |     |     |       |     |       |       |  |  |

|           |     |     |     |       |     |       |       |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                                                                             |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | ANS3: Analog Select Between Analog or Digital Function on Pin GP4<br>1 = Analog input. Pin is assigned as analog input <sup>(1)</sup> .<br>0 = Digital I/O. Pin is assigned to port or special function.                               |

| bit 2   | Unimplemented: Read as '0'                                                                                                                                                                                                             |

| bit 1   | <ul> <li>ANS1: Analog Select Between Analog or Digital Function on Pin GP1</li> <li>1 = Analog input. Pin is assigned as analog input.<sup>(1)</sup></li> <li>0 = Digital I/O. Pin is assigned to port or special function.</li> </ul> |

| bit 0   | <ul> <li>ANS0: Analog Select Between Analog or Digital Function on Pin GP0</li> <li>0 = Digital I/O. Pin is assigned to port or special function.</li> <li>1 = Analog input. Pin is assigned as analog input.<sup>(1)</sup></li> </ul> |

**Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-onchange if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

### REGISTER 5-4: ANSEL: ANALOG SELECT REGISTER (PIC12F615/617/HV615)

| U-0   | R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| —     | ADCS2 | ADCS1 | ADCS0 | ANS3  | ANS2  | ANS1  | ANS0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7   | <b>Unimplemented</b> : Read as '0'                                                                                                                                                                                                                                  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | ADCS<2:0>: A/D Conversion Clock Select bits<br>000 = Fosc/2<br>001 = Fosc/8<br>010 = Fosc/32                                                                                                                                                                        |

|         | x11 = FRC (clock derived from a dedicated internal oscillator = 500 kHz max)<br>100 = Fosc/4<br>101 = Fosc/16<br>110 = Fosc/64                                                                                                                                      |

| bit 3-0 | <b>ANS&lt;3:0&gt;</b> : Analog Select Between Analog or Digital Function on Pins GP4, GP2, GP1, GP0, respectively.<br>1 = Analog input. Pin is assigned as analog input <sup>(1)</sup> .<br>0 = Digital I/O. Pin is assigned to port or special function.           |

| Note 1: | Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-on-<br>change if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of<br>the voltage on the pin. |

## 6.0 TIMER0 MODULE

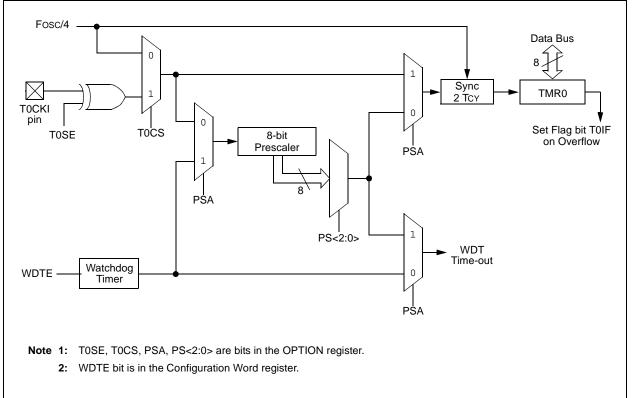

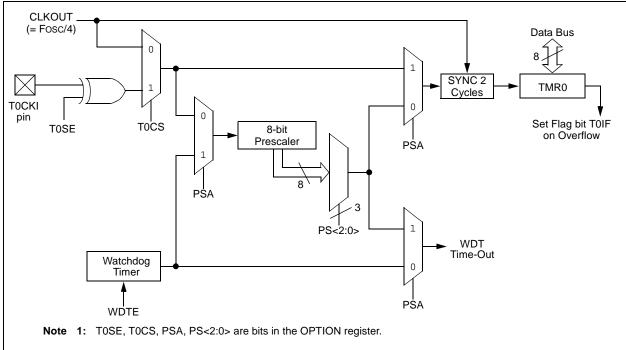

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (shared with Watchdog Timer)

- Programmable internal or external clock source

- Programmable external clock edge selection

- Interrupt on overflow

Figure 6-1 is a block diagram of the Timer0 module.

## 6.1 Timer0 Operation

When used as a timer, the Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 6.1.1 8-BIT TIMER MODE

When used as a timer, the Timer0 module will increment every instruction cycle (without prescaler). Timer mode is selected by clearing the T0CS bit of the OPTION register to '0'.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

Note: The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### 6.1.2 8-BIT COUNTER MODE

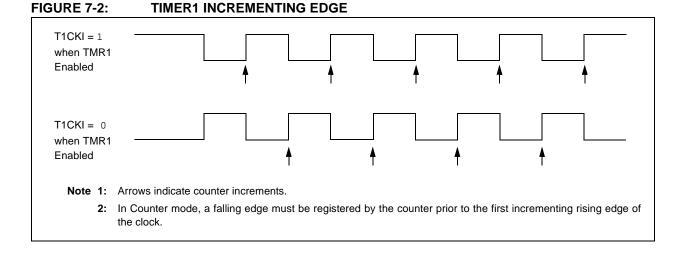

When used as a counter, the Timer0 module will increment on every rising or falling edge of the T0CKI pin. The incrementing edge is determined by the T0SE bit of the OPTION register. Counter mode is selected by setting the T0CS bit of the OPTION register to '1'.

#### FIGURE 6-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

#### 7.10 **ECCP Special Event Trigger** (PIC12F615/617/HV615 only)

If a ECCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The ECCP module may still be configured to generate a ECCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

Timer1 should be synchronized to the Fosc to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the ECCP, the write will take precedence.

For more information, see Section 11.0 "Enhanced Capture/Compare/PWM (With Auto-Shutdown and Dead Band) Module (PIC12F615/617/HV615 only)".

#### 7.11 **Comparator Synchronization**

The same clock used to increment Timer1 can also be used to synchronize the comparator output. This feature is enabled in the Comparator module.

When using the comparator for Timer1 gate, the comparator output should be synchronized to Timer1. This ensures Timer1 does not miss an increment if the comparator changes.

For more information, see Section 9.0 "Comparator Module".

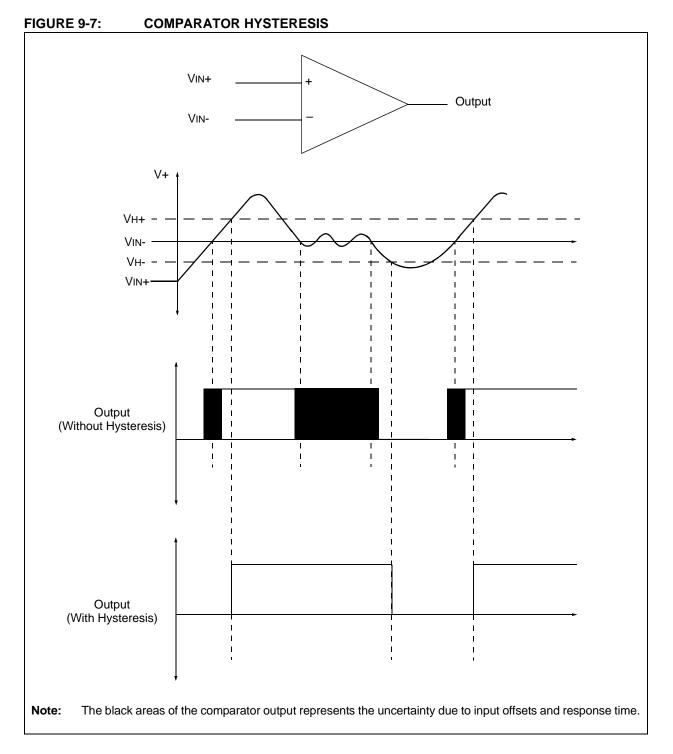

## 9.11 Comparator Hysteresis

Each comparator has built-in hysteresis that is user enabled by setting the CMHYS bit of the CMCON1 register. The hysteresis feature can help filter noise and reduce multiple comparator output transitions when the output is changing state. Figure 9-7 shows the relationship between the analog input levels and digital output of a comparator with and without hysteresis. The output of the comparator changes from a low state to a high state only when the analog voltage at VIN+ rises above the upper hysteresis threshold (VH+). The output of the comparator changes from a high state to a low state only when the analog voltage at VIN+ falls below the lower hysteresis threshold (VH-).

#### **REGISTER 10-2:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0 (READ-ONLY)

| R-x    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES9 | ADRES8 | ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 |

| bit 7  |        |        |        |        |        |        | bit 0  |

|        |        |        |        |        |        |        |        |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | s 'O'              |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-0

**ADRES<9:2>**: ADC Result Register bits Upper 8 bits of 10-bit conversion result

#### REGISTER 10-3: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0 (READ-ONLY)

| R-x      | R-x    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|----------|--------|-----|-----|-----|-----|-----|-------|

| ADRES1   | ADRES0 | —   | —   | —   | —   | —   | —     |

| bit 7    |        |     |     |     |     |     | bit 0 |

|          |        |     |     |     |     |     |       |

| l egend: |        |     |     |     |     |     |       |

| Legena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 7-6 | ADRES<1:0>: ADC Result Register bits     |

|---------|------------------------------------------|

|         | Lower 2 bits of 10-bit conversion result |

| bit 5-0 | Unimplemented: Read as '0'               |

#### REGISTER 10-4: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1 (READ-ONLY)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R-x    | R-x    |

|-------|-----|-----|-----|-----|-----|--------|--------|

| —     | —   | —   | —   | —   | —   | ADRES9 | ADRES8 |

| bit 7 |     |     |     |     |     |        | bit 0  |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | ʻ0'                |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-2 Unimplemented: Read as '0'

bit 1-0 ADRES<9:8>: ADC Result Register bits

Upper 2 bits of 10-bit conversion result

#### REGISTER 10-5: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1 (READ-ONLY)

| R-x    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | s 'O'              |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-0 ADRES<7:0>: ADC Result Register bits

Lower 8 bits of 10-bit conversion result

#### TABLE 10-2: SUMMARY OF ASSOCIATED ADC REGISTERS

| Name                    | Bit 7    | Bit 6                                                                             | Bit 5                 | Bit 4                | Bit 3   | Bit 2               | Bit 1                 | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------------------------|----------|-----------------------------------------------------------------------------------|-----------------------|----------------------|---------|---------------------|-----------------------|---------|----------------------|---------------------------------|

| ADCON0 <sup>(1)</sup>   | ADFM     | VCFG                                                                              | —                     | CHS2                 | CHS1    | CHS0                | GO/DONE               | ADON    | 00-0 0000            | 00-0 0000                       |

| ANSEL                   | —        | ADCS2 <sup>(1)</sup>                                                              | ADCS1 <sup>(1)</sup>  | ADCS0 <sup>(1)</sup> | ANS3    | ANS2 <sup>(1)</sup> | ANS1                  | ANS0    | -000 1111            | -000 1111                       |

| ADRESH <sup>(1,2)</sup> | A/D Resu | It Register                                                                       | High Byte             |                      |         |                     |                       |         | xxxx xxxx            | uuuu uuuu                       |

| ADRESL <sup>(1,2)</sup> | A/D Resu | ılt Register                                                                      | Low Byte              |                      |         |                     |                       |         | xxxx xxxx            | uuuu uuuu                       |

| GPIO                    | —        | —                                                                                 | GP5                   | GP4                  | GP3     | GP2                 | GP1                   | GP0     | x0 x000              | x0 x000                         |

| INTCON                  | GIE      | PEIE                                                                              | TOIE                  | INTE                 | GPIE    | TOIF                | INTF                  | GPIF    | 0000 0000            | 0000 0000                       |

| PIE1                    | —        | - ADIE <sup>(1)</sup> CCP1IE <sup>(1)</sup> - CMIE - TMR2IE <sup>(1)</sup> TMR1IE |                       |                      |         |                     |                       |         |                      | -00- 0-00                       |

| PIR1                    | _        | ADIF <sup>(1)</sup>                                                               | CCP1IF <sup>(1)</sup> | _                    | CMIF    | _                   | TMR2IF <sup>(1)</sup> | TMR1IF  | -00- 0-00            | -00- 0-00                       |

| TRISIO                  | _        | _                                                                                 | TRISIO5               | TRISIO4              | TRISIO3 | TRISIO2             | TRISIO1               | TRISIO0 | 11 1111              | 11 1111                         |

**Legend:** x = unknown, u = unchanged, – = unimplemented read as '0'. Shaded cells are not used for ADC module.

Note 1: For PIC12F615/617/HV615 only.

2: Read Only Register.

| Name    | Bit 7                                                                      | Bit 6                                                                       | Bit 5                 | Bit 4       | Bit 3   | Bit 2   | Bit 1                 | Bit 0   | Valu<br>POR, | e on<br>BOR | all o | e on<br>ther<br>sets |

|---------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------|-------------|---------|---------|-----------------------|---------|--------------|-------------|-------|----------------------|

| CCP1CON | P1M                                                                        | —                                                                           | DC1B1                 | DC1B0       | CCP1M3  | CCP1M2  | CCP1M1                | CCP1M0  | 0-00         | 0000        | 0-00  | 0000                 |

| CCPR1L  | Capture/C                                                                  | ompare/PW                                                                   | M Register            | 1 Low Byte  |         |         |                       |         | xxxx         | xxxx        | uuuu  | uuuu                 |

| CCPR1H  | Capture/C                                                                  | ompare/PW                                                                   | M Register            | 1 High Byte |         |         |                       |         | xxxx         | xxxx        | uuuu  | uuuu                 |

| INTCON  | GIE                                                                        | PEIE                                                                        | TOIE                  | INTE        | GPIE    | TOIF    | INTF                  | GPIF    | 0000         | 0000        | 0000  | 0000                 |

| PIE1    | _                                                                          | ADIE <sup>(1)</sup>                                                         | CCP1IE <sup>(1)</sup> | —           | CMIE    | _       | TMR2IE <sup>(1)</sup> | TMR1IE  | -00-         | 0-00        | -00-  | 0-00                 |

| PIR1    | _                                                                          | ADIF <sup>(1)</sup>                                                         | CCP1IF <sup>(1)</sup> | —           | CMIF    | _       | TMR2IF <sup>(1)</sup> | TMR1IF  | -00-         | 0-00        | -00-  | 0-00                 |

| T1CON   | T1GINV                                                                     | TMR1GE                                                                      | T1CKPS1               | T1CKPS0     | T1OSCEN | T1SYNC  | TMR1CS                | TMR10N  | 0000         | 0000        | uuuu  | uuuu                 |

| TMR1L   | Holding Re                                                                 | lolding Register for the Least Significant Byte of the 16-bit TMR1 Register |                       |             |         |         |                       |         | xxxx         | xxxx        | uuuu  | uuuu                 |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |                                                                             |                       |             |         |         |                       |         | xxxx         | xxxx        | uuuu  | uuuu                 |

| TRISIO  | _                                                                          | —                                                                           | TRISIO5               | TRISIO4     | TRISIO3 | TRISIO2 | TRISIO1               | TRISIO0 | 11           | 1111        | 11    | 1111                 |

#### TABLE 11-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPTURE

**Legend:** - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Capture.

Note 1: For PIC12F615/617/HV615 only.

# PIC12F609/615/617/12HV609/615

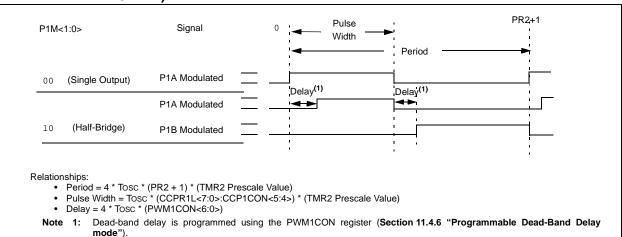

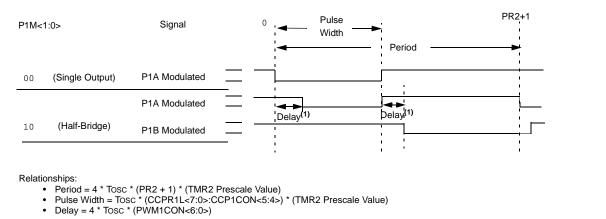

# FIGURE 11-6: EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS (ACTIVE-HIGH STATE)

#### FIGURE 11-7: EXAMPLE ENHANCED PWM OUTPUT RELATIONSHIPS (ACTIVE-LOW STATE)

Note 1: Dead-band delay is programmed using the PWM1CON register (Section 11.4.6 "Programmable Dead-Band Delay mode").

# PIC12F609/615/617/12HV609/615

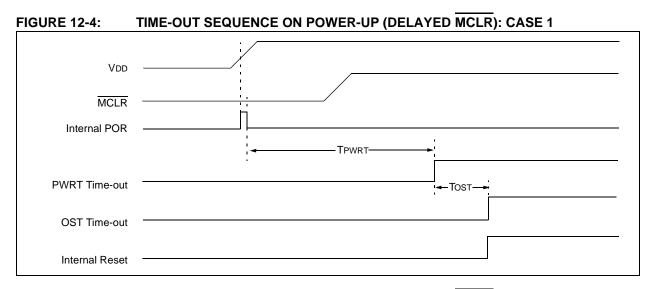

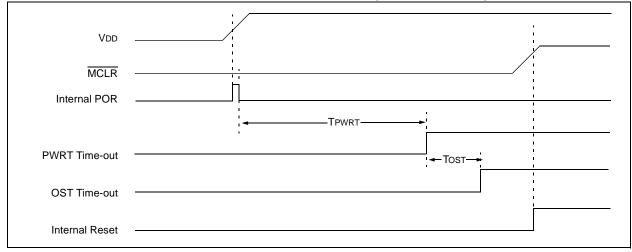

### FIGURE 12-5: TIME-OUT SEQUENCE ON POWER-UP (DELAYED MCLR): CASE 2

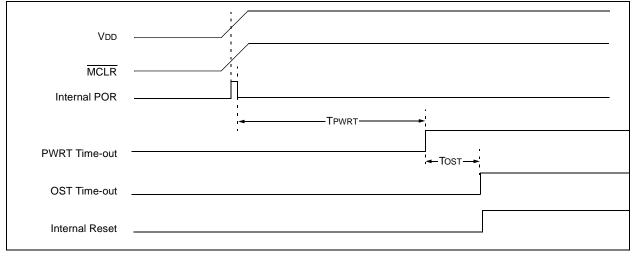

## FIGURE 12-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR WITH VDD)

#### 12.6.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worstcase conditions (i.e., VDD = Min., Temperature = Max., Max. WDT prescaler) it may take several seconds before a WDT time out occurs.

#### FIGURE 12-2: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 12-8: WDT STATUS

| Conditions                                              | WDT                          |

|---------------------------------------------------------|------------------------------|

| WDTE = 0                                                |                              |

| CLRWDT Command                                          | Cleared                      |

| Oscillator Fail Detected                                | Cleared                      |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTRC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                  | Cleared until the end of OST |

#### TABLE 12-9: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

| Name       | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|--------|--------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| OPTION_REG | GPPU   | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111            | 1111 1111                       |

| CONFIG     | IOSCFS | CP     | MCLRE | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0 | —                    | —                               |

Legend: Shaded cells are not used by the Watchdog Timer.

**Note 1:** See Register 12-1 for operation of all Configuration Word register bits.

## 15.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 15.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

## 15.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

## 15.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 15.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

## 16.0 ELECTRICAL SPECIFICATIONS

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                | 40° to +125°C             |

|---------------------------------------------------------------------------------------------------------------|---------------------------|

| Storage temperature                                                                                           | 65°C to +150°C            |

| Voltage on VDD with respect to Vss                                                                            | -0.3V to +6.5V            |

| Voltage on MCLR with respect to Vss                                                                           | -0.3V to +13.5V           |

| Voltage on all other pins with respect to Vss                                                                 | 0.3V to (VDD + 0.3V)      |

| Total power dissipation <sup>(1)</sup>                                                                        |                           |

| Maximum current out of Vss pin                                                                                | 95 mA                     |

| Maximum current into Vod pin                                                                                  | 95 mA                     |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                  | ± 20 mA                   |

| Output clamp current, Iок (Vo < 0 or Vo >VDD)                                                                 | ± 20 mA                   |

| Maximum output current sunk by any I/O pin                                                                    | 25 mA                     |

| Maximum output current sourced by any I/O pin                                                                 | 25 mA                     |

| Maximum current sunk by GPIO                                                                                  | 90 mA                     |

| Maximum current sourced GPIO                                                                                  | 90 mA                     |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $-\sum$ IOH} + $\sum$ {(VD IOL). | ⊡ – Vон) х Iон} + ∑(Vol х |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

## 16.1 DC Characteristics: PIC12F609/615/617/12HV609/615-I (Industrial) PIC12F609/615/617/12HV609/615-E (Extended)

| DC CHARACTERISTICS |      |                                                                  |      | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}\mbox{C} \leq T\mbox{A} \leq +85^{\circ}\mbox{C for industrial} \\ -40^{\circ}\mbox{C} \leq T\mbox{A} \leq +125^{\circ}\mbox{C for extended} \end{array}$ |     |       |                                                        |  |  |

|--------------------|------|------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------------------------------------------------------|--|--|

| Param<br>No.       | Sym  | Characteristic                                                   | Min  | Тур†                                                                                                                                                                                                                                                                                    | Max | Units | Conditions                                             |  |  |

|                    | Vdd  | Supply Voltage                                                   |      |                                                                                                                                                                                                                                                                                         |     |       |                                                        |  |  |

| D001               |      | PIC12F609/615/617                                                | 2.0  | —                                                                                                                                                                                                                                                                                       | 5.5 | V     | Fosc < = 4 MHz                                         |  |  |

| D001               |      | PIC12HV609/615                                                   | 2.0  | —                                                                                                                                                                                                                                                                                       | (2) | V     | Fosc < = 4 MHz                                         |  |  |

| D001B              |      | PIC12F609/615/617                                                | 2.0  | —                                                                                                                                                                                                                                                                                       | 5.5 | V     | Fosc < = 8 MHz                                         |  |  |

| D001B              |      | PIC12HV609/615                                                   | 2.0  | —                                                                                                                                                                                                                                                                                       | (2) | V     | Fosc < = 8 MHz                                         |  |  |

| D001C              |      | PIC12F609/615/617                                                | 3.0  | —                                                                                                                                                                                                                                                                                       | 5.5 | V     | Fosc < = 10 MHz                                        |  |  |

| D001C              |      | PIC12HV609/615                                                   | 3.0  | —                                                                                                                                                                                                                                                                                       | (2) | V     | Fosc < = 10 MHz                                        |  |  |

| D001D              |      | PIC12F609/615/617                                                | 4.5  | _                                                                                                                                                                                                                                                                                       | 5.5 | V     | Fosc < = 20 MHz                                        |  |  |

| D001D              |      | PIC12HV609/615                                                   | 4.5  | —                                                                                                                                                                                                                                                                                       | (2) | V     | Fosc < = 20 MHz                                        |  |  |

| D002*              | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | 1.5  | —                                                                                                                                                                                                                                                                                       |     | V     | Device in Sleep mode                                   |  |  |

| D003               | VPOR | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —    | Vss                                                                                                                                                                                                                                                                                     | _   | V     | See Section 12.3.1 "Power-on Reset (POR)" for details. |  |  |

| D004*              | SVDD | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05 | —                                                                                                                                                                                                                                                                                       |     | V/ms  | See Section 12.3.1 "Power-on Reset (POR)" for details. |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

2: User defined. Voltage across the shunt regulator should not exceed 5V.

### 16.8 DC Characteristics: PIC12F609/615/617/12HV609/615-I (Industrial) PIC12F609/615/617/12HV609/615-E (Extended)

| DC CHARACTERISTICS |      |                                          | Standard Operating Con<br>Operating temperature |          | ditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |       | 5°C for industrial                                                 |

|--------------------|------|------------------------------------------|-------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------|

| Param<br>No.       | Sym  | Characteristic                           | Min                                             | Тур†     | Max                                                                                                                            | Units | Conditions                                                         |

|                    | VIL  | Input Low Voltage                        |                                                 |          |                                                                                                                                |       |                                                                    |

|                    |      | I/O port:                                |                                                 |          |                                                                                                                                |       |                                                                    |

| D030               |      | with TTL buffer                          | Vss                                             | —        | 0.8                                                                                                                            | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                   |

| D030A              |      |                                          | Vss                                             | —        | 0.15 Vdd                                                                                                                       | V     | $2.0V \leq V \text{DD} \leq 4.5 \text{V}$                          |

| D031               |      | with Schmitt Trigger buffer              | Vss                                             | _        | 0.2 Vdd                                                                                                                        | V     | $2.0V \le VDD \le 5.5V$                                            |

| D032               |      | MCLR, OSC1 (RC mode)                     | Vss                                             | _        | 0.2 Vdd                                                                                                                        | V     | (NOTE 1)                                                           |

| D033               |      | OSC1 (XT and LP modes)                   | Vss                                             | _        | 0.3                                                                                                                            | V     |                                                                    |

| D033A              |      | OSC1 (HS mode)                           | Vss                                             | —        | 0.3 Vdd                                                                                                                        | V     |                                                                    |

|                    | VIH  | Input High Voltage                       |                                                 |          |                                                                                                                                |       |                                                                    |

|                    |      | I/O ports:                               |                                                 | _        |                                                                                                                                |       |                                                                    |

| D040               |      | with TTL buffer                          | 2.0                                             | _        | Vdd                                                                                                                            | V     | $4.5V \leq V \text{DD} \leq 5.5V$                                  |

| D040A              |      |                                          | 0.25 VDD + 0.8                                  | —        | Vdd                                                                                                                            | V     | $2.0V \leq V \text{DD} \leq 4.5 \text{V}$                          |

| D041               |      | with Schmitt Trigger buffer              | 0.8 Vdd                                         | —        | Vdd                                                                                                                            | V     | $2.0V \leq V \text{DD} \leq 5.5 \text{V}$                          |

| D042               |      | MCLR                                     | 0.8 Vdd                                         | —        | Vdd                                                                                                                            | V     |                                                                    |

| D043               |      | OSC1 (XT and LP modes)                   | 1.6                                             | —        | Vdd                                                                                                                            | V     |                                                                    |

| D043A              |      | OSC1 (HS mode)                           | 0.7 Vdd                                         | _        | Vdd                                                                                                                            | V     |                                                                    |

| D043B              |      | OSC1 (RC mode)                           | 0.9 Vdd                                         | —        | Vdd                                                                                                                            | V     | (NOTE 1)                                                           |

|                    | lı∟  | Input Leakage Current <sup>(2,3)</sup>   |                                                 |          |                                                                                                                                |       |                                                                    |

| D060               |      | I/O ports                                | _                                               | ± 0.1    | ± 1                                                                                                                            | μΑ    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance                   |

| D061               |      | GP3/MCLR <sup>(3,4)</sup>                | —                                               | $\pm0.7$ | ± 5                                                                                                                            | μΑ    | $V\text{SS} \leq V\text{PIN} \leq V\text{DD}$                      |

| D063               |      | OSC1                                     | —                                               | ± 0.1    | ± 5                                                                                                                            | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration |

| D070*              | IPUR | GPIO Weak Pull-up Current <sup>(5)</sup> | 50                                              | 250      | 400                                                                                                                            | μΑ    | VDD = 5.0V, VPIN = VSS                                             |

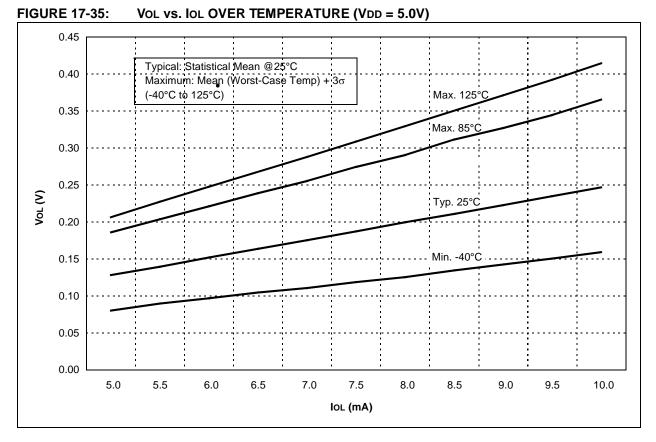

|                    | Vol  | Output Low Voltage                       | _                                               | _        | 0.6                                                                                                                            | V     | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                       |

| D080               |      | I/O ports                                | _                                               | -        | 0.6                                                                                                                            | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                        |

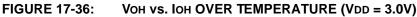

|                    | Vон  | Output High Voltage                      | VDD - 0.7                                       | —        | —                                                                                                                              | V     | IOH = -2.5mA, VDD = 4.5V,<br>-40°С to +125°С                       |

| D090               |      | I/O ports <sup>(2)</sup>                 | Vdd - 0.7                                       | -        | -                                                                                                                              | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                       |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: This specification applies to GP3/MCLR configured as GP3 with the internal weak pull-up disabled.

5: This specification applies to all weak pull-up pins, including the weak pull-up found on GP3/MCLR. When GP3/MCLR is configured as MCLR reset pin, the weak pull-up is always enabled.

6: Applies to PIC12F617 only.

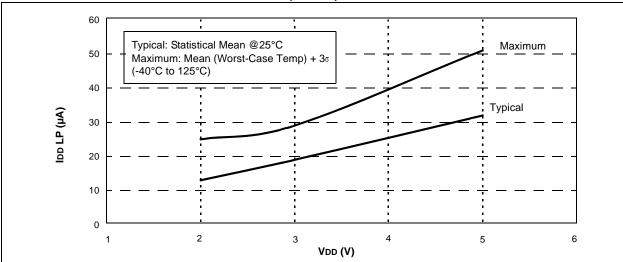

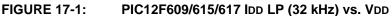

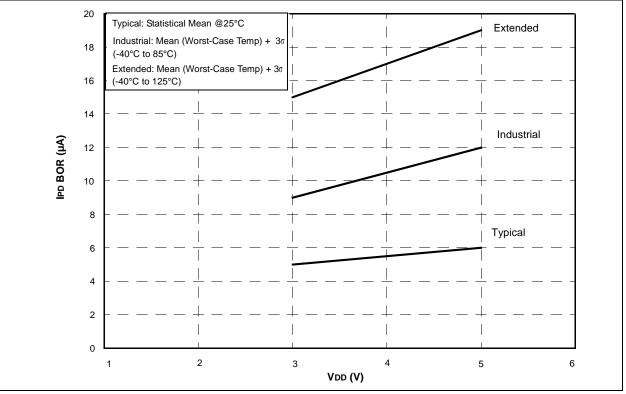

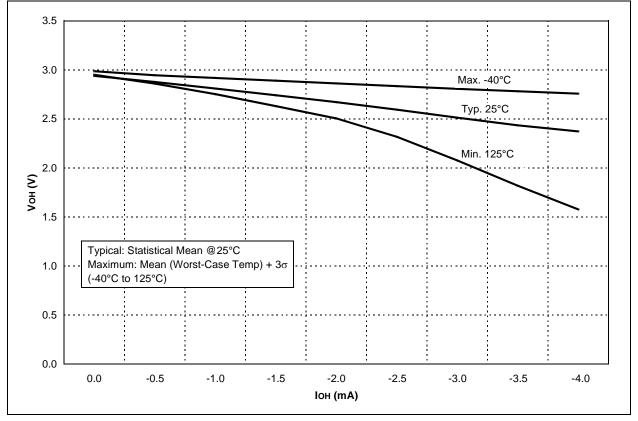

## 17.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where s is a standard deviation, over each temperature range.

# PIC12F609/615/617/12HV609/615

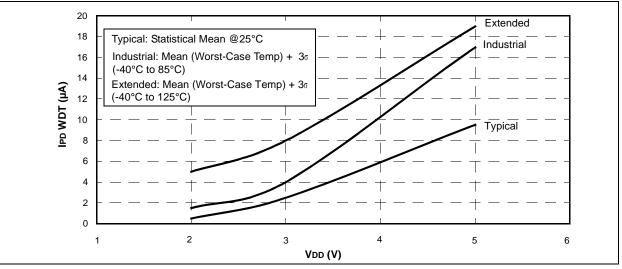

### FIGURE 17-12: PIC12F609/615/617 IPD WDT vs. VDD

© 2010 Microchip Technology Inc.

## INDEX

| Α                                        |            |

|------------------------------------------|------------|

| A/D                                      |            |

| Specifications                           | . 164. 165 |

| Absolute Maximum Ratings                 |            |

| AC Characteristics                       |            |

| Industrial and Extended                  | 156        |

| Load Conditions                          | 155        |

| ADC                                      |            |

| Acquisition Requirements                 |            |

| Associated registers                     |            |

| Block Diagram                            | 79         |

| Calculating Acquisition Time             |            |

| Channel Selection                        | 80         |

| Configuration                            |            |

| Configuring Interrupt                    |            |

| Conversion Clock                         |            |

| Conversion Procedure                     |            |

| Internal Sampling Switch (Rss) Impedance |            |

| Interrupts                               |            |

| Operation                                |            |

| Operation During Sleep                   |            |

| Port Configuration                       |            |

| Reference Voltage (VREF)                 |            |

| Result Formatting                        |            |

| Source Impedance                         |            |

| Special Event Trigger                    |            |

| Starting an A/D Conversion               |            |

| ADC (PIC12F615/617/HV615 Only)           |            |

| ADCON0 Register                          |            |

| ADRESH Register (ADFM = 0)               |            |

| ADRESH Register (ADFM = 1)               |            |

| ADRESL Register (ADFM = 0)               |            |

| ADRESL Register (ADFM = 1)               |            |

| Analog Input Connection Considerations   |            |

| Analog-to-Digital Converter. See ADC     |            |

| ANSEL Register (PIC12F609/HV609)         |            |

| ANSEL Register (PIC12F615/617/HV615)     |            |

| APFCON Register                          | 24         |

| Assembler                                | 4.40       |

| MPASM Assembler                          | 140        |

## В

| Block Diagrams                            |        |

|-------------------------------------------|--------|

| (CCP) Capture Mode Operation              |        |

| ADC                                       | 79     |

| ADC Transfer Function                     | 87     |

| Analog Input Model                        | 68, 87 |

| Auto-Shutdown                             |        |

| CCP PWM                                   | 94     |

| Clock Source                              | 37     |

| Comparator                                | 67     |

| Compare                                   | 92     |

| Crystal Operation                         | 39     |

| External RC Mode                          | 40     |

| GP0 and GP1 Pins                          | 47     |

| GP2 Pins                                  | 48     |

| GP3 Pin                                   | 49     |

| GP4 Pin                                   | 50     |

| GP5 Pin                                   | 51     |

| In-Circuit Serial Programming Connections | 125    |

| Interrupt Logic                           | 119    |

| MCLR Circuit                              | 111    |

| On-Chip Reset Circuit                     | 110    |

|                                           |        |

| PIC12F609/12HV609          | 7      |

|----------------------------|--------|

| PIC12F615/617/12HV615      | 8      |

| PWM (Enhanced)             | 97     |

| Resonator Operation        | 39     |

| Timer1                     | 57, 58 |

| Timer2                     | 65     |

| TMR0/WDT Prescaler         | 53     |

| Watchdog Timer             | 122    |

| Brown-out Reset (BOR)      | 112    |

| Associated Registers       | 113    |

| Specifications             | 160    |

| Timing and Characteristics | 159    |

## С

| C Compilers                                   |     |

|-----------------------------------------------|-----|

| MPLAB C18                                     | 140 |

| MPLAB C30                                     |     |

| Calibration Bits                              |     |

| Capture Module. See Enhanced Capture/Compare/ |     |

| PWM (ECCP)                                    |     |

| Capture/Compare/PWM (CCP)                     |     |

| Associated registers w/ Capture               | 91  |

| Associated registers w/ Compare               |     |

| Associated registers w/ PWM                   |     |

| Capture Mode                                  |     |

| CCP1 Pin Configuration                        |     |

| Compare Mode                                  |     |

| CCP1 Pin Configuration                        |     |

| Software Interrupt Mode                       |     |

| •                                             |     |

| Special Event Trigger                         |     |

| Timer1 Mode Selection                         | '   |

| Prescaler                                     |     |

| PWM Mode                                      | -   |

| Duty Cycle                                    |     |

| Effects of Reset                              | 96  |

| Example PWM Frequencies and                   |     |

| Resolutions, 20 MHZ                           | 95  |

| Example PWM Frequencies and                   |     |

| Resolutions, 8 MHz                            |     |

| Operation in Sleep Mode                       |     |

| Setup for Operation                           |     |

| System Clock Frequency Changes                |     |

| PWM Period                                    |     |

| Setup for PWM Operation                       |     |

| CCP1CON (Enhanced) Register                   | 89  |

| Clock Sources                                 |     |

| External Modes                                | 38  |

| EC                                            | 38  |

| HS                                            | 39  |

| LP                                            | 39  |

| OST                                           | 38  |

| RC                                            | 40  |

| XT                                            | 39  |

| Internal Modes                                | 40  |

| INTOSC                                        | 40  |

| INTOSCIO                                      |     |

| CMCON0 Register                               |     |

| CMCON1 Register                               |     |

| Code Examples                                 |     |

| A/D Conversion                                | 83  |

| Assigning Prescaler to Timer0                 |     |

| Assigning Prescaler to WDT                    |     |

| Changing Between Capture Prescalers           |     |

| Indirect Addressing                           |     |

|                                               |     |