Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-TSSOP, 8-MSOP (0.118", 3.00mm Width)                                   |

| Supplier Device Package    | 8-MSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f609-e-ms |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 MEMORY ORGANIZATION

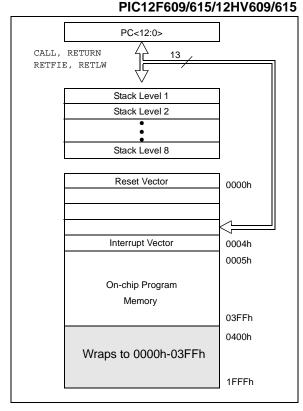

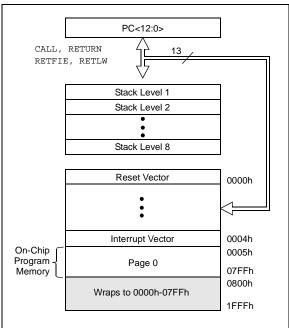

### 2.1 Program Memory Organization

The PIC12F609/615/617/12HV609/615 has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (000h-03FFh) for the PIC12F609/615/12HV609/615 is physically implemented. For the PIC12F617, the first 2K x 14 (0000h-07FFh) is physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 1K x 14 space for PIC12F609/615/12HV609/615 devices, and within the first 2K x 14 space for the PIC12F617 device. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 2-1).

### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK FOR THE

### FIGURE 2-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC12F617

## 2.2 Data Memory Organization

The data memory (see Figure 2-3) is partitioned into two banks, which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). The Special Function Registers are located in the first 32 locations of each bank. Register locations 40h-7Fh in Bank 0 are General Purpose Registers, implemented as static RAM. For the PIC12F617, the register locations 20h-7Fh in Bank 0 and A0h-EFh in Bank 1 are general purpose registers implemented as Static RAM. Register locations F0h-FFh in Bank 1 point to addresses 70h-7Fh in Bank 0. All other RAM is unimplemented and returns '0' when read. The RP0 bit of the STATUS register is the bank select bit.

### <u>RP0</u>

- $0 \rightarrow \text{Bank 0 is selected}$

- $1 \rightarrow \text{Bank 1 is selected}$

- Note: The IRP and RP1 bits of the STATUS register are reserved and should always be maintained as '0's.

### 2.2.2.5 PIR1 Register

The PIR1 register contains the Peripheral Interrupt flag bits, as shown in Register 2-5.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| U-0   | R/W-0               | R/W-0                 | U-0 | R/W-0 | U-0 | R/W-0                 | R/W-0  |

|-------|---------------------|-----------------------|-----|-------|-----|-----------------------|--------|

| —     | ADIF <sup>(1)</sup> | CCP1IF <sup>(1)</sup> | _   | CMIF  | —   | TMR2IF <sup>(1)</sup> | TMR1IF |

| bit 7 |                     |                       |     |       |     |                       | bit 0  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7 | Unimplemented: Read as '0'                                                                                                           |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ADIF: A/D Interrupt Flag bit <sup>(1)</sup>                                                                                          |

|       | 1 = A/D conversion complete                                                                                                          |

|       | 0 = A/D conversion has not completed or has not been started                                                                         |

| bit 5 | CCP1IF: CCP1 Interrupt Flag bit <sup>(1)</sup>                                                                                       |

|       | Capture mode:                                                                                                                        |

|       | <ul><li>1 = A TMR1 register capture occurred (must be cleared in software)</li><li>0 = No TMR1 register capture occurred</li></ul>   |

|       | <u>Compare mode</u> :<br>1 = A TMR1 register compare match occurred (must be cleared in software)                                    |

|       | 0 = No TMR1 register compare match occurred                                                                                          |

|       | <u>PWM mode</u> :                                                                                                                    |

|       | Unused in this mode                                                                                                                  |

| bit 4 | Unimplemented: Read as '0'                                                                                                           |

| bit 3 | CMIF: Comparator Interrupt Flag bit                                                                                                  |

|       | 1 = Comparator output has changed (must be cleared in software)                                                                      |

|       | 0 = Comparator output has not changed                                                                                                |

| bit 2 | Unimplemented: Read as '0'                                                                                                           |

| bit 1 | TMR2IF: Timer2 to PR2 Match Interrupt Flag bit <sup>(1)</sup>                                                                        |

|       | <ul> <li>1 = Timer2 to PR2 match occurred (must be cleared in software)</li> <li>0 = Timer2 to PR2 match has not occurred</li> </ul> |

| bit 0 | TMR1IF: Timer1 Overflow Interrupt Flag bit                                                                                           |

|       | 1 = Timer1 register overflowed (must be cleared in software)                                                                         |

|       | 0 = Timer1 has not overflowed                                                                                                        |

Note 1: PIC12F615/617/HV615 only. PIC12F609/HV609 unimplemented, read as '0'.

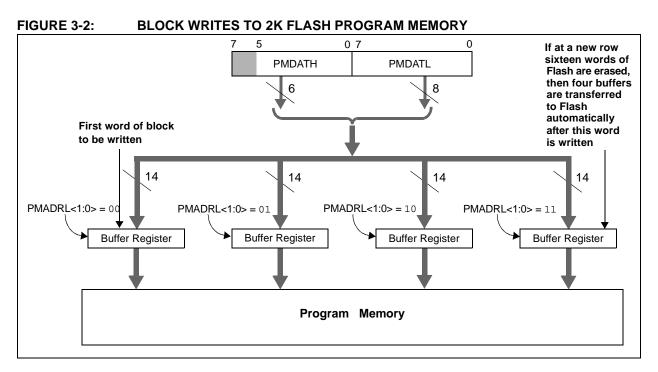

### 3.0 FLASH PROGRAM MEMORY SELF READ/SELF WRITE CONTROL (FOR PIC12F617 ONLY)

The Flash program memory is readable and writable during normal operation (full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers (see Registers 3-1 to 3-5). There are six SFRs used to read and write this memory:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When interfacing the program memory block, the PMDATL and PMDATH registers form a two-byte word which holds the 14-bit data for read/write, and the PMADRL and PMADRH registers form a two-byte word which holds the 13-bit address of the Flash location being accessed. These devices have 2K words of program Flash with an address range from 0000h to 07FFh.

The program memory allows single word read and a by four word write. A four word write automatically erases the row of the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

When the device is code-protected, the CPU may continue to read and write the Flash program memory.

Depending on the settings of the Flash Program Memory Enable (WRT<1:0>) bits, the device may or may not be able to write certain blocks of the program memory, however, reads of the program memory are allowed.

When the Flash program memory Code Protection  $(\overline{CP})$  bit in the Configuration Word register is enabled, the program memory is code-protected, and the device programmer (ICSP<sup>TM</sup>) cannot access data or program memory.

### 3.1 PMADRH and PMADRL Registers

The PMADRH and PMADRL registers can address up to a maximum of 8K words of program memory.

When selecting a program address value, the Most Significant Byte (MSB) of the address is written to the PMADRH register and the Least Significant Byte (LSB) is written to the PMADRL register.

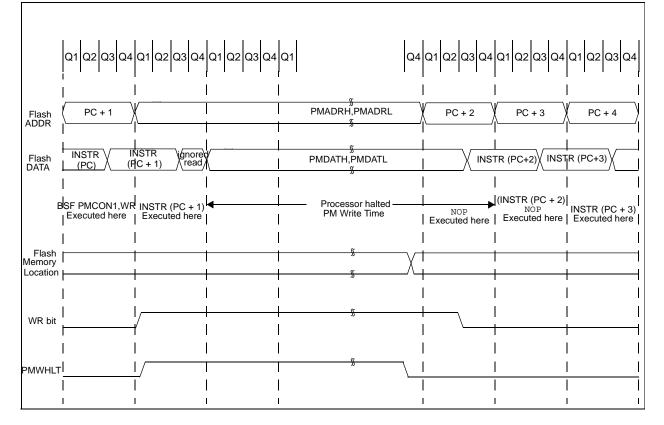

### 3.2 PMCON1 and PMCON2 Registers

PMCON1 is the control register for the data program memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear.

PMCON2 is not a physical register. Reading PMCON2 will read all '0's. The PMCON2 register is used exclusively in the Flash memory write sequence.

### TABLE 5-1:SUMMARY OF REGISTERS ASSOCIATED WITH GPIO

| Name                   | Bit 7  | Bit 6                | Bit 5                | Bit 4                | Bit 3   | Bit 2               | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|----------------------|----------------------|----------------------|---------|---------------------|---------|---------|----------------------|---------------------------------|

| ANSEL                  | _      | ADCS2 <sup>(1)</sup> | ADCS1 <sup>(1)</sup> | ADCS0 <sup>(1)</sup> | ANS3    | ANS2 <sup>(1)</sup> | ANS1    | ANS0    | -000 1111            | -000 1111                       |

| CMCON0                 | CMON   | COUT                 | CMOE                 | CMPOL                | _       | CMR                 | _       | CMCH    | 0000 -0-0            | 0000 -0-0                       |

| INTCON                 | GIE    | PEIE                 | TOIE                 | INTE                 | GPIE    | T0IF                | INTF    | GPIF    | 0000 0000            | 0000 0000                       |

| IOC                    | _      | _                    | IOC5                 | IOC4                 | IOC3    | IOC2                | IOC1    | IOC0    | 00 0000              | 00 0000                         |

| OPTION_REG             | GPPU   | INTEDG               | TOCS                 | T0SE                 | PSA     | PS2                 | PS1     | PS0     | 1111 1111            | 1111 1111                       |

| GPIO                   | _      | _                    | GP5                  | GP4                  | GP3     | GP2                 | GP1     | GP0     | xx xxxx              | u0 u000                         |

| TRISIO                 | _      | —                    | TRISIO5              | TRISIO4              | TRISIO3 | TRISIO2             | TRISIO1 | TRISIO0 | 11 1111              | 11 1111                         |

| WPU                    | _      | —                    | WPU5                 | WPU4                 | WPU3    | WPU2                | WPU1    | WPU0    | 11 1111              | 11 -111                         |

| T1CON                  | T1GINV | TMR1GE               | TICKPS1              | T1CKPS0              | T1OSCEN | T1SYNC              | TMR1CS  | TMR10N  | 0000 0000            | uuuu uuuu                       |

| CCP1CON <sup>(1)</sup> | P1M    | —                    | DC1B1                | DC1B0                | CCP1M3  | CCP1M2              | CCP1M1  | CCP1M0  | 0-00 0000            | 0-00 0000                       |

| APFCON <sup>(1)</sup>  | _      | —                    | _                    | T1GSEL               | —       | —                   | P1BSEL  | P1ASEL  | 000                  | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by GPIO. Note 1: PIC12F615/617/HV615 only.

## 7.12 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 7-1, is used to control Timer1 and select the various features of the Timer1 module.

### REGISTER 7-1: T1CON: TIMER 1 CONTROL REGISTER

| R/W-0               | R/W-0                                                                          | R/W-0                                                                                                                                                                                                               | R/W-0                  | R/W-0            | R/W-0           | R/W-0           | R/W-0     |  |  |  |

|---------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------|-----------------|-----------------|-----------|--|--|--|

| T1GINV <sup>(</sup> | <sup>1)</sup> TMR1GE <sup>(2)</sup>                                            | T1CKPS1                                                                                                                                                                                                             | T1CKPS0                | T1OSCEN          | T1SYNC          | TMR1CS          | TMR10N    |  |  |  |

| bit 7               |                                                                                |                                                                                                                                                                                                                     |                        | •                |                 | •               | bit 0     |  |  |  |

|                     |                                                                                |                                                                                                                                                                                                                     |                        |                  |                 |                 |           |  |  |  |

| Legend:             |                                                                                |                                                                                                                                                                                                                     |                        |                  |                 |                 |           |  |  |  |

| R = Reada           | ble bit                                                                        | W = Writable                                                                                                                                                                                                        | bit                    | U = Unimpler     | nented bit, rea | d as '0'        |           |  |  |  |

| -n = Value          | at POR                                                                         | '1' = Bit is set                                                                                                                                                                                                    |                        | '0' = Bit is cle | ared            | x = Bit is unkr | nown      |  |  |  |

| bit 7               | 1 = Timer1 ga                                                                  |                                                                                                                                                                                                                     | h (Timer1 cou          | nts when gate    | • •             |                 |           |  |  |  |

| bit 6               | TMR1GE: Tin<br><u>If TMR1ON =</u><br>This bit is igno<br><u>If TMR1ON =</u>    | ner1 Gate Ena<br><u>o:</u><br>ored<br><u>1:</u><br>on if Timer1 ga                                                                                                                                                  | ble bit <sup>(2)</sup> | c                |                 |                 |           |  |  |  |

| bit 5-4             | T1CKPS<1:0                                                                     | >: Timer1 Inpu                                                                                                                                                                                                      | t Clock Presca         | ale Select bits  |                 |                 |           |  |  |  |

|                     | 11 = 1:8 Pres<br>10 = 1:4 Pres<br>01 = 1:2 Pres<br>00 = 1:1 Pres               | cale Value<br>cale Value                                                                                                                                                                                            |                        |                  |                 |                 |           |  |  |  |

| bit 3               | T1OSCEN: L                                                                     | P Oscillator En                                                                                                                                                                                                     | able Control b         | it               |                 |                 |           |  |  |  |

|                     | 1 = LP oscilla<br>0 = LP oscilla<br><u>For all other s</u><br>This bit is igno | If INTOSC without CLKOUT oscillator is active:<br>1 = LP oscillator is enabled for Timer1 clock<br>0 = LP oscillator is off<br>For all other system clock modes:<br>This bit is ignored. LP oscillator is disabled. |                        |                  |                 |                 |           |  |  |  |

| bit 2               |                                                                                |                                                                                                                                                                                                                     | lock Input Syr         | chronization C   | ontrol bit      |                 |           |  |  |  |

|                     | 0 = Synchron<br>TMR1CS = 0:                                                    | nchronize exte<br>ize external clo                                                                                                                                                                                  | ock input              |                  |                 |                 |           |  |  |  |

| bit 1               | TMR1CS: Tin                                                                    | ner1 Clock Sou                                                                                                                                                                                                      | rce Select bit         |                  |                 |                 |           |  |  |  |

|                     |                                                                                | 1 = External clock from T1CKI pin (on the rising edge)<br>0 = Internal clock (FOSC/4) or system clock (FOSC) <sup>(3)</sup>                                                                                         |                        |                  |                 |                 |           |  |  |  |

| bit 0               | <b>TMR1ON:</b> Tin<br>1 = Enables T<br>0 = Stops Tim                           | īmer1                                                                                                                                                                                                               |                        |                  |                 |                 |           |  |  |  |

| 2:                  | T1GINV bit inverts<br>TMR1GE bit must<br>register, as a Time                   | be set to use e                                                                                                                                                                                                     | either T1G pin         |                  |                 | T1GSS bit of th | ne CMCON1 |  |  |  |

**3:** See T1ACS bit in CMCON1 register.

## 9.0 COMPARATOR MODULE

The comparator can be used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparator is a very useful mixed signal building block because it provides analog functionality independent of the program execution. The Analog Comparator module includes the following features:

- Programmable input section

- Comparator output is available internally/externally

- Programmable output polarity

- Interrupt-on-change

- · Wake-up from Sleep

- PWM shutdown

- Timer1 gate (count enable)

- Output synchronization to Timer1 clock input

- Programmable voltage reference

- User-enable Comparator Hysteresis

### 9.1 Comparator Overview

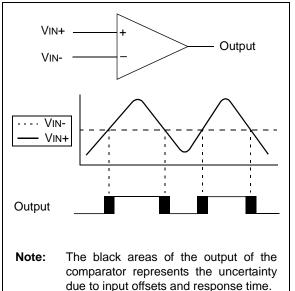

The comparator is shown in Figure 9-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less

than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

### **FIGURE 9-1:SINGLE COMPARATOR**

els and the

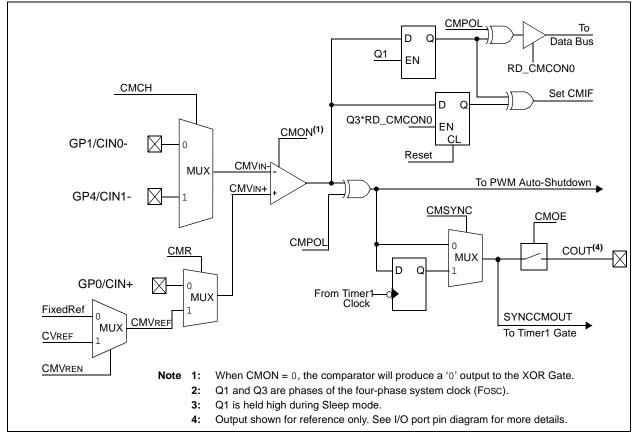

### FIGURE 9-2: COMPARATOR SIMPLIFIED BLOCK DIAGRAM

### 11.3.4 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

### 11.3.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See **Section 4.0** "Oscillator Module" for additional details.

### 11.3.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

### 11.3.7 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Disable the PWM pin (CCP1) output drivers by setting the associated TRIS bit.

- 2. Set the PWM period by loading the PR2 register.

- Configure the CCP module for the PWM mode by loading the CCP1CON register with the appropriate values.

- 4. Set the PWM duty cycle by loading the CCPR1L register and DC1B bits of the CCP1CON register.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register.

- Set the Timer2 prescale value by loading the T2CKPS bits of the T2CON register.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output after a new PWM cycle has started:

- Wait until Timer2 overflows (TMR2IF bit of the PIR1 register is set).

- Enable the CCP1 pin output driver by clearing the associated TRIS bit.

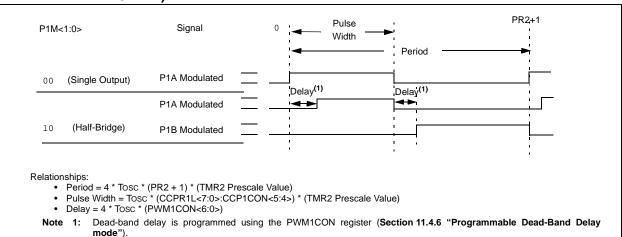

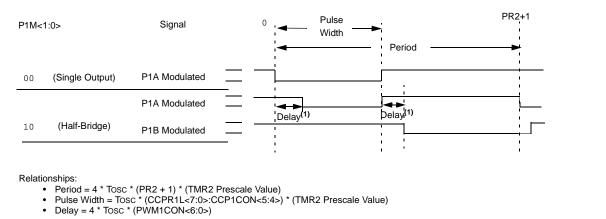

# FIGURE 11-6: EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS (ACTIVE-HIGH STATE)

### FIGURE 11-7: EXAMPLE ENHANCED PWM OUTPUT RELATIONSHIPS (ACTIVE-LOW STATE)

Note 1: Dead-band delay is programmed using the PWM1CON register (Section 11.4.6 "Programmable Dead-Band Delay mode").

NOTES:

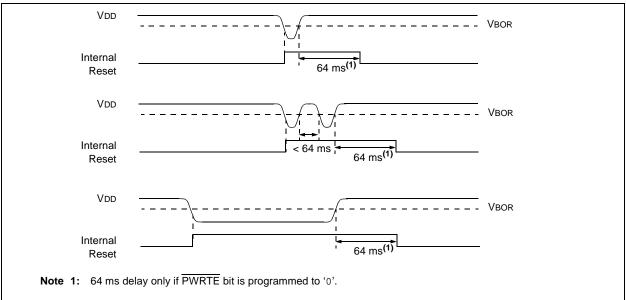

### 12.3.4 BROWN-OUT RESET (BOR)

The BOREN0 and BOREN1 bits in the Configuration Word register select one of three BOR modes. One mode has been added to allow control of the BOR enable for lower current during Sleep. By selecting BOREN<1:0> = 10, the BOR is automatically disabled in Sleep to conserve power and enabled on wake-up. See Register 12-1 for the Configuration Word definition.

A brown-out occurs when VDD falls below VBOR for greater than parameter TBOR (see Section 16.0 "Electrical Specifications"). The brown-out condition will reset the device. This will occur regardless of VDD slew rate. A Brown-out Reset may not occur if VDD falls below VBOR for less than parameter TBOR.

On any Reset (Power-on, Brown-out Reset, Watchdog timer, etc.), the chip will remain in Reset until VDD rises above VBOR (see Figure 12-3). If enabled, the Power-up Timer will be invoked by the Reset and keep the chip in Reset an additional 64 ms.

| Note: | The Power-up Timer is enabled by the |

|-------|--------------------------------------|

|       | PWRTE bit in the Configuration Word  |

|       | register.                            |

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

### FIGURE 12-3: BROWN-OUT SITUATIONS

### TABLE 12-5: INITIALIZATION CONDITION FOR REGISTERS (CONTINUED)(PIC12F615/617/HV615)

| Register              | Address | Power-on Reset | MCLR Reset<br>WDT Reset (Continued)<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep through<br>Interrupt<br>Wake-up from Sleep through<br>WDT Time-out (Continued) |

|-----------------------|---------|----------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| PMADRH <sup>(6)</sup> | 9Bh     | 000            | 000                                                                   | uuu                                                                                               |

| PMDATL <sup>(6)</sup> | 9Ch     | 0000 0000      | 0000 0000                                                             | uuuu uuuu                                                                                         |

| PMDATH <sup>(6)</sup> | 9Dh     | 00 0000        | 00 0000                                                               | uu uuuu                                                                                           |

| ADRESL <sup>(1)</sup> | 9Eh     | xxxx xxxx      | uuuu uuuu                                                             | uuuu uuuu                                                                                         |

| ANSEL                 | 9Fh     | -000 1111      | -000 1111                                                             | -uuu qqqq                                                                                         |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 12-6 for Reset value for specific condition.

5: If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

6: For PIC12F617 only.

### TABLE 12-6: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | Status<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 Ouuu          | uu               |

| WDT Reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | 10               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul 0uuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Interrupt Enable bit, GIE, is set, the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

### 12.6.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worstcase conditions (i.e., VDD = Min., Temperature = Max., Max. WDT prescaler) it may take several seconds before a WDT time out occurs.

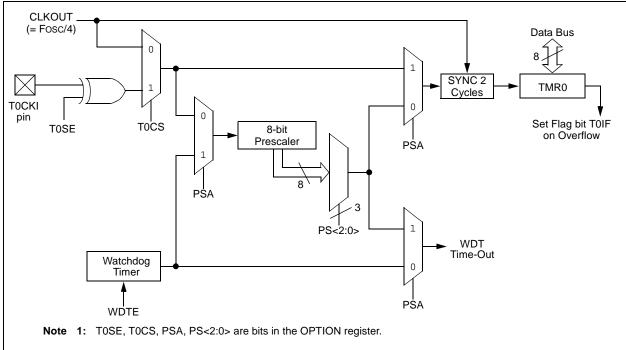

### FIGURE 12-2: WATCHDOG TIMER BLOCK DIAGRAM

### TABLE 12-8: WDT STATUS

| Conditions                                              | WDT                          |  |

|---------------------------------------------------------|------------------------------|--|

| WDTE = 0                                                |                              |  |

| CLRWDT Command                                          | Cleared                      |  |

| Oscillator Fail Detected                                | Cleared                      |  |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTRC, EXTCLK |                              |  |

| Exit Sleep + System Clock = XT, HS, LP                  | Cleared until the end of OST |  |

### TABLE 12-9: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

| Name       | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|--------|--------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| OPTION_REG | GPPU   | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111            | 1111 1111                       |

| CONFIG     | IOSCFS | CP     | MCLRE | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0 | —                    | —                               |

Legend: Shaded cells are not used by the Watchdog Timer.

**Note 1:** See Register 12-1 for operation of all Configuration Word register bits.

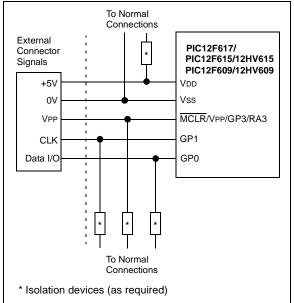

### 12.10 In-Circuit Serial Programming<sup>™</sup>

#### ThePIC12F609/615/617/12HV609/615

microcontrollers can be serially programmed while in the end application circuit. This is simply done with five connections for:

- clock

- data

- power

- ground

- · programming voltage

This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the GP0 and GP1 pins low, while raising the MCLR (VPP) pin from VIL to VIHH. See the *Memory Programming Specification* (DS41284) for more information. GP0 becomes the programming data and GP1 becomes the programming clock. Both GP0 and GP1 are Schmitt Trigger inputs in Program/Verify mode.

A typical In-Circuit Serial Programming connection is shown in Figure 12-10.

### FIGURE 12-10: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

Note: To erase the device VDD must be above the Bulk Erase VDD minimum given in the *Memory Programming Specification* (DS41284)

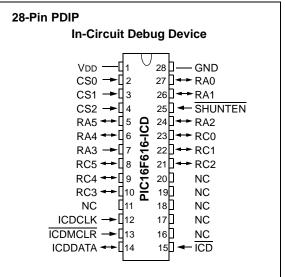

### 12.11 In-Circuit Debugger

Since in-circuit debugging requires access to three pins, MPLAB<sup>®</sup> ICD 2 development with an 14-pin device is not practical. A special 28-pin PIC12F609/615/617/12HV609/615 ICD device is used with MPLAB ICD 2 to provide separate clock, data and MCLR pins and frees all normally available pins to the user.

A special debugging adapter allows the ICD device to be used in place of a PIC12F609/615/617/12HV609/ 615 device. The debugging adapter is the only source of the ICD device.

When the ICD pin on the PIC12F609/615/617/ 12HV609/615 ICD device is held low, the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 12-10 shows which features are consumed by the background debugger.

| Resource       | Description                         |

|----------------|-------------------------------------|

| I/O pins       | ICDCLK, ICDDATA                     |

| Stack          | 1 level                             |

| Program Memory | Address 0h must be NOP<br>700h-7FFh |

For more information, see "*MPLAB*<sup>®</sup> *ICD 2 In-Circuit Debugger User's Guide*" (DS51331), available on Microchip's web site (www.microchip.com).

### FIGURE 12-11: 28 PIN ICD PINOUT

| ADDLW            | Add literal and W                                                                                                          |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |  |  |  |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the<br>W register. |  |  |  |  |  |  |

| 14.2 Instruction | Descriptions |

|------------------|--------------|

|------------------|--------------|

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BCF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ADDWF            | Add W and f                                                                                                                                                                        |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] ADDWF f,d                                                                                                                                                                |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                           |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |  |  |  |  |  |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BSF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND literal with W                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ANDLW k                                                                                                      |

| Operands:        | $0 \le k \le 255$                                                                                                      |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b' in register 'f' is '0', the next<br>instruction is discarded, and a NOP<br>is executed instead, making this a<br>two-cycle instruction. |

| ANDWF            | AND W with f                                                                                                                                                    |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] ANDWF f,d                                                                                                                                             |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |  |

### 16.2 DC Characteristics: PIC12F609/615/617-I (Industrial) PIC12F609/615/617-E (Extended)

| DC CHA | ARACTERISTICS                          |     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |       |       |     |                                     |  |

|--------|----------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-----|-------------------------------------|--|

| Param  | Device Characteristics                 | Min | Тур†                                                                                                                                                                                    | Мах   | Units |     | Conditions                          |  |

| No.    | Device Gilaracteristics                |     | וקעי                                                                                                                                                                                    | IVIAN | Units | Vdd | Note                                |  |

| D010   | Supply Current (IDD) <sup>(1, 2)</sup> |     | 13                                                                                                                                                                                      | 25    | μA    | 2.0 | Fosc = 32 kHz                       |  |

|        | PIC12F609/615/617                      |     | 19                                                                                                                                                                                      | 29    | μA    | 3.0 | LP Oscillator mode                  |  |

|        |                                        |     | 32                                                                                                                                                                                      | 51    | μA    | 5.0 |                                     |  |

| D011*  |                                        |     | 135                                                                                                                                                                                     | 225   | μA    | 2.0 | Fosc = 1 MHz                        |  |

|        |                                        |     | 185                                                                                                                                                                                     | 285   | μA    | 3.0 | XT Oscillator mode                  |  |

|        |                                        | _   | 300                                                                                                                                                                                     | 405   | μA    | 5.0 |                                     |  |

| D012   |                                        | —   | 240                                                                                                                                                                                     | 360   | μA    | 2.0 | Fosc = 4 MHz                        |  |

|        |                                        |     | 360                                                                                                                                                                                     | 505   | μA    | 3.0 | XT Oscillator mode                  |  |

|        |                                        |     | 0.66                                                                                                                                                                                    | 1.0   | mA    | 5.0 |                                     |  |

| D013*  |                                        |     | 75                                                                                                                                                                                      | 110   | μA    | 2.0 | Fosc = 1 MHz                        |  |

|        |                                        |     | 155                                                                                                                                                                                     | 255   | μA    | 3.0 | EC Oscillator mode                  |  |

|        |                                        |     | 345                                                                                                                                                                                     | 530   | μA    | 5.0 |                                     |  |

| D014   |                                        |     | 185                                                                                                                                                                                     | 255   | μA    | 2.0 | Fosc = 4 MHz                        |  |

|        |                                        |     | 325                                                                                                                                                                                     | 475   | μA    | 3.0 | EC Oscillator mode                  |  |

|        |                                        |     | 0.665                                                                                                                                                                                   | 1.0   | mA    | 5.0 |                                     |  |

| D016*  |                                        |     | 245                                                                                                                                                                                     | 340   | μA    | 2.0 | Fosc = 4 MHz                        |  |

|        |                                        |     | 360                                                                                                                                                                                     | 485   | μA    | 3.0 | INTOSC mode                         |  |

|        |                                        |     | 0.620                                                                                                                                                                                   | 0.845 | mA    | 5.0 |                                     |  |

| D017   |                                        |     | 395                                                                                                                                                                                     | 550   | μA    | 2.0 | Fosc = 8 MHz                        |  |

|        |                                        |     | 0.620                                                                                                                                                                                   | 0.850 | mA    | 3.0 | INTOSC mode                         |  |

|        |                                        |     | 1.2                                                                                                                                                                                     | 1.6   | mA    | 5.0 |                                     |  |

| D018   |                                        |     | 175                                                                                                                                                                                     | 235   | μA    | 2.0 | Fosc = 4 MHz                        |  |

|        |                                        |     | 285                                                                                                                                                                                     | 390   | μA    | 3.0 | EXTRC mode <sup>(3)</sup>           |  |

|        |                                        | —   | 530                                                                                                                                                                                     | 750   | μA    | 5.0 |                                     |  |

| D019   |                                        | —   | 2.2                                                                                                                                                                                     | 3.1   | mA    | 4.5 | Fosc = 20 MHz<br>HS Oscillator mode |  |

|        |                                        |     | 2.8                                                                                                                                                                                     | 3.35  | mA    | 5.0 |                                     |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-torail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in KOhms (KΩ).

### 16.8 DC Characteristics: PIC12F609/615/617/12HV609/615-I (Industrial) PIC12F609/615/617/12HV609/615-E (Extended)

| DC CHARACTERISTICS |      |                                          | -              |          |          | nless otherwise stated)<br>≤ TA ≤ +85°C for industrial<br>≤ TA ≤ +125°C for extended |                                                                    |  |

|--------------------|------|------------------------------------------|----------------|----------|----------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|

| Param<br>No.       | Sym  | Characteristic                           | Min            | Тур†     | Max      | Units                                                                                | Conditions                                                         |  |

|                    | VIL  | Input Low Voltage                        |                |          |          |                                                                                      |                                                                    |  |

|                    |      | I/O port:                                |                |          |          |                                                                                      |                                                                    |  |

| D030               |      | with TTL buffer                          | Vss            | —        | 0.8      | V                                                                                    | $4.5V \leq V\text{DD} \leq 5.5V$                                   |  |

| D030A              |      |                                          | Vss            | —        | 0.15 Vdd | V                                                                                    | $2.0V \leq V \text{DD} \leq 4.5 \text{V}$                          |  |

| D031               |      | with Schmitt Trigger buffer              | Vss            | _        | 0.2 Vdd  | V                                                                                    | $2.0V \le VDD \le 5.5V$                                            |  |

| D032               |      | MCLR, OSC1 (RC mode)                     | Vss            | _        | 0.2 Vdd  | V                                                                                    | (NOTE 1)                                                           |  |

| D033               |      | OSC1 (XT and LP modes)                   | Vss            | _        | 0.3      | V                                                                                    |                                                                    |  |

| D033A              |      | OSC1 (HS mode)                           | Vss            | _        | 0.3 Vdd  | V                                                                                    |                                                                    |  |

|                    | Vih  | Input High Voltage                       |                |          |          |                                                                                      |                                                                    |  |

|                    |      | I/O ports:                               |                | _        |          |                                                                                      |                                                                    |  |

| D040               |      | with TTL buffer                          | 2.0            | _        | Vdd      | V                                                                                    | $4.5V \leq V \text{DD} \leq 5.5V$                                  |  |

| D040A              |      |                                          | 0.25 VDD + 0.8 | —        | Vdd      | V                                                                                    | $2.0V \leq V \text{DD} \leq 4.5 \text{V}$                          |  |

| D041               |      | with Schmitt Trigger buffer              | 0.8 Vdd        | —        | Vdd      | V                                                                                    | $2.0V \leq V \text{DD} \leq 5.5 \text{V}$                          |  |

| D042               |      | MCLR                                     | 0.8 Vdd        | —        | Vdd      | V                                                                                    |                                                                    |  |

| D043               |      | OSC1 (XT and LP modes)                   | 1.6            | —        | Vdd      | V                                                                                    |                                                                    |  |

| D043A              |      | OSC1 (HS mode)                           | 0.7 Vdd        | _        | Vdd      | V                                                                                    |                                                                    |  |

| D043B              |      | OSC1 (RC mode)                           | 0.9 Vdd        | —        | Vdd      | V                                                                                    | (NOTE 1)                                                           |  |

|                    | lı∟  | Input Leakage Current <sup>(2,3)</sup>   |                |          |          |                                                                                      |                                                                    |  |

| D060               |      | I/O ports                                | _              | ± 0.1    | ± 1      | μA                                                                                   | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance                   |  |

| D061               |      | GP3/MCLR <sup>(3,4)</sup>                | —              | $\pm0.7$ | ± 5      | μΑ                                                                                   | $V\text{SS} \leq V\text{PIN} \leq V\text{DD}$                      |  |

| D063               |      | OSC1                                     | _              | ± 0.1    | ± 5      | μΑ                                                                                   | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration |  |

| D070*              | IPUR | GPIO Weak Pull-up Current <sup>(5)</sup> | 50             | 250      | 400      | μΑ                                                                                   | VDD = 5.0V, VPIN = VSS                                             |  |

|                    | Vol  | Output Low Voltage                       | _              | _        | 0.6      | V                                                                                    | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                       |  |

| D080               |      | I/O ports                                | —              | -        | 0.6      | V                                                                                    | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                        |  |

|                    | Vон  | Output High Voltage                      | VDD - 0.7      | —        | —        | V                                                                                    | IOH = -2.5mA, VDD = 4.5V,<br>-40°С to +125°С                       |  |

| D090               |      | I/O ports <sup>(2)</sup>                 | Vdd - 0.7      | -        | -        | V                                                                                    | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                       |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: This specification applies to GP3/MCLR configured as GP3 with the internal weak pull-up disabled.

5: This specification applies to all weak pull-up pins, including the weak pull-up found on GP3/MCLR. When GP3/MCLR is configured as MCLR reset pin, the weak pull-up is always enabled.

6: Applies to PIC12F617 only.

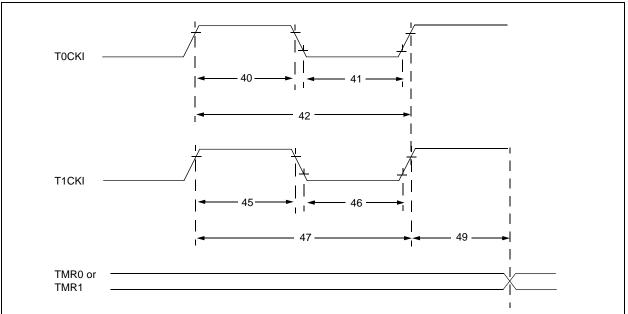

#### **FIGURE 16-8:** TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

#### TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS TABLE 16-5:

| Param<br>No. | Sym                                       |                                     | Characteristic                                              |                                           | Min                                       | Тур†   | Max    | Units                              | Conditions                         |

|--------------|-------------------------------------------|-------------------------------------|-------------------------------------------------------------|-------------------------------------------|-------------------------------------------|--------|--------|------------------------------------|------------------------------------|

| 40*          | T⊤0H                                      | T0CKI High F                        | TOCKI High Pulse Width No Prescaler<br>With Prescaler       |                                           | 0.5 TCY + 20                              | _      | _      | ns                                 |                                    |

|              |                                           |                                     |                                                             |                                           | 10                                        | —      | _      | ns                                 |                                    |

| 41*          | TT0L                                      | T0CKI Low Pulse Width               |                                                             | No Prescaler                              | 0.5 TCY + 20                              | —      | _      | ns                                 |                                    |

|              |                                           |                                     |                                                             | With Prescaler                            | 10                                        | —      | —      | ns                                 |                                    |

| 42*          | Тт0Р                                      | T0CKI Period                        | 1                                                           |                                           | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —      | _      | ns                                 | N = prescale value<br>(2, 4,, 256) |

| 45*          | TT1H                                      | T1CKI High                          | Synchronous, No Prescaler                                   |                                           | 0.5 TCY + 20                              | —      | —      | ns                                 |                                    |

|              | Time                                      | Synchronous,<br>with Prescaler      |                                                             | 15                                        | —                                         | _      | ns     |                                    |                                    |

|              |                                           | Asynchronous                        |                                                             |                                           | 30                                        | —      | _      | ns                                 |                                    |

| 46*          | TT1L                                      | T1CKI Low Synchronous, No Prescaler |                                                             | 0.5 TCY + 20                              | —                                         | _      | ns     |                                    |                                    |

| Time         |                                           | Time                                | Synchronous,<br>with Prescaler                              |                                           | 15                                        | —      | _      | ns                                 |                                    |

|              |                                           |                                     | Asynchronous                                                |                                           | 30                                        | —      | _      | ns                                 |                                    |

| 47*          | 7* TT1P T1CKI Input Synchronous<br>Period |                                     |                                                             | Greater of:<br>30 or <u>Tcy + 40</u><br>N |                                           | _      | ns     | N = prescale value<br>(1, 2, 4, 8) |                                    |

|              |                                           |                                     | Asynchronous                                                |                                           | 60                                        | —      | _      | ns                                 |                                    |

| 48           | F⊤1                                       |                                     | ator Input Frequency Range<br>abled by setting bit T10SCEN) |                                           | -                                         | 32.768 | —      | kHz                                |                                    |

| 49*          | TCKEZTMR1                                 | Delay from E<br>Increment           | xternal Clock E                                             | dge to Timer                              | 2 Tosc                                    | —      | 7 Tosc | —                                  | Timers in Sync<br>mode             |

Standard Operating Conditions (unless otherwise stated)

These parameters are characterized but not tested.

t Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

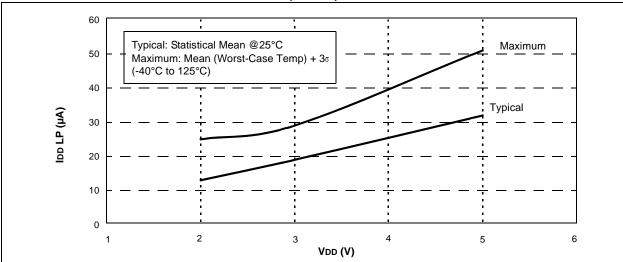

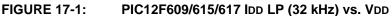

# 17.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where s is a standard deviation, over each temperature range.

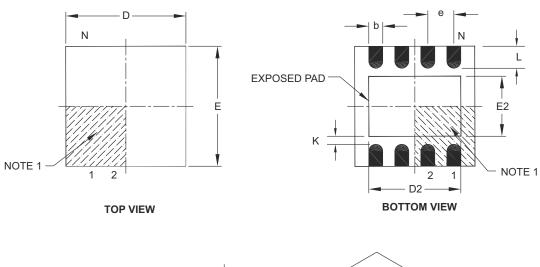

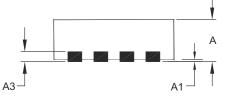

### 8-Lead Plastic Dual Flat, No Lead Package (MF) – 3x3x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            | MILLIMETERS |      |      |

|------------------------|------------------|-------------|------|------|

|                        | Dimension Limits |             | NOM  | MAX  |

| Number of Pins         | N                | 8           |      |      |

| Pitch                  | е                | 0.65 BSC    |      |      |

| Overall Height         | А                | 0.80        | 0.90 | 1.00 |

| Standoff               | A1               | 0.00        | 0.02 | 0.05 |

| Contact Thickness      | A3               | 0.20 REF    |      |      |

| Overall Length         | D                | 3.00 BSC    |      |      |

| Exposed Pad Width      | E2               | 0.00        | -    | 1.60 |

| Overall Width          | E                | 3.00 BSC    |      |      |

| Exposed Pad Length     | D2               | 0.00        | -    | 2.40 |

| Contact Width          | b                | 0.25        | 0.30 | 0.35 |

| Contact Length         | L                | 0.20        | 0.30 | 0.55 |

| Contact-to-Exposed Pad | K                | 0.20        | -    | -    |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-062B