# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-VDFN Exposed Pad                                                        |

| Supplier Device Package    | 8-DFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f609t-i-md |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, GPIO change and external GP2/INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | GPIE  | T0IF  | INTF  | GPIF  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 7 | GIE: Global Interrupt Enable bit<br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts                                                                                        |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                      |

| bit 5 | <b>TolE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                    |

| bit 4 | INTE: GP2/INT External Interrupt Enable bit<br>1 = Enables the GP2/INT external interrupt<br>0 = Disables the GP2/INT external interrupt                                                      |

| bit 3 | <b>GPIE:</b> GPIO Change Interrupt Enable bit <sup>(1)</sup><br>1 = Enables the GPIO change interrupt<br>0 = Disables the GPIO change interrupt                                               |

| bit 2 | <b>T0IF:</b> Timer0 Overflow Interrupt Flag bit <sup>(2)</sup><br>1 = Timer0 register has overflowed (must be cleared in software)<br>0 = Timer0 register did not overflow                    |

| bit 1 | INTF: GP2/INT External Interrupt Flag bit<br>1 = The GP2/INT external interrupt occurred (must be cleared in software)<br>0 = The GP2/INT external interrupt did not occur                    |

| bit 0 | <b>GPIF:</b> GPIO Change Interrupt Flag bit<br>1 = When at least one of the GPIO <5:0> pins changed state (must be cleared in software)<br>0 = None of the GPIO <5:0> pins have changed state |

**Note 1:** IOC register must also be enabled.

2: T0IF bit is set when TMR0 rolls over. TMR0 is unchanged on Reset and should be initialized before clearing T0IF bit.

An example of the complete four-word write sequence is shown in Example 3-2. The initial address is loaded into the PMADRH and PMADRL register pair; the eight words of data are loaded using indirect addressing.

#### EXAMPLE 3-2: WRITING TO FLASH PROGRAM MEMORY

```

*****

; This write routine assumes the following:

A valid starting address (the least significant bits = '00')

;

is loaded in ADDRH:ADDRL

;

;

ADDRH, ADDRL and DATADDR are all located in data memory

;

BANKSEL PMADRH

MOVF

ADDRH,W

; Load initial address

MOVWF

PMADRH

MOVF

ADDRL,W

MOVWF

PMADRL

;

DATAADDR,W ; Load initial data address

MOVF

MOVWF

FSR

LOOP

MOVF

INDF,W

; Load first data byte into lower

;

MOVWF PMDATL

; Next byte

INCE

FSR,F

; Load second data byte into upper

MOVF

INDF,W

MOVWF

PMDATH

INCF

FSR,F

BANKSEL PMCON1

PMCON1,WREN ; Enable writes

BSF

BCF

INTCON,GIE ; Disable interrupts (if using)

BTFSC INTCON, GIE ; See AN576

GOTO

$-2

Required Sequence

;

MOVLW

55h

; Start of required write sequence:

MOVWF

PMCON2

; Write 55h

MOVLW

0AAh

PMCON2

; Write OAAh

MOVWF

PMCON1,WR ; Set WR bit to begin write

BSF

NOP

; Required to transfer data to the buffer

NOP

; registers

PMCON1,WREN ; Disable writes

BCF

BSF

INTCON,GIE ; Enable interrupts (comment out if not using interrupts)

BANKSEL PMADRL

MOVF

PMADRL, W

INCF

PMADRL, F

; Increment address

; Indicates when sixteen words have been programmed

ANDLW

0x03

SUBLW

0x03

; 0x0F = 16 words

; 0x0B = 12 words

; 0x07 = 8 words

; 0x03 = 4 words

; Exit on a match,

BTFSS

STATUS, Z

GOTO

LOOP

; Continue if more data needs to be written

```

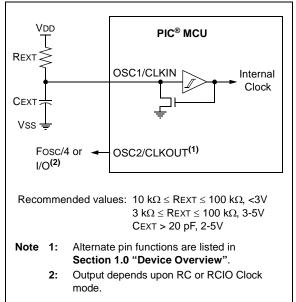

### 4.3.4 EXTERNAL RC MODES

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required. There are two modes: RC and RCIO.

In RC mode, the RC circuit connects to OSC1. OSC2/ CLKOUT outputs the RC oscillator frequency divided by 4. This signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements. Figure 4-5 shows the external RC mode connections.

FIGURE 4-5: EXTERNAL RC MODES

In RCIO mode, the RC circuit is connected to OSC1. OSC2 becomes an additional general purpose I/O pin.

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- threshold voltage variation

- component tolerances

- packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

### 4.4 Internal Clock Modes

The Oscillator module provides a selectable system clock source of either 4 MHz or 8 MHz. The selectable frequency is configured through the IOSCFS bit of the Configuration Word.

The frequency of the internal oscillator can be trimmed with a calibration value in the OSCTUNE register.

#### 4.4.1 INTOSC AND INTOSCIO MODES

The INTOSC and INTOSCIO modes configure the internal oscillators as the system clock source when the device is programmed using the oscillator selection or the FOSC<2:0> bits in the Configuration Word register (CONFIG). See Section 12.0 "Special Features of the CPU" for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT outputs the selected internal oscillator frequency divided by 4. The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

In **INTOSCIO** mode, OSC1/CLKIN and OSC2/CLKOUT are available for general purpose I/O.

NOTES:

NOTES:

### 9.10 Comparator Voltage Reference

The Comparator Voltage Reference module provides an internally generated voltage reference for the comparators. The following features are available:

- Independent from Comparator operation

- 16-level voltage range

- Output clamped to Vss

- Ratiometric with VDD

- Fixed Reference (0.6)

The VRCON register (Register 9-3) controls the Voltage Reference module shown in Register 9-6.

#### 9.10.1 INDEPENDENT OPERATION

The comparator voltage reference is independent of the comparator configuration. Setting the VREN bit of the VRCON register will enable the voltage reference.

#### 9.10.2 OUTPUT VOLTAGE SELECTION

The CVREF voltage reference has 2 ranges with 16 voltage levels in each range. Range selection is controlled by the VRR bit of the VRCON register. The 16 levels are set with the VR<3:0> bits of the VRCON register.

The CVREF output voltage is determined by the following equations:

#### EQUATION 9-1: CVREF OUTPUT VOLTAGE

VRR = 1 (low range):  $CVREF = (VR < 3:0 > /24) \times VDD$  VRR = 0 (high range):  $CVREF = (VDD/4) + (VR < 3:0 > \times VDD/32)$

The full range of Vss to VDD cannot be realized due to the construction of the module. See Figure 9-6.

#### 9.10.3 OUTPUT CLAMPED TO Vss

The CVREF output voltage can be set to Vss with no power consumption by configuring VRCON as follows:

#### • FVREN = 0

This allows the comparator to detect a zero-crossing while not consuming additional CVREF module current.

#### 9.10.4 OUTPUT RATIOMETRIC TO VDD

The comparator voltage reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 16.0 "Electrical Specifications"**.

#### 9.10.5 FIXED VOLTAGE REFERENCE

The fixed voltage reference is independent of VDD, with a nominal output voltage of 0.6V. This reference can be enabled by setting the FVREN bit of the VRCON register to '1'. This reference is always enabled when the HFINTOSC oscillator is active.

#### 9.10.6 FIXED VOLTAGE REFERENCE STABILIZATION PERIOD

When the Fixed Voltage Reference module is enabled, it will require some time for the reference and its amplifier circuits to stabilize. The user program must include a small delay routine to allow the module to settle. See **Section 16.0 "Electrical Specifications"** for the minimum delay requirement.

#### 9.10.7 VOLTAGE REFERENCE SELECTION

Multiplexers on the output of the Voltage Reference module enable selection of either the CVREF or fixed voltage reference for use by the comparators.

Setting the CMVREN bit of the VRCON register enables current to flow in the CVREF voltage divider and selects the CVREF voltage for use by the Comparator. Clearing the CMVREN bit selects the fixed voltage for use by the Comparator.

When the CMVREN bit is cleared, current flow in the CVREF voltage divider is disabled minimizing the power drain of the voltage reference peripheral.

#### 10.2.7 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

#### REGISTER 10-1: ADCON0: A/D CONTROL REGISTER 0

| R/W-0      | ) R/W-0                                                                                                                                                                                                                                                     | U-0                                                                      | R/W-0                           | R/W-0            | R/W-0                          | R/W-0                               | R/W-0 |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------|------------------|--------------------------------|-------------------------------------|-------|--|--|

| ADFM       | 1 VCFG                                                                                                                                                                                                                                                      | —                                                                        | CHS2                            | CHS1             | CHS0                           | GO/DONE                             | ADON  |  |  |

| bit 7      |                                                                                                                                                                                                                                                             |                                                                          |                                 |                  |                                |                                     | bit 0 |  |  |

| Legend:    |                                                                                                                                                                                                                                                             |                                                                          |                                 |                  |                                |                                     |       |  |  |

| R = Read   | able bit                                                                                                                                                                                                                                                    | W = Writable                                                             | bit                             | U = Unimpler     | mented bit, rea                | ad as '0'                           |       |  |  |

| -n = Value | e at POR                                                                                                                                                                                                                                                    | '1' = Bit is se                                                          | t                               | '0' = Bit is cle | ared                           | x = Bit is unkn                     | own   |  |  |

| bit 7      | <b>ADFM:</b> A/D<br>1 = Right ju:<br>0 = Left just                                                                                                                                                                                                          |                                                                          | sult Format Se                  | elect bit        |                                |                                     |       |  |  |

| bit 6      | <b>VCFG:</b> Volta<br>1 = VREF pir<br>0 = VDD                                                                                                                                                                                                               | age Reference I                                                          | bit                             |                  |                                |                                     |       |  |  |

| bit 5      | Unimpleme                                                                                                                                                                                                                                                   | nted: Read as                                                            | '0'                             |                  |                                |                                     |       |  |  |

| bit 4-2    | 000 = Chan<br>001 = Chan<br>010 = Chan<br>011 = Chan<br>100 = CVRE<br>101 = 0.6V<br>110 = 1.2V                                                                                                                                                              | Reference                                                                |                                 |                  |                                |                                     |       |  |  |

| bit 1      | 1 = A/D con<br>This bit i                                                                                                                                                                                                                                   | A/D Conversior<br>version cycle in<br>is automatically<br>version comple | progress. Set<br>cleared by har | rdware when th   | ts an A/D con<br>e A/D convers | version cycle.<br>sion has complete | ed.   |  |  |

| bit 0      | <b>ADON:</b> ADO<br>1 = ADC is 0                                                                                                                                                                                                                            | C Enable bit                                                             |                                 |                  |                                |                                     |       |  |  |

| Note 1:    | When the CHS<2:0> bits change to select the 1.2V or 0.6V reference, the reference output voltage will have a transient. If the Comparator module uses this 0.6V reference voltage, the comparator output may momentarily change state due to the transient. |                                                                          |                                 |                  |                                |                                     |       |  |  |

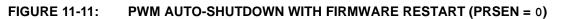

### 11.0 ENHANCED CAPTURE/ COMPARE/PWM (WITH AUTO-SHUTDOWN AND DEAD BAND) MODULE (PIC12F615/617/ HV615 ONLY)

The Enhanced Capture/Compare/PWM module is a peripheral which allows the user to time and control different events. In Capture mode, the peripheral allows the timing of the duration of an event.The Compare mode allows the user to trigger an external

event when a predetermined amount of time has expired. The PWM mode can generate a Pulse-Width Modulated signal of varying frequency and duty cycle.

Table 11-1 shows the timer resources required by the ECCP module.

#### TABLE 11-1: ECCP MODE – TIMER RESOURCES REQUIRED

| ECCP Mode | Timer Resource |

|-----------|----------------|

| Capture   | Timer1         |

| Compare   | Timer1         |

| PWM       | Timer2         |

### REGISTER 11-1: CCP1CON: ENHANCED CCP1 CONTROL REGISTER

| R/W-0         | U-0                                                                                                                                                                                                                               | R/W-0                                                                                                                                                           | R/W-0                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                | R/W-0                               | R/W-0                               | R/W-0                              |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------|------------------------------------|

| P1M           |                                                                                                                                                                                                                                   | DC1B1                                                                                                                                                           | DC1B0                                                                                                                                                                                                                               | CCP1M3                                                                                                                                                               | CCP1M2                              | CCP1M1                              | CCP1M0                             |

| bit 7         |                                                                                                                                                                                                                                   |                                                                                                                                                                 |                                                                                                                                                                                                                                     |                                                                                                                                                                      | •                                   |                                     | bit 0                              |

|               |                                                                                                                                                                                                                                   |                                                                                                                                                                 |                                                                                                                                                                                                                                     |                                                                                                                                                                      |                                     |                                     |                                    |

| Legend:       | 1.5                                                                                                                                                                                                                               |                                                                                                                                                                 |                                                                                                                                                                                                                                     |                                                                                                                                                                      |                                     |                                     |                                    |

| R = Readable  |                                                                                                                                                                                                                                   | W = Writable k                                                                                                                                                  | Dit                                                                                                                                                                                                                                 |                                                                                                                                                                      | nented bit, read                    |                                     |                                    |

| -n = Value at | POR                                                                                                                                                                                                                               | '1' = Bit is set                                                                                                                                                |                                                                                                                                                                                                                                     | '0' = Bit is clea                                                                                                                                                    | ared                                | x = Bit is unkr                     | nown                               |

| bit 7         | <u>lf CCP1M&lt;3:2</u><br>x = P1A assig<br><u>lf CCP1M&lt;3:2</u><br>0 = Single ou                                                                                                                                                | 2 <u>&gt; = 11:</u><br>itput; P1A modu                                                                                                                          | <u>:</u><br>e/Compare in<br>ulated; P1B as                                                                                                                                                                                          | out; P1B assign<br>signed as port p<br>d with dead-bar                                                                                                               | oins                                |                                     |                                    |

| bit 6         | Unimplemen                                                                                                                                                                                                                        | ted: Read as '                                                                                                                                                  | 0'                                                                                                                                                                                                                                  |                                                                                                                                                                      |                                     |                                     |                                    |

| bit 5-4       | <u>Capture mode</u><br>Unused.<br><u>Compare moc</u><br>Unused.<br><u>PWM mode:</u>                                                                                                                                               | <u>le:</u>                                                                                                                                                      | Ţ                                                                                                                                                                                                                                   | uty cycle. The ei                                                                                                                                                    | ight MSbs are t                     | found in CCPR1                      | IL.                                |

| bit 3-0       | 0000 =Captur<br>0001 =Unuse<br>0010 =Compa<br>0011 =Unuse<br>0100 =Captur<br>0101 =Captur<br>0111 =Captur<br>0111 =Captur<br>1000 =Compa<br>1001 =Compa<br>1011 =Compa<br>1011 =Compa<br>1011 =CMPA<br>1010 =PWM 1<br>1101 =PWM 1 | are mode, tóggl<br>d (reserved)<br>re mode, every<br>re mode, every<br>re mode, every<br>re mode, every<br>are mode, set o<br>are mode, clear<br>are mode, gene | /M off (resets<br>le output on m<br>falling edge<br>4th rising edg<br>16th rising ed<br>utput on matc<br>output on matc<br>output on matc<br>rate software i<br>er special ever<br>the ADC modu<br>ve-high; P1B a<br>ve-high; P1B a | atch (CCP1IF b<br>ge<br>h (CCP1IF bit is<br>tch (CCP1IF bit is<br>tch (CCP1IF bit<br>nt (CCP1IF bit is<br>ile is enabled)<br>active-high<br>active-low<br>ctive-high | s set)<br>is set)<br>ch (CCP1IF bit | is set, CCP1 pir<br>sets TMR1 or TI | n is unaffected)<br>MR2 and starts |

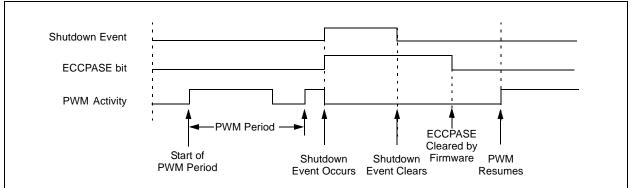

#### 11.4.5 AUTO-RESTART MODE

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PRSEN bit in the PWM1CON register.

If auto-restart is enabled, the ECCPASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the ECCPASE bit will be cleared via hardware and normal operation will resume.

#### FIGURE 11-12: PWM AUTO-SHUTDOWN WITH AUTO-RESTART ENABLED (PRSEN = 1)

| Register   | Address | s Power-on<br>Reset Brown-out Reset <sup>(1)</sup> |                      | Wake-up from Sleep through<br>Interrupt<br>Wake-up from Sleep through<br>WDT Time-out |

|------------|---------|----------------------------------------------------|----------------------|---------------------------------------------------------------------------------------|

| W          | _       | xxxx xxxx                                          | uuuu uuuu            | uuuu uuuu                                                                             |

| INDF       | 00h/80h | xxxx xxxx                                          | XXXX XXXX            | uuuu uuuu                                                                             |

| TMR0       | 01h     | xxxx xxxx                                          | uuuu uuuu            | uuuu uuuu                                                                             |

| PCL        | 02h/82h | 0000 0000                                          | 0000 0000            | PC + 1 <sup>(3)</sup>                                                                 |

| STATUS     | 03h/83h | 0001 1xxx                                          | 000q quuu <b>(4)</b> | uuuq quuu <sup>(4)</sup>                                                              |

| FSR        | 04h/84h | xxxx xxxx                                          | uuuu uuuu            | uuuu uuuu                                                                             |

| GPIO       | 05h     | x0 x000                                            | u0 u000              | uu uuuu                                                                               |

| PCLATH     | 0Ah/8Ah | 0 0000                                             | 0 0000               | u uuuu                                                                                |

| INTCON     | 0Bh/8Bh | 0000 0000                                          | 0000 0000            | uuuu uuuu <b>(2)</b>                                                                  |

| PIR1       | 0Ch     | 00                                                 | 00                   | uu <b>(2)</b>                                                                         |

| TMR1L      | 0Eh     | xxxx xxxx                                          | uuuu uuuu            | uuuu uuuu                                                                             |

| TMR1H      | 0Fh     | xxxx xxxx                                          | uuuu uuuu            | uuuu uuuu                                                                             |

| T1CON      | 10h     | 0000 0000                                          | uuuu uuuu            | -uuu uuuu                                                                             |

| VRCON      | 19h     | 0-00 0000                                          | 0-00 0000            | u-uu uuuu                                                                             |

| CMCON0     | 1Ah     | 0000 -0-0                                          | 0000 -0-0            | uuuu -u-u                                                                             |

| CMCON1     | 1Ch     | 0 0-10                                             | 0 0-10               | u u-qu                                                                                |

| OPTION_REG | 81h     | 1111 1111                                          | 1111 1111            | uuuu uuuu                                                                             |

| TRISIO     | 85h     | 11 1111                                            | 11 1111              | uu uuuu                                                                               |

| PIE1       | 8Ch     | 00                                                 | 00                   | uu                                                                                    |

| PCON       | 8Eh     | 0x                                                 | (1, 5)               | uu                                                                                    |

| OSCTUNE    | 90h     | 0 0000                                             | u uuuu               | u uuuu                                                                                |

| WPU        | 95h     | 11 -111                                            | 11 -111              | uu -uuu                                                                               |

| IOC        | 96h     | 00 0000                                            | 00 0000              | uu uuuu                                                                               |

| ANSEL      | 9Fh     | 1-11                                               | 1-11                 | d-dd                                                                                  |

### TABLE 12-4: INITIALIZATION CONDITION FOR REGISTERS (PIC12F609/HV609)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

**3:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 12-6 for Reset value for specific condition.

5: If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

NOTES:

NOTES:

### 16.6 DC Characteristics: PIC12HV609/615 - I (Industrial)

| DC CHA                       | ARACTERISTICS                                     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |       |       |     |                                               |  |  |

|------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|-----|-----------------------------------------------|--|--|

| Param Device Characteristics |                                                   | Min                                                                                                                                | Тур† | Мах   | Units |     | Conditions                                    |  |  |

| No.                          | Device Characteristics                            | IVIIII                                                                                                                             | турт | IVIAX | Units | Vdd | Note                                          |  |  |

| D020                         | Power-down Base<br>Current (IPD) <sup>(2,3)</sup> | —                                                                                                                                  | 135  | 200   | μΑ    | 2.0 | WDT, BOR, Comparator, VREF and T1OSC disabled |  |  |

|                              |                                                   | _                                                                                                                                  | 210  | 280   | μΑ    | 3.0 | 7                                             |  |  |

|                              | PIC12HV609/615                                    | _                                                                                                                                  | 260  | 350   | μΑ    | 4.5 |                                               |  |  |

| D021                         |                                                   | —                                                                                                                                  | 135  | 200   | μΑ    | 2.0 | WDT Current <sup>(1)</sup>                    |  |  |

|                              |                                                   | _                                                                                                                                  | 210  | 285   | μΑ    | 3.0 |                                               |  |  |

|                              |                                                   | _                                                                                                                                  | 265  | 360   | μΑ    | 4.5 | 7                                             |  |  |

| D022                         |                                                   | —                                                                                                                                  | 215  | 285   | μΑ    | 3.0 | BOR Current <sup>(1)</sup>                    |  |  |

|                              |                                                   | _                                                                                                                                  | 265  | 360   | μΑ    | 4.5 | 7                                             |  |  |

| D023                         |                                                   | —                                                                                                                                  | 185  | 270   | μΑ    | 2.0 | Comparator Current <sup>(1)</sup> , single    |  |  |

|                              |                                                   | —                                                                                                                                  | 265  | 350   | μΑ    | 3.0 | comparator enabled                            |  |  |

|                              |                                                   | —                                                                                                                                  | 320  | 430   | μΑ    | 4.5 |                                               |  |  |

| D024                         |                                                   |                                                                                                                                    | 165  | 235   | μΑ    | 2.0 | CVREF Current <sup>(1)</sup> (high range)     |  |  |

|                              |                                                   | _                                                                                                                                  | 255  | 330   | μΑ    | 3.0 |                                               |  |  |

|                              |                                                   | —                                                                                                                                  | 330  | 430   | μΑ    | 4.5 |                                               |  |  |

| D025*                        |                                                   | —                                                                                                                                  | 175  | 245   | μΑ    | 2.0 | CVREF Current <sup>(1)</sup> (low range)      |  |  |

|                              |                                                   | —                                                                                                                                  | 275  | 350   | μΑ    | 3.0 |                                               |  |  |

|                              |                                                   | —                                                                                                                                  | 355  | 450   | μΑ    | 4.5 |                                               |  |  |

| D026                         |                                                   | _                                                                                                                                  | 140  | 205   | μΑ    | 2.0 | T1OSC Current <sup>(1)</sup> , 32.768 kHz     |  |  |

|                              |                                                   | _                                                                                                                                  | 220  | 290   | μΑ    | 3.0 |                                               |  |  |

|                              |                                                   | —                                                                                                                                  | 270  | 360   | μA    | 4.5 |                                               |  |  |

| D027                         |                                                   | _                                                                                                                                  | 210  | 280   | μΑ    | 3.0 | A/D Current <sup>(1)</sup> , no conversion in |  |  |

|                              |                                                   | —                                                                                                                                  | 260  | 350   | μΑ    | 4.5 | progress                                      |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 4.5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral  $\Delta$  current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

3: Shunt regulator is always on and always draws operating current.

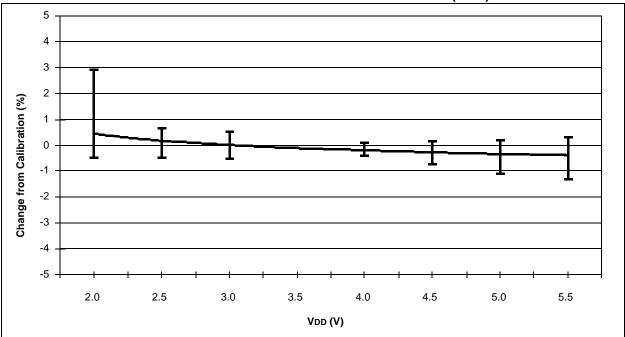

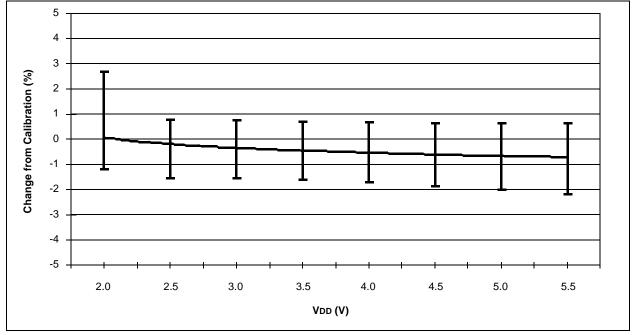

#### TABLE 16-2: OSCILLATOR PARAMETERS

|              | Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                                        |                    |      |      |      |                                                                                                 |                                                                                                                                                                                  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------|------|------|------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No. | Sym                                                                                                                  | Characteristic                                         | Freq.<br>Tolerance | Min  | Тур† | Max  | Units                                                                                           | Conditions                                                                                                                                                                       |  |  |

| OS06         | Twarm                                                                                                                | Internal Oscillator Switch when running <sup>(3)</sup> | —                  |      |      | 2    | Tosc                                                                                            | Slowest clock                                                                                                                                                                    |  |  |

| OS07 INTosc  |                                                                                                                      | Internal Calibrated                                    | ±1%                | 3.96 | 4.0  | 4.04 | MHz                                                                                             | $VDD = 3.5V, T_A = 25^{\circ}C$                                                                                                                                                  |  |  |

|              | INTOSC Frequency <sup>(2)</sup><br>(4MHz)                                                                            | ±2%                                                    | 3.92               | 4.0  | 4.08 | MHz  | $\begin{array}{l} 2.5V \leq VDD \leq 5.5V, \\ 0^{\circ}C \leq TA \leq +85^{\circ}C \end{array}$ |                                                                                                                                                                                  |  |  |

|              |                                                                                                                      |                                                        | ±5%                | 3.80 | 4.0  | 4.2  | MHz                                                                                             | $2.0V \le VDD \le 5.5V$ ,<br>-40°C $\le$ TA $\le$ +85°C (Ind.),<br>-40°C $\le$ TA $\le$ +125°C (Ext.)                                                                            |  |  |

| OS08         | INTosc                                                                                                               | Internal Calibrated                                    | ±1%                | 7.92 | 8.0  | 8.08 | MHz                                                                                             | VDD = 3.5V, T <sub>A</sub> = 25°C                                                                                                                                                |  |  |

|              |                                                                                                                      | INTOSC Frequency <sup>(2)</sup><br>(8MHz)              | ±2%                | 7.84 | 8.0  | 8.16 | MHz                                                                                             | $\begin{array}{l} 2.5V \leq VDD \leq 5.5V, \\ 0^{\circ}C \leq TA \leq +85^{\circ}C \end{array}$                                                                                  |  |  |

|              |                                                                                                                      |                                                        | ±5%                | 7.60 | 8.0  | 8.40 | MHz                                                                                             | $\begin{array}{l} 2.0V \leq V D D \leq 5.5 V, \\ -40^{\circ}C \leq T A \leq +85^{\circ}C \mbox{ (Ind.)}, \\ -40^{\circ}C \leq T A \leq +125^{\circ}C \mbox{ (Ext.)} \end{array}$ |  |  |

| OS10*        | TIOSC ST                                                                                                             | INTOSC Oscillator Wake-                                | —                  | 5.5  | 12   | 24   | μs                                                                                              | VDD = 2.0V, -40°C to +85°C                                                                                                                                                       |  |  |

|              |                                                                                                                      | up from Sleep                                          | _                  | 3.5  | 7    | 14   | μs                                                                                              | VDD = 3.0V, -40°C to +85°C                                                                                                                                                       |  |  |

|              |                                                                                                                      | Start-up Time                                          | —                  | 3    | 6    | 11   | μS                                                                                              | $VDD = 5.0V, -40^{\circ}C \text{ to } +85^{\circ}C$                                                                                                                              |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

2: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1 µF and 0.01 µF values in parallel are recommended.

3: By design.

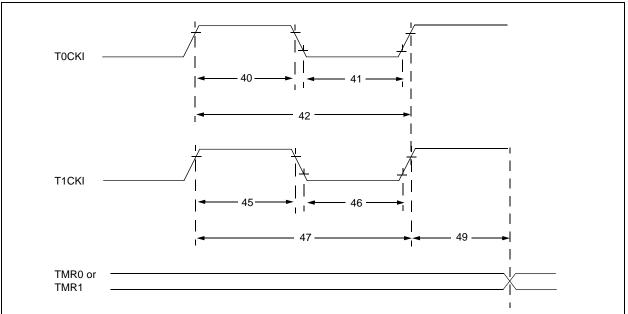

#### **FIGURE 16-8:** TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

#### TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS TABLE 16-5:

| Param<br>No. | Sym       |                           | Characterist                     | ic                            | Min                                       | Тур†   | Max    | Units | Conditions                         |

|--------------|-----------|---------------------------|----------------------------------|-------------------------------|-------------------------------------------|--------|--------|-------|------------------------------------|

| 40*          | T⊤0H      | T0CKI High F              | Pulse Width                      | No Prescaler                  | 0.5 TCY + 20                              | _      | _      | ns    |                                    |

|              |           |                           |                                  | With Prescaler                | 10                                        | —      | _      | ns    |                                    |

| 41*          | TT0L      | T0CKI Low P               | ulse Width                       | No Prescaler                  | 0.5 TCY + 20                              | —      | _      | ns    |                                    |

|              |           | With Prescaler            |                                  |                               | 10                                        | —      | —      | ns    |                                    |

| 42*          | Тт0Р      | T0CKI Period              | 1                                |                               | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —      | _      | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | TT1H      | T1CKI High<br>Time        | Synchronous, No Prescaler        |                               | 0.5 TCY + 20                              | —      | _      | ns    |                                    |

|              |           |                           | Synchronous,<br>with Prescaler   |                               | 15                                        | —      | _      | ns    |                                    |

|              |           |                           | Asynchronous                     |                               | 30                                        | —      | _      | ns    |                                    |

| 46*          | TT1L      | T1CKI Low<br>Time         | Synchronous, No Prescaler        |                               | 0.5 TCY + 20                              | —      | _      | ns    |                                    |

|              |           |                           | Synchronous,<br>with Prescaler   |                               | 15                                        | —      | _      | ns    |                                    |

|              |           |                           | Asynchronous                     |                               | 30                                        | —      | _      | ns    |                                    |

| 47*          | TT1P      | T1CKI Input<br>Period     | ut Synchronous                   |                               | Greater of:<br>30 or <u>Tcy + 40</u><br>N |        | _      | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                           | Asynchronous                     |                               | 60                                        | —      | _      | ns    |                                    |

| 48           | F⊤1       |                           | ator Input Frequebled by setting | uency Range<br>j bit T1OSCEN) | -                                         | 32.768 | —      | kHz   |                                    |

| 49*          | TCKEZTMR1 | Delay from E<br>Increment | xternal Clock E                  | dge to Timer                  | 2 Tosc                                    | —      | 7 Tosc | -     | Timers in Sync<br>mode             |

Standard Operating Conditions (unless otherwise stated)

These parameters are characterized but not tested.

t Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

FIGURE 17-44: TYPICAL HFINTOSC FREQUENCY CHANGE vs. VDD (85°C)

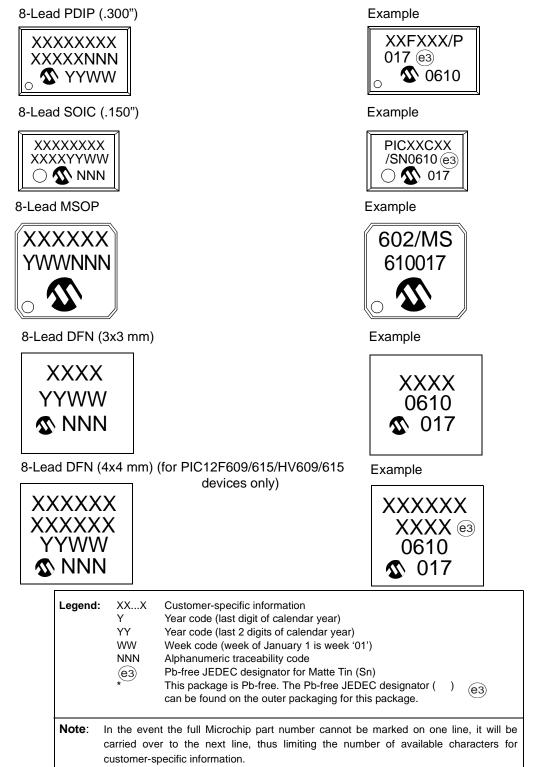

### **18.0 PACKAGING INFORMATION**

### **18.1** Package Marking Information

Standard PIC device marking consists of Microchip part number, year code, week code, and traceability code. For PIC device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com