Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 5                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 64 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 4x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 8-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f615-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Device     | Program<br>Memory | Data Memory  | Self Read/ |     | 10-bit A/D | Comparators | ECCP | Timers   | Veltage Bange     |

|------------|-------------------|--------------|------------|-----|------------|-------------|------|----------|-------------------|

| Device     | Flash<br>(words)  | SRAM (bytes) | Self Write | 1/0 | (ch)       | Comparators | ECCP | 8/16-bit | Voltage Range     |

| PIC12F609  | 1024              | 64           | —          | 5   | 0          | 1           | _    | 1/1      | 2.0V-5.5V         |

| PIC12HV609 | 1024              | 64           | —          | 5   | 0          | 1           |      | 1/1      | 2.0V-user defined |

| PIC12F615  | 1024              | 64           | —          | 5   | 4          | 1           | YES  | 2/1      | 2.0V-5.5V         |

| PIC12HV615 | 1024              | 64           | —          | 5   | 4          | 1           | YES  | 2/1      | 2.0V-user defined |

| PIC12F617  | 2048              | 128          | YES        | 5   | 4          | 1           | YES  | 2/1      | 2.0V-5.5V         |

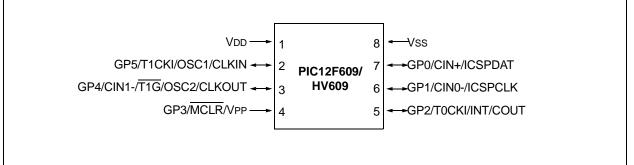

#### 8-Pin Diagram, PIC12F609/HV609 (PDIP, SOIC, MSOP, DFN)

#### TABLE 1: PIC12F609/HV609 PIN SUMMARY (PDIP, SOIC, MSOP, DFN)

| I/O                | Pin | Comparators | Timer | Interrupts | Pull-ups | Basic       |

|--------------------|-----|-------------|-------|------------|----------|-------------|

| GP0                | 7   | CIN+        | _     | IOC        | Y        | ICSPDAT     |

| GP1                | 6   | CIN0-       | —     | IOC        | Y        | ICSPCLK     |

| GP2                | 5   | COUT        | TOCKI | INT/IOC    | Y        | —           |

| GP3 <sup>(1)</sup> | 4   | _           |       | IOC        | Y(2)     | MCLR/VPP    |

| GP4                | 3   | CIN1-       | T1G   | IOC        | Y        | OSC2/CLKOUT |

| GP5                | 2   | —           | T1CKI | IOC        | Y        | OSC1/CLKIN  |

| _                  | 1   | -           |       | _          |          | Vdd         |

|                    | 8   | _           | _     | _          | _        | Vss         |

Note 1: Input only.

2: Only when pin is configured for external MCLR.

#### FIGURE 2-4: DATA MEMORY MAP OF THE PIC12F615/617/HV615

|                               | File        |                                                | File       |

|-------------------------------|-------------|------------------------------------------------|------------|

|                               | Address     |                                                | Address    |

| Indirect Addr. <sup>(1)</sup> | 00h         | Indirect Addr. <sup>(1)</sup>                  | 80h        |

| TMR0                          | 01h         | OPTION_REG                                     | 81h        |

| PCL                           | 02h         | PCL                                            | 82h        |

| STATUS                        | 03h         | STATUS                                         | 83h        |

| FSR                           | 04h         | FSR                                            | 84h        |

| GPIO                          | 05h         | TRISIO                                         | 85h        |

|                               | 06h         |                                                | 86h        |

|                               | 07h         |                                                | 87h        |

|                               | 08h         |                                                | 88h        |

|                               | 09h         |                                                | 89h        |

| PCLATH                        | 0Ah         | PCLATH                                         | 8Ah        |

| INTCON                        | 0Bh         | INTCON                                         | 8Bh        |

| PIR1                          | 0Ch         | PIE1                                           | 8Ch        |

|                               | 0Dh         |                                                | 8Dh        |

| TMR1L                         | 0Eh         | PCON                                           | 8Eh        |

| TMR1H                         | 0Fh         |                                                | 8Fh        |

| T1CON                         | 10h         | OSCTUNE                                        | 90h        |

| TMR2                          | 11h         |                                                | 91h        |

| T2CON                         | 12h         | PR2                                            | 92h        |

| CCPR1L                        | 13h         | APFCON                                         | 93h        |

| CCPR1H                        | 14h         |                                                | 94h        |

| CCP1CON                       | 15h         | WPU                                            | 95h        |

| PWM1CON                       | 16h         | IOC                                            | 96h        |

| ECCPAS                        | 17h         |                                                | 97h        |

|                               | 18h         | PMCON1 <sup>(2)</sup>                          | 98h        |

| VRCON                         | 19h         | PMCON2 <sup>(2)</sup>                          | 99h        |

| CMCON0                        | 1Ah         | PMADRL <sup>(2)</sup><br>PMADRH <sup>(2)</sup> | 9Ah        |

| CMCONIA                       | 1Bh         | PMADRH<br>PMDATL <sup>(2)</sup>                | 9Bh        |

| CMCON1                        | 1Ch         | PMDATE<br>PMDATH <sup>(2)</sup>                | 9Ch        |

|                               | 1Dh         |                                                | 9Dh        |

| ADRESH                        | 1Eh         | ADRESL                                         | 9Eh        |

| ADCON0                        | 1Fh         | ANSEL                                          | 9Fh<br>A0h |

|                               | 20h         | General                                        | Aun        |

| General                       |             | Purpose                                        |            |

| Purpose<br>Registers          |             | Registers<br>32 Bytes <sup>(2)</sup>           |            |

| 96 Bytes from                 |             |                                                |            |

| 20h-7Fh <sup>(2)</sup>        |             | Unimplemented for<br>PIC12F615/HV615           |            |

| Unimplemented for             |             | 110121013/11013                                | BFh        |

| PIC12F615/HV615               |             |                                                | C0h        |

|                               | 3Fh         |                                                |            |

| General                       | 40h         |                                                |            |

| Purpose<br>Registers          |             |                                                |            |

| 64 Bytes                      | 6Fh         |                                                | EFh        |

| Accesses 70h-7Fh              | 70h<br>7Fh  | Accesses 70h-7Fh                               | F0h<br>FFh |

| Bank 0                        |             | Bank 1                                         | - FF(1     |

| <b>—</b>                      |             |                                                |            |

|                               |             | y locations, read as '0'.                      |            |

|                               | /sical regi |                                                |            |

| 2: Used for                   |             | 2F617 only.                                    |            |

|                               |             |                                                |            |

| Addr   | Name   | Bit 7              | Bit 6                                                                                        | Bit 5         | Bit 4     | Bit 3           | Bit 2          | Bit 1      | Bit 0     | Value on<br>POR, BOR | Page    |  |

|--------|--------|--------------------|----------------------------------------------------------------------------------------------|---------------|-----------|-----------------|----------------|------------|-----------|----------------------|---------|--|

| Bank 0 |        |                    |                                                                                              |               |           |                 |                |            |           |                      |         |  |

| 00h    | INDF   | Addressing         | dressing this location uses contents of FSR to address data memory (not a physical register) |               |           |                 |                |            |           | xxxx xxxx            | 25, 119 |  |

| 01h    | TMR0   | Timer0 Mod         | lule's Registe                                                                               | er            |           |                 |                |            |           | xxxx xxxx            | 53, 11  |  |

| 02h    | PCL    | Program Co         | ounter's (PC)                                                                                | Least Signifi | cant Byte |                 |                |            |           | 0000 0000            | 25, 11  |  |

| 03h    | STATUS | IRP <sup>(1)</sup> | RP1 <sup>(1)</sup>                                                                           | RP0           | ТО        | PD              | Z              | DC         | С         | 0001 1xxx            | 18, 11  |  |

| 04h    | FSR    | Indirect Dat       | a Memory Ac                                                                                  | dress Pointe  | er        |                 |                |            |           | xxxx xxxx            | 25, 11  |  |

| 05h    | GPIO   | -                  | _                                                                                            | GP5           | GP4       | GP3             | GP2            | GP1        | GP0       | x0 x000              | 43, 11  |  |

| 06h    | _      | Unimpleme          | nted                                                                                         |               |           |                 |                |            |           | —                    | —       |  |

| 07h    | _      | Unimpleme          | nted                                                                                         |               |           |                 |                |            |           | —                    | —       |  |

| 08h    | _      | Unimpleme          | nted                                                                                         |               |           |                 |                |            |           | —                    | —       |  |

| 09h    | _      | Unimpleme          | nted                                                                                         |               |           |                 |                |            |           | —                    | —       |  |

| 0Ah    | PCLATH | _                  | _                                                                                            | _             | Write     | e Buffer for up | oper 5 bits of | Program Co | unter     | 0 0000               | 25, 11  |  |

| 0Bh    | INTCON | GIE                | PEIE                                                                                         | T0IE          | INTE      | GPIE            | T0IF           | INTF       | GPIF      | 0000 0000            | 20, 11  |  |

| 0Ch    | PIR1   | _                  | _                                                                                            | _             | _         | CMIF            | -              | _          | TMR1IF    | 00                   | 22, 11  |  |

| 0Dh    | —      | Unimpleme          | Unimplemented                                                                                |               |           |                 |                |            | —         | _                    |         |  |

| 0Eh    | TMR1L  | Holding Reg        | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register                  |               |           |                 |                |            | xxxx xxxx | 57, 11               |         |  |

| 0Fh    | TMR1H  | Holding Reg        | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register                   |               |           |                 |                |            | xxxx xxxx | 57, 11               |         |  |

| 10h    | T1CON  | T1GINV             | TMR1GE                                                                                       | T1CKPS1       | T1CKPS0   | T1OSCEN         | T1SYNC         | TMR1CS     | TMR10N    | 0000 0000            | 62, 11  |  |

| 11h    | _      | Unimpleme          | nted                                                                                         |               | •         |                 |                | •          | •         | _                    |         |  |

| 12h    | _      | Unimpleme          | nted                                                                                         |               |           |                 |                |            |           | _                    |         |  |

| 13h    | _      | Unimpleme          | nted                                                                                         |               |           |                 |                |            |           | _                    |         |  |

| 14h    | —      | Unimpleme          | nted                                                                                         |               |           |                 |                |            |           | —                    |         |  |

| 15h    | —      | Unimpleme          | nted                                                                                         |               |           |                 |                |            |           | —                    |         |  |

| 16h    | —      | Unimpleme          | nted                                                                                         |               |           |                 |                |            |           | —                    |         |  |

| 17h    | —      | Unimpleme          | nted                                                                                         |               |           |                 |                |            |           | —                    |         |  |

| 18h    | —      | Unimpleme          | nted                                                                                         |               |           |                 |                |            |           | —                    |         |  |

| 19h    | VRCON  | CMVREN             | _                                                                                            | VRR           | FVREN     | VR3             | VR2            | VR1        | VR0       | 0-00 0000            | 76, 11  |  |

| 1Ah    | CMCON0 | CMON               | COUT                                                                                         | CMOE          | CMPOL     | —               | CMR            | —          | CMCH      | 0000 -0-0            | 72, 11  |  |

| 1Bh    | —      |                    |                                                                                              |               |           | —               |                | —          |           | —                    |         |  |

| 1Ch    | CMCON1 | _                  | _                                                                                            | _             | T1ACS     | CMHYS           | _              | T1GSS      | CMSYNC    | 0 0-10               | 73, 11  |  |

| 1Dh    | —      | Unimpleme          | nted                                                                                         |               |           |                 |                |            |           | _                    | —       |  |

| 1Eh    | _      | Unimpleme          | nted                                                                                         |               |           |                 |                |            |           | _                    | _       |  |

| 1Fh    | _      | Unimpleme          | nted                                                                                         |               |           |                 | •              |            |           |                      |         |  |

#### **TABLE 2-1:** PIC12F609/HV609 SPECIAL FUNCTION REGISTERS SUMMARY BANK 0

IRP and RP1 bits are reserved, always maintain these bits clear. 1:

2: Read only register.

#### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

REGISTER 2-1:

the bank select bits for data memory (RAM)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

STATUS: STATUS REGISTER

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, see the Section 14.0 "Instruction Set Summary".

- Note 1: Bits IRP and RP1 of the STATUS register are not used by the PIC12F609/615/617/ 12HV609/615 and should be maintained as clear. Use of these bits is not recommended, since this may affect upward compatibility with future products.

- 2: The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| Reserved | Reserved | R/W-0 | R-1 | R-1 | R/W-x | R/W-x | R/W-x |

|----------|----------|-------|-----|-----|-------|-------|-------|

| IRP      | RP1      | RP0   | TO  | PD  | Z     | DC    | С     |

| bit 7    |          |       |     |     |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | IRP: This bit is reserved and should be maintained as '0'                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | RP1: This bit is reserved and should be maintained as '0'                                                                                                               |

| bit 5   | RP0: Register Bank Select bit (used for direct addressing)                                                                                                              |

|         | 1 = Bank 1 (80h – FFh)<br>0 = Bank 0 (00h – 7Fh)                                                                                                                        |

| bit 4   | TO: Time-out bit                                                                                                                                                        |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                                              |

| bit 3   | PD: Power-down bit                                                                                                                                                      |

|         | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                                                  |

| bit 2   | Z: Zero bit                                                                                                                                                             |

|         | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                  |

| bit 1   | DC: Digit Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions), For Borrow, the polarity is reversed.                                                             |

|         | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul>                |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions)                                                                                            |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the                                                                   |

Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the Note 1: second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

#### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, GPIO change and external GP2/INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | GPIE  | T0IF  | INTF  | GPIF  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | GIE: Global Interrupt Enable bit<br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts                                                                                        |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                      |

| bit 5 | <b>TolE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                    |

| bit 4 | INTE: GP2/INT External Interrupt Enable bit<br>1 = Enables the GP2/INT external interrupt<br>0 = Disables the GP2/INT external interrupt                                                      |

| bit 3 | <b>GPIE:</b> GPIO Change Interrupt Enable bit <sup>(1)</sup><br>1 = Enables the GPIO change interrupt<br>0 = Disables the GPIO change interrupt                                               |

| bit 2 | <b>T0IF:</b> Timer0 Overflow Interrupt Flag bit <sup>(2)</sup><br>1 = Timer0 register has overflowed (must be cleared in software)<br>0 = Timer0 register did not overflow                    |

| bit 1 | INTF: GP2/INT External Interrupt Flag bit<br>1 = The GP2/INT external interrupt occurred (must be cleared in software)<br>0 = The GP2/INT external interrupt did not occur                    |

| bit 0 | <b>GPIF:</b> GPIO Change Interrupt Flag bit<br>1 = When at least one of the GPIO <5:0> pins changed state (must be cleared in software)<br>0 = None of the GPIO <5:0> pins have changed state |

**Note 1:** IOC register must also be enabled.

2: T0IF bit is set when TMR0 rolls over. TMR0 is unchanged on Reset and should be initialized before clearing T0IF bit.

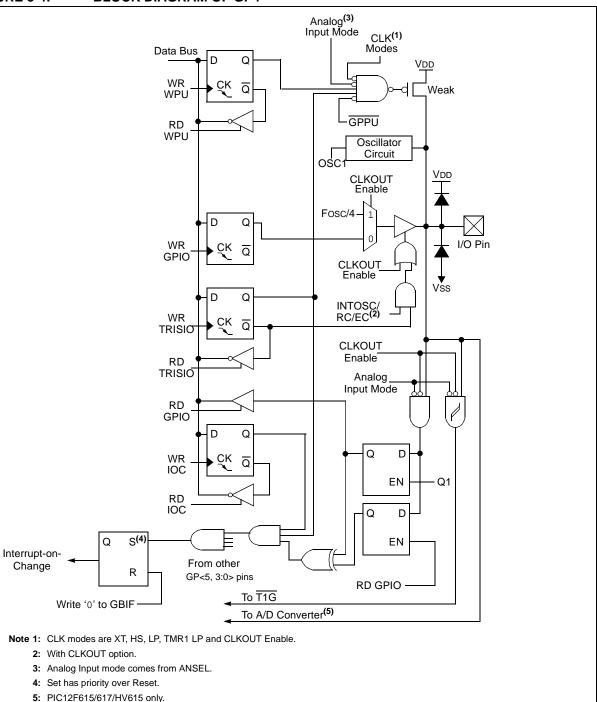

#### 5.2.4.5 GP4/AN3<sup>(2)</sup>/CIN1-/T1G/ P1B<sup>(1, 2)</sup>/OSC2/CLKOUT

Figure 5-4 shows the diagram for this pin. The GP4 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(2)</sup>

- Comparator inverting input

- a Timer1 gate (count enable)

#### FIGURE 5-4: BLOCK DIAGRAM OF GP4

- PWM output, alternate pin(1, 2)

- a crystal/resonator connection

- · a clock output

Note 1: Alternate pin function.2: PIC12F615/617/HV615 only.

#### 10.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- Results formatting

#### 10.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. See the corresponding port section for more information.

| Note: | Analog voltages on any pin that is defined |

|-------|--------------------------------------------|

|       | as a digital input may cause the input     |

|       | buffer to conduct excess current.          |

#### 10.1.2 CHANNEL SELECTION

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 10.2 "ADC Operation"** for more information.

#### 10.1.3 ADC VOLTAGE REFERENCE

The VCFG bit of the ADCON0 register provides control of the positive voltage reference. The positive voltage reference can be either VDD or an external voltage source. The negative voltage reference is always connected to the ground reference.

#### 10.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ANSEL register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11 TAD periods as shown in Figure 10-3.

For correct conversion, the appropriate TAD specification must be met. See A/D conversion requirements in **Section 16.0 "Electrical Specifications"** for more information. Table 10-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

#### 10.2.7 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

#### REGISTER 10-1: ADCON0: A/D CONTROL REGISTER 0

| R/W-0      | ) R/W-0                                                                                        | U-0                                                                                                                                                                                                                                                                                                   | R/W-0          | R/W-0            | R/W-0                | R/W-0     | R/W-0 |  |  |  |

|------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|----------------------|-----------|-------|--|--|--|

| ADFM       | 1 VCFG                                                                                         | —                                                                                                                                                                                                                                                                                                     | CHS2           | CHS1             | CHS0                 | GO/DONE   | ADON  |  |  |  |

| bit 7      |                                                                                                |                                                                                                                                                                                                                                                                                                       |                |                  | ·                    |           | bit 0 |  |  |  |

| Legend:    |                                                                                                |                                                                                                                                                                                                                                                                                                       |                |                  |                      |           |       |  |  |  |

| R = Read   | able bit                                                                                       | W = Writable                                                                                                                                                                                                                                                                                          | bit            | U = Unimpler     | mented bit, rea      | ad as '0' |       |  |  |  |

| -n = Value | e at POR                                                                                       | '1' = Bit is set                                                                                                                                                                                                                                                                                      |                | '0' = Bit is cle | '0' = Bit is cleared |           | own   |  |  |  |

| bit 7      | <b>ADFM:</b> A/D<br>1 = Right ju:<br>0 = Left just                                             |                                                                                                                                                                                                                                                                                                       | sult Format Se | elect bit        |                      |           |       |  |  |  |

| bit 6      |                                                                                                | VCFG: Voltage Reference bit<br>1 = VREF pin<br>0 = VDD                                                                                                                                                                                                                                                |                |                  |                      |           |       |  |  |  |

| bit 5      | Unimpleme                                                                                      | nted: Read as                                                                                                                                                                                                                                                                                         | '0'            |                  |                      |           |       |  |  |  |

| bit 4-2    | 000 = Chan<br>001 = Chan<br>010 = Chan<br>011 = Chan<br>100 = CVRE<br>101 = 0.6V<br>110 = 1.2V | Reference                                                                                                                                                                                                                                                                                             |                |                  |                      |           |       |  |  |  |

| bit 1      | 1 = A/D con<br>This bit i                                                                      | <ul> <li>GO/DONE: A/D Conversion Status bit</li> <li>1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle.<br/>This bit is automatically cleared by hardware when the A/D conversion has completed.</li> <li>0 = A/D conversion completed/not in progress</li> </ul> |                |                  |                      |           |       |  |  |  |

| bit 0      | <b>ADON:</b> ADO<br>1 = ADC is 0                                                               | C Enable bit                                                                                                                                                                                                                                                                                          |                |                  |                      |           |       |  |  |  |

| Note 1:    |                                                                                                |                                                                                                                                                                                                                                                                                                       |                |                  |                      |           |       |  |  |  |

#### 11.3.1 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 11-1.

#### EQUATION 11-1: PWM PERIOD

$$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$$

$$(TMR2 Prescale Value)$$

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from CCPR1L into CCPR1H.

| Note: | The Timer2 postscaler (see Section 8.1 |

|-------|----------------------------------------|

|       | "Timer2 Operation") is not used in the |

|       | determination of the PWM frequency.    |

#### 11.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPR1L register and DC1B<1:0> bits of the CCP1CON register. The CCPR1L contains the eight MSbs and the DC1B<1:0> bits of the CCP1CON register contain the two LSbs. CCPR1L and DC1B<1:0> bits of the CCP1CON register can be written to at any time. The duty cycle value is not latched into CCPR1H until after the period completes (i.e., a match between PR2 and TMR2 registers occurs). While using the PWM, the CCPR1H register is read-only.

Equation 11-2 is used to calculate the PWM pulse width.

Equation 11-3 is used to calculate the PWM duty cycle ratio.

#### EQUATION 11-2: PULSE WIDTH

$Pulse Width = (CCPR1L:CCP1CON < 5:4>) \bullet$

TOSC • (TMR2 Prescale Value)

#### EQUATION 11-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(CCPR1L:CCP1CON < 5:4>)}{4(PR2 + 1)}$$

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (Fosc), or 2 bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPR1H and 2-bit latch, then the CCP1 pin is cleared (see Figure 11-3).

#### 11.3.3 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 11-4.

#### EQUATION 11-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

#### TABLE 11-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 11-5: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 11.4.4 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the ECCPASx bits of the ECCPAS register. A shutdown event may be generated by:

- A logic '0' on the INT pin

- Comparator

- Setting the ECCPASE bit in firmware

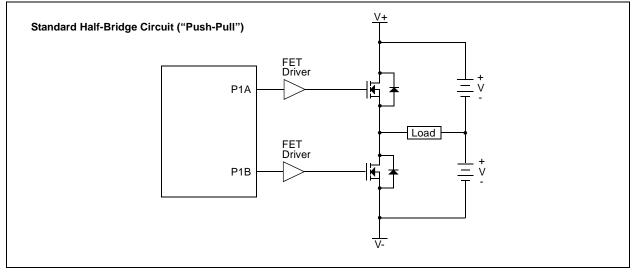

A shutdown condition is indicated by the ECCPASE (Auto-Shutdown Event Status) bit of the ECCPAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state. Refer to Figure 1.

When a shutdown event occurs, two things happen:

The ECCPASE bit is set to '1'. The ECCPASE will remain set until cleared in firmware or an auto-restart occurs (see Section 11.4.5 "Auto-Restart Mode").

The enabled PWM pins are asynchronously placed in their shutdown states. The state of P1A is determined by the PSSAC bit. The state of P1B is determined by the PSSBD bit. The PSSAC and PSSBD bits are located in the ECCPAS register. Each pin may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

#### ECCPAS<2:0> 111 110 101 100 011 010 ╧ PSSAC<0: From Comparator 001 P1A\_DRV 000 PRSEN Ŧ PSSAC<1> Х R s TRISx From Data Bus ECCPASE D Q Write to ECCPASE PSSBD<0> P1B DRV PSSBD<1> Х P1B TRIS

#### FIGURE 11-10: AUTO-SHUTDOWN BLOCK DIAGRAM

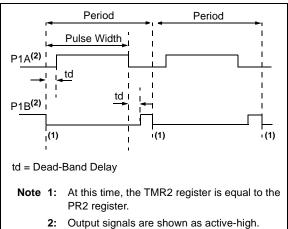

#### 11.4.6 PROGRAMMABLE DEAD-BAND DELAY MODE

In Half-Bridge applications where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In Half-Bridge mode, a digitally programmable deadband delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 11-13 for illustration. The lower seven bits of the associated PWMxCON register (Register 11-3) sets the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc).

#### FIGURE 11-13: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

#### FIGURE 11-14: EXAMPLE OF HALF-BRIDGE APPLICATIONS

#### 12.3.5 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows:

- PWRT time-out is invoked after POR has expired.

- OST is activated after the PWRT time-out has expired.

The total time-out will vary based on oscillator configuration and PWRTE bit status. For example, in EC mode with PWRTE bit erased (PWRT disabled), there will be no time-out at all. Figure 12-4, Figure 12-5 and Figure 12-6 depict time-out sequences.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then, bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 12-5). This is useful for testing purposes or to synchronize more than one PIC12F609/615/617/12HV609/615 device operating in parallel.

Table 12-6 shows the Reset conditions for some special registers, while Table 12-5 shows the Reset conditions for all the registers.

#### 12.3.6 POWER CONTROL (PCON) REGISTER

The Power Control register PCON (address 8Eh) has two Status bits to indicate what type of Reset occurred last.

Bit 0 is  $\overline{\text{BOR}}$  (Brown-out).  $\overline{\text{BOR}}$  is unknown on Poweron Reset. It must then be set by the user and checked on subsequent Resets to see if  $\overline{\text{BOR}} = 0$ , indicating that a Brown-out has occurred. The  $\overline{\text{BOR}}$  Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (BOREN<1:0> = 00 in the Configuration Word register).

Bit 1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent Reset, if POR is '0', it will indicate that a Power-on Reset has occurred (i.e., VDD may have gone too low).

For more information, see Section 12.3.4 "Brown-out Reset (BOR)".

| Oscillator Configuration | Powe                   | er-up            | Brown-o                | Wake-up from     |             |

|--------------------------|------------------------|------------------|------------------------|------------------|-------------|

| Oscillator Configuration | <b>PWRTE</b> = 0       | <b>PWRTE</b> = 1 | <b>PWRTE</b> = 0       | <b>PWRTE</b> = 1 | Sleep       |

| XT, HS, LP               | TPWRT + 1024 •<br>Tosc | 1024 • Tosc      | TPWRT + 1024 •<br>Tosc | 1024 • Tosc      | 1024 • Tosc |

| RC, EC, INTOSC           | TPWRT                  | —                | TPWRT                  | —                | —           |

#### TABLE 12-1: TIME-OUT IN VARIOUS SITUATIONS

#### TABLE 12-2: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD | Condition                          |  |  |  |

|-----|-----|----|----|------------------------------------|--|--|--|

| 0   | х   | 1  | 1  | Power-on Reset                     |  |  |  |

| u   | 0   | 1  | 1  | Brown-out Reset                    |  |  |  |

| u   | u   | 0  | u  | WDT Reset                          |  |  |  |

| u   | u   | 0  | 0  | WDT Wake-up                        |  |  |  |

| u   | u   | u  | u  | MCLR Reset during normal operation |  |  |  |

| u   | u   | 1  | 0  | MCLR Reset during Sleep            |  |  |  |

**Legend:** u = unchanged, x = unknown

#### TABLE 12-3: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT RESET

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|----------------------|------------------------------------------------|

| PCON   |       |       | _     | _     |       |       | POR   | BOR   | dd                   | uu                                             |

| STATUS | IRP   | RP1   | RP0   | TO    | PD    | Z     | DC    | С     | 0001 1xxx            | 000q quuu                                      |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition. Shaded cells are not used by BOR.

**Note 1:** Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

| Register   | Register Address Power-on Reset WDT Reset Brown-out Reset |           | WDT Reset            | Wake-up from Sleep through<br>Interrupt<br>Wake-up from Sleep through<br>WDT Time-out |

|------------|-----------------------------------------------------------|-----------|----------------------|---------------------------------------------------------------------------------------|

| W          | _                                                         | xxxx xxxx | uuuu uuuu            | uuuu uuuu                                                                             |

| INDF       | 00h/80h                                                   | xxxx xxxx | XXXX XXXX            | uuuu uuuu                                                                             |

| TMR0       | 01h                                                       | xxxx xxxx | uuuu uuuu            | uuuu uuuu                                                                             |

| PCL        | 02h/82h                                                   | 0000 0000 | 0000 0000            | PC + 1 <sup>(3)</sup>                                                                 |

| STATUS     | 03h/83h                                                   | 0001 1xxx | 000q quuu <b>(4)</b> | uuuq quuu <sup>(4)</sup>                                                              |

| FSR        | 04h/84h                                                   | xxxx xxxx | uuuu uuuu            | uuuu uuuu                                                                             |

| GPIO       | 05h                                                       | x0 x000   | u0 u000              | uu uuuu                                                                               |

| PCLATH     | 0Ah/8Ah                                                   | 0 0000    | 0 0000               | u uuuu                                                                                |

| INTCON     | 0Bh/8Bh                                                   | 0000 0000 | 0000 0000            | uuuu uuuu <b>(2)</b>                                                                  |

| PIR1       | 0Ch                                                       | 00        | 00                   | uu <b>(2)</b>                                                                         |

| TMR1L      | 0Eh                                                       | xxxx xxxx | uuuu uuuu            | uuuu uuuu                                                                             |

| TMR1H      | 0Fh                                                       | xxxx xxxx | uuuu uuuu            | uuuu uuuu                                                                             |

| T1CON      | 10h                                                       | 0000 0000 | uuuu uuuu            | -uuu uuuu                                                                             |

| VRCON      | 19h                                                       | 0-00 0000 | 0-00 0000            | u-uu uuuu                                                                             |

| CMCON0     | 1Ah                                                       | 0000 -0-0 | 0000 -0-0            | uuuu -u-u                                                                             |

| CMCON1     | 1Ch                                                       | 0 0-10    | 0 0-10               | u u-qu                                                                                |

| OPTION_REG | 81h                                                       | 1111 1111 | 1111 1111            | uuuu uuuu                                                                             |

| TRISIO     | 85h                                                       | 11 1111   | 11 1111              | uu uuuu                                                                               |

| PIE1       | 8Ch                                                       | 00        | 00                   | uu                                                                                    |

| PCON       | 8Eh                                                       | 0x        | (1, 5)               | uu                                                                                    |

| OSCTUNE    | 90h                                                       | 0 0000    | u uuuu               | u uuuu                                                                                |

| WPU        | 95h                                                       | 11 -111   | 11 -111              | uu -uuu                                                                               |

| IOC        | 96h                                                       | 00 0000   | 00 0000              | uu uuuu                                                                               |

| ANSEL      | 9Fh                                                       | 1-11      | 1-11                 | d-dd                                                                                  |

#### TABLE 12-4: INITIALIZATION CONDITION FOR REGISTERS (PIC12F609/HV609)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

**3:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 12-6 for Reset value for specific condition.

5: If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

#### 16.3 DC Characteristics: PIC12HV609/615-I (Industrial) PIC12HV609/615-E (Extended)

| DC CHA       | ARACTERISTICS                          |     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |     |       |     |                                     |  |

|--------------|----------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|-------------------------------------|--|

| Param<br>No. | Device Characteristics                 | Min | Typ†                                                                                                                                                                                    | Max | Units |     | Conditions                          |  |

| NO.          |                                        |     |                                                                                                                                                                                         |     |       | Vdd | Note                                |  |

| D010 Suppl   | Supply Current (IDD) <sup>(1, 2)</sup> | _   | 160                                                                                                                                                                                     | 230 | μΑ    | 2.0 | Fosc = 32 kHz                       |  |

|              | PIC12HV609/615                         |     | 240                                                                                                                                                                                     | 310 | μΑ    | 3.0 | LP Oscillator mode                  |  |

|              |                                        | —   | 280                                                                                                                                                                                     | 400 | μA    | 4.5 |                                     |  |

| D011*        |                                        |     | 270                                                                                                                                                                                     | 380 | μA    | 2.0 | Fosc = 1 MHz                        |  |

|              |                                        | _   | 400                                                                                                                                                                                     | 560 | μΑ    | 3.0 | XT Oscillator mode                  |  |

|              |                                        | —   | 520                                                                                                                                                                                     | 780 | μΑ    | 4.5 |                                     |  |

| D012         |                                        | _   | 380                                                                                                                                                                                     | 540 | μΑ    | 2.0 | Fosc = 4 MHz                        |  |

|              |                                        |     | 575                                                                                                                                                                                     | 810 | μA    | 3.0 | XT Oscillator mode                  |  |

|              |                                        | —   | 0.875                                                                                                                                                                                   | 1.3 | mA    | 4.5 |                                     |  |

| D013*        |                                        | _   | 215                                                                                                                                                                                     | 310 | μΑ    | 2.0 | Fosc = 1 MHz                        |  |

|              |                                        |     | 375                                                                                                                                                                                     | 565 | μA    | 3.0 | EC Oscillator mode                  |  |

|              |                                        | —   | 570                                                                                                                                                                                     | 870 | μΑ    | 4.5 |                                     |  |

| D014         |                                        |     | 330                                                                                                                                                                                     | 475 | μΑ    | 2.0 | Fosc = 4 MHz                        |  |

|              |                                        | _   | 550                                                                                                                                                                                     | 800 | μΑ    | 3.0 | EC Oscillator mode                  |  |

|              |                                        | —   | 0.85                                                                                                                                                                                    | 1.2 | mA    | 4.5 |                                     |  |

| D016*        |                                        |     | 310                                                                                                                                                                                     | 435 | μΑ    | 2.0 | Fosc = 4 MHz                        |  |

|              |                                        | _   | 500                                                                                                                                                                                     | 700 | μΑ    | 3.0 | INTOSC mode                         |  |

|              |                                        | —   | 0.74                                                                                                                                                                                    | 1.1 | mA    | 4.5 |                                     |  |

| D017         |                                        |     | 460                                                                                                                                                                                     | 650 | μA    | 2.0 | Fosc = 8 MHz                        |  |

|              |                                        | _   | 0.75                                                                                                                                                                                    | 1.1 | mA    | 3.0 | INTOSC mode                         |  |

|              |                                        | —   | 1.2                                                                                                                                                                                     | 1.6 | mA    | 4.5 |                                     |  |

| D018         |                                        | _   | 320                                                                                                                                                                                     | 465 | μΑ    | 2.0 | Fosc = 4 MHz                        |  |

|              |                                        |     | 510                                                                                                                                                                                     | 750 | μA    | 3.0 | EXTRC mode <sup>(3)</sup>           |  |

|              |                                        | —   | 0.770                                                                                                                                                                                   | 1.0 | mA    | 4.5 |                                     |  |

| D019         |                                        |     | 2.5                                                                                                                                                                                     | 3.4 | mA    | 4.5 | Fosc = 20 MHz<br>HS Oscillator mode |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 4.5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

#### 16.8 DC Characteristics: PIC12F609/615/617/12HV609/615-I (Industrial) PIC12F609/615/617/12HV609/615-E (Extended) (Continued)

| DC CHA       | DC CHARACTERISTICS |                                                        | Standard Opera<br>Operating tempe | -    | -40°C ≤ | ≤ <b>T</b> A ≤ <b>+</b> 8 | less otherwise stated)<br>TA $\leq$ +85°C for industrial<br>TA $\leq$ +125°C for extended |  |  |  |

|--------------|--------------------|--------------------------------------------------------|-----------------------------------|------|---------|---------------------------|-------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No. | Sym                | Characteristic                                         | Min                               | Тур† | Мах     | Units                     | Conditions                                                                                |  |  |  |

| D101*        | COSC2              | Capacitive Loading Specs on<br>Output Pins<br>OSC2 pin | _                                 | _    | 15      | pF                        | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1                    |  |  |  |

| D101A*       | Сю                 | All I/O pins                                           | —                                 | —    | 50      | pF                        |                                                                                           |  |  |  |

|              |                    | Program Flash Memory                                   |                                   |      |         |                           |                                                                                           |  |  |  |

| D130         | Eр                 | Cell Endurance                                         | 10K                               | 100K | —       | E/W                       | $-40^{\circ}C \le TA \le +85^{\circ}C$                                                    |  |  |  |

| D130A        | ED                 | Cell Endurance                                         | 1K                                | 10K  | _       | E/W                       | $+85^{\circ}C \le TA \le +125^{\circ}C$                                                   |  |  |  |

| D131         | Vpr                | VDD for Read                                           | Vmin                              | —    | 5.5     | V                         | VMIN = Minimum operating<br>voltage                                                       |  |  |  |

| D132         | VPEW               | VDD for Bulk Erase/Write                               | 4.5                               | _    | 5.5     | V                         |                                                                                           |  |  |  |

| D132A        | VPEW               | VDD for Row Erase/Write <sup>(6)</sup>                 | Vmin                              | _    | 5.5     | V                         |                                                                                           |  |  |  |

| D133         | TPEW               | Erase/Write cycle time                                 | _                                 | 2    | 2.5     | ms                        |                                                                                           |  |  |  |

| D134         | TRETD              | Characteristic Retention                               | 40                                | —    | _       | Year                      | Provided no other specifications are violated                                             |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: This specification applies to GP3/MCLR configured as GP3 with the internal weak pull-up disabled.

5: This specification applies to all weak pull-up pins, including the weak pull-up found on GP3/MCLR. When GP3/MCLR is configured as MCLR reset pin, the weak pull-up is always enabled.

6: Applies to PIC12F617 only.

#### **16.9** Thermal Considerations

| Param<br>No. | Sym       | Characteristic             | Тур    | Units | Conditions                                                                                            |

|--------------|-----------|----------------------------|--------|-------|-------------------------------------------------------------------------------------------------------|

| TH01         | θJA       | Thermal Resistance         | 84.6*  | C/W   | 8-pin PDIP package                                                                                    |

|              |           | Junction to Ambient        | 149.5* | C/W   | 8-pin SOIC package                                                                                    |

|              |           |                            | 211*   | C/W   | 8-pin MSOP package                                                                                    |

|              |           |                            | 60*    | C/W   | 8-pin DFN 3x3mm package                                                                               |

|              |           |                            | 44*    | C/W   | 8-pin DFN 4x4mm package                                                                               |

| TH02         | θJC       | Thermal Resistance         | 41.2*  | C/W   | 8-pin PDIP package                                                                                    |

|              |           | Junction to Case           | 39.9*  | C/W   | 8-pin SOIC package                                                                                    |

|              |           |                            | 39*    | C/W   | 8-pin MSOP package                                                                                    |

|              |           |                            | 9*     | C/W   | 8-pin DFN 3x3mm package                                                                               |

|              |           |                            | 3.0*   | C/W   | 8-pin DFN 4x4mm package                                                                               |

| TH03         | TDIE      | Die Temperature            | 150*   | С     |                                                                                                       |

| TH04         | PD        | Power Dissipation          | —      | W     | PD = PINTERNAL + PI/O                                                                                 |

| TH05         | PINTERNAL | Internal Power Dissipation | —      | W     | PINTERNAL = IDD x VDD<br>(NOTE 1)                                                                     |

| TH06         | Pi/o      | I/O Power Dissipation      | —      | W     | $ \begin{array}{l} PI/O = \Sigma \ (IOL \ ^* \ VOL) + \Sigma \ (IOH \ ^* \ (VDD - VOH)) \end{array} $ |

| TH07         | Pder      | Derated Power              | —      | W     | Pder = PDmax (Tdie - Ta)/θja<br>(NOTE 2)                                                              |

\* These parameters are characterized but not tested.

**Note 1:** IDD is current to run the chip alone without driving any load on the output pins.

**2:**  $T_A$  = Ambient temperature.

#### TABLE 16-11: PIC12F615/617/HV615 A/D CONVERTER (ADC) CHARACTERISTICS:

|               | -    | rating Conditions (unless perature $-40^{\circ}C \le TA \le -40^{\circ}C$ |            | vise stated | d)       |       |                                                                     |

|---------------|------|---------------------------------------------------------------------------|------------|-------------|----------|-------|---------------------------------------------------------------------|

| Param<br>No.  | Sym  | Characteristic                                                            | Min        | Тур†        | Max      | Units | Conditions                                                          |

| AD01          | Nr   | Resolution                                                                | _          | _           | 10 bits  | bit   |                                                                     |

| AD02          | EIL  | Integral Error                                                            | —          | _           | ±1       | LSb   | VREF = 5.12V <sup>(5)</sup>                                         |

| AD03          | Edl  | Differential Error                                                        | _          | —           | ±1       | LSb   | No missing codes to 10 bits<br>VREF = 5.12V <sup>(5)</sup>          |

| AD04          | EOFF | Offset Error                                                              |            | +1.5        | +2.0     | LSb   | Vref = 5.12V <sup>(5)</sup>                                         |

| AD07          | Egn  | Gain Error                                                                |            | _           | ±1       | LSb   | VREF = 5.12V <sup>(5)</sup>                                         |

| AD06<br>AD06A | Vref | Reference Voltage <sup>(3)</sup>                                          | 2.2<br>2.5 | _           | —<br>Vdd | V     | Absolute minimum to ensure 1 LSb<br>accuracy                        |

| AD07          | VAIN | Full-Scale Range                                                          | Vss        | _           | VREF     | V     |                                                                     |

| AD08          | ZAIN | Recommended<br>Impedance of Analog<br>Voltage Source                      | —          | _           | 10       | kΩ    |                                                                     |

| AD09*         | IREF | VREF Input Current <sup>(3)</sup>                                         | 10         | —           | 1000     | μΑ    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN. |

|               |      |                                                                           |            |             | 50       | μA    | During A/D conversion cycle.                                        |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error includes integral, differential, offset and gain errors.

- 2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

- **3:** ADC VREF is from external VREF or VDD pin, whichever is selected as reference input.

- 4: When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

**5:** VREF = 5V for PIC12HV615.

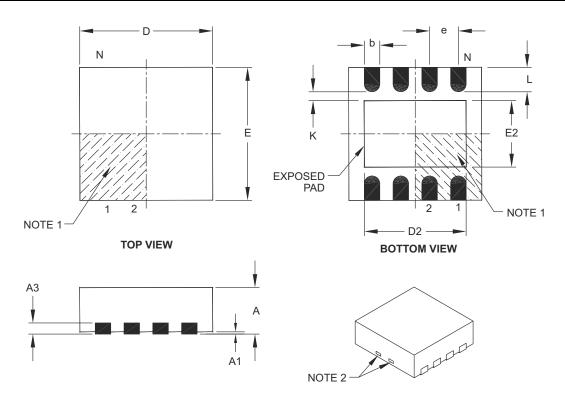

#### 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units |          | MILLIMETERS |      |  |

|------------------------|-------|----------|-------------|------|--|

| Dimension Limits       |       | MIN      | NOM         | MAX  |  |

| Number of Pins         | Ν     | 8        |             |      |  |