Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 4x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VDFN Exposed Pad                                                       |

| Supplier Device Package    | 8-DFN (3x3)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f615-i-mf |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.7 APFCON Register (PIC12F615/617/HV615 only)

The Alternate Pin Function Control (APFCON) register is used to steer specific peripheral input and output functions between different pins. For this device, the P1A, P1B and Timer1 Gate functions can be moved between different pins.

The APFCON register bits are shown in Register 2-7.

### REGISTER 2-7: APFCON:ALTERNATE PIN FUNCTION REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0  | U-0 | U-0 | R/W-0  | R/W-0  |

|-------|-----|-----|--------|-----|-----|--------|--------|

| —     | —   | —   | T1GSEL | -   | —   | P1BSEL | P1ASEL |

| bit 7 |     |     |        |     |     |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-5    | Unimplemented: Read as '0'                                               |

|------------|--------------------------------------------------------------------------|

| bit 4      | T1GSEL: TMR1 Input Pin Select bit                                        |

|            | 1 = T1G function is on GP3/T1G <sup>(2)</sup> /MCLR/VPP (2)              |

|            | 0 = T1G function is on GP4/AN3/CIN1-/T1G/P1B <sup>(2)</sup> /OSC2/CLKOUT |

| bit 3-2    | Unimplemented: Read as '0'                                               |

| bit 1      | P1BSEL: P1B Output Pin Select bit                                        |

|            | 1 = P1B function is on GP4/AN3/CIN1-/T1G/P1B <sup>(2)</sup> /OSC2/CLKOUT |

|            | 0 = P1B function is on GP0/AN0/CIN+/P1B/ICSPDAT                          |

| bit 0      | P1ASEL: P1A Output Pin Select bit                                        |

|            | 1 = P1A function is on GP5/T1CKI/P1A <sup>(2)</sup> /OSC1/CLKIN          |

|            | 0 = P1A function is on GP2/AN2/T0CKI/INT/COUT/CCP1/P1A                   |

| Nata A. Di |                                                                          |

Note 1: PIC12F615/617/HV615 only.

2: Alternate pin function.

| U-1   | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/S-0 | R/S-0 |

|-------|-----|-----|-----|-----|-------|-------|-------|

| —     | _   | —   | —   | —   | WREN  | WR    | RD    |

| bit 7 |     |     |     |     |       |       | bit 0 |

- bit 7 Unimplemented: Read as '1'

- bit 6-3 Unimplemented: Read as '0'

- bit 2 WREN: Program Memory Write Enable bit

- 1 = Allows write cycles

- 0 = Inhibits write to the EEPROM

- bit 1 WR: Write Control bit

- 1 = Initiates a write cycle to program memory. (The bit is cleared by hardware when write is complete. The WR bit can only be set (not cleared) in software.)

- 0 = Write cycle to the Flash memory is complete

#### bit 0 **RD:** Read Control bit

- 1 = Initiates a program memory read (The read takes one cycle. The RD is cleared in hardware; the RD bit can only be set (not cleared) in software).

- 0 = Does not initiate a Flash memory read

| Legend:           |                  |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared    | x = bit is unknown |  |

NOTES:

#### 7.10 **ECCP Special Event Trigger** (PIC12F615/617/HV615 only)

If a ECCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The ECCP module may still be configured to generate a ECCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

Timer1 should be synchronized to the Fosc to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the ECCP, the write will take precedence.

For more information, see Section 11.0 "Enhanced Capture/Compare/PWM (With Auto-Shutdown and Dead Band) Module (PIC12F615/617/HV615 only)".

#### 7.11 **Comparator Synchronization**

The same clock used to increment Timer1 can also be used to synchronize the comparator output. This feature is enabled in the Comparator module.

When using the comparator for Timer1 gate, the comparator output should be synchronized to Timer1. This ensures Timer1 does not miss an increment if the comparator changes.

For more information, see Section 9.0 "Comparator Module".

### 7.12 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 7-1, is used to control Timer1 and select the various features of the Timer1 module.

#### REGISTER 7-1: T1CON: TIMER 1 CONTROL REGISTER

| R/W-0               | R/W-0                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                              | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0     |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|-----------------|-----------------|-----------|

| T1GINV <sup>(</sup> | <sup>1)</sup> TMR1GE <sup>(2)</sup>                                                                                                                                                                                 | T1CKPS1                                                                                                                                                                                                                                                                                            | T1CKPS0        | T1OSCEN          | T1SYNC          | TMR1CS          | TMR10N    |

| bit 7               |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                    |                |                  |                 |                 | bit 0     |

|                     |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                    |                |                  |                 |                 |           |

| Legend:             |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                    |                |                  |                 |                 |           |

| R = Reada           | ble bit                                                                                                                                                                                                             | W = Writable                                                                                                                                                                                                                                                                                       | bit            | U = Unimpler     | nented bit, rea | d as '0'        |           |

| -n = Value          | at POR                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                   |                | '0' = Bit is cle | ared            | x = Bit is unkr | nown      |

| bit 7               | 1 = Timer1 gate is active-high (Timer1 cou                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                    |                | •                | • •             |                 |           |

| bit 6               | TMR1GE: Tin<br><u>If TMR1ON =</u><br>This bit is igno<br><u>If TMR1ON =</u>                                                                                                                                         | <ul> <li>0 = Timer1 gate is active-low (Timer1 counts when gate is low)</li> <li>TMR1GE: Timer1 Gate Enable bit<sup>(2)</sup></li> <li>If TMR1ON = 0:</li> <li>This bit is ignored</li> <li>If TMR1ON = 1:</li> <li>1 = Timer1 is on if Timer1 gate is active</li> <li>0 = Timer1 is on</li> </ul> |                |                  |                 |                 |           |

| bit 5-4             | T1CKPS<1:0                                                                                                                                                                                                          | >: Timer1 Inpu                                                                                                                                                                                                                                                                                     | t Clock Presca | ale Select bits  |                 |                 |           |

|                     | 10 = 1:4 Pres<br>01 = 1:2 Pres                                                                                                                                                                                      | 11 = 1:8 Prescale Value<br>10 = 1:4 Prescale Value<br>01 = 1:2 Prescale Value<br>00 = 1:1 Prescale Value                                                                                                                                                                                           |                |                  |                 |                 |           |

| bit 3               | T1OSCEN: L                                                                                                                                                                                                          | P Oscillator En                                                                                                                                                                                                                                                                                    | able Control b | it               |                 |                 |           |

|                     | If INTOSC without CLKOUT oscillator is active:<br>1 = LP oscillator is enabled for Timer1 clock<br>0 = LP oscillator is off<br>For all other system clock modes:<br>This bit is ignored. LP oscillator is disabled. |                                                                                                                                                                                                                                                                                                    |                |                  |                 |                 |           |

| bit 2               |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                    | lock Input Syr | chronization C   | ontrol bit      |                 |           |

|                     | 1 = Do not sy<br>0 = Synchron<br><u>TMR1CS = 0</u> :                                                                                                                                                                | <u>TMR1CS = 1:</u><br>1 = Do not synchronize external clock input<br>0 = Synchronize external clock input<br><u>TMR1CS = 0:</u><br>This bit is ignored. Timer1 uses the internal clock                                                                                                             |                |                  |                 |                 |           |

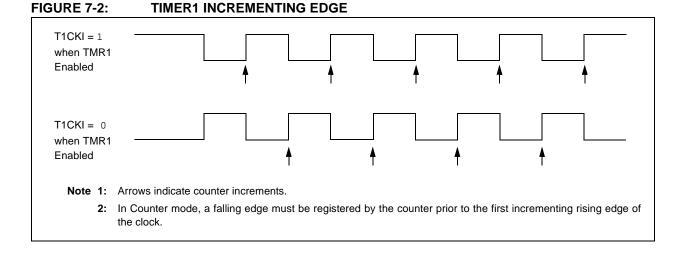

| bit 1               | TMR1CS: Timer1 Clock Source Select bit                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                    |                |                  |                 |                 |           |

|                     | 1 = External clock from T1CKI pin (on the rising edge)<br>0 = Internal clock (Fosc/4) or system clock (Fosc) <sup>(3)</sup>                                                                                         |                                                                                                                                                                                                                                                                                                    |                |                  |                 |                 |           |

| bit 0               | 1 = Enables T                                                                                                                                                                                                       | TMR1ON: Timer1 On bit<br>1 = Enables Timer1<br>0 = Stops Timer1                                                                                                                                                                                                                                    |                |                  |                 |                 |           |

| 2:                  | T1GINV bit inverts the Timer1 gate logic, regardless of source.<br>TMR1GE bit must be set to use either $\overline{T1G}$ pin or COUT, as selected by the T1GSS bit of the 0<br>register, as a Timer1 gate source.   |                                                                                                                                                                                                                                                                                                    |                |                  |                 |                 | ne CMCON1 |

**3:** See T1ACS bit in CMCON1 register.

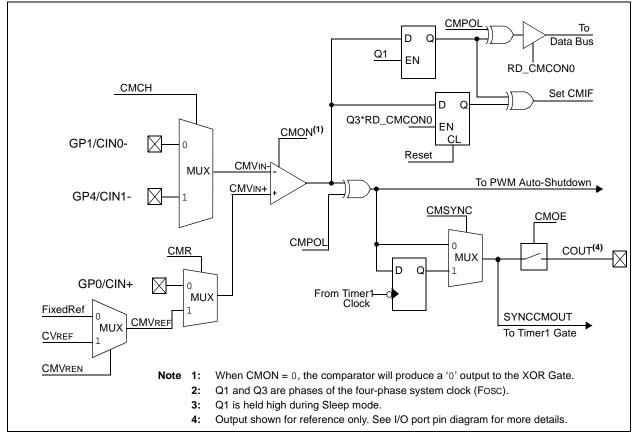

### 9.0 COMPARATOR MODULE

The comparator can be used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparator is a very useful mixed signal building block because it provides analog functionality independent of the program execution. The Analog Comparator module includes the following features:

- Programmable input section

- · Comparator output is available internally/externally

- Programmable output polarity

- Interrupt-on-change

- · Wake-up from Sleep

- PWM shutdown

- Timer1 gate (count enable)

- Output synchronization to Timer1 clock input

- Programmable voltage reference

- User-enable Comparator Hysteresis

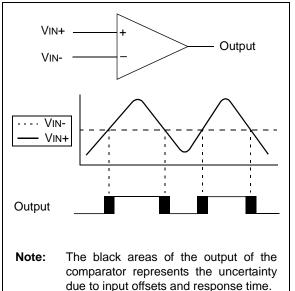

#### 9.1 Comparator Overview

The comparator is shown in Figure 9-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less

than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

#### **FIGURE 9-1:SINGLE COMPARATOR**

els and the

#### FIGURE 9-2: COMPARATOR SIMPLIFIED BLOCK DIAGRAM

## TABLE 9-2:SUMMARY OF REGISTERS ASSOCIATED WITH THE COMPARATOR AND<br/>VOLTAGE REFERENCE MODULES

| Name   | Bit 7  | Bit 6                | Bit 5                 | Bit 4                | Bit 3   | Bit 2               | Bit 1                 | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|--------|----------------------|-----------------------|----------------------|---------|---------------------|-----------------------|---------|----------------------|---------------------------------|

| ANSEL  | _      | ADCS2 <sup>(1)</sup> | ADCS1 <sup>(1)</sup>  | ADCS0 <sup>(1)</sup> | ANS3    | ANS2 <sup>(1)</sup> | ANS1                  | ANS0    | -000 1111            | -000 1111                       |

| CMCON0 | CMON   | COUT                 | CMOE                  | CMPOL                | _       | CMR                 | _                     | CMCH    | 0000 -000            | 0000 -000                       |

| CMCON1 | _      | _                    | _                     | T1ACS                | CMHYS   | —                   | T1GSS                 | CMSYNC  | 0000 0000            | 0000 0000                       |

| INTCON | GIE    | PEIE                 | T0IE                  | INTE                 | GPIE    | T0IF                | INTF                  | GPIF    | 0000 000x            | 0000 000x                       |

| PIE1   | _      | ADIE <sup>(1)</sup>  | CCP1IE <sup>(1)</sup> | _                    | CMIE    | —                   | TMR2IE <sup>(1)</sup> | TMR1IE  | -00-0-00             | -00-0-00                        |

| PIR1   | _      | ADIF <sup>(1)</sup>  | CCP1IF <sup>(1)</sup> | _                    | CMIF    | —                   | TMR2IF <sup>(1)</sup> | TMR1IF  | -00-0-00             | -00-0-00                        |

| GPIO   | _      | _                    | GP5                   | GP4                  | GP3     | GP2                 | GP1                   | GP0     | xx xxxx              | uu uuuu                         |

| TRISIO | _      | _                    | TRISIO5               | TRISIO4              | TRISIO3 | TRISIO2             | TRISIO1               | TRISIO0 | 11 1111              | 11 1111                         |

| VRCON  | CMVREN |                      | VRR                   | FVREN                | VR3     | VR2                 | VR1                   | VR0     | 0-00 0000            | 0-00 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for comparator.

**Note 1:** For PIC12F615/617/HV615 only.

### 12.0 SPECIAL FEATURES OF THE CPU

The PIC12F609/615/617/12HV609/615 has a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving features and offer code protection.

These features are:

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Oscillator selection

- Sleep

- Code protection

- ID Locations

- In-Circuit Serial Programming

The PIC12F609/615/617/12HV609/615 has two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 64 ms (nominal) on power-up only, designed to keep the part in Reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which can use the Power-up Timer to provide at least a 64 ms Reset. With these three functions-on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through:

- External Reset

- Watchdog Timer Wake-up

- An interrupt

Several oscillator options are also made available to allow the part to fit the application. The INTOSC option saves system cost while the LP crystal option saves power. A set of Configuration bits are used to select various options (see Register 12-1).

### 12.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations as shown in Register 12-1. These bits are mapped in program memory location 2007h.

**Note:** Address 2007h is beyond the user program memory space. It belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See *Memory Programming Specification* (DS41204) for more information.

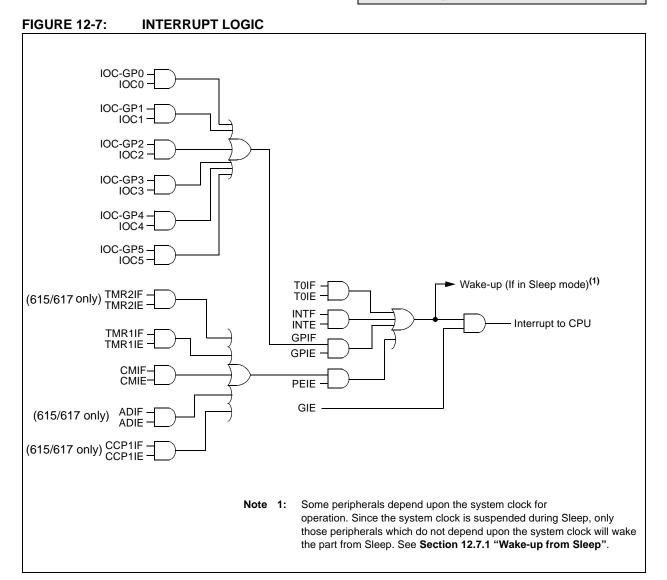

#### 12.4.2 TIMER0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF bit of the INTCON register. The interrupt can be enabled/disabled by setting/clearing T0IE bit of the INTCON register. See **Section 6.0 "Timer0 Module"** for operation of the Timer0 module.

#### 12.4.3 GPIO INTERRUPT-ON-CHANGE

An input change on GPIO sets the GPIF bit of the INTCON register. The interrupt can be enabled/ disabled by setting/clearing the GPIE bit of the INTCON register. Plus, individual pins can be configured through the IOC register.

Note: If a change on the I/O pin should occur when any GPIO operation is being executed, then the GPIF interrupt flag may not get set.

| SUBWF            | Subtract W                                                      | from f                                                                                                                       |

|------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SU                                                      | JBWF f,d                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$ |                                                                                                                              |

| Operation:       | (f) - (W) $\rightarrow$ (                                       | destination)                                                                                                                 |

| Status Affected: | C, DC, Z                                                        |                                                                                                                              |

| Description:     | W register f<br>'0', the resu<br>register. If 'd                | s complement method)<br>rom register 'f'. If 'd' is<br>It is stored in the W<br>d' is '1', the result is<br>in register 'f'. |

|                  | <b>C</b> = 0                                                    | W > f                                                                                                                        |

|                  | <b>C</b> = 1                                                    | $W \leq f$                                                                                                                   |

DC = 0

**DC** = 1

W<3:0> > f<3:0>

W<3:0> ≤ f<3:0>

| XORWF            | Exclusive OR W with f                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORWF f,d                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                 |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                               |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                     |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |

| Status Affected: | None                                                                                                                                                                   |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |

| XORLW            | Exclusive OR literal with W                                                                                                |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                   |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |  |  |  |  |  |

| Status Affected: | Z                                                                                                                          |  |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |  |  |

| DC CHA                       | RACTERISTICS                                     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |     |       |            |                                               |  |

|------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|------------|-----------------------------------------------|--|

| Param Device Characteristics |                                                  | Min                                                                                                                               | Тур† | Мах | Units | Conditions |                                               |  |

| No.                          |                                                  |                                                                                                                                   |      | VDD | Note  |            |                                               |  |

| D020E                        | Power-down Base                                  |                                                                                                                                   | 135  | 200 | μA    | 2.0        | WDT, BOR, Comparator, VREF and                |  |

|                              | Current (IPD) <sup>(2,3)</sup><br>PIC12HV609/615 |                                                                                                                                   | 210  | 280 | μA    | 3.0        | T1OSC disabled                                |  |

|                              |                                                  |                                                                                                                                   | 260  | 350 | μA    | 4.5        |                                               |  |

| D021E                        |                                                  |                                                                                                                                   | 135  | 200 | μA    | 2.0        | WDT Current <sup>(1)</sup>                    |  |

|                              |                                                  |                                                                                                                                   | 210  | 285 | μΑ    | 3.0        |                                               |  |

|                              |                                                  |                                                                                                                                   | 265  | 360 | μΑ    | 4.5        |                                               |  |

| D022E                        |                                                  |                                                                                                                                   | 215  | 285 | μA    | 3.0        | BOR Current <sup>(1)</sup>                    |  |

|                              |                                                  |                                                                                                                                   | 265  | 360 | μΑ    | 4.5        |                                               |  |

| D023E                        |                                                  | _                                                                                                                                 | 185  | 280 | μΑ    | 2.0        | Comparator Current <sup>(1)</sup> , single    |  |

|                              |                                                  |                                                                                                                                   | 265  | 360 | μA    | 3.0        | comparator enabled                            |  |

|                              |                                                  |                                                                                                                                   | 320  | 430 | μΑ    | 4.5        |                                               |  |

| D024E                        |                                                  |                                                                                                                                   | 165  | 235 | μA    | 2.0        | CVREF Current <sup>(1)</sup> (high range)     |  |

|                              |                                                  |                                                                                                                                   | 255  | 330 | μA    | 3.0        |                                               |  |

|                              |                                                  |                                                                                                                                   | 330  | 430 | μA    | 4.5        |                                               |  |

| D025E*                       |                                                  |                                                                                                                                   | 175  | 245 | μA    | 2.0        | CVREF Current <sup>(1)</sup> (low range)      |  |

|                              |                                                  |                                                                                                                                   | 275  | 350 | μA    | 3.0        |                                               |  |

|                              |                                                  |                                                                                                                                   | 355  | 450 | μA    | 4.5        |                                               |  |

| D026E                        |                                                  |                                                                                                                                   | 140  | 205 | μA    | 2.0        | T1OSC Current <sup>(1)</sup> , 32.768 kHz     |  |

|                              |                                                  |                                                                                                                                   | 220  | 290 | μA    | 3.0        | 7                                             |  |

|                              |                                                  |                                                                                                                                   | 270  | 360 | μA    | 4.5        |                                               |  |

| D027E                        |                                                  |                                                                                                                                   | 210  | 280 | μA    | 3.0        | A/D Current <sup>(1)</sup> , no conversion in |  |

|                              |                                                  |                                                                                                                                   | 260  | 350 | μΑ    | 4.5        | progress                                      |  |

#### 16.7 DC Characteristics: PIC12HV609/615-E (Extended)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 4.5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

**2:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

3: Shunt regulator is always on and always draws operating current.

| Param<br>No. | Device<br>Characteristics | Units | Min | Тур   |      | Condition |                     |  |

|--------------|---------------------------|-------|-----|-------|------|-----------|---------------------|--|

|              |                           |       |     |       | Max  | Vdd       | Note                |  |

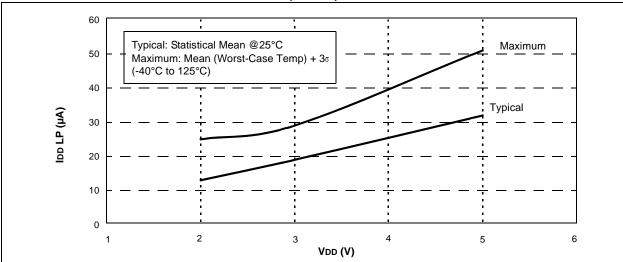

| D010         |                           | μΑ    | _   | 13    | 58   | 2.0       |                     |  |

|              | Supply Current (IDD)      |       | _   | 19    | 67   | 3.0       | IDD LP OSC (32 kHz) |  |

|              |                           |       | _   | 32    | 92   | 5.0       |                     |  |

| D011         |                           | μΑ    |     | 135   | 316  | 2.0       |                     |  |

|              |                           |       | _   | 185   | 400  | 3.0       | IDD XT OSC (1 MHz)  |  |

|              |                           |       | _   | 300   | 537  | 5.0       |                     |  |

| D012         |                           |       | _   | 240   | 495  | 2.0       |                     |  |

|              |                           | μA    | _   | 360   | 680  | 3.0       | IDD XT OSC (4 MHz)  |  |

|              |                           | mA    | _   | 0.660 | 1.20 | 5.0       |                     |  |

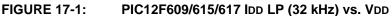

| D013         |                           |       | _   | 75    | 158  | 2.0       |                     |  |

|              |                           | μΑ    | _   | 155   | 338  | 3.0       | IDD EC OSC (1 MHz)  |  |

|              |                           |       | _   | 345   | 792  | 5.0       |                     |  |

| D014         |                           | μA    | _   | 185   | 357  | 2.0       |                     |  |

|              |                           |       |     | 325   | 625  | 3.0       | IDD EC OSC (4 MHz)  |  |

|              |                           | mA    | _   | 0.665 | 1.30 | 5.0       |                     |  |

| D016         |                           |       |     | 245   | 476  | 2.0       |                     |  |

|              |                           | μA    | _   | 360   | 672  | 3.0       | IDD INTOSC (4 MHz)  |  |

|              |                           |       | _   | 620   | 1.10 | 5.0       |                     |  |

| D017         | 17                        | μΑ    | _   | 395   | 757  | 2.0       |                     |  |

|              |                           | mA    |     | 0.620 | 1.20 | 3.0       | IDD INTOSC (8 MHz)  |  |

|              |                           |       |     | 1.20  | 2.20 | 5.0       |                     |  |

| D018         |                           | μΑ    |     | 175   | 332  | 2.0       |                     |  |

|              |                           |       |     | 285   | 518  | 3.0       | IDD EXTRC (4 MHz)   |  |

|              |                           |       |     | 530   | 972  | 5.0       |                     |  |

| D019         |                           | mA    |     | 2.20  | 4.10 | 4.5       | IDD HS OSC (20 MHz) |  |

|              |                           |       |     | 2.80  | 4.80 | 5.0       |                     |  |

#### TABLE 16-14: DC CHARACTERISTICS FOR IDD SPECIFICATIONS FOR PIC12F615-H (High Temp.)

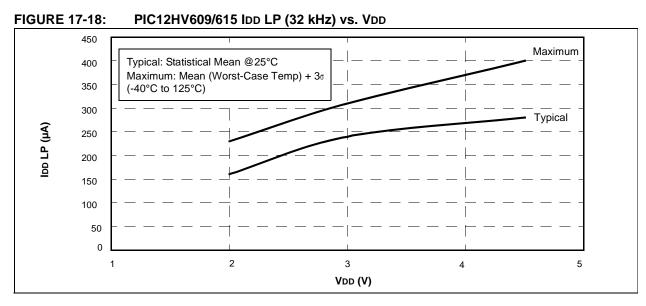

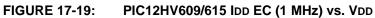

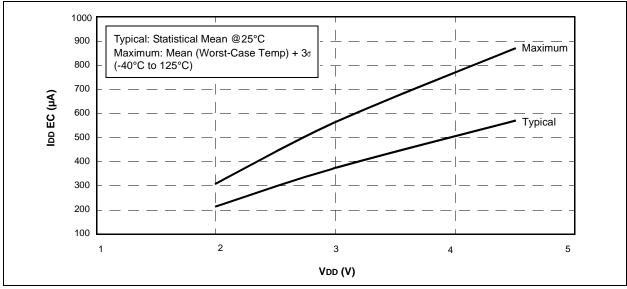

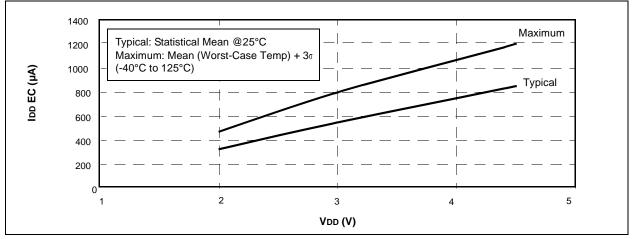

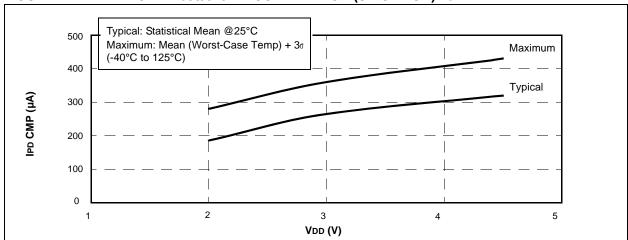

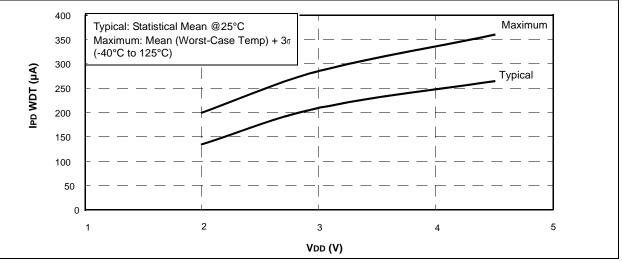

## 17.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

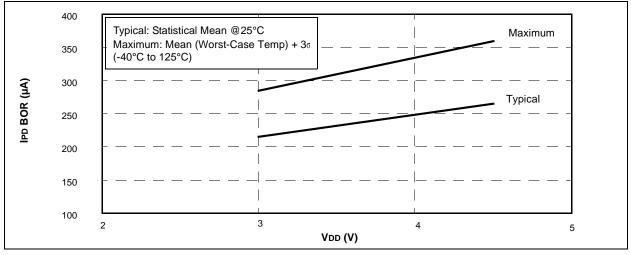

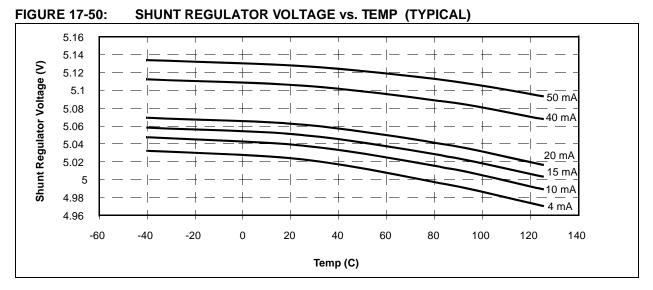

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where s is a standard deviation, over each temperature range.

#### FIGURE 17-27: PIC12HV609/615 IPD COMPARATOR (SINGLE ON) vs. VDD

NOTES:

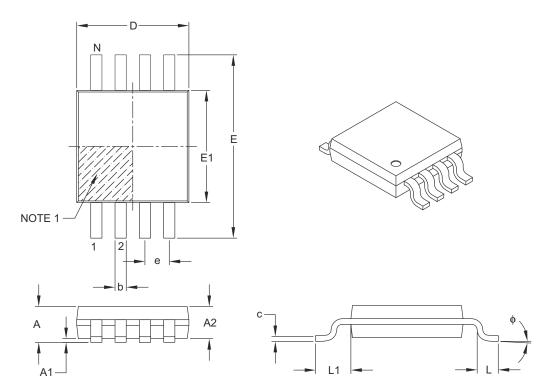

### 8-Lead Plastic Micro Small Outline Package (MS) [MSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |      |      |  |

|--------------------------|------------------|-------------|------|------|--|

|                          | Dimension Limits | MIN         | NOM  | MAX  |  |

| Number of Pins           | N                | 8           |      |      |  |

| Pitch                    | е                | 0.65 BSC    |      |      |  |

| Overall Height           | A                | -           | -    | 1.10 |  |

| Molded Package Thickness | A2               | 0.75        | 0.85 | 0.95 |  |

| Standoff                 | A1               | 0.00        | -    | 0.15 |  |

| Overall Width            | E                | 4.90 BSC    |      |      |  |

| Molded Package Width     | E1               | 3.00 BSC    |      |      |  |

| Overall Length           | D                | 3.00 BSC    |      |      |  |

| Foot Length              | L                | 0.40        | 0.60 | 0.80 |  |

| Footprint                | L1               | 0.95 REF    |      |      |  |

| Foot Angle               | φ                | 0°          | -    | 8°   |  |

| Lead Thickness           | С                | 0.08        | -    | 0.23 |  |

| Lead Width               | b                | 0.22        | -    | 0.40 |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-111B

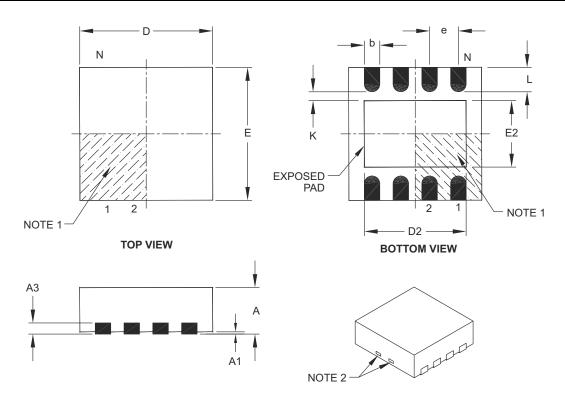

### 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units    | MILLIMETERS |      |      |  |

|------------------------|----------|-------------|------|------|--|

| Dimensio               | n Limits | MIN         | NOM  | MAX  |  |

| Number of Pins         | Ν        | 8           |      |      |  |

| Pitch                  | е        | 0.80 BSC    |      |      |  |

| Overall Height         | А        | 0.80        | 0.90 | 1.00 |  |

| Standoff               | A1       | 0.00        | 0.02 | 0.05 |  |

| Contact Thickness      | A3       | 0.20 REF    |      |      |  |

| Overall Length         | D        | 4.00 BSC    |      |      |  |

| Exposed Pad Width      | E2       | 0.00        | 2.20 | 2.80 |  |

| Overall Width          | E        | 4.00 BSC    |      |      |  |

| Exposed Pad Length     | D2       | 0.00        | 3.00 | 3.60 |  |

| Contact Width          | b        | 0.25        | 0.30 | 0.35 |  |

| Contact Length         | L        | 0.30        | 0.40 | 0.50 |  |

| Contact-to-Exposed Pad | K        | 0.20        | -    | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-131D

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com