Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 4x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-TSSOP, 8-MSOP (0.118", 3.00mm Width)                                   |

| Supplier Device Package    | 8-MSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f615-i-ms |

### MICROCHIP PIC12F609/615/617/12HV609/615

#### 8-Pin Flash-Based, 8-Bit CMOS Microcontrollers

#### **High-Performance RISC CPU:**

- Only 35 Instructions to Learn:

- All single-cycle instructions except branches

- Operating Speed:

- DC 20 MHz oscillator/clock input

- DC 200 ns instruction cycle

- Interrupt Capability

- 8-Level Deep Hardware Stack

- · Direct, Indirect and Relative Addressing modes

#### **Special Microcontroller Features:**

- · Precision Internal Oscillator:

- Factory calibrated to ±1%, typical

- Software selectable frequency: 4 MHz or 8 MHz

- · Power-Saving Sleep mode

- · Voltage Range:

- PIC12F609/615/617: 2.0V to 5.5V

- PIC12HV609/615: 2.0V to user defined maximum (see note)

- Industrial and Extended Temperature Range

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Watchdog Timer (WDT) with independent Oscillator for Reliable Operation

- Multiplexed Master Clear with Pull-up/Input Pin

- Programmable Code Protection

- · High Endurance Flash:

- 100.000 write Flash endurance

- Flash retention: > 40 years

- Self Read/ Write Program Memory (PIC12F617 only)

#### Low-Power Features:

- · Standby Current:

- 50 nA @ 2.0V, typical

- Operating Current:

- 11 μA @ 32 kHz, 2.0V, typical

- 260 μA @ 4 MHz, 2.0V, typical

- Watchdog Timer Current:

- 1 μA @ 2.0V, typical

**Note:** Voltage across the shunt regulator should not exceed 5V.

#### **Peripheral Features:**

- Shunt Voltage Regulator (PIC12HV609/615 only):

- 5 volt regulation

- 4 mA to 50 mA shunt range

- 5 I/O Pins and 1 Input Only

- High Current Source/Sink for Direct LED Drive

- Interrupt-on-pin change or pins

- Individually programmable weak pull-ups

- Analog Comparator module with:

- One analog comparator

- Programmable on-chip voltage reference (CVREF) module (% of VDD)

- Comparator inputs and output externally accessible

- Built-In Hysteresis (software selectable)

- Timer0: 8-Bit Timer/Counter with 8-Bit Programmable Prescaler

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Timer1 Gate (count enable)

- Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator if INTOSC mode selected

- Option to use system clock as Timer1

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

#### PIC12F615/617/HV615 ONLY:

- Enhanced Capture, Compare, PWM module:

- 16-bit Capture, max. resolution 12.5 ns

- Compare, max. resolution 200 ns

- 10-bit PWM with 1 or 2 output channels, 1 output channel programmable "dead time," max. frequency 20 kHz, auto-shutdown

- A/D Converter:

- 10-bit resolution and 4 channels, samples internal voltage references

- Timer2: 8-Bit Timer/Counter with 8-Bit Period Register, Prescaler and Postscaler

#### 2.0 MEMORY ORGANIZATION

#### 2.1 Program Memory Organization

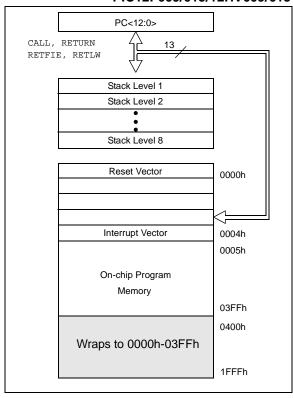

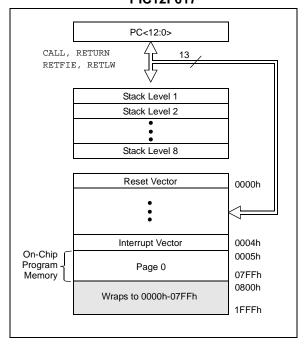

The PIC12F609/615/617/12HV609/615 has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (0000h-03FFh) for the PIC12F609/615/12HV609/615 is physically implemented. For the PIC12F617, the first 2K x 14 (0000h-07FFh) is physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 1K x 14 space for PIC12F609/615/12HV609/615 devices, and within the first 2K x 14 space for the PIC12F617 device. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 2-1).

FIGURE 2-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC12F609/615/12HV609/615

FIGURE 2-2: PROGRAM MEMORY MAP

AND STACK FOR THE

PIC12F617

#### 2.2 Data Memory Organization

The data memory (see Figure 2-3) is partitioned into two banks, which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). The Special Function Registers are located in the first 32 locations of each bank. Register locations 40h-7Fh in Bank 0 are General Purpose Registers, implemented as static RAM. For the PIC12F617, the register locations 20h-7Fh in Bank 0 and A0h-EFh in Bank 1 are general purpose registers implemented as Static RAM. Register locations F0h-FFh in Bank 1 point to addresses 70h-7Fh in Bank 0. All other RAM is unimplemented and returns '0' when read. The RP0 bit of the STATUS register is the bank select bit.

#### RP0

- 0 → Bank 0 is selected

- 1 → Bank 1 is selected

**Note:** The IRP and RP1 bits of the STATUS register are reserved and should always be maintained as '0's.

TABLE 2-1: PIC12F609/HV609 SPECIAL FUNCTION REGISTERS SUMMARY BANK 0

| IADE   | L Z-1.          | TICIZI 009/TV003 SI EGIAL I GNOTION REGISTERS SOMMART BANK O                |                    |               |                |               |                | _            |          |                   |         |

|--------|-----------------|-----------------------------------------------------------------------------|--------------------|---------------|----------------|---------------|----------------|--------------|----------|-------------------|---------|

| Addr   | Name            | Bit 7                                                                       | Bit 6              | Bit 5         | Bit 4          | Bit 3         | Bit 2          | Bit 1        | Bit 0    | Value on POR, BOR | Page    |

| Bank 0 | ank 0           |                                                                             |                    |               |                |               |                |              |          |                   |         |

| 00h    | INDF            | Addressing                                                                  | this location      | uses content  | s of FSR to a  | address data  | memory (not    | a physical r | egister) | xxxx xxxx         | 25, 115 |

| 01h    | TMR0            | Timer0 Mod                                                                  | ule's Registe      | er            |                |               |                |              |          | xxxx xxxx         | 53, 115 |

| 02h    | PCL             | Program Co                                                                  | unter's (PC)       | Least Signifi | cant Byte      |               |                |              |          | 0000 0000         | 25, 115 |

| 03h    | STATUS          | IRP <sup>(1)</sup>                                                          | RP1 <sup>(1)</sup> | RP0           | TO             | PD            | Z              | DC           | С        | 0001 1xxx         | 18, 115 |

| 04h    | FSR             | Indirect Data                                                               | a Memory Ad        | dress Pointe  | er             |               |                |              |          | xxxx xxxx         | 25, 115 |

| 05h    | GPIO            | _                                                                           | _                  | GP5           | GP4            | GP3           | GP2            | GP1          | GP0      | x0 x000           | 43, 115 |

| 06h    | _               | Unimplemen                                                                  | nted               |               |                |               |                |              |          | _                 | _       |

| 07h    | _               | Unimplemen                                                                  | nted               |               |                |               |                |              |          | _                 | _       |

| 08h    | _               | Unimplemen                                                                  | nted               |               |                |               |                |              |          | _                 | _       |

| 09h    | _               | Unimplemen                                                                  | nted               |               |                |               |                |              |          | _                 | _       |

| 0Ah    | PCLATH          | _                                                                           | _                  | _             | Write          | Buffer for up | oper 5 bits of | Program Co   | unter    | 0 0000            | 25, 115 |

| 0Bh    | INTCON          | GIE                                                                         | PEIE               | T0IE          | INTE           | GPIE          | T0IF           | INTF         | GPIF     | 0000 0000         | 20, 115 |

| 0Ch    | PIR1            | _                                                                           | _                  | _             | _              | CMIF          | _              | _            | TMR1IF   | 00                | 22, 115 |

| 0Dh    | _               | Unimplemented                                                               |                    |               |                |               |                |              |          | _                 | _       |

| 0Eh    | TMR1L           | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                    |               |                |               |                |              |          | xxxx xxxx         | 57, 115 |

| 0Fh    | TMR1H           | Holding Reg                                                                 | gister for the     | Most Signific | ant Byte of th | ne 16-bit TMF | R1 Register    |              |          | xxxx xxxx         | 57, 115 |

| 10h    | T1CON           | T1GINV                                                                      | TMR1GE             | T1CKPS1       | T1CKPS0        | T10SCEN       | T1SYNC         | TMR1CS       | TMR10N   | 0000 0000         | 62, 115 |

| 11h    | _               | Unimplemen                                                                  | nted               |               |                |               |                |              |          | _                 | _       |

| 12h    | _               | Unimplemen                                                                  | nted               |               |                |               |                |              |          | _                 | _       |

| 13h    | _               | Unimplemen                                                                  | nted               |               |                |               |                |              |          | _                 | I       |

| 14h    | _               | Unimplemen                                                                  | nted               |               |                |               |                |              |          | _                 | _       |

| 15h    | _               | Unimplemen                                                                  | nted               |               |                |               |                |              |          | _                 | _       |

| 16h    | _               | Unimplemen                                                                  | nted               |               |                |               |                |              |          | _                 | I       |

| 17h    | _               | Unimplemen                                                                  | nted               |               |                |               |                |              |          | _                 | I       |

| 18h    | _               | Unimplemen                                                                  | nted               |               |                |               |                |              |          | _                 | I       |

| 19h    | VRCON           | CMVREN                                                                      | _                  | VRR           | FVREN          | VR3           | VR2            | VR1          | VR0      | 0-00 0000         | 76, 116 |

| 1Ah    | CMCON0          | CMON                                                                        | COUT               | CMOE          | CMPOL          |               | CMR            |              | CMCH     | 0000 -0-0         | 72, 116 |

| 1Bh    |                 |                                                                             |                    |               |                |               |                |              |          | _                 |         |

| 1Ch    | CMCON1          | _                                                                           | _                  | _             | T1ACS          | CMHYS         | _              | T1GSS        | CMSYNC   | 0 0-10            | 73, 116 |

| 1Dh    | _               | Unimplemented                                                               |                    |               |                |               |                | _            | _        |                   |         |

| 1Eh    | — Unimplemented |                                                                             |                    |               |                |               |                | _            | _        |                   |         |

| 1Fh    | — Unimplemented |                                                                             |                    |               |                |               |                |              | _        | _                 |         |

|        |                 |                                                                             |                    |               |                |               |                |              |          |                   |         |

$\textbf{Legend:} \qquad -= \text{Unimplemented locations read as '0'}, \ u = \text{unchanged}, \ x = \text{unknown}, \ q = \text{value depends on condition}, \ shaded = \text{unimplemented locations}, \$

<sup>1:</sup> IRP and RP1 bits are reserved, always maintain these bits clear.

<sup>2:</sup> Read only register.

TABLE 2-2: PIC12F615/617/HV615 SPECIAL FUNCTION REGISTERS SUMMARY BANK 0

| Addr   | Name                   | Bit 7              | Bit 6                                                                                    | Bit 5          | Bit 4            | Bit 3         | Bit 2          | Bit 1         | Bit 0    | Value on POR, BOR | Page        |

|--------|------------------------|--------------------|------------------------------------------------------------------------------------------|----------------|------------------|---------------|----------------|---------------|----------|-------------------|-------------|

| Bank 0 |                        |                    |                                                                                          |                |                  |               |                |               |          |                   |             |

| 00h    | INDF                   | Addressing         | this location                                                                            | uses content   | s of FSR to a    | ddress data   | memory (not    | a physical re | egister) | xxxx xxxx         | 25, 116     |

| 01h    | TMR0                   | Timer0 Mod         | ule's Registe                                                                            | r              |                  |               |                |               |          | xxxx xxxx         | 53, 116     |

| 02h    | PCL                    | Program Co         | unter's (PC)                                                                             | Least Signifi  | cant Byte        |               |                | 5.            |          | 0000 0000         | 25, 116     |

| 03h    | STATUS                 | IRP <sup>(1)</sup> | RP1 <sup>(1)</sup>                                                                       | RP0            | TO               | PD            | Z              | DC            | С        | 0001 1xxx         | 18, 116     |

| 04h    | FSR                    | Indirect Data      | a Memory Ad                                                                              | ldress Pointe  | er               |               |                |               |          | xxxx xxxx         | 25, 116     |

| 05h    | GPIO                   | -                  | 1                                                                                        | GP5            | GP4              | GP3           | GP2            | GP1           | GP0      | x0 x000           | 43, 116     |

| 06h    | _                      | Unimplemen         | nted                                                                                     |                |                  |               |                |               |          | _                 | _           |

| 07h    | _                      | Unimplemen         | nted                                                                                     |                |                  |               |                |               |          | _                 | _           |

| 08h    | _                      | Unimplemen         | nted                                                                                     |                |                  |               |                |               |          | _                 | _           |

| 09h    | _                      | Unimplemen         | nted                                                                                     |                |                  |               |                |               |          | _                 | _           |

| 0Ah    | PCLATH                 | -                  | 1                                                                                        | _              | Write            | Buffer for up | oper 5 bits of | Program Co    | unter    | 0 0000            | 25, 116     |

| 0Bh    | INTCON                 | GIE                | PEIE                                                                                     | TOIE           | INTE             | GPIE          | TOIF           | INTF          | GPIF     | 0000 0000         | 20, 116     |

| 0Ch    | PIR1                   | -                  | ADIF                                                                                     | CCP1IF         | _                | CMIF          | ı              | TMR2IF        | TMR1IF   | -00- 0-00         | 22, 116     |

| 0Dh    | _                      | Unimplemen         | nted                                                                                     |                |                  |               |                |               |          | _                 | _           |

| 0Eh    | TMR1L                  | Holding Reg        | ister for the I                                                                          | Least Signific | cant Byte of the | ne 16-bit TM  | R1 Register    |               |          | xxxx xxxx         | 57, 116     |

| 0Fh    | TMR1H                  | Holding Reg        | ister for the I                                                                          | Most Signific  | ant Byte of th   | e 16-bit TMF  | R1 Register    |               |          | xxxx xxxx         | 57, 116     |

| 10h    | T1CON                  | T1GINV             | TMR1GE                                                                                   | T1CKPS1        | T1CKPS0          | T10SCEN       | T1SYNC         | TMR1CS        | TMR10N   | 0000 0000         | 62, 116     |

| 11h    | TMR2 <sup>(3)</sup>    | Timer2 Mod         | ule Register                                                                             |                |                  |               |                |               |          | 0000 0000         | 65, 116     |

| 12h    | T2CON <sup>(3)</sup>   | _                  | TOUTPS3                                                                                  | TOUTPS2        | TOUTPS1          | TOUTPS0       | TMR2ON         | T2CKPS1       | T2CKPS0  | -000 0000         | 66, 116     |

| 13h    | CCPR1L <sup>(3)</sup>  | Capture/Cor        | mpare/PWM                                                                                | Register 1 Lo  | ow Byte          |               |                |               |          | XXXX XXXX         | 90, 116     |

| 14h    | CCPR1H <sup>(3)</sup>  | Capture/Cor        | mpare/PWM                                                                                | Register 1 H   | igh Byte         |               |                |               |          | XXXX XXXX         | 90, 116     |

| 15h    | CCP1CON <sup>(3)</sup> | P1M                | -                                                                                        | DC1B1          | DC1B0            | CCP1M3        | CCP1M2         | CCP1M1        | CCP1M0   | 0-00 0000         | 89, 116     |

| 16h    | PWM1CON <sup>(3)</sup> | PRSEN              | PDC6                                                                                     | PDC5           | PDC4             | PDC3          | PDC2           | PDC1          | PDC0     | 0000 0000         | 105,<br>116 |

| 17h    | ECCPAS <sup>(3)</sup>  | ECCPASE            | ECCPAS2                                                                                  | ECCPAS1        | ECCPAS0          | PSSAC1        | PSSAC0         | PSSBD1        | PSSBD0   | 0000 0000         | 102,<br>116 |

| 18h    | _                      | Unimplemented      |                                                                                          |                |                  |               |                |               | _        | _                 |             |

| 19h    | VRCON                  | CMVREN             | _                                                                                        | VRR            | FVREN            | VR3           | VR2            | VR1           | VR0      | 0-00 0000         | 76, 116     |

| 1Ah    | CMCON0                 | CMON               | COUT                                                                                     | CMOE           | CMPOL            | _             | CMR            | _             | CMCH     | 0000 -0-0         | 72, 116     |

| 1Bh    |                        |                    |                                                                                          |                |                  |               |                | _             |          |                   | _           |

| 1Ch    | CMCON1                 | _                  |                                                                                          |                | T1ACS            | CMHYS         |                | T1GSS         | CMSYNC   | 0 0-10            | 73, 116     |

| 1Dh    |                        | Unimplemented —    |                                                                                          |                |                  |               |                |               | _        | _                 |             |

| 1Eh    | ADRESH(2, 3)           | Most Signific      | Most Significant 8 bits of the left shifted A/D result or 2 bits of right shifted result |                |                  |               |                |               |          | xxxx xxxx         | 85, 116     |

| 1Fh    | ADCON0 <sup>(3)</sup>  | ADFM               | VCFG                                                                                     | _              | CHS2             | CHS1          | CHS0           | GO/DONE       | ADON     | 00-0 0000         | 84, 116     |

$\textbf{Legend:} \qquad -= \text{Unimplemented locations read as '0', } \\ \textbf{u} = \text{unchanged, } \\ \textbf{x} = \text{unknown, } \\ \textbf{q} = \text{value depends on condition, shaded} = \text{unimplemented locations read as '0', } \\ \textbf{u} = \text{unchanged, } \\ \textbf{x} = \text{unknown, } \\ \textbf{q} = \text{value depends on condition, shaded} = \text{unimplemented locations read as '0', } \\ \textbf{u} = \text{unchanged, } \\ \textbf{x} = \text{unknown, } \\ \textbf{q} = \text{value depends on condition, shaded} = \text{unimplemented locations read as '0', } \\ \textbf{u} = \text{unchanged, } \\ \textbf{x} = \text{unknown, } \\ \textbf{q} = \text{value depends on condition, shaded} = \text{unimplemented locations read as '0', } \\ \textbf{u} = \text{unchanged, } \\ \textbf{x} = \text{unknown, } \\ \textbf{q} = \text{value depends on condition, shaded} = \text{unimplemented locations read as '0', } \\ \textbf{u} = \text{unchanged, } \\ \textbf{u} = \text{$

Note 1: IRP and RP1 bits are reserved, always maintain these bits clear.

- 2: Read only register.

- 3: PIC12F615/617/HV615 only.

**TABLE 2-4:** PIC12F615/617/HV615 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

| .,,,   |                          |                    | 13/01//11                                                                                | V 0 1 3 31    | LOIALI         | 0.100.                 |                |               |                     |                   |         |

|--------|--------------------------|--------------------|------------------------------------------------------------------------------------------|---------------|----------------|------------------------|----------------|---------------|---------------------|-------------------|---------|

| Addr   | Name                     | Bit 7              | Bit 6                                                                                    | Bit 5         | Bit 4          | Bit 3                  | Bit 2          | Bit 1         | Bit 0               | Value on POR, BOR | Page    |

| Bank 1 | Bank 1                   |                    |                                                                                          |               |                |                        |                |               |                     |                   |         |

| 80h    | INDF                     | Addressing         | this location                                                                            | uses content  | ts of FSR to a | ddress data            | memory (not    | a physical re | gister)             | xxxx xxxx         | 25, 116 |

| 81h    | OPTION_REG               | GPPU               | INTEDG                                                                                   | T0CS          | T0SE           | PSA                    | PS2            | PS1           | PS0                 | 1111 1111         | 19, 116 |

| 82h    | PCL                      |                    | unter's (PC)                                                                             | Least Signifi | cant Byte      |                        |                |               |                     | 0000 0000         | 25, 116 |

| 83h    | STATUS                   | IRP <sup>(1)</sup> | RP1 <sup>(1)</sup>                                                                       | RP0           | TO             | PD                     | Z              | DC            | С                   | 0001 1xxx         | 18, 116 |

| 84h    | FSR                      | Indirect Data      | a Memory Ac                                                                              | dress Pointe  | er             |                        |                |               |                     | xxxx xxxx         | 25, 116 |

| 85h    | TRISIO                   | _                  | _                                                                                        | TRISIO5       | TRISIO4        | TRISIO3 <sup>(4)</sup> | TRISIO2        | TRISIO1       | TRISIO0             | 11 1111           | 44, 116 |

| 86h    | _                        | Unimplemen         | nted                                                                                     |               |                |                        |                |               |                     | _                 | _       |

| 87h    | _                        | Unimplemen         | nted                                                                                     |               |                |                        |                |               |                     | _                 | _       |

| 88h    | _                        | Unimplemen         | nted                                                                                     |               |                |                        |                |               |                     | _                 | _       |

| 89h    | _                        | Unimplemen         | nted                                                                                     |               |                |                        |                |               |                     | _                 | _       |

| 8Ah    | PCLATH                   | _                  | -                                                                                        | _             | Writ           | e Buffer for u         | pper 5 bits of | Program Cou   | unter               | 0 0000            | 25, 116 |

| 8Bh    | INTCON                   | GIE                | PEIE                                                                                     | T0IE          | INTE           | GPIE                   | TOIF           | INTF          | GPIF <sup>(3)</sup> | 0000 0000         | 20, 116 |

| 8Ch    | PIE1                     | _                  | ADIE                                                                                     | CCP1IE        | _              | CMIE                   | _              | TMR2IE        | TMR1IE              | -00- 0-00         | 21, 116 |

| 8Dh    | _                        | Unimplemen         | nted                                                                                     |               |                |                        |                |               |                     | _                 | _       |

| 8Eh    | PCON                     | _                  | -                                                                                        | _             | _              | _                      | _              | POR           | BOR                 | qq                | 23, 116 |

| 8Fh    | _                        | Unimplemen         | nted                                                                                     |               |                |                        |                |               |                     | _                 | _       |

| 90h    | OSCTUNE                  | _                  | -                                                                                        | _             | TUN4           | TUN3                   | TUN2           | TUN1          | TUN0                | 0 0000            | 41, 116 |

| 91h    | _                        | Unimplemen         | nted                                                                                     |               |                |                        |                |               |                     | _                 | _       |

| 92h    | PR2                      | Timer2 Mod         | ule Period R                                                                             | egister       |                |                        |                |               |                     | 1111 1111         | 65, 116 |

| 93h    | APFCON                   | _                  | -                                                                                        | _             | T1GSEL         | _                      | _              | P1BSEL        | P1ASEL              | 000               | 21, 116 |

| 94h    | _                        | Unimplemen         | nted                                                                                     |               |                |                        |                |               |                     | _                 | _       |

| 95h    | WPU <sup>(2)</sup>       | 1                  | I                                                                                        | WPU5          | WPU4           | ı                      | WPU2           | WPU1          | WPU0                | 11 -111           | 46, 116 |

| 96h    | IOC                      | _                  | -                                                                                        | IOC5          | IOC4           | IOC3                   | IOC2           | IOC1          | IOC0                | 00 0000           | 46, 116 |

| 97h    | _                        | Unimplemen         | nted                                                                                     |               |                |                        |                |               |                     | _                 | _       |

| 98h    | PMCON1 <sup>(7)</sup>    | _                  | -                                                                                        | _             | _              | _                      | WREN           | WR            | RD                  | 000               | 29      |

| 99h    | PMCON2 <sup>(7)</sup>    | Program Me         | Program Memory Control Register 2 (not a physical register).                             |               |                |                        |                |               |                     |                   | _       |

| 9Ah    | PMADRL <sup>(7)</sup>    | PMADRL7            | PMADRL6                                                                                  | PMADRL5       | PMADRL4        | PMADRL3                | PMADRL2        | PMADRL1       | PMADRL0             | 0000 0000         | 28      |

| 9Bh    | PMADRH <sup>(7)</sup>    | 1                  | I                                                                                        | ı             | _              | ı                      | PMADRH2        | PMADRH1       | PMADRH0             | 000               | 28      |

| 9Ch    | PMDATL <sup>(7)</sup>    | PMDATL7            | PMDATL6                                                                                  | PMDATL5       | PMDATL4        | PMDATL3                | PMDATL2        | PMDATL1       | PMDATL0             | 0000 0000         | 28      |

| 9Dh    | PMDATH <sup>(7)</sup>    | _                  | — — Program Memory Data Register High Byte.                                              |               |                |                        |                |               |                     | 00 0000           | 28      |

| 9Eh    | ADRESL <sup>(5, 6)</sup> | Least Signif       | east Significant 2 bits of the left shifted result or 8 bits of the right shifted result |               |                |                        |                |               |                     | xxxx xxxx         | 85, 117 |

| 9Fh    | ANSEL                    | _                  | ADCS2                                                                                    | ADCS1         | ADCS0          | ANS3                   | ANS2           | ANS1          | ANS0                | -000 1111         | 45, 117 |

Legend: - = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

IRP and RP1 bits are reserved, always maintain these bits clear.

GP3 pull-up is enabled when MCLRE is '1' in the Configuration Word register.

MCLR and WDT Reset does not affect the previous value data latch. The GPIF bit will clear upon Reset but will set again if the mismatch 3:

- TRISIO3 always reads as '1' since it is an input only pin.

- Read only register. 5:

- PIC12F615/617/HV615 only. 6:

- PIC12F617 only.

#### 2.2.2.2 OPTION Register

The OPTION register is a readable and writable register, which contains various control bits to configure:

- Timer0/WDT prescaler

- External GP2/INT interrupt

- Timer0

- Weak pull-ups on GPIO

Note: To achieve a 1:1 prescaler assignment for Timer0, assign the prescaler to the WDT by setting PSA bit to '1' of the OPTION register. See Section 6.1.3 "Software Programmable Prescaler".

#### REGISTER 2-2: OPTION\_REG: OPTION REGISTER

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| GPPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | GPPU: GPIO Pull-up Enable bit                                 |

|---------|---------------------------------------------------------------|

|         | 1 = GPIO pull-ups are disabled                                |

|         | 0 = GPIO pull-ups are enabled by individual PORT latch values |

| bit 6   | INTEDG: Interrupt Edge Select bit                             |

|         | 1 = Interrupt on rising edge of GP2/INT pin                   |

|         | 0 = Interrupt on falling edge of GP2/INT pin                  |

| bit 5   | T0CS: Timer0 Clock Source Select bit                          |

|         | 1 = Transition on GP2/T0CKI pin                               |

|         | 0 = Internal instruction cycle clock (Fosc/4)                 |

| bit 4   | T0SE: Timer0 Source Edge Select bit                           |

|         | 1 = Increment on high-to-low transition on GP2/T0CKI pin      |

|         | 0 = Increment on low-to-high transition on GP2/T0CKI pin      |

| bit 3   | PSA: Prescaler Assignment bit                                 |

|         | 1 = Prescaler is assigned to the WDT                          |

|         | 0 = Prescaler is assigned to the Timer0 module                |

| bit 2-0 | PS<2:0>: Prescaler Rate Select bits                           |

| BIT VALUE | TIMERO RATE                                   | WDT RATE                                                            |

|-----------|-----------------------------------------------|---------------------------------------------------------------------|

| 000       | 1:2                                           | 1:1                                                                 |

| 001       | 1:4                                           | 1:2                                                                 |

| 010       | 1:8                                           | 1:4                                                                 |

| 011       | 1:16                                          | 1:8                                                                 |

| 100       | 1:32                                          | 1:16                                                                |

| 101       | 1:64                                          | 1:32                                                                |

| 110       | 1:128                                         | 1:64                                                                |

| 111       | 1:256                                         | 1:128                                                               |

|           | 000<br>001<br>010<br>011<br>100<br>101<br>110 | 001 1:4<br>010 1:8<br>011 1:16<br>100 1:32<br>101 1:64<br>110 1:128 |

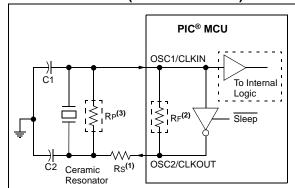

#### 4.3.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 4-3). The mode selects a low, medium or high gain setting of the internal inverteramplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 4-3 and Figure 4-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

FIGURE 4-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

- Note 1: A series resistor (Rs) may be required for quartz crystals with low drive level.

- 2: The value of RF varies with the Oscillator mode selected (typically between 2 M $\Omega$  to 10 M $\Omega$ ).

- **Note 1:** Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC® Oscillator Design" (DS00849)

- AN943, "Practical PIC® Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

# FIGURE 4-4: CERAMIC RESONATOR OPERATION (XT OR HS MODE)

- Note 1: A series resistor (Rs) may be required for ceramic resonators with low drive level.

- 2: The value of RF varies with the Oscillator mode selected (typically between 2 M $\Omega$  to 10 M $\Omega$ ).

- An additional parallel feedback resistor (RP) may be required for proper ceramic resonator operation.

TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

| Name                  | Bit 7                                                                          | Bit 6               | Bit 5                 | Bit 4   | Bit 3   | Bit 2  | Bit 1                 | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|--------------------------------------------------------------------------------|---------------------|-----------------------|---------|---------|--------|-----------------------|-----------|----------------------|---------------------------------|

| APFCON <sup>(1)</sup> | 1                                                                              | _                   | _                     | T1GSEL  | _       | _      | P1BSEL                | P1ASEL    | 000                  | 000                             |

| CMCON0                | CMON                                                                           | COUT                | CMOE                  | CMPOL   | ı       | CMR    | I                     | CMCH      | 0000 -0-0            | 0000 -0-0                       |

| CMCON1                | I                                                                              | _                   |                       | T1ACS   | CMHYS   |        | T1GSS                 | CMSYNC    | 0 0-10               | 0 0-10                          |

| INTCON                | GIE                                                                            | PEIE                | TOIE                  | INTE    | GPIE    | TOIF   | INTF                  | GPIF      | 0000 000x            | 0000 000x                       |

| PIE1                  | I                                                                              | ADIE <sup>(1)</sup> | CCP1IE <sup>(1)</sup> | I       | CMIE    |        | TMR2IE <sup>(1)</sup> | TMR1IE    | -00- 0-00            | -00- 0-00                       |

| PIR1                  | I                                                                              | ADIF <sup>(1)</sup> | CCP1IF <sup>(1)</sup> | I       | CMIF    |        | TMR2IF <sup>(1)</sup> | TMR1IF    | -00- 0-00            | -00- 0-00                       |

| TMR1H                 | R1H Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |                     |                       |         |         |        |                       |           | xxxx xxxx            | uuuu uuuu                       |

| TMR1L                 | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register    |                     |                       |         |         |        |                       | xxxx xxxx | uuuu uuuu            |                                 |

| T1CON                 | T1GINV                                                                         | TMR1GE              | T1CKPS1               | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS                | TMR10N    | 0000 0000            | uuuu uuuu                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: PIC12F615/617/HV615 only.

#### 11.4 PWM (Enhanced Mode)

The Enhanced PWM Mode can generate a PWM signal on up to four different output pins with up to 10-bits of resolution. It can do this through four different PWM output modes:

- Single PWM

- Half-Bridge PWM

To select an Enhanced PWM mode, the P1M bits of the CCP1CON register must be set appropriately.

The PWM outputs are multiplexed with I/O pins and are designated P1A and P1B. The polarity of the PWM pins is configurable and is selected by setting the CCP1M bits in the CCP1CON register appropriately.

Table 11-6 shows the pin assignments for each Enhanced PWM mode.

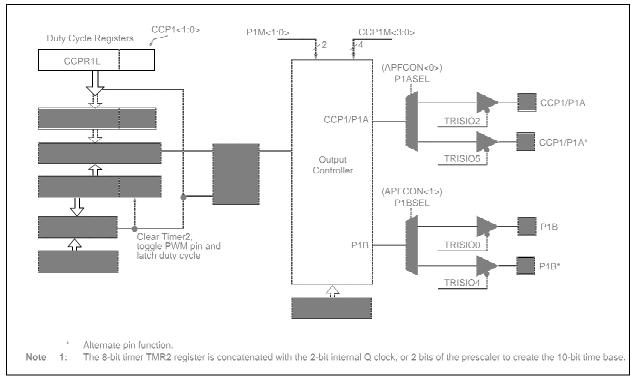

Figure 11-5 shows an example of a simplified block diagram of the Enhanced PWM module.

Note: To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

#### FIGURE 11-5: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

- **Note 1:** The TRIS register value for each PWM output must be configured appropriately.

- 2: Clearing the CCP1CON register will relinquish ECCP control of all PWM output pins.

- 3: Any pin not used by an Enhanced PWM mode is available for alternate pin functions.

TABLE 11-6: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES

| ECCP Mode   | P1M<1:0> | CCP1/P1A           | P1B                |

|-------------|----------|--------------------|--------------------|

| Single      | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge | 10       | Yes                | Yes                |

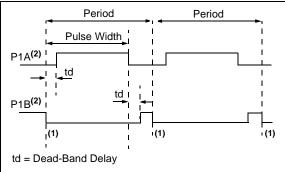

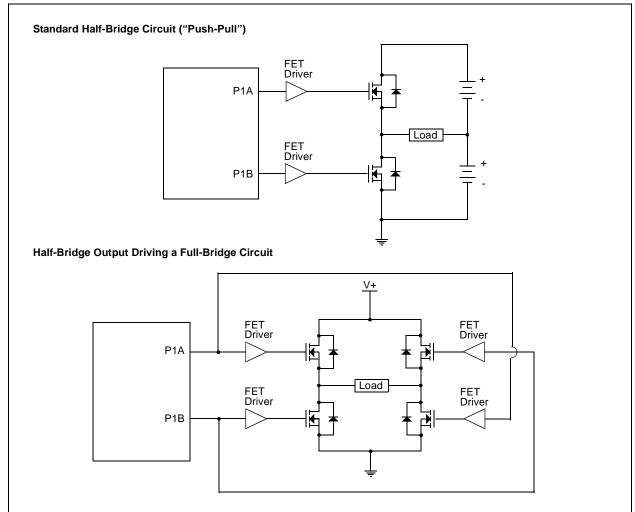

#### 11.4.1 HALF-BRIDGE MODE

In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the CCP1/P1A pin, while the complementary PWM output signal is output on the P1B pin (see Figure 11-8). This mode can be used for Half-Bridge applications, as shown in Figure 11-9, or for Full-Bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge mode, the programmable dead-band delay can be used to prevent shoot-through current in Half-Bridge power devices. The value of the PDC<6:0> bits of the PWM1CON register sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See Section 11.4.6 "Programmable Dead-Band Delay mode" for more details of the dead-band delay operations.

Since the P1A and P1B outputs are multiplexed with the PORT data latches, the associated TRIS bits must be cleared to configure P1A and P1B as outputs.

FIGURE 11-8: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

Note 1: At this time, the TMR2 register is equal to the PR2 register.

2: Output signals are shown as active-high.

FIGURE 11-9: EXAMPLE OF HALF-BRIDGE APPLICATIONS

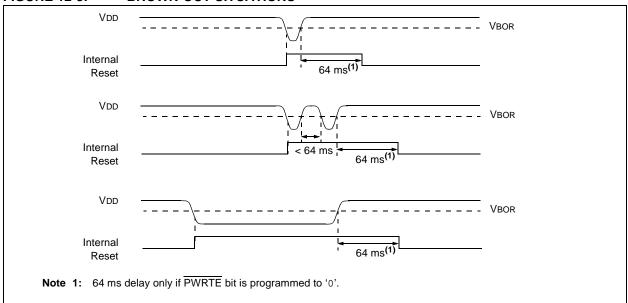

#### 12.3.4 BROWN-OUT RESET (BOR)

The BOREN0 and BOREN1 bits in the Configuration Word register select one of three BOR modes. One mode has been added to allow control of the BOR enable for lower current during Sleep. By selecting BOREN<1:0> = 10, the BOR is automatically disabled in Sleep to conserve power and enabled on wake-up. See Register 12-1 for the Configuration Word definition.

A brown-out occurs when VDD falls below VBOR for greater than parameter TBOR (see **Section 16.0** "**Electrical Specifications**"). The brown-out condition will reset the device. This will occur regardless of VDD slew rate. A Brown-out Reset may not occur if VDD falls below VBOR for less than parameter TBOR.

On any Reset (Power-on, Brown-out Reset, Watchdog timer, etc.), the chip will remain in Reset until VDD rises above VBOR (see Figure 12-3). If enabled, the Power-up Timer will be invoked by the Reset and keep the chip in Reset an additional 64 ms.

Note: The Power-up Timer is enabled by the PWRTE bit in the Configuration Word register.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

#### FIGURE 12-3: BROWN-OUT SITUATIONS

TABLE 12-5: INITIALIZATION CONDITION FOR REGISTERS (PIC12F615/617/HV615)

| Register               | Address | Power-on Reset | MCLR Reset<br>WDT Reset<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep through<br>Interrupt<br>Wake-up from Sleep through<br>WDT Time-out |

|------------------------|---------|----------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------|

| W                      |         | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| INDF                   | 00h/80h | xxxx xxxx      | xxxx xxxx                                                 | uuuu uuuu                                                                             |

| TMR0                   | 01h     | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| PCL                    | 02h/82h | 0000 0000      | 0000 0000                                                 | PC + 1 <sup>(3)</sup>                                                                 |

| STATUS                 | 03h/83h | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                  | uuuq quuu <sup>(4)</sup>                                                              |

| FSR                    | 04h/84h | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| GPIO                   | 05h     | x0 x000        | u0 u000                                                   | uu uuuu                                                                               |

| PCLATH                 | 0Ah/8Ah | 0 0000         | 0 0000                                                    | u uuuu                                                                                |

| INTCON                 | 0Bh/8Bh | 0000 0000      | 0000 0000                                                 | uuuu uuuu <sup>(2)</sup>                                                              |

| PIR1                   | 0Ch     | -000 0-00      | -000 0-00                                                 | -uuu u-uu <b>(2)</b>                                                                  |

| TMR1L                  | 0Eh     | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| TMR1H                  | 0Fh     | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| T1CON                  | 10h     | 0000 0000      | uuuu uuuu                                                 | -uuu uuuu                                                                             |

| TMR2 <sup>(1)</sup>    | 11h     | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| T2CON <sup>(1)</sup>   | 12h     | -000 0000      | -000 0000                                                 | -uuu uuuu                                                                             |

| CCPR1L <sup>(1)</sup>  | 13h     | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| CCPR1H <sup>(1)</sup>  | 14h     | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| CCP1CON <sup>(1)</sup> | 15h     | 0-00 0000      | 0-00 0000                                                 | u-uu uuuu                                                                             |

| PWM1CON <sup>(1)</sup> | 16h     | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| ECCPAS <sup>(1)</sup>  | 17h     | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| VRCON                  | 19h     | 0-00 0000      | 0-00 0000                                                 | u-uu uuuu                                                                             |

| CMCON0                 | 1Ah     | 0000 -0-0      | 0000 -0-0                                                 | uuuu -u-u                                                                             |

| CMCON1                 | 1Ch     | 0 0-10         | 0 0-10                                                    | u u-qu                                                                                |

| ADRESH <sup>(1)</sup>  | 1Eh     | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| ADCON0 <sup>(1)</sup>  | 1Fh     | 00-0 0000      | 00-0 0000                                                 | uu-u uuuu                                                                             |

| OPTION_REG             | 81h     | 1111 1111      | 1111 1111                                                 | uuuu uuuu                                                                             |

| TRISIO                 | 85h     | 11 1111        | 11 1111                                                   | uu uuuu                                                                               |

| PIE1                   | 8Ch     | -00- 0-00      | -00- 0-00                                                 | -uu- u-uu                                                                             |

| PCON                   | 8Eh     | 0x             | (1, 5)                                                    | uu                                                                                    |

| OSCTUNE                | 90h     | 0 0000         | u uuuu                                                    | u uuuu                                                                                |

| PR2                    | 92h     | 1111 1111      | 1111 1111                                                 | 1111 1111                                                                             |

| APFCON                 | 93h     | 000            | 000                                                       | uuu                                                                                   |

| WPU                    | 95h     | 11 -111        | 11 -111                                                   | uu -uuu                                                                               |

| IOC                    | 96h     | 00 0000        | 00 0000                                                   | uu uuuu                                                                               |

| PMCON1 <sup>(6)</sup>  | 98h     | 000            | 000                                                       | uuu                                                                                   |

| PMCON2 <sup>(6)</sup>  | 99h     |                |                                                           |                                                                                       |

| PMADRL <sup>(6)</sup>  | 9Ah     | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

**Legend:** u = unchanged, x = unknown, -= unimplemented bit, reads as '0', <math>q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

- 2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

- 3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 4: See Table 12-6 for Reset value for specific condition.

- 5: If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

- **6:** For PIC12F617 only.

#### 12.7 Power-Down Mode (Sleep)

The Power-Down mode is entered by executing a SLEEP instruction.

If the Watchdog Timer is enabled:

- · WDT will be cleared but keeps running.

- PD bit in the STATUS register is cleared.

- TO bit is set.

- Oscillator driver is turned off.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or high-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or Vss, with no external circuitry drawing current from the I/O pin and the comparators and CVREF should be disabled. I/O pins that are high-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pullups on GPIO should be considered.

The MCLR pin must be at a logic high level.

Note: It should be noted that a Reset generated by a WDT time-out does not drive MCLR pin low.

#### 12.7.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin.

- Watchdog Timer wake-up (if WDT was enabled).

- Interrupt from GP2/INT pin, GPIO change or a peripheral interrupt.

The first event will cause a device Reset. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. TO bit is cleared if WDT wake-up occurred.

The following peripheral interrupts can wake the device from Sleep:

- Timer1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. ECCP Capture mode interrupt.

- 3. A/D conversion (when A/D clock source is RC).

- 4. Comparator output changes state.

- 5. Interrupt-on-change.

- 6. External Interrupt from INT pin.

Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction, then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

Note: If the global interrupts are disabled (GIE is cleared) and any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from Sleep.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

#### 12.7.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will not be cleared, the TO bit will not be set and the PD bit will not be cleared.

- If the interrupt occurs **during or after** the execution of a SLEEP instruction, the device will Immediately wake-up from Sleep. The SLEEP instruction is executed. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will be cleared, the  $\overline{\text{TO}}$  bit will be set and the  $\overline{\text{PD}}$  bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction. See Figure 12-9 for more details.

#### 16.12 High Temperature Operation

This section outlines the specifications for the <u>PIC12F615 device operating in a temperature range between -40°C and 150°C. (4)</u> The specifications between -40°C and 150°C (4) are identical to those shown in DS41288 and DS80329.

- **Note 1:** Writes are <u>not allowed</u> for Flash Program Memory above 125°C.

- **2:** All AC timing specifications are increased by 30%. This derating factor will include parameters such as TPWRT.

- 3: The temperature range indicator in the part number is "H" for -40°C to 150°C. (4)

- Example: PIC12F615T-H/ST indicates the device is shipped in a TAPE and reel configuration, in the MSOP package, and is rated for operation from -40°C to 150°C. (4)

- 4: AEC-Q100 reliability testing for devices intended to operate at 150°C is 1,000 hours. Any design in which the total operating time from 125°C to 150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

TABLE 16-13: ABSOLUTE MAXIMUM RATINGS

| Parameter                    | Source/Sink | Value | Units |

|------------------------------|-------------|-------|-------|

| Max. Current: VDD            | Source      | 20    | mA    |

| Max. Current: Vss            | Sink        | 50    | mA    |

| Max. Current: PIN            | Source      | 5     | mA    |

| Max. Current: PIN            | Sink        | 10    | mA    |

| Pin Current: at VOH          | Source      | 3     | mA    |

| Pin Current: at VoL          | Sink        | 8.5   | mA    |

| Port Current: GPIO           | Source      | 20    | mA    |

| Port Current: GPIO           | Sink        | 50    | mA    |

| Maximum Junction Temperature |             | 155   | °C    |

**Note:** Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

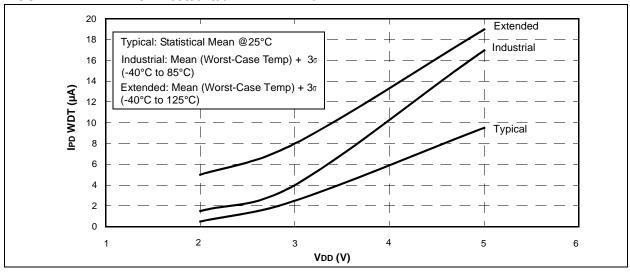

FIGURE 17-12: PIC12F609/615/617 IPD WDT vs. VDD

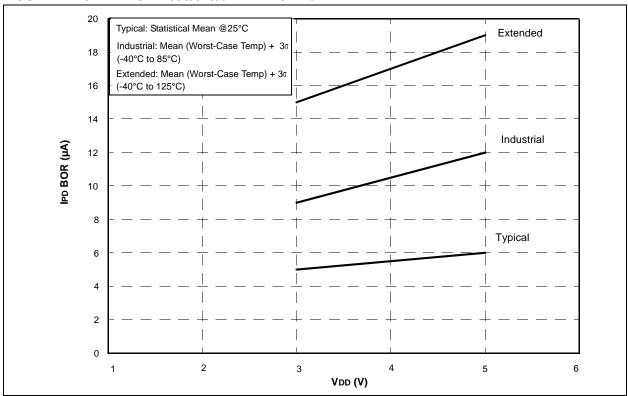

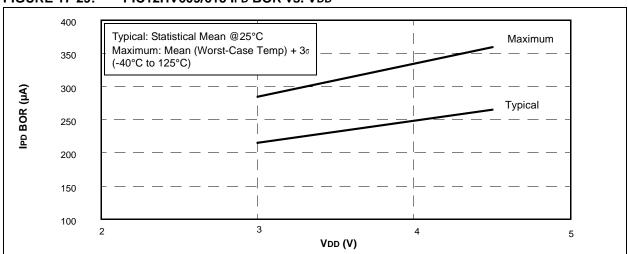

FIGURE 17-13: PIC12F609/615/617 IPD BOR vs. VDD

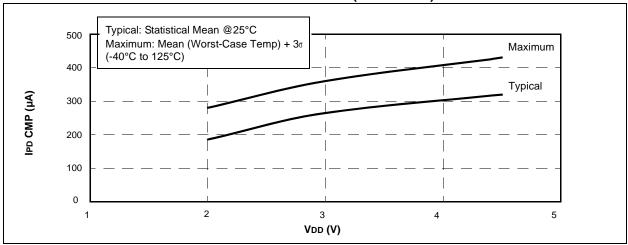

FIGURE 17-27: PIC12HV609/615 IPD COMPARATOR (SINGLE ON) vs. VDD

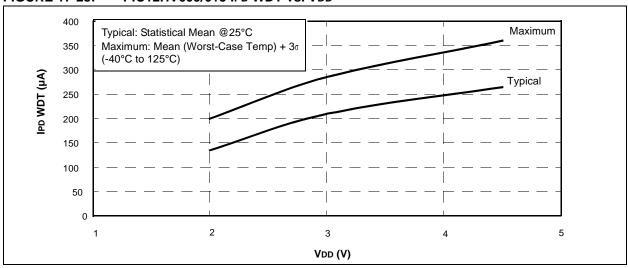

FIGURE 17-28: PIC12HV609/615 IPD WDT vs. VDD

FIGURE 17-29: PIC12HV609/615 IPD BOR vs. VDD

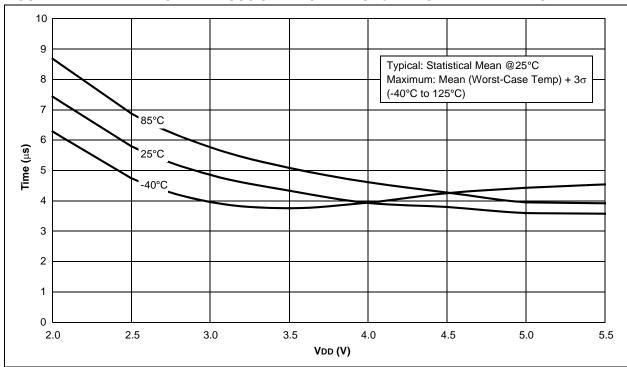

FIGURE 17-41: MAXIMUM HFINTOSC START-UP TIMES vs. VDD OVER TEMPERATURE

FIGURE 17-42: MINIMUM HFINTOSC START-UP TIMES vs. VDD OVER TEMPERATURE

#### **INDEX**

| A                                            |          | PIC12F609/12HV609                             | 7      |

|----------------------------------------------|----------|-----------------------------------------------|--------|

| A/D                                          |          | PIC12F615/617/12HV615                         |        |

| Specifications                               | 164, 165 | PWM (Enhanced)                                |        |

| Absolute Maximum Ratings                     |          | Resonator Operation                           |        |

| AC Characteristics                           |          | Timer1                                        | 57, 58 |

| Industrial and Extended                      | 156      | Timer2                                        |        |

| Load Conditions                              |          | TMR0/WDT Prescaler                            | 53     |

| ADC                                          |          | Watchdog Timer                                |        |

| Acquisition Requirements                     | 86       | Brown-out Reset (BOR)                         | 112    |

| Associated registers                         |          | Associated Registers                          | 113    |

| Block Diagram                                |          | Specifications                                | 160    |

| Calculating Acquisition Time                 |          | Timing and Characteristics                    | 159    |

| Channel Selection                            |          | •                                             |        |

| Configuration                                |          | С                                             |        |

| •                                            |          | C Compilers                                   |        |

| Configuring Interrupt Conversion Clock       |          | MPLAB C18                                     | 140    |

| Conversion Procedure                         |          | MPLAB C30                                     | 140    |

| Internal Sampling Switch (Rss) Impedance     |          | Calibration Bits                              | 109    |

|                                              |          | Capture Module. See Enhanced Capture/Compare/ |        |

| Interrupts<br>Operation                      |          | PWM (ECCP)                                    |        |

| ·                                            |          | Capture/Compare/PWM (CCP)                     |        |

| Operation During Sleep                       |          | Associated registers w/ Capture               | 91     |

| Port Configuration                           |          | Associated registers w/ Compare               | 93     |

| Reference Voltage (VREF)                     |          | Associated registers w/ PWM                   | 105    |

| Result Formatting                            |          | Capture Mode                                  | 90     |

| Source Impedance                             |          | CCP1 Pin Configuration                        |        |

| Special Event Trigger                        |          | Compare Mode                                  |        |

| Starting an A/D Conversion                   |          | CCP1 Pin Configuration                        | 92     |

| ADC (PIC12F615/617/HV615 Only)               |          | Software Interrupt Mode                       |        |

| ADCON0 Register                              |          | Special Event Trigger                         |        |

| ADRESH Register (ADFM = 0)                   |          | Timer1 Mode Selection                         |        |

| ADRESH Register (ADFM = 1)                   |          | Prescaler                                     | 90     |

| ADRESL Register (ADFM = 0)                   |          | PWM Mode                                      | 94     |

| ADRESL Register (ADFM = 1)                   |          | Duty Cycle                                    | 95     |

| Analog Input Connection Considerations       | 68       | Effects of Reset                              |        |

| Analog-to-Digital Converter. See ADC         |          | Example PWM Frequencies and                   |        |

| ANSEL Register (PIC12F609/HV609)             |          | Resolutions, 20 MHZ                           | 95     |

| ANSEL Register (PIC12F615/617/HV615)         |          | Example PWM Frequencies and                   |        |

| APFCON Register                              | 24       | Resolutions, 8 MHz                            | 95     |

| Assembler                                    | 4.40     | Operation in Sleep Mode                       |        |

| MPASM Assembler                              | 140      | Setup for Operation                           |        |

| В                                            |          | System Clock Frequency Changes                |        |

|                                              |          | PWM Period                                    |        |

| Block Diagrams (CCR) Continue Mode Operation | 00       | Setup for PWM Operation                       | 96     |

| (CCP) Capture Mode Operation                 |          | CCP1CON (Enhanced) Register                   |        |

| ADC Transfer Function                        |          | Clock Sources                                 |        |

| ADC Transfer Function                        |          | External Modes                                | 38     |

| Analog Input Model                           |          | EC                                            |        |

| Auto-Shutdown                                | _        | HS                                            | 39     |

| CCP PWM                                      |          | LP                                            | 39     |

| Clock Source                                 |          | OST                                           |        |

| Comparator                                   |          | RC                                            |        |

| Compare                                      |          | XT                                            |        |

| Crystal Operation                            |          | Internal Modes                                |        |

| External RC Mode                             |          | INTOSC                                        | 40     |

| GP0 and GP1 Pins                             |          | INTOSCIO                                      |        |

| GP2 Pins                                     |          | CMCON0 Register                               |        |

| GP3 Pin                                      |          | CMCON1 Register                               |        |

| GP4 Pin                                      |          | Code Examples                                 |        |

| GP5 Pin                                      |          | A/D Conversion                                | 83     |

| In-Circuit Serial Programming Connections    |          | Assigning Prescaler to Timer0                 |        |

| Interrupt Logic                              |          | Assigning Prescaler to WDT                    |        |

| MCLR Circuit                                 |          | Changing Between Capture Prescalers           |        |

| On-Chip Reset Circuit                        | 110      | Indirect Addressing                           |        |

|                                              |          |                                               | = 0    |

#### WORLDWIDE SALES AND SERVICE

#### **AMERICAS**

Corporate Office

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277

Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca. IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario, Canada

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### **ASIA/PACIFIC**

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2401-1200

Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755