# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64 × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-VDFN Exposed Pad                                                        |

| Supplier Device Package    | 8-DFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f615t-i-md |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                                                                   | 7   |

|-------|---------------------------------------------------------------------------------------------------|-----|

| 2.0   | Memory Organization                                                                               |     |

| 3.0   | Flash Program Memory Self Read/Self Write Control (PIC12F617 only)                                | 27  |

| 4.0   | Oscillator Module                                                                                 | 37  |

| 5.0   | I/O Port                                                                                          | 43  |

| 6.0   | Timer0 Module                                                                                     | 53  |

| 7.0   | Timer1 Module with Gate Control                                                                   | 57  |

| 8.0   | Timer2 Module (PIC12F615/617/HV615 only)                                                          | 65  |

| 9.0   | Comparator Module                                                                                 |     |

| 10.0  | Analog-to-Digital Converter (ADC) Module (PIC12F615/617/HV615 only)                               | 79  |

| 11.0  | Enhanced Capture/Compare/PWM (With Auto-Shutdown and Dead Band) Module (PIC12F615/617/HV615 only) | 89  |

| 12.0  | Special Features of the CPU                                                                       | 107 |

| 13.0  | Voltage Regulator                                                                                 | 127 |

| 14.0  | Instruction Set Summary                                                                           | 129 |

| 15.0  | Development Support                                                                               |     |

| 16.0  | Electrical Specifications                                                                         | 143 |

| 17.0  | DC and AC Characteristics Graphs and Tables                                                       | 171 |

| 18.0  | Packaging Information                                                                             | 195 |

|       | ndix A: Data Sheet Revision History                                                               |     |

| Appe  | ndix B: Migrating from other PIC <sup>®</sup> Devices                                             | 203 |

| Index | <                                                                                                 | 205 |

| The N | /icrochip Web Site                                                                                | 209 |

| Custo | mer Change Notification Service                                                                   | 209 |

| Custo | mer Support                                                                                       | 209 |

| Read  | er Response                                                                                       | 210 |

| Produ | uct Identification System                                                                         | 211 |

| World | lwide Sales and Service                                                                           | 212 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

# Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

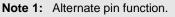

# 5.2.4.6 GP5/T1CKI/P1A<sup>(1, 2)</sup>/OSC1/CLKIN

Figure 5-5 shows the diagram for this pin. The GP5 pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 clock input

- PWM output, alternate pin<sup>(1, 2)</sup>

- a crystal/resonator connection

- a clock input

2: PIC12F615/617/HV615 only.

# FIGURE 5-5: BLOCK DIAGRAM OF GP5

# 7.12 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 7-1, is used to control Timer1 and select the various features of the Timer1 module.

### REGISTER 7-1: T1CON: TIMER 1 CONTROL REGISTER

| R/W-0               | R/W-0                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                   | R/W-0                  | R/W-0            | R/W-0           | R/W-0           | R/W-0     |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------|-----------------|-----------------|-----------|--|

| T1GINV <sup>(</sup> | <sup>1)</sup> TMR1GE <sup>(2)</sup>                                                                                                                                                                                   | T1CKPS1                                                                                                                                                                                                                                 | T1CKPS0                | T1OSCEN          | T1SYNC          | TMR1CS          | TMR10N    |  |

| bit 7               |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                         |                        | •                |                 | •               | bit 0     |  |

|                     |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                         |                        |                  |                 |                 |           |  |

| Legend:             |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                         |                        |                  |                 |                 |           |  |

| R = Readable bit    |                                                                                                                                                                                                                       | W = Writable                                                                                                                                                                                                                            | bit                    | U = Unimpler     | nented bit, rea | d as '0'        |           |  |

| -n = Value          | at POR                                                                                                                                                                                                                | '1' = Bit is set                                                                                                                                                                                                                        |                        | '0' = Bit is cle | ared            | x = Bit is unkr | nown      |  |

| bit 7               | 1 = Timer1 ga                                                                                                                                                                                                         |                                                                                                                                                                                                                                         | h (Timer1 cou          | nts when gate    | • •             |                 |           |  |

| bit 6               | TMR1GE: Tin<br><u>If TMR1ON =</u><br>This bit is igno<br><u>If TMR1ON =</u>                                                                                                                                           | ner1 Gate Ena<br><u>o:</u><br>ored<br><u>1:</u><br>on if Timer1 ga                                                                                                                                                                      | ble bit <sup>(2)</sup> | c                |                 |                 |           |  |

| bit 5-4             | T1CKPS<1:0                                                                                                                                                                                                            | >: Timer1 Inpu                                                                                                                                                                                                                          | t Clock Presca         | ale Select bits  |                 |                 |           |  |

|                     | 10 = 1:4 Pres<br>01 = 1:2 Pres                                                                                                                                                                                        | 11 = 1:8 Prescale Value<br>10 = 1:4 Prescale Value<br>01 = 1:2 Prescale Value<br>00 = 1:1 Prescale Value                                                                                                                                |                        |                  |                 |                 |           |  |

| bit 3               | T1OSCEN: L                                                                                                                                                                                                            | P Oscillator En                                                                                                                                                                                                                         | able Control b         | it               |                 |                 |           |  |

|                     | 1 = LP oscilla<br>0 = LP oscilla<br><u>For all other s</u><br>This bit is igno                                                                                                                                        | If INTOSC without CLKOUT oscillator is active:         1 = LP oscillator is enabled for Timer1 clock         0 = LP oscillator is off         For all other system clock modes:         This bit is ignored. LP oscillator is disabled. |                        |                  |                 |                 |           |  |

| bit 2               |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                         | lock Input Syr         | chronization C   | ontrol bit      |                 |           |  |

|                     | $\frac{\text{TMR1CS} = 1:}{1 = \text{Do not synchronize external clock input}}$ $0 = \text{Synchronize external clock input}$ $\frac{\text{TMR1CS} = 0:}{\text{This bit is ignored. Timer1 uses the internal clock}}$ |                                                                                                                                                                                                                                         |                        |                  |                 |                 |           |  |

| bit 1               | TMR1CS: Tin                                                                                                                                                                                                           | ner1 Clock Sou                                                                                                                                                                                                                          | rce Select bit         |                  |                 |                 |           |  |

|                     |                                                                                                                                                                                                                       | 1 = External clock from T1CKI pin (on the rising edge)<br>0 = Internal clock (Fosc/4) or system clock (Fosc) <sup>(3)</sup>                                                                                                             |                        |                  |                 |                 |           |  |

| bit 0               | <b>TMR1ON:</b> Tin<br>1 = Enables T<br>0 = Stops Tim                                                                                                                                                                  | īmer1                                                                                                                                                                                                                                   |                        |                  |                 |                 |           |  |

| 2:                  | T1GINV bit inverts<br>TMR1GE bit must<br>register, as a Time                                                                                                                                                          | be set to use e                                                                                                                                                                                                                         | either T1G pin         |                  |                 | T1GSS bit of th | ne CMCON1 |  |

**3:** See T1ACS bit in CMCON1 register.

# 9.6 Operation During Sleep

The comparator, if enabled before entering Sleep mode, remains active during Sleep. The additional current consumed by the comparator is shown separately in the **Section 16.0** "**Electrical Specifications**". If the comparator is not used to wake the device, power consumption can be minimized while in Sleep mode by turning off the comparator. The comparator is turned off by clearing the CMON bit of the CMCON0 register.

A change to the comparator output can wake-up the device from Sleep. To enable the comparator to wake the device from Sleep, the CMIE bit of the PIE1 register and the PEIE bit of the INTCON register must be set. The instruction following the SLEEP instruction always executes following a wake from Sleep. If the GIE bit of the INTCON register is also set, the device will then execute the Interrupt Service Routine.

# 9.7 Effects of a Reset

A device Reset forces the CMCON1 register to its Reset state. This sets the comparator and the voltage reference to the OFF state.

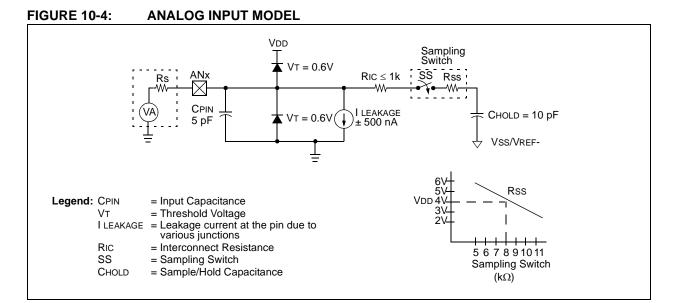

# 10.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- Results formatting

#### 10.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. See the corresponding port section for more information.

| Note: | Analog voltages on any pin that is defined |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | as a digital input may cause the input     |  |  |  |  |  |  |  |

|       | buffer to conduct excess current.          |  |  |  |  |  |  |  |

#### 10.1.2 CHANNEL SELECTION

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 10.2 "ADC Operation"** for more information.

### 10.1.3 ADC VOLTAGE REFERENCE

The VCFG bit of the ADCON0 register provides control of the positive voltage reference. The positive voltage reference can be either VDD or an external voltage source. The negative voltage reference is always connected to the ground reference.

### 10.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ANSEL register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11 TAD periods as shown in Figure 10-3.

For correct conversion, the appropriate TAD specification must be met. See A/D conversion requirements in **Section 16.0 "Electrical Specifications"** for more information. Table 10-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

### 10.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (See TRIS register)

- Configure pin as analog

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- · Select result format

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the  $GO/\overline{DONE}$  bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: See Section 10.3 "A/D Acquisition Requirements".

#### EXAMPLE 10-1: A/D CONVERSION

```

;This code block configures the ADC

; for polling, Vdd reference, Frc clock

;and GP0 input.

;Conversion start & polling for completion

; are included.

;

BANKSEL TRISIO

;

TRISIO,0

BSF

;Set GP0 to input

BANKSEL ANSEL

;

MOVLW B'01110001' ;ADC Frc clock,

IORWF

ANSEL ; and GPO as analog

BANKSEL ADCON0

;

MOVLW B'10000001' ;Right justify,

ADCON0 ;Vdd Vref, ANO, On

SampleTime ;Acquisiton delay

ADCON0,GO ;Start conversion

MOVWF

CALL

BSF

ADCON0,GO ;Is conversion done?

BTFSC

GOTO

$-1

;No, test again

BANKSEL ADRESH

;

MOVF

ADRESH,W ;Read upper 2 bits

MOVWF

RESULTHI ;Store in GPR space

BANKSEL ADRESL

;

MOVF

ADRESL,W

;Read lower 8 bits

MOVWF

RESULTLO

;Store in GPR space

```

#### **REGISTER 10-2:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0 (READ-ONLY)

| R-x    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES9 | ADRES8 | ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 |

| bit 7  |        |        |        |        |        |        | bit 0  |

|        |        |        |        |        |        |        |        |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-0

**ADRES<9:2>**: ADC Result Register bits Upper 8 bits of 10-bit conversion result

### REGISTER 10-3: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0 (READ-ONLY)

| R-x      | R-x    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |

|----------|--------|-----|-----|-----|-----|-----|-----|

| ADRES1   | ADRES0 | —   | —   | —   | —   | —   | —   |

| bit 7 k  |        |     |     |     |     |     |     |

|          |        |     |     |     |     |     |     |

| l egend: |        |     |     |     |     |     |     |

| Legena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 7-6 | ADRES<1:0>: ADC Result Register bits     |

|---------|------------------------------------------|

|         | Lower 2 bits of 10-bit conversion result |

| bit 5-0 | Unimplemented: Read as '0'               |

### REGISTER 10-4: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1 (READ-ONLY)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R-x    | R-x    |

|-------|-----|-----|-----|-----|-----|--------|--------|

| —     | —   | —   | —   | —   | —   | ADRES9 | ADRES8 |

| bit 7 |     |     |     |     |     |        | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-2 Unimplemented: Read as '0'

bit 1-0 ADRES<9:8>: ADC Result Register bits

Upper 2 bits of 10-bit conversion result

### REGISTER 10-5: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1 (READ-ONLY)

| R-x    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | s 'O'              |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-0 ADRES<7:0>: ADC Result Register bits

Lower 8 bits of 10-bit conversion result

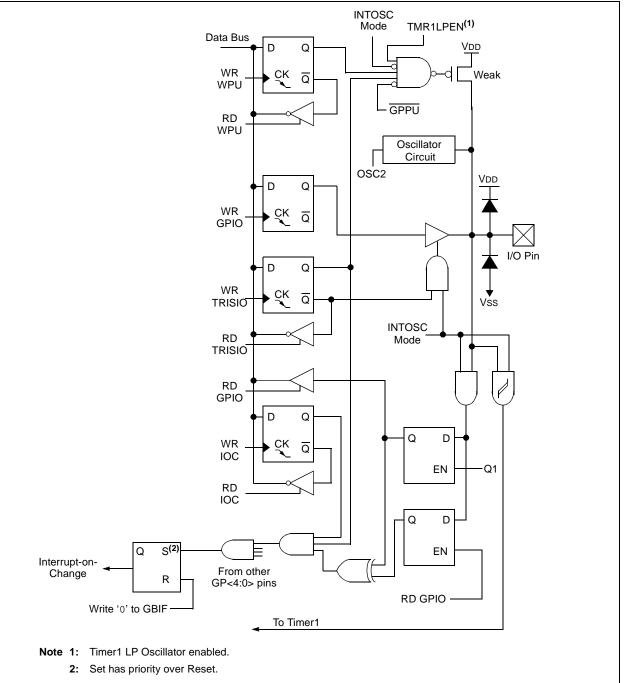

### **10.3** A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 10-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 10-4. **The maximum recommended impedance for analog sources is 10 k** $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 10-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

### EQUATION 10-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{2047}\right) = V_{CHOLD} \qquad ;[1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-T_{C}}{R_{C}}}\right) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED}$$

$$V_{APPLIED}\left(1-e^{\frac{-1}{RC}}\right) = V_{APPLIED}\left(1-\frac{1}{2047}\right) \quad (combining [1] and [2])$$

Solving for TC:

$$Tc = -C_{HOLD}(R_{IC} + R_{SS} + R_{S}) \ln(1/2047)$$

$$= -10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$$

$$= 1.37us$$

Therefore:

$$TACQ = 2\mu s + 1.37\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.67\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

### 11.3 PWM Mode

The PWM mode generates a Pulse-Width Modulated signal on the CCP1 pin. The duty cycle, period and resolution are determined by the following registers:

- PR2

- T2CON

- CCPR1L

- CCP1CON

In Pulse-Width Modulation (PWM) mode, the CCP module produces up to a 10-bit resolution PWM output on the CCP1 pin. Since the CCP1 pin is multiplexed with the PORT data latch, the TRIS for that pin must be cleared to enable the CCP1 pin output driver.

| Note: | Clearing   | the | CCP1CON         | register | will |

|-------|------------|-----|-----------------|----------|------|

|       | relinquish | CCP | 1 control of th | ne CCP1  | pin. |

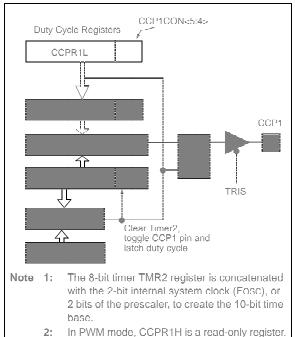

Figure 11-3 shows a simplified block diagram of PWM operation.

Figure 11-4 shows a typical waveform of the PWM signal.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 11.3.7** "Setup for PWM Operation".

FIGURE 11-3: SIMPLIFIED PWM BLOCK DIAGRAM

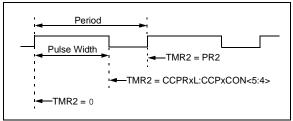

The PWM output (Figure 11-4) has a time base (period) and a time that the output stays high (duty cycle).

FIGURE 11-4: CCP PWM OUTPUT

#### REGISTER 11-2: ECCPAS: ENHANCED CAPTURE/COMPARE/PWM AUTO-SHUTDOWN CONTROL REGISTER

| R/W-0                                                                                                                                                                                                                                                                                                                          | R/W-0         | R/W-0            | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|-----------------|------------------|------------------|-----------------|--------|

| ECCPASE                                                                                                                                                                                                                                                                                                                        | ECCPAS2       | ECCPAS1          | ECCPAS0         | PSSAC1           | PSSAC0           | PSSBD1          | PSSBD0 |

| bit 7                                                                                                                                                                                                                                                                                                                          | -             | •                | •               |                  | ·                |                 | bit 0  |

|                                                                                                                                                                                                                                                                                                                                |               |                  |                 |                  |                  |                 |        |

| Legend:                                                                                                                                                                                                                                                                                                                        |               |                  |                 |                  |                  |                 |        |

| R = Readable                                                                                                                                                                                                                                                                                                                   | bit           | W = Writable     | bit             | U = Unimpler     | mented bit, read | d as '0'        |        |

| -n = Value at I                                                                                                                                                                                                                                                                                                                | POR           | '1' = Bit is set |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 7 <b>ECCPASE:</b> ECCP Auto-Shutdown Event Status bit<br>1 = A shutdown event has occurred; ECCP outputs are in shutdown state<br>0 = ECCP outputs are operating                                                                                                                                                           |               |                  |                 |                  |                  |                 |        |

| bit 6-4 ECCPAS<2:0>: ECCP Auto-shutdown Source Select bits<br>000 =Auto-Shutdown is disabled<br>001 =Comparator output change<br>010 =Auto-Shutdown is disabled<br>011 =Comparator output change <sup>(1)</sup><br>100 =VIL on INT pin<br>101 =VIL on INT pin or Comparator change<br>110 =VIL on INT pin or Comparator change |               |                  |                 |                  |                  |                 |        |

| bit 3-2                                                                                                                                                                                                                                                                                                                        |               |                  |                 |                  |                  |                 |        |

| bit 1-0 <b>PSSBD&lt;1:0&gt;:</b> Pin P1B Shutdown State Control bits<br>00 = Drive pin P1B to '0'<br>01 = Drive pin P1B to '1'<br>1x = Pin P1B tri-state                                                                                                                                                                       |               |                  |                 |                  |                  |                 |        |

| Note 1: If C                                                                                                                                                                                                                                                                                                                   | CMSYNC is ena | abled, the shutc | lown will be de | layed by Time    | r1.              |                 |        |

| Note 1: | The auto-shutdown condition is a level-<br>based signal, not an edge-based signal.<br>As long as the level is present, the auto- |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|         | shutdown will persist.                                                                                                           |  |  |  |

| 2:      | Writing to the ECCPASE bit is disabled while an auto-shutdown condition persists.                                                |  |  |  |

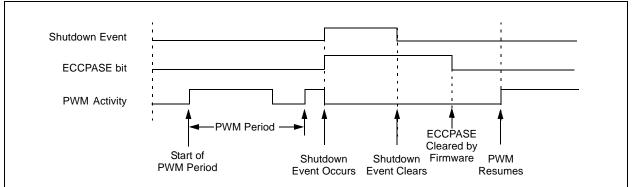

**3:** Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart) the PWM signal will always restart at the beginning of the next PWM period.

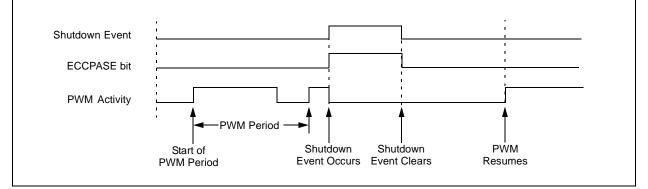

### 11.4.5 AUTO-RESTART MODE

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PRSEN bit in the PWM1CON register.

If auto-restart is enabled, the ECCPASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the ECCPASE bit will be cleared via hardware and normal operation will resume.

#### FIGURE 11-12: PWM AUTO-SHUTDOWN WITH AUTO-RESTART ENABLED (PRSEN = 1)

### REGISTER 12-1: CONFIG: CONFIGURATION WORD REGISTER (ADDRESS: 2007h) FOR PIC12F609/615/HV609/615 ONLY

| U-1           | U-1     | U-1     | U-1                | R/P-1                                | R/P-1                 | R/P-1        | R/P-1             | R/P-1                | R/P-1        | R/P-1     | R/P-1    | R/P-1      | R/P-1     |

|---------------|---------|---------|--------------------|--------------------------------------|-----------------------|--------------|-------------------|----------------------|--------------|-----------|----------|------------|-----------|

| —             | _       | _       | _                  | BOREN1 <sup>(1)</sup>                | BOREN0 <sup>(1)</sup> | IOSCFS       | CP <sup>(2)</sup> | MCLRE <sup>(3)</sup> | PWRTE        | WDTE      | FOSC2    | FOSC1      | FOSC      |

| oit 13        | 3       |         |                    |                                      |                       |              |                   | I                    |              |           |          |            | bit       |

| 000           | ndu     |         |                    |                                      |                       |              |                   |                      |              |           |          |            |           |

| Lege<br>R = F | Readat  | ole bit |                    | W = Writable                         | e bit                 | P = Prog     | rammab            | le                   |              | U = Uni   | mplement | ed bit, re | ad as '0' |

| -n = \        | Value a | at POR  |                    | '1' = Bit is se                      | et                    | '0' = Bit is | s cleared         | ł                    |              | x = Bit i | s unknow | n          |           |

| bit 13        | 8-10    | Un      | implen             | nented: Read                         | as '1'                |              |                   |                      |              |           |          |            |           |

| bit 9-        |         |         | •                  | I:0>: Brown-o                        |                       | ction hits(  | 1)                |                      |              |           |          |            |           |

| Sit 0         | 0       |         |                    | enabled                              |                       |              |                   |                      |              |           |          |            |           |

|               |         |         |                    | enabled durir                        | ig operation a        | and disable  | ed in Sle         | ер                   |              |           |          |            |           |

|               |         |         |                    | disabled                             |                       |              |                   |                      |              |           |          |            |           |

| bit 7         |         |         |                    | Internal Oscilla                     | ator Frequence        | cy Select b  | it                |                      |              |           |          |            |           |

|               |         |         | = 8 MHz<br>= 4 MHz |                                      |                       |              |                   |                      |              |           |          |            |           |

| h:+ C         |         | -       |                    | Protection bit                       | (2)                   |              |                   |                      |              |           |          |            |           |

| bit 6         |         |         |                    | am memory co                         |                       | ic dicabla   | d                 |                      |              |           |          |            |           |

|               |         |         | •                  | am memory co                         | •                     |              |                   |                      |              |           |          |            |           |

| bit 5         |         |         | °_                 | ICLR Pin Fun                         | •                     | (-)          |                   |                      |              |           |          |            |           |

|               |         |         |                    | pin function is                      |                       |              |                   |                      |              |           |          |            |           |

|               |         |         |                    | pin function is                      |                       | MCLR inte    | ernally tie       | ed to VDD            |              |           |          |            |           |

| bit 4         |         | PW      | RTE: P             | ower-up Time                         | r Enable bit          |              |                   |                      |              |           |          |            |           |

|               |         | 1 =     | 1 = PWRT disabled  |                                      |                       |              |                   |                      |              |           |          |            |           |

|               |         | 0 =     | PWRT               | enabled                              |                       |              |                   |                      |              |           |          |            |           |

| bit 3         |         | WD      | DTE: Wa            | atchdog Timer                        | Enable bit            |              |                   |                      |              |           |          |            |           |

|               |         |         | WDT e              |                                      |                       |              |                   |                      |              |           |          |            |           |

|               |         |         | WDT d              |                                      |                       |              |                   |                      |              |           |          |            |           |

| bit 2-        | 0       |         |                    | >: Oscillator S                      |                       | 0040         | 000/01            |                      |              |           |          |            |           |

|               |         |         |                    | scillator: CLK(<br>) oscillator: I/C |                       |              |                   |                      |              |           |          |            |           |

|               |         |         |                    | SC oscillator: (                     |                       |              |                   |                      |              |           | IIN      |            |           |

|               |         |         |                    | 5/OSC1/CLK                           |                       |              |                   |                      | .,           |           |          |            |           |

|               |         | 100     |                    | SCIO oscillat<br>5/OSC1/CLK          |                       | on on GP4    | /OSC2/0           | CLKOUT pin           | , I/O functi | on on     |          |            |           |

|               |         | 011     |                    | O function on                        |                       | CI KOUT n    | in. CI K          | IN on GP5/C          | DSC1/CLK     | IN        |          |            |           |

|               |         |         |                    | scillator: High-                     |                       |              |                   |                      |              |           | C1/CLKIN |            |           |

|               |         | 001     | = XT o             | scillator: Crys                      | tal/resonator         | on GP4/O     | SC2/CLI           | KOUT and G           | GP5/OSC1     | /CLKIN    |          |            |           |

|               |         | 000     | = LP o             | scillator: Low-                      | power crystal         | on GP4/C     | SC2/CL            | KOUT and             | GP5/OSC      | 1/CLKIN   |          |            |           |

| Note          | 1.      | Enabli  | na Brow            | n-out Reset d                        | nes not autor         | natically o  | nahla D/          | wor-un Tim           | or           |           |          |            |           |

| NOLE          | 2:      |         | 0                  | gram memory                          |                       | -            |                   | •                    |              |           |          |            |           |

|               |         |         |                    | J                                    |                       |              | P                 |                      |              |           |          |            |           |

3: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                            |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                       |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', then a NOP is<br>executed instead, making it a<br>two-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                    |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                       |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                            |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a two-cycle<br>instruction. |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                             |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                             |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |

| IORLW            | Inclusive OR literal with W                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |

| Operands:        | $0 \leq k \leq 255$                                                                                                       |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |

| Status Affected: | Z                                                                                                                         |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the<br>W register. |

| INCF             | Increment f                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                            |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                                                                                                                                          |

| Description:     | The contents of register 'f' is<br>moved to a destination dependent<br>upon the status of 'd'. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register 'f'<br>itself. $d = 1$ is useful to test a file<br>register since Status flag Z is<br>affected. |

| Words:           | 1                                                                                                                                                                                                                                                                                          |

| Cycles:          | 1                                                                                                                                                                                                                                                                                          |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                                |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                                 |

| MOVWF            | Move W to f                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVWF f                                                                                   |

| Operands:        | $0 \leq f \leq 127$                                                                               |

| Operation:       | $(W) \rightarrow (f)$                                                                             |

| Status Affected: | None                                                                                              |

| Description:     | Move data from W register to register 'f'.                                                        |

| Words:           | 1                                                                                                 |

| Cycles:          | 1                                                                                                 |

| Example:         | MOVW OPTION<br>F                                                                                  |

|                  | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION = 0x4F<br>W = 0x4F |

| MOVLW            | Move literal to W                                                                                   |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                            |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                   |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                                 |  |  |  |  |  |

| Status Affected: | None                                                                                                |  |  |  |  |  |

| Description:     | The eight-bit literal 'k' is loaded into<br>W register. The "don't cares" will<br>assemble as '0's. |  |  |  |  |  |

| Words:           | 1                                                                                                   |  |  |  |  |  |

| Cycles:          | 1                                                                                                   |  |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                          |  |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                                       |  |  |  |  |  |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| RLF              | Rotate Left f through Carry                                                                                                                                                                                          |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] RLF f,d                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is stored<br>back in register 'f'. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Example:         | RLF REG1,0                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|                  | REG1 = 1110 0110                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|                  | C = 0<br>After Instruction                                                                                                                                                                                           |  |  |  |  |  |  |  |

|                  | REG1 = 1110 0110                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|                  | W = 1100 1100                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|                  | C = 1                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                      |

| Operands:        | None                                                                                                                                                                                                                               |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow \underline{W}DT \text{ prescaler}, \\ 1 \rightarrow \overline{\underline{TO}}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                 |

| Status Affected: | TO, PD                                                                                                                                                                                                                             |

| Description:     | The power-down Status bit, $\overline{PD}$<br>is cleared. Time-out Status bit,<br>$\overline{TO}$ is set. Watchdog Timer and<br>its prescaler are cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] RRF f,d                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                       |  |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is placed<br>back in register 'f'. |  |  |  |  |  |  |  |

|                  | C Register f                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| SUBLW            | Subtract W from literal                                                                                                      |        |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|--|--|

| Syntax:          | [label] SL                                                                                                                   | JBLW k |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |        |  |  |  |  |  |

| Operation:       | $k \text{-} (W) \to (V)$                                                                                                     | N)     |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     |        |  |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |        |  |  |  |  |  |

|                  | Result Condition                                                                                                             |        |  |  |  |  |  |

|                  | C = 0 $W > k$                                                                                                                |        |  |  |  |  |  |

| Result        | Condition       |

|---------------|-----------------|

| <b>C</b> = 0  | W > k           |

| <b>C</b> = 1  | $W \leq k$      |

| DC = 0        | W<3:0> > k<3:0> |

| <b>DC</b> = 1 | W<3:0> ≤ k<3:0> |

### 15.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 15.12 MPLAB PM3 Device Programmer