# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

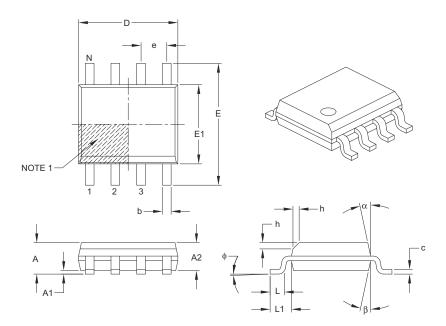

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-VDFN Exposed Pad                                                        |

| Supplier Device Package    | 8-DFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12hv609-e-md |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, PIC<sup>32</sup> logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL00® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# 2.0 MEMORY ORGANIZATION

# 2.1 Program Memory Organization

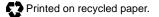

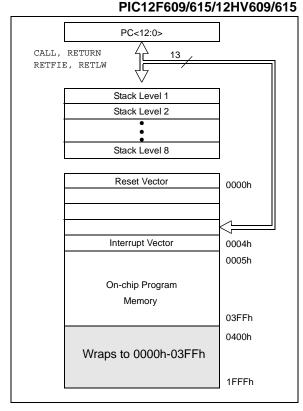

The PIC12F609/615/617/12HV609/615 has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (000h-03FFh) for the PIC12F609/615/12HV609/615 is physically implemented. For the PIC12F617, the first 2K x 14 (0000h-07FFh) is physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 1K x 14 space for PIC12F609/615/12HV609/615 devices, and within the first 2K x 14 space for the PIC12F617 device. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 2-1).

# FIGURE 2-1: PROGRAM MEMORY MAP AND STACK FOR THE

# FIGURE 2-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC12F617

# 2.2 Data Memory Organization

The data memory (see Figure 2-3) is partitioned into two banks, which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). The Special Function Registers are located in the first 32 locations of each bank. Register locations 40h-7Fh in Bank 0 are General Purpose Registers, implemented as static RAM. For the PIC12F617, the register locations 20h-7Fh in Bank 0 and A0h-EFh in Bank 1 are general purpose registers implemented as Static RAM. Register locations F0h-FFh in Bank 1 point to addresses 70h-7Fh in Bank 0. All other RAM is unimplemented and returns '0' when read. The RP0 bit of the STATUS register is the bank select bit.

# <u>RP0</u>

- $0 \rightarrow \text{Bank 0 is selected}$

- $1 \rightarrow \text{Bank 1 is selected}$

- Note: The IRP and RP1 bits of the STATUS register are reserved and should always be maintained as '0's.

### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $64 \times 8$  in the PIC12F609/615/12HV609/615, and as  $128 \times 8$  in the PIC12F617. Each register is accessed, either directly or indirectly, through the File Select Register (FSR) (see Section 2.4 "Indirect Addressing, INDF and FSR Registers").

# 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Table 2-1). These registers are static RAM.

The special registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

# FIGURE 2-3:

#### DATA MEMORY MAP OF THE PIC12F609/HV609

|                                 | THE                       | PIC12F609/HV                     | 609             |

|---------------------------------|---------------------------|----------------------------------|-----------------|

|                                 | File<br>Address           |                                  | File<br>Address |

| Indirect Addr.(1)               | 00h                       | Indirect Addr.(1)                | 80h             |

| TMR0                            | 01h                       | OPTION_REG                       | 81h             |

| PCL                             | 02h                       | PCL                              | 82h             |

| STATUS                          | 03h                       | STATUS                           | 83h             |

| FSR                             | 04h                       | FSR                              | 84h             |

| GPIO                            | 05h                       | TRISIO                           | 85h             |

|                                 | 06h                       |                                  | 86h             |

|                                 | 07h                       |                                  | 87h             |

|                                 | 08h                       |                                  | 88h             |

|                                 | 09h                       |                                  | 89h             |

| PCLATH                          | 0Ah                       | PCLATH                           | 8Ah             |

| INTCON                          | 0Bh                       | INTCON                           | 8Bh             |

| PIR1                            | 0Ch                       | PIE1                             | 8Ch             |

|                                 | 0Dh                       |                                  | 8Dh             |

| TMR1L                           | 0Eh                       | PCON                             | 8Eh             |

| TMR1H                           | 0Fh                       |                                  | 8Fh             |

| T1CON                           | 10h                       | OSCTUNE                          | 90h             |

|                                 | 11h                       |                                  | 91h             |

|                                 | 12h                       |                                  | 92h             |

|                                 | 13h                       |                                  | 93h             |

|                                 | 14h                       |                                  | 94h             |

|                                 | 15h                       | WPU                              | 95h             |

|                                 | 16h                       | IOC                              | 96h             |

|                                 | 17h                       |                                  | 97h             |

|                                 | 18h                       |                                  | 98h             |

| VRCON                           | 19h                       |                                  | 99h             |

| CMCON0                          | 1Ah                       |                                  | 9Ah             |

| -                               | 1Bh                       |                                  | 9Bh             |

| CMCON1                          | 1Ch                       |                                  | 9Ch             |

|                                 | 1Dh                       |                                  | 9Dh             |

|                                 | 1Eh                       |                                  | 9Eh             |

|                                 | 1Fh                       | ANSEL                            | 9Fh             |

|                                 | 20h                       |                                  | A0h             |

|                                 |                           |                                  |                 |

|                                 | 3Fh                       |                                  |                 |

| General<br>Purpose<br>Registers | 40h                       |                                  |                 |

| 64 Bytes                        | 6Fh<br>Z0h                |                                  | EFh<br>F0h      |

| Accesses 70h-7Fh                | 70h<br>7Fh                | Accesses 70h-7Fh                 | FUN             |

| Bank 0                          |                           | Bank 1                           |                 |

|                                 | ata memor<br>iysical regi | y locations, read as '0<br>ster. | ·               |

| Addr   | Name                     | Bit 7              | Bit 6                                                                                          | Bit 5            | Bit 4          | Bit 3                  | Bit 2           | Bit 1       | Bit 0               | Value on<br>POR, BOR | Page    |

|--------|--------------------------|--------------------|------------------------------------------------------------------------------------------------|------------------|----------------|------------------------|-----------------|-------------|---------------------|----------------------|---------|

| Bank 1 |                          |                    |                                                                                                |                  |                |                        |                 |             |                     |                      |         |

| 80h    | INDF                     | Addressing         | Addressing this location uses contents of FSR to address data memory (not a physical register) |                  |                |                        |                 |             |                     |                      |         |

| 81h    | OPTION_REG               | GPPU               | INTEDG                                                                                         | TOCS             | T0SE           | PSA                    | PS2             | PS1         | PS0                 | 1111 1111            | 19, 116 |

| 82h    | PCL                      | Program Co         | ounter's (PC)                                                                                  | Least Signifi    | icant Byte     |                        |                 |             |                     | 0000 0000            | 25, 116 |

| 83h    | STATUS                   | IRP <sup>(1)</sup> | RP1 <sup>(1)</sup>                                                                             | RP0              | TO             | PD                     | Z               | DC          | С                   | 0001 1xxx            | 18, 116 |

| 84h    | FSR                      | Indirect Data      | a Memory Ac                                                                                    | Idress Pointe    | er             |                        |                 |             |                     | xxxx xxxx            | 25, 116 |

| 85h    | TRISIO                   |                    |                                                                                                | TRISIO5          | TRISIO4        | TRISIO3 <sup>(4)</sup> | TRISIO2         | TRISIO1     | TRISIO0             | 11 1111              | 44, 116 |

| 86h    | _                        | Unimplemen         | nted                                                                                           |                  |                |                        |                 |             |                     | _                    | _       |

| 87h    | _                        | Unimplemen         | nted                                                                                           |                  |                |                        |                 |             |                     | _                    | _       |

| 88h    | _                        | Unimplemen         | nted                                                                                           |                  |                |                        |                 |             |                     | _                    | _       |

| 89h    | _                        | Unimplemen         | nted                                                                                           |                  |                |                        |                 |             |                     | —                    | —       |

| 8Ah    | PCLATH                   | _                  | _                                                                                              | _                | Writ           | e Buffer for u         | pper 5 bits of  | Program Cou | unter               | 0 0000               | 25, 116 |

| 8Bh    | INTCON                   | GIE                | PEIE                                                                                           | T0IE             | INTE           | GPIE                   | T0IF            | INTF        | GPIF <sup>(3)</sup> | 0000 0000            | 20, 116 |

| 8Ch    | PIE1                     | _                  | ADIE                                                                                           | CCP1IE           | _              | CMIE                   | _               | TMR2IE      | TMR1IE              | -00- 0-00            | 21, 116 |

| 8Dh    | _                        | Unimplemer         | nted                                                                                           |                  |                |                        |                 |             |                     | —                    | —       |

| 8Eh    | PCON                     | _                  | —                                                                                              | —                | —              | _                      | —               | POR         | BOR                 | dd                   | 23, 116 |

| 8Fh    | _                        | Unimplemen         | nted                                                                                           |                  |                |                        |                 |             |                     | _                    | _       |

| 90h    | OSCTUNE                  | _                  | _                                                                                              | _                | TUN4           | TUN3                   | TUN2            | TUN1        | TUN0                | 0 0000               | 41, 116 |

| 91h    | _                        | Unimplemen         | nted                                                                                           |                  |                |                        |                 |             |                     | _                    | _       |

| 92h    | PR2                      | Timer2 Mod         | ule Period R                                                                                   | egister          |                |                        |                 |             |                     | 1111 1111            | 65, 116 |

| 93h    | APFCON                   | _                  | _                                                                                              | _                | T1GSEL         | _                      | _               | P1BSEL      | P1ASEL              | 000                  | 21, 116 |

| 94h    | _                        | Unimplemen         | nted                                                                                           |                  |                |                        |                 |             |                     | _                    | _       |

| 95h    | WPU <sup>(2)</sup>       | _                  | _                                                                                              | WPU5             | WPU4           | _                      | WPU2            | WPU1        | WPU0                | 11 -111              | 46, 116 |

| 96h    | IOC                      | _                  | _                                                                                              | IOC5             | IOC4           | IOC3                   | IOC2            | IOC1        | IOC0                | 00 0000              | 46, 116 |

| 97h    | _                        | Unimplemen         | nted                                                                                           |                  |                |                        |                 |             |                     | _                    | _       |

| 98h    | PMCON1 <sup>(7)</sup>    | _                  | —                                                                                              | —                | —              | _                      | WREN            | WR          | RD                  | 000                  | 29      |

| 99h    | PMCON2 <sup>(7)</sup>    | Program Me         | emory Contro                                                                                   | l Register 2     | (not a physic  | al register).          |                 |             |                     |                      | —       |

| 9Ah    | PMADRL <sup>(7)</sup>    | PMADRL7            | PMADRL6                                                                                        | PMADRL5          | PMADRL4        | PMADRL3                | PMADRL2         | PMADRL1     | PMADRL0             | 0000 0000            | 28      |

| 9Bh    | PMADRH <sup>(7)</sup>    | _                  | _                                                                                              | _                | —              | _                      | PMADRH2         | PMADRH1     | PMADRH0             | 000                  | 28      |

| 9Ch    | PMDATL <sup>(7)</sup>    | PMDATL7            | PMDATL6                                                                                        | PMDATL5          | PMDATL4        | PMDATL3                | PMDATL2         | PMDATL1     | PMDATL0             | 0000 0000            | 28      |

| 9Dh    | PMDATH <sup>(7)</sup>    | —                  | —                                                                                              | Program M        | emory Data F   | Register High          | Byte.           |             |                     | 00 0000              | 28      |

| 9Eh    | ADRESL <sup>(5, 6)</sup> | Least Signif       | icant 2 bits o                                                                                 | f the left shift | ed result or 8 | bits of the rig        | ght shifted res | sult        |                     | xxxx xxxx            | 85, 117 |

| 9Fh    | ANSEL                    | —                  | ADCS2                                                                                          | ADCS1            | ADCS0          | ANS3                   | ANS2            | ANS1        | ANS0                | -000 1111            | 45, 117 |

| Logon  |                          |                    | sations road :                                                                                 |                  |                | l                      |                 | l           | 1                   | 1                    | ·       |

#### **TABLE 2-4:** PIC12F615/617/HV615 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

- = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented IRP and RP1 bits are reserved, always maintain these bits clear. GP3 pull-up is enabled when MCLRE is '1' in the Configuration Word register. Legend: Note 1:

2:

MCLR and WDT Reset does not affect the previous value data latch. The GPIF bit will clear upon Reset but will set again if the mismatch 3: exists.

TRISIO3 always reads as '1' since it is an input only pin. 4:

Read only register. 5:

PIC12F615/617/HV615 only. 6:

7: PIC12F617 only.

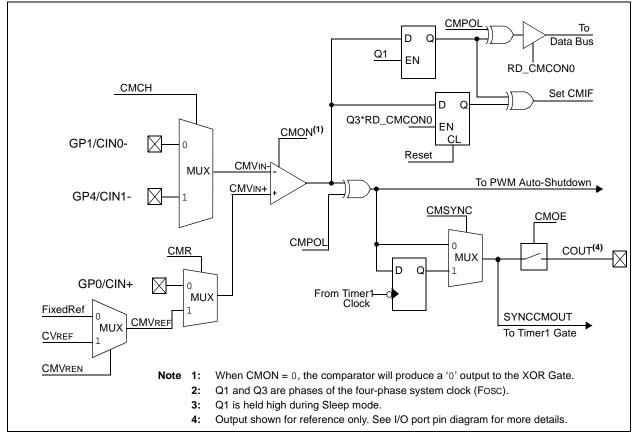

# 9.0 COMPARATOR MODULE

The comparator can be used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparator is a very useful mixed signal building block because it provides analog functionality independent of the program execution. The Analog Comparator module includes the following features:

- Programmable input section

- Comparator output is available internally/externally

- Programmable output polarity

- Interrupt-on-change

- · Wake-up from Sleep

- PWM shutdown

- Timer1 gate (count enable)

- Output synchronization to Timer1 clock input

- Programmable voltage reference

- User-enable Comparator Hysteresis

# 9.1 Comparator Overview

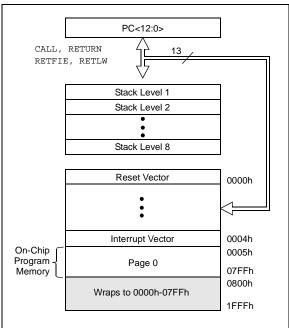

The comparator is shown in Figure 9-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less

than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

### **FIGURE 9-1:SINGLE COMPARATOR**

els and the

# FIGURE 9-2: COMPARATOR SIMPLIFIED BLOCK DIAGRAM

# 10.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- Results formatting

# 10.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. See the corresponding port section for more information.

| Note: | Analog voltages on any pin that is defined |

|-------|--------------------------------------------|

|       | as a digital input may cause the input     |

|       | buffer to conduct excess current.          |

### 10.1.2 CHANNEL SELECTION

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 10.2 "ADC Operation"** for more information.

# 10.1.3 ADC VOLTAGE REFERENCE

The VCFG bit of the ADCON0 register provides control of the positive voltage reference. The positive voltage reference can be either VDD or an external voltage source. The negative voltage reference is always connected to the ground reference.

# 10.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ANSEL register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11 TAD periods as shown in Figure 10-3.

For correct conversion, the appropriate TAD specification must be met. See A/D conversion requirements in **Section 16.0 "Electrical Specifications"** for more information. Table 10-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

# 11.0 ENHANCED CAPTURE/ COMPARE/PWM (WITH AUTO-SHUTDOWN AND DEAD BAND) MODULE (PIC12F615/617/ HV615 ONLY)

The Enhanced Capture/Compare/PWM module is a peripheral which allows the user to time and control different events. In Capture mode, the peripheral allows the timing of the duration of an event.The Compare mode allows the user to trigger an external

event when a predetermined amount of time has expired. The PWM mode can generate a Pulse-Width Modulated signal of varying frequency and duty cycle.

Table 11-1 shows the timer resources required by the ECCP module.

# TABLE 11-1: ECCP MODE – TIMER RESOURCES REQUIRED

| ECCP Mode | Timer Resource |

|-----------|----------------|

| Capture   | Timer1         |

| Compare   | Timer1         |

| PWM       | Timer2         |

# REGISTER 11-1: CCP1CON: ENHANCED CCP1 CONTROL REGISTER

| R/W-0         | U-0                                                                                                                                                                                                                                  | R/W-0                                  | R/W-0                               | R/W-0                                                   | R/W-0            | R/W-0           | R/W-0  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------|---------------------------------------------------------|------------------|-----------------|--------|

| P1M           |                                                                                                                                                                                                                                      | DC1B1                                  | DC1B0                               | CCP1M3                                                  | CCP1M2           | CCP1M1          | CCP1M0 |

| bit 7         |                                                                                                                                                                                                                                      | •                                      |                                     |                                                         |                  |                 | bit 0  |

| Legend:       |                                                                                                                                                                                                                                      |                                        |                                     |                                                         |                  |                 |        |

| R = Readable  | e bit                                                                                                                                                                                                                                | W = Writable b                         | oit                                 | U = Unimplen                                            | nented bit, read | 1 as '0'        |        |

| -n = Value at |                                                                                                                                                                                                                                      | '1' = Bit is set                       |                                     | '0' = Bit is clea                                       |                  | x = Bit is unkr | nown   |

|               |                                                                                                                                                                                                                                      |                                        |                                     |                                                         |                  |                 | -      |

| bit 7         | <u>If CCP1M&lt;3:2</u><br>x = P1A assig<br><u>If CCP1M&lt;3:2</u><br>0 = Single ou                                                                                                                                                   | 2 <u>&gt; = 11:</u><br>itput; P1A modu | :<br>e/Compare in<br>ulated; P1B as | put; P1B assign<br>ssigned as port p<br>d with dead-bar | oins             | 5               |        |

| bit 6         | Unimplemen                                                                                                                                                                                                                           | ted: Read as '                         | 0'                                  |                                                         |                  |                 |        |

|               | DC1B<1:0>: PWM Duty Cycle Least Significant bits<br><u>Capture mode:</u><br>Unused.<br><u>Compare mode:</u><br>Unused.<br><u>PWM mode:</u><br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPR1L. |                                        |                                     |                                                         |                  |                 |        |

| bit 3-0       |                                                                                                                                                                                                                                      |                                        |                                     |                                                         |                  |                 |        |

# 11.3.4 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

### 11.3.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See **Section 4.0** "Oscillator Module" for additional details.

# 11.3.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

# 11.3.7 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Disable the PWM pin (CCP1) output drivers by setting the associated TRIS bit.

- 2. Set the PWM period by loading the PR2 register.

- Configure the CCP module for the PWM mode by loading the CCP1CON register with the appropriate values.

- 4. Set the PWM duty cycle by loading the CCPR1L register and DC1B bits of the CCP1CON register.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register.

- Set the Timer2 prescale value by loading the T2CKPS bits of the T2CON register.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output after a new PWM cycle has started:

- Wait until Timer2 overflows (TMR2IF bit of the PIR1 register is set).

- Enable the CCP1 pin output driver by clearing the associated TRIS bit.

# REGISTER 12-1: CONFIG: CONFIGURATION WORD REGISTER (ADDRESS: 2007h) FOR PIC12F609/615/HV609/615 ONLY

| U-1           | U-1     | U-1                                                                                            | U-1                                                                                                 | R/P-1                                | R/P-1                 | R/P-1        | R/P-1             | R/P-1                | R/P-1   | R/P-1     | R/P-1    | R/P-1      | R/P-1     |

|---------------|---------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------|--------------|-------------------|----------------------|---------|-----------|----------|------------|-----------|

| —             | _       | _                                                                                              | _                                                                                                   | BOREN1 <sup>(1)</sup>                | BOREN0 <sup>(1)</sup> | IOSCFS       | CP <sup>(2)</sup> | MCLRE <sup>(3)</sup> | PWRTE   | WDTE      | FOSC2    | FOSC1      | FOSC      |

| oit 13        | 3       |                                                                                                |                                                                                                     |                                      |                       |              |                   | I                    |         |           |          |            | bit       |

| 000           | ndu     |                                                                                                |                                                                                                     |                                      |                       |              |                   |                      |         |           |          |            |           |

| Lege<br>R = F | Readat  | ole bit                                                                                        |                                                                                                     | W = Writable                         | e bit                 | P = Prog     | rammab            | le                   |         | U = Uni   | mplement | ed bit, re | ad as '0' |

| -n = \        | Value a | at POR                                                                                         |                                                                                                     | '1' = Bit is se                      | et                    | '0' = Bit is | s cleared         | ł                    |         | x = Bit i | s unknow | n          |           |

| bit 13        | 8-10    | Un                                                                                             | implen                                                                                              | nented: Read                         | as '1'                |              |                   |                      |         |           |          |            |           |

| bit 9-        |         |                                                                                                | •                                                                                                   | I:0>: Brown-o                        |                       | ction hits(  | 1)                |                      |         |           |          |            |           |

| Sit 0         | 0       |                                                                                                |                                                                                                     | enabled                              |                       |              |                   |                      |         |           |          |            |           |

|               |         |                                                                                                |                                                                                                     | enabled durir                        | ig operation a        | and disable  | ed in Sle         | ер                   |         |           |          |            |           |

|               |         |                                                                                                |                                                                                                     | disabled                             |                       |              |                   |                      |         |           |          |            |           |

| bit 7         |         |                                                                                                |                                                                                                     | Internal Oscilla                     | ator Frequence        | cy Select b  | it                |                      |         |           |          |            |           |

|               |         |                                                                                                | = 8 MHz<br>= 4 MHz                                                                                  |                                      |                       |              |                   |                      |         |           |          |            |           |

| h:+ C         |         | -                                                                                              |                                                                                                     | Protection bit                       | (2)                   |              |                   |                      |         |           |          |            |           |

| bit 6         |         |                                                                                                |                                                                                                     | am memory co                         |                       | ic dicabla   | d                 |                      |         |           |          |            |           |

|               |         |                                                                                                | •                                                                                                   |                                      | •                     |              |                   |                      |         |           |          |            |           |

| bit 5         |         |                                                                                                | 0 = Program memory code protection is enabled<br>MCLRE: MCLR Pin Function Select bit <sup>(3)</sup> |                                      |                       |              |                   |                      |         |           |          |            |           |

|               |         |                                                                                                |                                                                                                     | pin function is                      |                       |              |                   |                      |         |           |          |            |           |

|               |         |                                                                                                |                                                                                                     | pin function is                      |                       | MCLR inte    | ernally tie       | ed to VDD            |         |           |          |            |           |

| bit 4         |         | PW                                                                                             | RTE: P                                                                                              | ower-up Time                         | r Enable bit          |              |                   |                      |         |           |          |            |           |

|               |         | 1 =                                                                                            | PWRT                                                                                                | disabled                             |                       |              |                   |                      |         |           |          |            |           |

|               |         | 0 =                                                                                            | PWRT                                                                                                | enabled                              |                       |              |                   |                      |         |           |          |            |           |

| bit 3         |         | WD                                                                                             | DTE: Wa                                                                                             | atchdog Timer                        | Enable bit            |              |                   |                      |         |           |          |            |           |

|               |         |                                                                                                | WDT e                                                                                               |                                      |                       |              |                   |                      |         |           |          |            |           |

|               |         |                                                                                                | WDT d                                                                                               |                                      |                       |              |                   |                      |         |           |          |            |           |

| bit 2-        | 0       |                                                                                                |                                                                                                     | >: Oscillator S                      |                       | 0040         | 000/01            |                      |         |           |          |            |           |

|               |         |                                                                                                |                                                                                                     | scillator: CLK(<br>) oscillator: I/C |                       |              |                   |                      |         |           |          |            |           |

|               |         |                                                                                                |                                                                                                     | SC oscillator: (                     |                       |              |                   |                      |         |           | IIN      |            |           |

|               |         |                                                                                                |                                                                                                     | 5/OSC1/CLK                           |                       |              |                   |                      | .,      |           |          |            |           |

|               |         | 100 = INTOSCIO oscillator: I/O function on GP4/OSC2/CLKOUT pin, I/O function on GP5/OSC1/CLKIN |                                                                                                     |                                      |                       |              |                   |                      |         |           |          |            |           |

|               |         | 011                                                                                            | 011 =EC: I/O function on GP4/OSC2/CLKOUT pin, CLKIN on GP5/OSC1/CLKIN                               |                                      |                       |              |                   |                      |         |           |          |            |           |

|               |         |                                                                                                | 010 =HS oscillator: High-speed crystal/resonator on GP4/OSC2/CLKOUT and GP5/OSC1/CLKIN              |                                      |                       |              |                   |                      |         |           |          |            |           |

|               |         | 001 = XT oscillator: Crystal/resonator on GP4/OSC2/CLKOUT and GP5/OSC1/CLKIN                   |                                                                                                     |                                      |                       |              |                   |                      |         |           |          |            |           |

|               |         | 000                                                                                            | = LP o                                                                                              | scillator: Low-                      | power crystal         | on GP4/C     | SC2/CL            | KOUT and             | GP5/OSC | 1/CLKIN   |          |            |           |

| Note          | 1.      | Enabli                                                                                         | na Brow                                                                                             | n-out Reset d                        | nes not autor         | natically o  | nahla D/          | wor-un Tim           | or      |           |          |            |           |

| NOLE          | 2:      |                                                                                                | 0                                                                                                   | gram memory                          |                       | -            |                   | •                    |         |           |          |            |           |

|               |         |                                                                                                |                                                                                                     | J                                    |                       |              | P                 |                      |         |           |          |            |           |

3: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

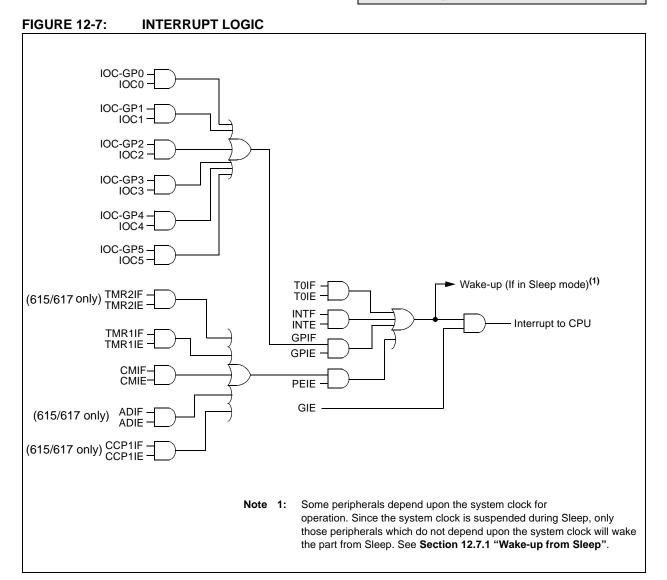

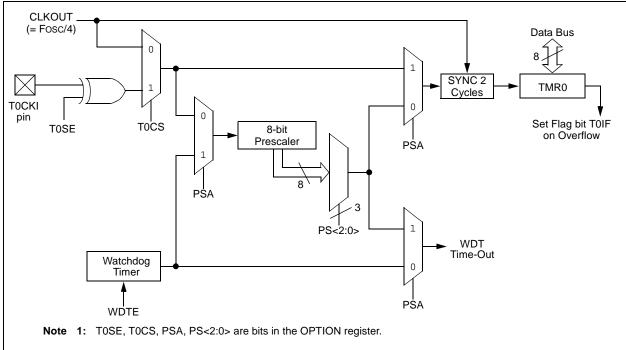

# 12.4.2 TIMER0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF bit of the INTCON register. The interrupt can be enabled/disabled by setting/clearing T0IE bit of the INTCON register. See **Section 6.0 "Timer0 Module"** for operation of the Timer0 module.

# 12.4.3 GPIO INTERRUPT-ON-CHANGE

An input change on GPIO sets the GPIF bit of the INTCON register. The interrupt can be enabled/ disabled by setting/clearing the GPIE bit of the INTCON register. Plus, individual pins can be configured through the IOC register.

Note: If a change on the I/O pin should occur when any GPIO operation is being executed, then the GPIF interrupt flag may not get set.

### 12.6.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worstcase conditions (i.e., VDD = Min., Temperature = Max., Max. WDT prescaler) it may take several seconds before a WDT time out occurs.

# FIGURE 12-2: WATCHDOG TIMER BLOCK DIAGRAM

### TABLE 12-8: WDT STATUS

| Conditions                                              | WDT                          |  |

|---------------------------------------------------------|------------------------------|--|

| WDTE = 0                                                |                              |  |

| CLRWDT Command                                          | Cleared                      |  |

| Oscillator Fail Detected                                | Cleared                      |  |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTRC, EXTCLK |                              |  |

| Exit Sleep + System Clock = XT, HS, LP                  | Cleared until the end of OST |  |

# TABLE 12-9: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

| Name       | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|--------|--------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| OPTION_REG | GPPU   | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111            | 1111 1111                       |

| CONFIG     | IOSCFS | CP     | MCLRE | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0 | —                    | —                               |

Legend: Shaded cells are not used by the Watchdog Timer.

**Note 1:** See Register 12-1 for operation of all Configuration Word register bits.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                            |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                       |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', then a NOP is<br>executed instead, making it a<br>two-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a two-cycle<br>instruction. |  |  |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                             |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                             |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |

| IORLW            | Inclusive OR literal with W                                                                                               |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                       |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |  |  |  |  |

| Status Affected: | Z                                                                                                                         |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the<br>W register. |  |  |  |  |

| INCF             | Increment f                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                         |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                   |  |  |  |  |  |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                                |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                   |  |  |  |  |  |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top-of-Stack (TOS)<br>is loaded in the PC. Interrupts are<br>enabled by setting Global<br>Interrupt Enable bit, GIE (INT-<br>CON<7>). This is a two-cycle<br>instruction. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                      |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                      |  |  |  |  |  |

| Example:         | RETFIE                                                                                                                                                                                                                 |  |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                                 |  |  |  |  |  |

| RETLW            | Return with literal in W                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                 |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                |

| Description:     | The W register is loaded with the<br>eight-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. |

| Words:           | 1                                                                                                                                                                                   |

| Cycles:          | 2                                                                                                                                                                                   |

| <u>Example:</u>  | CALL TABLE;W contains<br>;table offset<br>;value<br>GOTO DONE                                                                                                                       |

| TABLE            | •<br>•<br>ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>•<br>•<br>•<br>RETLW kn ;End of table                                                                      |

| DONE             | Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8                                                                                                              |

| RETURN           | Return from Subroutine                                                                                                                                                              |

| Syntax:          | [label] RETURN                                                                                                                                                                      |

| Operands:        | None                                                                                                                                                                                |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction.                          |

| DC CHA                       | RACTERISTICS    | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |     |       |            |                                               |

|------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|------------|-----------------------------------------------|

| Param Device Characteristics |                 | Min                                                                                                                               | Тур† | Max | Units | Conditions |                                               |

| No.                          |                 |                                                                                                                                   |      |     | •     | Vdd        | Note                                          |

| D020E                        | Power-down Base | -                                                                                                                                 | 135  | 200 | μΑ    | 2.0        | WDT, BOR, Comparator, VREF and                |

|                              |                 | _                                                                                                                                 | 210  | 280 | μΑ    | 3.0        | T1OSC disabled                                |

|                              | PIC12HV609/615  | _                                                                                                                                 | 260  | 350 | μA    | 4.5        |                                               |

| D021E                        |                 | —                                                                                                                                 | 135  | 200 | μA    | 2.0        | WDT Current <sup>(1)</sup>                    |

|                              |                 | _                                                                                                                                 | 210  | 285 | μΑ    | 3.0        |                                               |

|                              |                 | _                                                                                                                                 | 265  | 360 | μΑ    | 4.5        |                                               |

| D022E                        |                 | —                                                                                                                                 | 215  | 285 | μA    | 3.0        | BOR Current <sup>(1)</sup>                    |

|                              |                 | _                                                                                                                                 | 265  | 360 | μΑ    | 4.5        |                                               |

| D023E                        |                 | —                                                                                                                                 | 185  | 280 | μA    | 2.0        | Comparator Current <sup>(1)</sup> , single    |

|                              |                 | —                                                                                                                                 | 265  | 360 | μΑ    | 3.0        | comparator enabled                            |

|                              |                 | —                                                                                                                                 | 320  | 430 | μΑ    | 4.5        |                                               |

| D024E                        |                 | —                                                                                                                                 | 165  | 235 | μΑ    | 2.0        | CVREF Current <sup>(1)</sup> (high range)     |

|                              |                 | —                                                                                                                                 | 255  | 330 | μΑ    | 3.0        |                                               |

|                              |                 | —                                                                                                                                 | 330  | 430 | μΑ    | 4.5        |                                               |

| D025E*                       |                 |                                                                                                                                   | 175  | 245 | μΑ    | 2.0        | CVREF Current <sup>(1)</sup> (low range)      |

|                              |                 | —                                                                                                                                 | 275  | 350 | μΑ    | 3.0        |                                               |