Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                   |

| Data Converters            |                                                                           |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-VDFN Exposed Pad                                                        |

| Supplier Device Package    | 8-DFN (3x3)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12hv609-e-mf |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

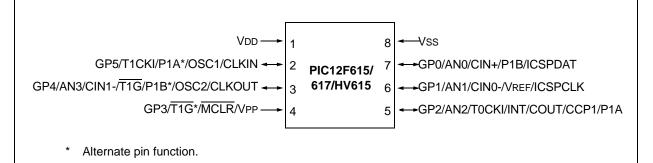

### 8-Pin Diagram, PIC12F615/617/HV615 (PDIP, SOIC, MSOP, DFN)

#### TABLE 2: PIC12F615/617/HV615 PIN SUMMARY (PDIP, SOIC, MSOP, DFN)

| I/O                | Pin | Analog | Comparator<br>s | Timer | ССР      | Interrupts | Pull-ups | Basic        |

|--------------------|-----|--------|-----------------|-------|----------|------------|----------|--------------|

| GP0                | 7   | AN0    | CIN+            | _     | P1B      | IOC        | Y        | ICSPDAT      |

| GP1                | 6   | AN1    | CIN0-           | —     | —        | IOC        | Y        | ICSPCLK/VREF |

| GP2                | 5   | AN2    | COUT            | T0CKI | CCP1/P1A | INT/IOC    | Y        | —            |

| GP3 <sup>(1)</sup> | 4   |        | —               | T1G*  | _        | IOC        | Y(2)     | MCLR/VPP     |

| GP4                | 3   | AN3    | CIN1-           | T1G   | P1B*     | IOC        | Y        | OSC2/CLKOUT  |

| GP5                | 2   | -      | —               | T1CKI | P1A*     | IOC        | Y        | OSC1/CLKIN   |

| —                  | 1   | —      | —               | —     | —        | —          | —        | Vdd          |

| —                  | 8   |        | —               | _     | _        | _          | —        | Vss          |

|                    |     |        |                 |       |          |            |          |              |

\* Alternate pin function.

Note 1: Input only.

2: Only when pin is configured for external MCLR.

| FIGURE 3-1:                  | FLASH PROGRAM MEMORY READ CYCLE EXECUTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Flash ADDR                   | $\left(\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Flash DATA                   | Image: |

|                              | INSTR (PC - 1)       BSF PMCON1,RD       INSTR (PC + 1)       INSTR (PC + 3)       INSTR (PC + 4)         Executed here       Executed here       Executed here       Executed here       Executed here                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RD bit                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PMDATH<br>PMDATL<br>Register |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PMRHLT                       | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

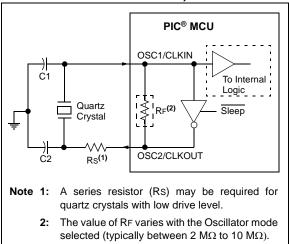

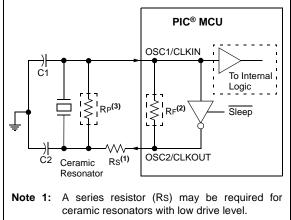

#### 4.3.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 4-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 4-3 and Figure 4-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

#### FIGURE 4-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

#### CERAMIC RESONATOR OPERATION (XT OR HS MODE)

- 2: The value of RF varies with the Oscillator mode selected (typically between 2 M $\Omega$  to 10 M $\Omega$ ).

- **3:** An additional parallel feedback resistor (RP) may be required for proper ceramic resonator operation.

| U-0   | U-0 | U-0 | U-0 | R/W-1 | U-0 | R/W-1 | R/W-1 |

|-------|-----|-----|-----|-------|-----|-------|-------|

| —     | —   | —   | —   | ANS3  | —   | ANS1  | ANS0  |

| bit 7 |     |     |     |       |     |       | bit 0 |

|       |     |     |     |       |     |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                                                                             |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | ANS3: Analog Select Between Analog or Digital Function on Pin GP4<br>1 = Analog input. Pin is assigned as analog input <sup>(1)</sup> .<br>0 = Digital I/O. Pin is assigned to port or special function.                               |

| bit 2   | Unimplemented: Read as '0'                                                                                                                                                                                                             |

| bit 1   | <ul> <li>ANS1: Analog Select Between Analog or Digital Function on Pin GP1</li> <li>1 = Analog input. Pin is assigned as analog input.<sup>(1)</sup></li> <li>0 = Digital I/O. Pin is assigned to port or special function.</li> </ul> |

| bit 0   | <ul> <li>ANS0: Analog Select Between Analog or Digital Function on Pin GP0</li> <li>0 = Digital I/O. Pin is assigned to port or special function.</li> <li>1 = Analog input. Pin is assigned as analog input.<sup>(1)</sup></li> </ul> |

**Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-onchange if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### REGISTER 5-4: ANSEL: ANALOG SELECT REGISTER (PIC12F615/617/HV615)

| U-0   | R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| —     | ADCS2 | ADCS1 | ADCS0 | ANS3  | ANS2  | ANS1  | ANS0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:                                                              |                  |                      |                    |  |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |  |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 7   | <b>Unimplemented</b> : Read as '0'                                                                                                                                                                                                                                  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | ADCS<2:0>: A/D Conversion Clock Select bits<br>000 = Fosc/2<br>001 = Fosc/8<br>010 = Fosc/32                                                                                                                                                                        |

|         | x11 = FRC (clock derived from a dedicated internal oscillator = 500 kHz max)<br>100 = Fosc/4<br>101 = Fosc/16<br>110 = Fosc/64                                                                                                                                      |

| bit 3-0 | <b>ANS&lt;3:0&gt;</b> : Analog Select Between Analog or Digital Function on Pins GP4, GP2, GP1, GP0, respectively.<br>1 = Analog input. Pin is assigned as analog input <sup>(1)</sup> .<br>0 = Digital I/O. Pin is assigned to port or special function.           |

| Note 1: | Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-on-<br>change if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of<br>the voltage on the pin. |

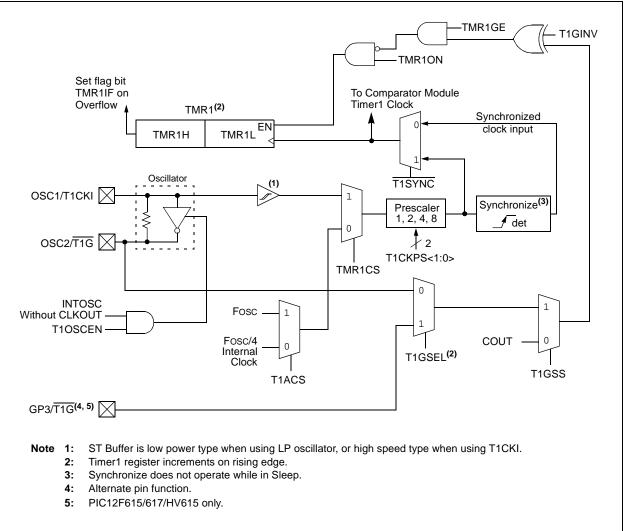

### FIGURE 7-1: TIMER1 BLOCK DIAGRAM

### 11.0 ENHANCED CAPTURE/ COMPARE/PWM (WITH AUTO-SHUTDOWN AND DEAD BAND) MODULE (PIC12F615/617/ HV615 ONLY)

The Enhanced Capture/Compare/PWM module is a peripheral which allows the user to time and control different events. In Capture mode, the peripheral allows the timing of the duration of an event.The Compare mode allows the user to trigger an external

event when a predetermined amount of time has expired. The PWM mode can generate a Pulse-Width Modulated signal of varying frequency and duty cycle.

Table 11-1 shows the timer resources required by the ECCP module.

#### TABLE 11-1: ECCP MODE – TIMER RESOURCES REQUIRED

| ECCP Mode | Timer Resource |  |  |

|-----------|----------------|--|--|

| Capture   | Timer1         |  |  |

| Compare   | Timer1         |  |  |

| PWM       | Timer2         |  |  |

### REGISTER 11-1: CCP1CON: ENHANCED CCP1 CONTROL REGISTER

| R/W-0         | U-0                                                                                                                                                                                                                            | R/W-0                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                              | R/W-0                             | R/W-0                               | R/W-0                              |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------|------------------------------------|

| P1M           |                                                                                                                                                                                                                                | DC1B1                                                                                                                                                           | DC1B0                                                                                                                                                                                                                                                 | CCP1M3                                                                                                                                             | CCP1M2                            | CCP1M1                              | CCP1M0                             |

| bit 7         |                                                                                                                                                                                                                                | •                                                                                                                                                               |                                                                                                                                                                                                                                                       |                                                                                                                                                    |                                   |                                     | bit 0                              |

| Legend:       |                                                                                                                                                                                                                                |                                                                                                                                                                 |                                                                                                                                                                                                                                                       |                                                                                                                                                    |                                   |                                     |                                    |

| R = Readable  | e bit                                                                                                                                                                                                                          | W = Writable b                                                                                                                                                  | oit                                                                                                                                                                                                                                                   | U = Unimplen                                                                                                                                       | nented bit, read                  | 1 as '0'                            |                                    |

| -n = Value at |                                                                                                                                                                                                                                | '1' = Bit is set                                                                                                                                                |                                                                                                                                                                                                                                                       | '0' = Bit is clea                                                                                                                                  |                                   | x = Bit is unkr                     | nown                               |

|               |                                                                                                                                                                                                                                |                                                                                                                                                                 |                                                                                                                                                                                                                                                       |                                                                                                                                                    |                                   |                                     | -                                  |

| bit 7         | <u>If CCP1M&lt;3:2</u><br>x = P1A assig<br><u>If CCP1M&lt;3:2</u><br>0 = Single ou                                                                                                                                             | 2 <u>&gt; = 11:</u><br>itput; P1A modu                                                                                                                          | <u>:</u><br>e/Compare in<br>ulated; P1B as                                                                                                                                                                                                            | put; P1B assign<br>ssigned as port p<br>d with dead-bar                                                                                            | oins                              | 5                                   |                                    |

| bit 6         | Unimplemen                                                                                                                                                                                                                     | ted: Read as '                                                                                                                                                  | 0'                                                                                                                                                                                                                                                    |                                                                                                                                                    |                                   |                                     |                                    |

|               | <u>Capture mode</u><br>Unused.<br><u>Compare moc</u><br>Unused.<br><u>PWM mode:</u>                                                                                                                                            | <u>le:</u>                                                                                                                                                      | Ţ                                                                                                                                                                                                                                                     | uty cycle. The ei                                                                                                                                  | ght MSbs are t                    | found in CCPR1                      | IL.                                |

| bit 3-0       | 0000 =Captur<br>0001 =Unuse<br>0010 =Compa<br>0011 =Unuse<br>0100 =Captur<br>0101 =Captur<br>0111 =Captur<br>0111 =Captur<br>1000 =Compa<br>1001 =Compa<br>1011 =Compa<br>1011 =Compa<br>1011 =Compa<br>1011 =CWM<br>1100 =PWM | are mode, tóggl<br>d (reserved)<br>re mode, every<br>re mode, every<br>re mode, every<br>re mode, every<br>are mode, set o<br>are mode, clear<br>are mode, gene | /M off (resets<br>e output on m<br>falling edge<br>4th rising edg<br>16th rising edg<br>16th rising ed<br>utput on matc<br>output on matc<br>output on matc<br>rate software i<br>er special ever<br>the ADC modu<br>ve-high; P1B a<br>ve-high; P1B a | atch (CCP1IF b<br>ge<br>h (CCP1IF bit is<br>tch (CCP1IF bit is<br>tch (CCP1IF bit is<br>ule is enabled)<br>active-high<br>active-low<br>ctive-high | set)<br>is set)<br>ch (CCP1IF bit | is set, CCP1 pir<br>sets TMR1 or Tf | n is unaffected)<br>MR2 and starts |

| Name    | Bit 7                                                                      | Bit 6               | Bit 5                 | Bit 4         | Bit 3         | Bit 2       | Bit 1                 | Bit 0   | Valu<br>POR, |      | all c | e on<br>other<br>sets |

|---------|----------------------------------------------------------------------------|---------------------|-----------------------|---------------|---------------|-------------|-----------------------|---------|--------------|------|-------|-----------------------|

| CCP1CON | P1M                                                                        | —                   | DC1B1                 | DC1B0         | CCP1M3        | CCP1M2      | CCP1M1                | CCP1M0  | 0-00         | 0000 | 0-00  | 0000                  |

| CCPR1L  | Capture/C                                                                  | ompare/PW           | /M Register           | 1 Low Byte    |               |             |                       |         | xxxx         | xxxx | uuuu  | uuuu                  |

| CCPR1H  | Capture/C                                                                  | ompare/PW           | /M Register           | 1 High Byte   | 9             |             |                       |         | xxxx         | xxxx | uuuu  | uuuu                  |

| INTCON  | GIE                                                                        | PEIE                | TOIE                  | INTE          | GPIE          | T0IF        | INTF                  | GPIF    | 0000         | 0000 | 0000  | 0000                  |

| PIE1    | —                                                                          | ADIE <sup>(1)</sup> | CCP1IE <sup>(1)</sup> | —             | CMIE          | _           | TMR2IE <sup>(1)</sup> | TMR1IE  | -00-         | 0-00 | -00-  | 0-00                  |

| PIR1    | _                                                                          | ADIF <sup>(1)</sup> | CCP1IF <sup>(1)</sup> | —             | CMIF          | -           | TMR2IF <sup>(1)</sup> | TMR1IF  | -00-         | 0-00 | -00-  | 0-00                  |

| T1CON   | T1GINV                                                                     | TMR1GE              | T1CKPS1               | T1CKPS0       | T1OSCEN       | T1SYNC      | TMR1CS                | TMR10N  | 0000         | 0000 | uuuu  | uuuu                  |

| TMR1L   | Holding R                                                                  | egister for tl      | he Least Sig          | nificant Byte | e of the 16-b | oit TMR1 Re | egister               |         | xxxx         | xxxx | uuuu  | uuuu                  |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |                     |                       |               |               |             |                       | xxxx    | xxxx         | uuuu | uuuu  |                       |

| TMR2    | Timer2 Module Register                                                     |                     |                       |               |               |             |                       | 0000    | 0000         | 0000 | 0000  |                       |

| TRISIO  | _                                                                          | —                   | TRISIO5               | TRISIO4       | TRISIO3       | TRISIO2     | TRISIO1               | TRISIO0 | 11           | 1111 | 11    | 1111                  |

#### TABLE 11-3: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARE

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Compare.

**Note 1:** For PIC12F615/617/HV615 only.

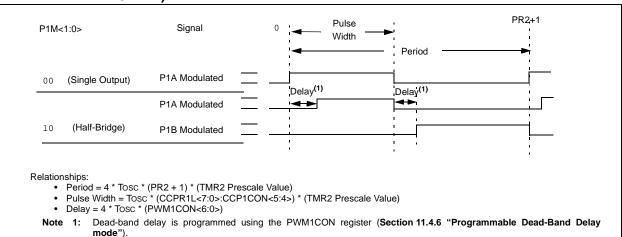

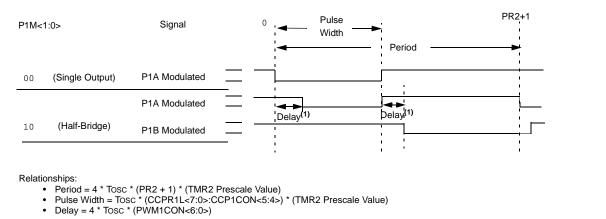

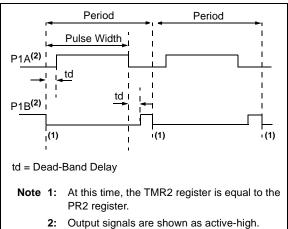

## FIGURE 11-6: EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS (ACTIVE-HIGH STATE)

#### FIGURE 11-7: EXAMPLE ENHANCED PWM OUTPUT RELATIONSHIPS (ACTIVE-LOW STATE)

Note 1: Dead-band delay is programmed using the PWM1CON register (Section 11.4.6 "Programmable Dead-Band Delay mode").

#### 11.4.6 PROGRAMMABLE DEAD-BAND DELAY MODE

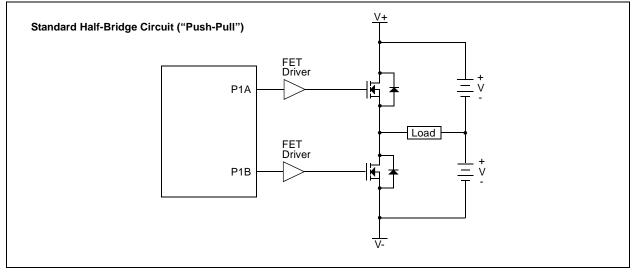

In Half-Bridge applications where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In Half-Bridge mode, a digitally programmable deadband delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 11-13 for illustration. The lower seven bits of the associated PWMxCON register (Register 11-3) sets the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc).

### FIGURE 11-13: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

#### FIGURE 11-14: EXAMPLE OF HALF-BRIDGE APPLICATIONS

NOTES:

| Register   | Address | Power-on<br>Reset | MCLR Reset<br>WDT Reset<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep through<br>Interrupt<br>Wake-up from Sleep through<br>WDT Time-out |

|------------|---------|-------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------|

| W          | _       | xxxx xxxx         | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| INDF       | 00h/80h | xxxx xxxx         | XXXX XXXX                                                 | uuuu uuuu                                                                             |

| TMR0       | 01h     | xxxx xxxx         | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| PCL        | 02h/82h | 0000 0000         | 0000 0000                                                 | PC + 1 <sup>(3)</sup>                                                                 |

| STATUS     | 03h/83h | 0001 1xxx         | 000q quuu <b>(4)</b>                                      | uuuq quuu <sup>(4)</sup>                                                              |

| FSR        | 04h/84h | xxxx xxxx         | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| GPIO       | 05h     | x0 x000           | u0 u000                                                   | uu uuuu                                                                               |

| PCLATH     | 0Ah/8Ah | 0 0000            | 0 0000                                                    | u uuuu                                                                                |

| INTCON     | 0Bh/8Bh | 0000 0000         | 0000 0000                                                 | uuuu uuuu <b>(2)</b>                                                                  |

| PIR1       | 0Ch     | 00                | 00                                                        | uu <b>(2)</b>                                                                         |

| TMR1L      | 0Eh     | xxxx xxxx         | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| TMR1H      | 0Fh     | xxxx xxxx         | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| T1CON      | 10h     | 0000 0000         | uuuu uuuu                                                 | -uuu uuuu                                                                             |

| VRCON      | 19h     | 0-00 0000         | 0-00 0000                                                 | u-uu uuuu                                                                             |

| CMCON0     | 1Ah     | 0000 -0-0         | 0000 -0-0                                                 | uuuu -u-u                                                                             |

| CMCON1     | 1Ch     | 0 0-10            | 0 0-10                                                    | u u-qu                                                                                |

| OPTION_REG | 81h     | 1111 1111         | 1111 1111                                                 | uuuu uuuu                                                                             |

| TRISIO     | 85h     | 11 1111           | 11 1111                                                   | uu uuuu                                                                               |

| PIE1       | 8Ch     | 00                | 00                                                        | uu                                                                                    |

| PCON       | 8Eh     | 0x                | (1, 5)                                                    | uu                                                                                    |

| OSCTUNE    | 90h     | 0 0000            | u uuuu                                                    | u uuuu                                                                                |

| WPU        | 95h     | 11 -111           | 11 -111                                                   | uu -uuu                                                                               |

| IOC        | 96h     | 00 0000           | 00 0000                                                   | uu uuuu                                                                               |

| ANSEL      | 9Fh     | 1-11              | 1-11                                                      | d-dd                                                                                  |

#### TABLE 12-4: INITIALIZATION CONDITION FOR REGISTERS (PIC12F609/HV609)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

**3:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 12-6 for Reset value for specific condition.

5: If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                           |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                               |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                                |  |  |  |  |  |  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                           |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                              |  |  |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>two-cycle instruction. |  |  |  |  |  |  |

| CLRWDT           | Clear Watchdog Timer                                                                                                           |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] CLRWDT                                                                                                                 |  |  |  |  |  |  |

| Operands:        | None                                                                                                                           |  |  |  |  |  |  |

| Operation:       | $00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$       |  |  |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                         |  |  |  |  |  |  |

| Description:     | CLRWDT instruction resets the<br>Watchdog Timer. It also resets<br>the prescaler of the WDT.<br>Status bits TO and PD are set. |  |  |  |  |  |  |

| CALL             | Call Subroutine                                                                                                                                                                                                                               |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                          |  |  |  |  |  |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0>, \\ (PCLATH < 4:3>) \rightarrow PC < 12:11> \end{array}$                                                                                                                |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                          |  |  |  |  |  |

| Description:     | Call Subroutine. First, return<br>address (PC + 1) is pushed onto<br>the stack. The eleven-bit<br>immediate address is loaded into<br>PC bits <10:0>. The upper bits of<br>the PC are loaded from PCLATH.<br>CALL is a two-cycle instruction. |  |  |  |  |  |

| COMF             | Complement f                                                                                                                                                   |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] COMF f,d                                                                                                                                               |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                    |  |  |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                     |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                              |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in W. If 'd' is '1',<br>the result is stored back in<br>register 'f'. |  |  |  |  |  |  |

| CLRF             | Clear f                                                                                    |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] CLRF f                                                                           |  |  |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                                        |  |  |  |  |  |  |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{(f)} \\ 1 \rightarrow \text{Z} \end{array}$ |  |  |  |  |  |  |

| Status Affected: | Z                                                                                          |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.                             |  |  |  |  |  |  |

| CLRW             | Clear W                                                                                    |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                                               |

| Operands:        | None                                                                                       |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{(W)} \\ 1 \rightarrow \text{Z} \end{array}$ |

| Status Affected: | Z                                                                                          |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                |

| DECF             | Decrement f                                                                                                                                       |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] DECF f,d                                                                                                                                |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                   |  |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                 |  |  |  |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is '0',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |  |  |

### 16.1 DC Characteristics: PIC12F609/615/617/12HV609/615-I (Industrial) PIC12F609/615/617/12HV609/615-E (Extended)

| DC CHARACTERISTICS |      |                                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |      |     |       |                                                        |  |  |

|--------------------|------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|--------------------------------------------------------|--|--|

| Param<br>No.       | Sym  | Characteristic                                                   | Min                                                                                                                                                                                                                                                             | Тур† | Max | Units | Conditions                                             |  |  |

|                    | Vdd  | Supply Voltage                                                   |                                                                                                                                                                                                                                                                 |      |     |       |                                                        |  |  |

| D001               |      | PIC12F609/615/617                                                | 2.0                                                                                                                                                                                                                                                             | —    | 5.5 | V     | Fosc < = 4 MHz                                         |  |  |

| D001               |      | PIC12HV609/615                                                   | 2.0                                                                                                                                                                                                                                                             | —    | (2) | V     | Fosc < = 4 MHz                                         |  |  |

| D001B              |      | PIC12F609/615/617                                                | 2.0                                                                                                                                                                                                                                                             | —    | 5.5 | V     | Fosc < = 8 MHz                                         |  |  |

| D001B              |      | PIC12HV609/615                                                   | 2.0                                                                                                                                                                                                                                                             | —    | (2) | V     | Fosc < = 8 MHz                                         |  |  |

| D001C              |      | PIC12F609/615/617                                                | 3.0                                                                                                                                                                                                                                                             | —    | 5.5 | V     | Fosc < = 10 MHz                                        |  |  |

| D001C              |      | PIC12HV609/615                                                   | 3.0                                                                                                                                                                                                                                                             | —    | (2) | V     | Fosc < = 10 MHz                                        |  |  |

| D001D              |      | PIC12F609/615/617                                                | 4.5                                                                                                                                                                                                                                                             | —    | 5.5 | V     | Fosc < = 20 MHz                                        |  |  |

| D001D              |      | PIC12HV609/615                                                   | 4.5                                                                                                                                                                                                                                                             | —    | (2) | V     | Fosc < = 20 MHz                                        |  |  |

| D002*              | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | 1.5                                                                                                                                                                                                                                                             | —    |     | V     | Device in Sleep mode                                   |  |  |

| D003               | VPOR | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —                                                                                                                                                                                                                                                               | Vss  | _   | V     | See Section 12.3.1 "Power-on Reset (POR)" for details. |  |  |

| D004*              | SVDD | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05                                                                                                                                                                                                                                                            | —    |     | V/ms  | See Section 12.3.1 "Power-on Reset (POR)" for details. |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

2: User defined. Voltage across the shunt regulator should not exceed 5V.

#### 16.8 DC Characteristics: PIC12F609/615/617/12HV609/615-I (Industrial) PIC12F609/615/617/12HV609/615-E (Extended)

| DC CHARACTERISTICS |      |                                          |                |          |          | nless otherwise stated)<br>≤ TA ≤ +85°C for industrial<br>≤ TA ≤ +125°C for extended |                                                                    |  |

|--------------------|------|------------------------------------------|----------------|----------|----------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|

| Param<br>No.       | Sym  | Characteristic                           | Min            | Тур†     | Max      | Units                                                                                | Conditions                                                         |  |

|                    | VIL  | Input Low Voltage                        |                |          |          |                                                                                      |                                                                    |  |

|                    |      | I/O port:                                |                |          |          |                                                                                      |                                                                    |  |

| D030               |      | with TTL buffer                          | Vss            | —        | 0.8      | V                                                                                    | $4.5V \leq V\text{DD} \leq 5.5V$                                   |  |

| D030A              |      |                                          | Vss            | —        | 0.15 Vdd | V                                                                                    | $2.0V \leq V \text{DD} \leq 4.5 \text{V}$                          |  |

| D031               |      | with Schmitt Trigger buffer              | Vss            | _        | 0.2 Vdd  | V                                                                                    | $2.0V \le VDD \le 5.5V$                                            |  |

| D032               |      | MCLR, OSC1 (RC mode)                     | Vss            | _        | 0.2 Vdd  | V                                                                                    | (NOTE 1)                                                           |  |

| D033               |      | OSC1 (XT and LP modes)                   | Vss            | _        | 0.3      | V                                                                                    |                                                                    |  |

| D033A              |      | OSC1 (HS mode)                           | Vss            | _        | 0.3 Vdd  | V                                                                                    |                                                                    |  |

|                    | Viн  | Input High Voltage                       |                |          |          |                                                                                      |                                                                    |  |

|                    |      | I/O ports:                               |                | _        |          |                                                                                      |                                                                    |  |

| D040               |      | with TTL buffer                          | 2.0            | _        | Vdd      | V                                                                                    | $4.5V \leq V \text{DD} \leq 5.5V$                                  |  |

| D040A              |      |                                          | 0.25 VDD + 0.8 | —        | Vdd      | V                                                                                    | $2.0V \leq V \text{DD} \leq 4.5 \text{V}$                          |  |

| D041               |      | with Schmitt Trigger buffer              | 0.8 Vdd        | —        | Vdd      | V                                                                                    | $2.0V \leq V \text{DD} \leq 5.5 \text{V}$                          |  |

| D042               |      | MCLR                                     | 0.8 Vdd        | —        | Vdd      | V                                                                                    |                                                                    |  |

| D043               |      | OSC1 (XT and LP modes)                   | 1.6            | —        | Vdd      | V                                                                                    |                                                                    |  |

| D043A              |      | OSC1 (HS mode)                           | 0.7 Vdd        | _        | Vdd      | V                                                                                    |                                                                    |  |

| D043B              |      | OSC1 (RC mode)                           | 0.9 Vdd        | —        | Vdd      | V                                                                                    | (NOTE 1)                                                           |  |

|                    | lı∟  | Input Leakage Current <sup>(2,3)</sup>   |                |          |          |                                                                                      |                                                                    |  |

| D060               |      | I/O ports                                | _              | ± 0.1    | ± 1      | μA                                                                                   | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance                   |  |

| D061               |      | GP3/MCLR <sup>(3,4)</sup>                | —              | $\pm0.7$ | ± 5      | μΑ                                                                                   | $V\text{SS} \leq V\text{PIN} \leq V\text{DD}$                      |  |

| D063               |      | OSC1                                     | _              | ± 0.1    | ± 5      | μΑ                                                                                   | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration |  |

| D070*              | IPUR | GPIO Weak Pull-up Current <sup>(5)</sup> | 50             | 250      | 400      | μΑ                                                                                   | VDD = 5.0V, VPIN = VSS                                             |  |

|                    | Vol  | Output Low Voltage                       | _              | _        | 0.6      | V                                                                                    | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                       |  |

| D080               |      | I/O ports                                | —              | -        | 0.6      | V                                                                                    | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                        |  |

|                    | Vон  | Output High Voltage                      | VDD - 0.7      | —        | —        | V                                                                                    | IOH = -2.5mA, VDD = 4.5V,<br>-40°С to +125°С                       |  |

| D090               |      | I/O ports <sup>(2)</sup>                 | Vdd - 0.7      | -        | -        | V                                                                                    | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                       |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: This specification applies to GP3/MCLR configured as GP3 with the internal weak pull-up disabled.

5: This specification applies to all weak pull-up pins, including the weak pull-up found on GP3/MCLR. When GP3/MCLR is configured as MCLR reset pin, the weak pull-up is always enabled.

6: Applies to PIC12F617 only.

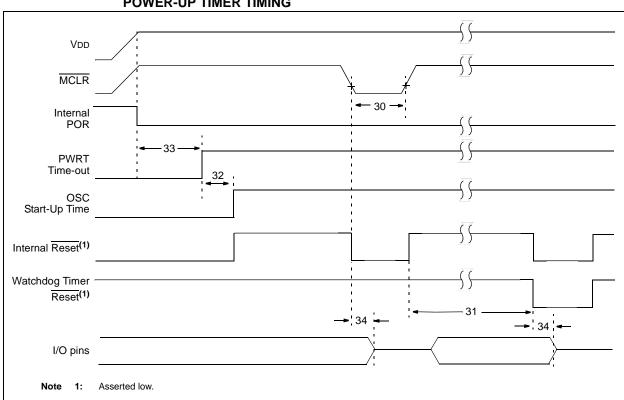

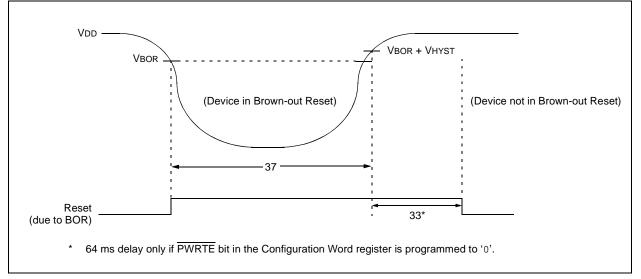

## FIGURE 16-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

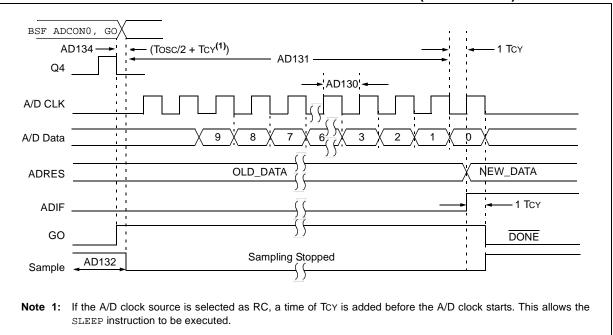

### TABLE 16-11: PIC12F615/617/HV615 A/D CONVERTER (ADC) CHARACTERISTICS:

|               | -    | rating Conditions (unless perature $-40^{\circ}C \le TA \le -40^{\circ}C$ |            | vise stated | d)       |       |                                                                     |

|---------------|------|---------------------------------------------------------------------------|------------|-------------|----------|-------|---------------------------------------------------------------------|

| Param<br>No.  | Sym  | Characteristic                                                            | Min        | Тур†        | Max      | Units | Conditions                                                          |

| AD01          | Nr   | Resolution                                                                | _          | _           | 10 bits  | bit   |                                                                     |

| AD02          | EIL  | Integral Error                                                            | —          | _           | ±1       | LSb   | VREF = 5.12V <sup>(5)</sup>                                         |

| AD03          | Edl  | Differential Error                                                        | _          | —           | ±1       | LSb   | No missing codes to 10 bits<br>VREF = 5.12V <sup>(5)</sup>          |

| AD04          | EOFF | Offset Error                                                              |            | +1.5        | +2.0     | LSb   | Vref = 5.12V <sup>(5)</sup>                                         |

| AD07          | Egn  | Gain Error                                                                |            | _           | ±1       | LSb   | VREF = 5.12V <sup>(5)</sup>                                         |

| AD06<br>AD06A | Vref | Reference Voltage <sup>(3)</sup>                                          | 2.2<br>2.5 | _           | —<br>Vdd | V     | Absolute minimum to ensure 1 LSb<br>accuracy                        |