# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 8-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12hv609-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

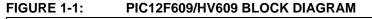

### 1.0 DEVICE OVERVIEW

The PIC12F609/615/617/12HV609/615 devices are covered by this data sheet. They are available in 8-pin PDIP, SOIC, MSOP and DFN packages.

Block Diagrams and pinout descriptions of the devices are as follows:

- PIC12F609/HV609 (Figure 1-1, Table 1-1)

- PIC12F615/617/HV615 (Figure 1-2, Table 1-2)

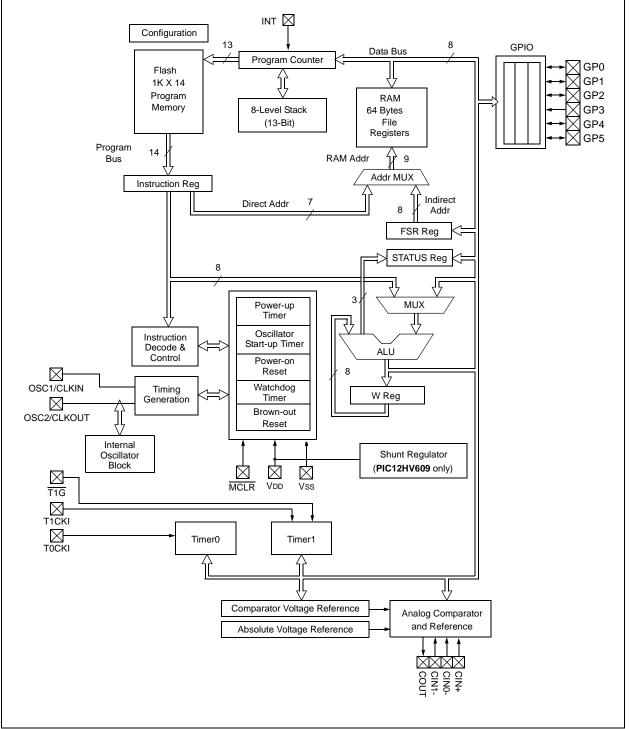

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $64 \times 8$  in the PIC12F609/615/12HV609/615, and as  $128 \times 8$  in the PIC12F617. Each register is accessed, either directly or indirectly, through the File Select Register (FSR) (see Section 2.4 "Indirect Addressing, INDF and FSR Registers").

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Table 2-1). These registers are static RAM.

The special registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

### FIGURE 2-3:

#### DATA MEMORY MAP OF THE PIC12F609/HV609

|                                 | THE                       | PIC12F609/HV                     | 609             |

|---------------------------------|---------------------------|----------------------------------|-----------------|

|                                 | File<br>Address           |                                  | File<br>Address |

| Indirect Addr.(1)               | 00h                       | Indirect Addr.(1)                | 80h             |

| TMR0                            | 01h                       | OPTION_REG                       | 81h             |

| PCL                             | 02h                       | PCL                              | 82h             |

| STATUS                          | 03h                       | STATUS                           | 83h             |

| FSR                             | 04h                       | FSR                              | 84h             |

| GPIO                            | 05h                       | TRISIO                           | 85h             |

|                                 | 06h                       |                                  | 86h             |

|                                 | 07h                       |                                  | 87h             |

|                                 | 08h                       |                                  | 88h             |

|                                 | 09h                       |                                  | 89h             |

| PCLATH                          | 0Ah                       | PCLATH                           | 8Ah             |

| INTCON                          | 0Bh                       | INTCON                           | 8Bh             |

| PIR1                            | 0Ch                       | PIE1                             | 8Ch             |

|                                 | 0Dh                       |                                  | 8Dh             |

| TMR1L                           | 0Eh                       | PCON                             | 8Eh             |

| TMR1H                           | 0Fh                       |                                  | 8Fh             |

| T1CON                           | 10h                       | OSCTUNE                          | 90h             |

|                                 | 11h                       |                                  | 91h             |

|                                 | 12h                       |                                  | 92h             |

|                                 | 13h                       |                                  | 93h             |

|                                 | 14h                       |                                  | 94h             |

|                                 | 15h                       | WPU                              | 95h             |

|                                 | 16h                       | IOC                              | 96h             |

|                                 | 17h                       |                                  | 97h             |

|                                 | 18h                       |                                  | 98h             |

| VRCON                           | 19h                       |                                  | 99h             |

| CMCON0                          | 1Ah                       |                                  | 9Ah             |

| -                               | 1Bh                       |                                  | 9Bh             |

| CMCON1                          | 1Ch                       |                                  | 9Ch             |

|                                 | 1Dh                       |                                  | 9Dh             |

|                                 | 1Eh                       |                                  | 9Eh             |

|                                 | 1Fh                       | ANSEL                            | 9Fh             |

|                                 | 20h                       |                                  | A0h             |

|                                 |                           |                                  |                 |

|                                 | 3Fh                       |                                  |                 |

| General<br>Purpose<br>Registers | 40h                       |                                  |                 |

| 64 Bytes                        | 6Fh<br>Z0h                |                                  | EFh<br>F0h      |

| Accesses 70h-7Fh                | 70h<br>7Fh                | Accesses 70h-7Fh                 | FUN             |

| Bank 0                          |                           | Bank 1                           |                 |

|                                 | ata memor<br>iysical regi | y locations, read as '0<br>ster. | ·               |

#### FIGURE 2-6: DIRECT/INDIRECT ADDRESSING PIC12F609/615/617/12HV609/615

#### REGISTER 5-2: TRISIO: GPIO TRI-STATE REGISTER

| U-0               | U-0 | R/W-1            | R/W-1   | R-1                | R/W-1              | R/W-1             | R/W-1   |

|-------------------|-----|------------------|---------|--------------------|--------------------|-------------------|---------|

| _                 | _   | TRISIO5          | TRISIO4 | TRISIO3            | TRISIO2            | TRISIO1           | TRISIO0 |

| bit 7             |     |                  | •       |                    |                    |                   | bit 0   |

|                   |     |                  |         |                    |                    |                   |         |

| Legend:           |     |                  |         |                    |                    |                   |         |

| R = Readable bit  |     | W = Writable bi  | t       | U = Unimpleme      | ented bit, read as | '0'               |         |

| -n = Value at POR |     | '1' = Bit is set |         | '0' = Bit is clear | red                | x = Bit is unknow | wn      |

bit 7-6 Unimplemented: Read as '0'

TRISIO<5:0>: GPIO Tri-State Control bit

1 = GPIO pin configured as an input (tri-stated)

0 = GPIO pin configured as an output

**Note 1:** TRISIO<3> always reads '1'.

bit 5-0

2: TRISIO<5:4> always reads '1' in XT, HS and LP Oscillator modes.

#### 5.2 Additional Pin Functions

Every GPIO pin on the PIC12F609/615/617/12HV609/ 615 has an interrupt-on-change option and a weak pullup option. The next three sections describe these functions.

#### 5.2.1 ANSEL REGISTER

The ANSEL register is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSEL bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSEL bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

#### 5.2.2 WEAK PULL-UPS

Each of the GPIO pins, except GP3, has an individually configurable internal weak pull-up. Control bits WPUx enable or disable each pull-up. Refer to Register 5-5. Each weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset by the GPPU bit of the OPTION register). A weak pull-up is automatically enabled for GP3 when configured as MCLR and disabled when GP3 is an I/O. There is no software control of the MCLR pull-up.

#### 5.2.3 INTERRUPT-ON-CHANGE

Each GPIO pin is individually configurable as an interrupt-on-change pin. Control bits IOCx enable or disable the interrupt function for each pin. Refer to Register 5-6. The interrupt-on-change is disabled on a Power-on Reset.

For enabled interrupt-on-change pins, the values are compared with the old value latched on the last read of GPIO. The 'mismatch' outputs of the last read are OR'd together to set the GPIO Change Interrupt Flag bit (GPIF) in the INTCON register (Register 2-3).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, clears the interrupt by:

- Any read of GPIO AND Clear flag bit GPIF. This will end the mismatch condition;

OR

- b) Any write of GPIO AND Clear flag bit GPIF will end the mismatch condition;

A mismatch condition will continue to set flag bit GPIF. Reading GPIO will end the mismatch condition and allow flag bit GPIF to be cleared. The latch holding the last read value is not affected by a MCLR nor BOR Reset. After these resets, the GPIF flag will continue to be set if a mismatch is present.

| Note: | If a change on the I/O pin should occur    |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | when any GPIO operation is being           |  |  |  |  |  |

|       | executed, then the GPIF interrupt flag may |  |  |  |  |  |

|       | not get set.                               |  |  |  |  |  |

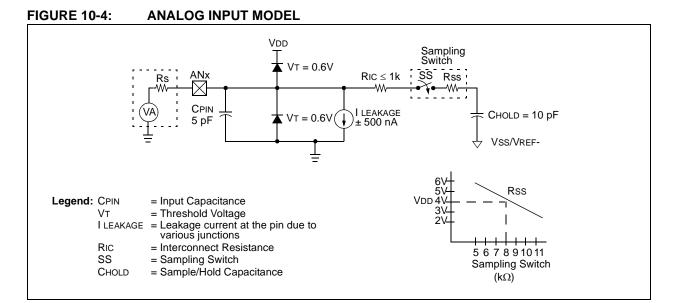

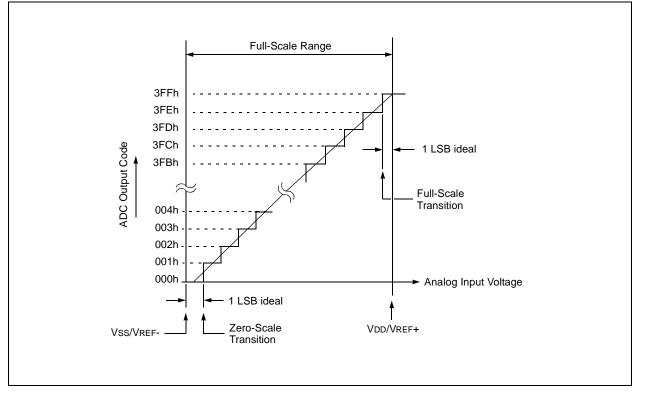

#### 10.2.7 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

#### REGISTER 10-1: ADCON0: A/D CONTROL REGISTER 0

| R/W-0      | ) R/W-0                                                                                        | U-0                                                                      | R/W-0                          | R/W-0             | R/W-0                          | R/W-0                               | R/W-0 |  |

|------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------|-------------------|--------------------------------|-------------------------------------|-------|--|

| ADFM       | 1 VCFG                                                                                         | —                                                                        | CHS2                           | CHS1              | CHS0                           | GO/DONE                             | ADON  |  |

| bit 7      |                                                                                                |                                                                          |                                |                   | ·                              |                                     | bit 0 |  |

| Legend:    |                                                                                                |                                                                          |                                |                   |                                |                                     |       |  |

| R = Read   | able bit                                                                                       | W = Writable                                                             | bit                            | U = Unimpler      | mented bit, rea                | ad as '0'                           |       |  |

| -n = Value | e at POR                                                                                       | '1' = Bit is se                                                          | t                              | '0' = Bit is cle  | ared                           | x = Bit is unkn                     | own   |  |

| bit 7      | <b>ADFM:</b> A/D<br>1 = Right ju:<br>0 = Left just                                             |                                                                          | sult Format Se                 | elect bit         |                                |                                     |       |  |

| bit 6      |                                                                                                | VCFG: Voltage Reference bit<br>1 = VREF pin                              |                                |                   |                                |                                     |       |  |

| bit 5      | Unimpleme                                                                                      | nted: Read as                                                            | 'O'                            |                   |                                |                                     |       |  |

| bit 4-2    | 000 = Chan<br>001 = Chan<br>010 = Chan<br>011 = Chan<br>100 = CVRE<br>101 = 0.6V<br>110 = 1.2V | Reference                                                                |                                |                   |                                |                                     |       |  |

| bit 1      | 1 = A/D con<br>This bit i                                                                      | A/D Conversior<br>version cycle in<br>is automatically<br>version comple | progress. Set<br>cleared by ha | rdware when th    | ts an A/D con<br>e A/D convers | version cycle.<br>sion has complete | ed.   |  |

| bit 0      | <b>ADON:</b> ADO<br>1 = ADC is 0                                                               | C Enable bit                                                             |                                |                   |                                |                                     |       |  |

| Note 1:    | When the CHS<<br>have a transient.<br>momentarily cha                                          | If the Compara                                                           | tor module use                 | es this 0.6V refe |                                |                                     |       |  |

#### TABLE 10-2: SUMMARY OF ASSOCIATED ADC REGISTERS

| Name                    | Bit 7                                                 | Bit 6                | Bit 5                 | Bit 4                | Bit 3   | Bit 2               | Bit 1                 | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------------------------|-------------------------------------------------------|----------------------|-----------------------|----------------------|---------|---------------------|-----------------------|---------|----------------------|---------------------------------|

| ADCON0 <sup>(1)</sup>   | ADFM                                                  | VCFG                 | —                     | CHS2                 | CHS1    | CHS0                | GO/DONE               | ADON    | 00-0 0000            | 00-0 0000                       |

| ANSEL                   | —                                                     | ADCS2 <sup>(1)</sup> | ADCS1 <sup>(1)</sup>  | ADCS0 <sup>(1)</sup> | ANS3    | ANS2 <sup>(1)</sup> | ANS1                  | ANS0    | -000 1111            | -000 1111                       |

| ADRESH <sup>(1,2)</sup> | ADRESH <sup>(1,2)</sup> A/D Result Register High Byte |                      |                       |                      |         |                     |                       |         | xxxx xxxx            | uuuu uuuu                       |

| ADRESL <sup>(1,2)</sup> | A/D Resu                                              | ılt Register         | Low Byte              |                      |         |                     |                       |         | xxxx xxxx            | uuuu uuuu                       |

| GPIO                    | —                                                     | —                    | GP5                   | GP4                  | GP3     | GP2                 | GP1                   | GP0     | x0 x000              | x0 x000                         |

| INTCON                  | GIE                                                   | PEIE                 | TOIE                  | INTE                 | GPIE    | TOIF                | INTF                  | GPIF    | 0000 0000            | 0000 0000                       |

| PIE1                    | —                                                     | ADIE <sup>(1)</sup>  | CCP1IE <sup>(1)</sup> |                      | CMIE    | _                   | TMR2IE <sup>(1)</sup> | TMR1IE  | -00- 0-00            | -00- 0-00                       |

| PIR1                    | _                                                     | ADIF <sup>(1)</sup>  | CCP1IF <sup>(1)</sup> | _                    | CMIF    | _                   | TMR2IF <sup>(1)</sup> | TMR1IF  | -00- 0-00            | -00- 0-00                       |

| TRISIO                  | _                                                     | _                    | TRISIO5               | TRISIO4              | TRISIO3 | TRISIO2             | TRISIO1               | TRISIO0 | 11 1111              | 11 1111                         |

**Legend:** x = unknown, u = unchanged, – = unimplemented read as '0'. Shaded cells are not used for ADC module.

Note 1: For PIC12F615/617/HV615 only.

2: Read Only Register.

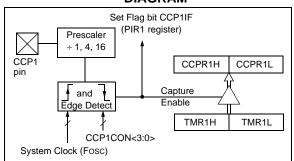

#### 11.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin CCP1. An event is defined as one of the following and is configured by the CCP1M<3:0> bits of the CCP1CON register:

- · Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCP1IF of the PIR1 register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPR1H, CCPR1L register pair is read, the old captured value is overwritten by the new captured value (see Figure 11-1).

#### 11.1.1 CCP1 PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the associated TRIS control bit.

| Note: | If the CCP1 pin is configured as an output, |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | a write to the port can cause a capture     |  |  |  |  |  |

|       | condition.                                  |  |  |  |  |  |

#### FIGURE 11-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 11.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 11.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCP1IE interrupt enable bit of the PIE1 register clear to avoid false interrupts. Additionally, the user should clear the CCP1IF interrupt flag bit of the PIR1 register following any change in operating mode.

#### 11.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCP1M<3:0> bits of the CCP1CON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCP1CON register before changing the prescaler (see Example 11-1).

#### EXAMPLE 11-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEI | CCP1CON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCP1CON             |

| CLRF    | CCP1CON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ; the new prescaler     |

|         |             | ; move value and CCP ON |

| MOVWF   | CCP1CON     | ;Load CCP1CON with this |

|         |             | ; value                 |

|         |             |                         |

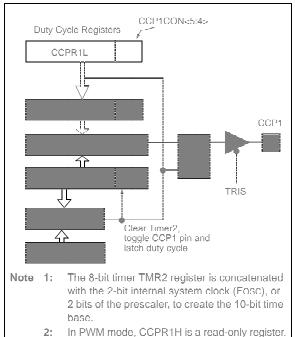

#### 11.3 PWM Mode

The PWM mode generates a Pulse-Width Modulated signal on the CCP1 pin. The duty cycle, period and resolution are determined by the following registers:

- PR2

- T2CON

- CCPR1L

- CCP1CON

In Pulse-Width Modulation (PWM) mode, the CCP module produces up to a 10-bit resolution PWM output on the CCP1 pin. Since the CCP1 pin is multiplexed with the PORT data latch, the TRIS for that pin must be cleared to enable the CCP1 pin output driver.

| Note: | Clearing   | the | CCP1CON         | register | will |

|-------|------------|-----|-----------------|----------|------|

|       | relinquish | CCP | 1 control of th | ne CCP1  | pin. |

Figure 11-3 shows a simplified block diagram of PWM operation.

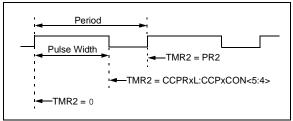

Figure 11-4 shows a typical waveform of the PWM signal.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 11.3.7** "Setup for PWM Operation".

FIGURE 11-3: SIMPLIFIED PWM BLOCK DIAGRAM

The PWM output (Figure 11-4) has a time base (period) and a time that the output stays high (duty cycle).

FIGURE 11-4: CCP PWM OUTPUT

#### 11.3.4 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 11.3.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See **Section 4.0** "Oscillator Module" for additional details.

#### 11.3.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 11.3.7 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Disable the PWM pin (CCP1) output drivers by setting the associated TRIS bit.

- 2. Set the PWM period by loading the PR2 register.

- Configure the CCP module for the PWM mode by loading the CCP1CON register with the appropriate values.

- 4. Set the PWM duty cycle by loading the CCPR1L register and DC1B bits of the CCP1CON register.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register.

- Set the Timer2 prescale value by loading the T2CKPS bits of the T2CON register.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output after a new PWM cycle has started:

- Wait until Timer2 overflows (TMR2IF bit of the PIR1 register is set).

- Enable the CCP1 pin output driver by clearing the associated TRIS bit.

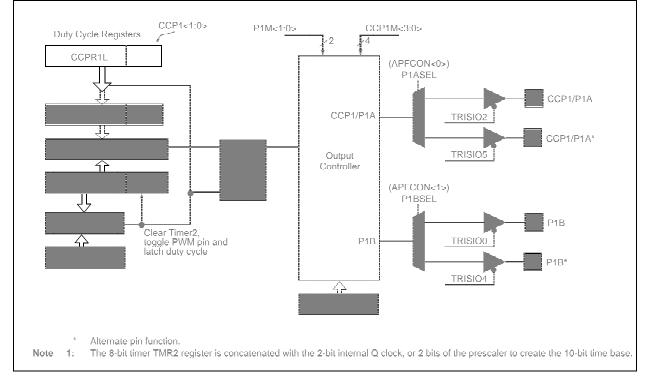

### 11.4 PWM (Enhanced Mode)

The Enhanced PWM Mode can generate a PWM signal on up to four different output pins with up to 10-bits of resolution. It can do this through four different PWM output modes:

- Single PWM

- Half-Bridge PWM

To select an Enhanced PWM mode, the P1M bits of the CCP1CON register must be set appropriately.

The PWM outputs are multiplexed with I/O pins and are designated P1A and P1B. The polarity of the PWM pins is configurable and is selected by setting the CCP1M bits in the CCP1CON register appropriately.

Table 11-6 shows the pin assignments for each Enhanced PWM mode.

Figure 11-5 shows an example of a simplified block diagram of the Enhanced PWM module.

**Note:** To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

#### FIGURE 11-5: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

Note 1: The TRIS register value for each PWM output must be configured appropriately.

- 2: Clearing the CCP1CON register will relinquish ECCP control of all PWM output pins.

- **3:** Any pin not used by an Enhanced PWM mode is available for alternate pin functions.

#### TABLE 11-6: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES

| ECCP Mode   | P1M<1:0> | CCP1/P1A           | P1B                |

|-------------|----------|--------------------|--------------------|

| Single      | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge | 10       | Yes                | Yes                |

| TABLE 12-5: | INITIALIZATION CONDITION FOR REGISTERS (PIC12F615/617/HV615) |

|-------------|--------------------------------------------------------------|

|-------------|--------------------------------------------------------------|

| Register               | Address | Power-on Reset | MCLR Reset<br>WDT Reset<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep through<br>Interrupt<br>Wake-up from Sleep through<br>WDT Time-out |

|------------------------|---------|----------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------|

| W                      | —       | xxxx xxxx      | uuuu uuuu                                                 | սսսս սսսս                                                                             |

| INDF                   | 00h/80h | XXXX XXXX      | XXXX XXXX                                                 | uuuu uuuu                                                                             |

| TMR0                   | 01h     | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| PCL                    | 02h/82h | 0000 0000      | 0000 0000                                                 | PC + 1 <sup>(3)</sup>                                                                 |

| STATUS                 | 03h/83h | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                  | uuuq quuu <sup>(4)</sup>                                                              |

| FSR                    | 04h/84h | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| GPIO                   | 05h     | x0 x000        | u0 u000                                                   | uu uuuu                                                                               |

| PCLATH                 | 0Ah/8Ah | 0 0000         | 0 0000                                                    | u uuuu                                                                                |

| INTCON                 | 0Bh/8Bh | 0000 0000      | 0000 0000                                                 | uuuu uuuu <sup>(2)</sup>                                                              |

| PIR1                   | 0Ch     | -000 0-00      | -000 0-00                                                 | -uuu u-uu <b>(2)</b>                                                                  |

| TMR1L                  | 0Eh     | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| TMR1H                  | 0Fh     | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| T1CON                  | 10h     | 0000 0000      | uuuu uuuu                                                 | -uuu uuuu                                                                             |

| TMR2 <sup>(1)</sup>    | 11h     | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| T2CON <sup>(1)</sup>   | 12h     | -000 0000      | -000 0000                                                 | -uuu uuuu                                                                             |

| CCPR1L <sup>(1)</sup>  | 13h     | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| CCPR1H <sup>(1)</sup>  | 14h     | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| CCP1CON <sup>(1)</sup> | 15h     | 0-00 0000      | 0-00 0000                                                 | u-uu uuuu                                                                             |

| PWM1CON <sup>(1)</sup> | 16h     | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| ECCPAS <sup>(1)</sup>  | 17h     | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| VRCON                  | 19h     | 0-00 0000      | 0-00 0000                                                 | u-uu uuuu                                                                             |

| CMCON0                 | 1Ah     | 0000 -0-0      | 0000 -0-0                                                 | uuuu -u-u                                                                             |

| CMCON1                 | 1Ch     | 0 0-10         | 0 0-10                                                    | u u-qu                                                                                |

| ADRESH <sup>(1)</sup>  | 1Eh     | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| ADCON0 <sup>(1)</sup>  | 1Fh     | 00-0 0000      | 00-0 0000                                                 | uu-u uuuu                                                                             |

| OPTION_REG             | 81h     | 1111 1111      | 1111 1111                                                 | uuuu uuuu                                                                             |

| TRISIO                 | 85h     | 11 1111        | 11 1111                                                   | uu uuuu                                                                               |

| PIE1                   | 8Ch     | -00-0-00       | -00-0-00                                                  | -uu- u-uu                                                                             |

| PCON                   | 8Eh     | 0x             | (1, 5)                                                    | uu                                                                                    |

| OSCTUNE                | 90h     | 0 0000         | u uuuu                                                    | u uuuu                                                                                |

| PR2                    | 92h     | 1111 1111      | 1111 1111                                                 | 1111 1111                                                                             |

| APFCON                 | 93h     | 000            | 000                                                       | uuu                                                                                   |

| WPU                    | 95h     | 11 -111        | 11 -111                                                   | uu -uuu                                                                               |

| IOC                    | 96h     | 00 0000        | 00 0000                                                   | uu uuuu                                                                               |

| PMCON1 <sup>(6)</sup>  | 98h     | 000            | 000                                                       | uuu                                                                                   |

| PMCON2 <sup>(6)</sup>  | 99h     |                |                                                           |                                                                                       |

| PMADRL <sup>(6)</sup>  | 9Ah     | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 12-6 for Reset value for specific condition.

5: If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

6: For PIC12F617 only.

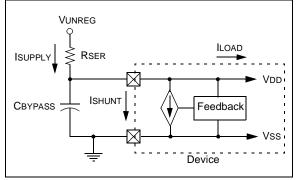

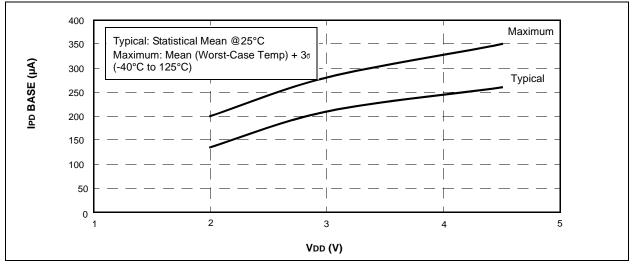

### 13.0 VOLTAGE REGULATOR

The PIC12HV609/HV615 devices include a permanent internal 5 volt (nominal) shunt regulator in parallel with the VDD pin. This eliminates the need for an external voltage regulator in systems sourced by an unregulated supply. All external devices connected directly to the VDD pin will share the regulated supply voltage and contribute to the total VDD supply current (ILOAD).

#### 13.1 Regulator Operation

A shunt regulator generates a specific supply voltage by creating a voltage drop across a pass resistor RSER. The voltage at the VDD pin of the microcontroller is monitored and compared to an internal voltage reference. The current through the resistor is then adjusted, based on the result of the comparison, to produce a voltage drop equal to the difference between the supply voltage VUNREG and the VDD of the microcontroller. See Figure 13-1 for voltage regulator schematic.

An external current limiting resistor, RSER, located between the unregulated supply, VUNREG, and the VDD pin, drops the difference in voltage between VUNREG and VDD. RSER must be between RMAX and RMIN as defined by Equation 13-1.

#### EQUATION 13-1: RSER LIMITING RESISTOR

$$RMAX = \frac{(VUMIN - 5V)}{1.05 \cdot (4 MA + ILOAD)}$$

$$RMIN = \frac{(VUMAX - 5V)}{0.95 \cdot (50 \text{ MA})}$$

Where:

RMAX = maximum value of RSER (ohms)

RMIN = minimum value of RSER (ohms)

VUMIN = minimum value of VUNREG

VUMAX = maximum value of VUNREG

VDD = regulated voltage (5V nominal)

- ILOAD = maximum expected load current in mA including I/O pin currents and external circuits connected to VDD.

- 1.05 = compensation for +5% tolerance of RSER

- 0.95 = compensation for -5% tolerance of RSER

### 13.2 Regulator Considerations

The supply voltage VUNREG and load current are not constant. Therefore, the current range of the regulator is limited. Selecting a value for RSER must take these three factors into consideration.

Since the regulator uses the band gap voltage as the regulated voltage reference, this voltage reference is permanently enabled in the PIC12HV609/HV615 devices.

The shunt regulator will still consume current when below operating voltage range for the shunt regulator.

### 13.3 Design Considerations

For more information on using the shunt regulator and managing current load, see Application Note AN1035, "*Designing with HV Microcontrollers*" (DS01035).

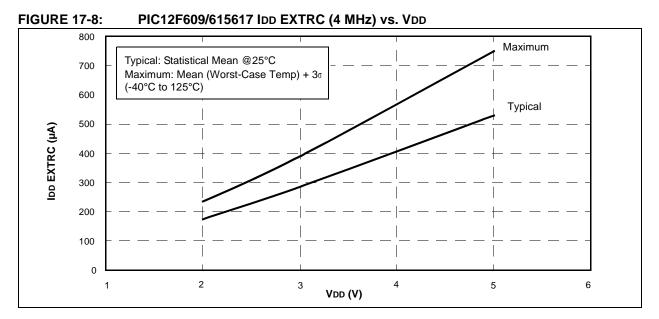

| DC CHARACTERISTICS           |                                                                     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |     |        |            |                                               |  |  |

|------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|-----|--------|------------|-----------------------------------------------|--|--|

| Param Device Characteristics |                                                                     | Min                                                                                                                               | Typ† | Max | Units  | Conditions |                                               |  |  |

| No.                          |                                                                     |                                                                                                                                   | .761 | max | •••••• | Vdd        | Note                                          |  |  |

| D020E                        | Power-down Base<br>Current (IPD) <sup>(2,3)</sup><br>PIC12HV609/615 | -                                                                                                                                 | 135  | 200 | μΑ     | 2.0        | WDT, BOR, Comparator, VREF and                |  |  |

|                              |                                                                     | _                                                                                                                                 | 210  | 280 | μA     | 3.0        | T1OSC disabled                                |  |  |

|                              |                                                                     | _                                                                                                                                 | 260  | 350 | μA     | 4.5        | 1                                             |  |  |

| D021E                        |                                                                     | _                                                                                                                                 | 135  | 200 | μA     | 2.0        | WDT Current <sup>(1)</sup>                    |  |  |

|                              |                                                                     | _                                                                                                                                 | 210  | 285 | μA     | 3.0        | 1                                             |  |  |

|                              |                                                                     | _                                                                                                                                 | 265  | 360 | μA     | 4.5        | 1                                             |  |  |

| D022E                        |                                                                     | _                                                                                                                                 | 215  | 285 | μA     | 3.0        | BOR Current <sup>(1)</sup>                    |  |  |

|                              |                                                                     | _                                                                                                                                 | 265  | 360 | μA     | 4.5        | 7                                             |  |  |

| D023E                        |                                                                     | —                                                                                                                                 | 185  | 280 | μA     | 2.0        | Comparator Current <sup>(1)</sup> , single    |  |  |

|                              |                                                                     | _                                                                                                                                 | 265  | 360 | μΑ     | 3.0        | comparator enabled                            |  |  |

|                              |                                                                     | _                                                                                                                                 | 320  | 430 | μA     | 4.5        |                                               |  |  |

| D024E                        |                                                                     | _                                                                                                                                 | 165  | 235 | μΑ     | 2.0        | CVREF Current <sup>(1)</sup> (high range)     |  |  |

|                              |                                                                     | —                                                                                                                                 | 255  | 330 | μA     | 3.0        | 7                                             |  |  |

|                              |                                                                     | _                                                                                                                                 | 330  | 430 | μΑ     | 4.5        | 1                                             |  |  |

| D025E*                       |                                                                     | —                                                                                                                                 | 175  | 245 | μA     | 2.0        | CVREF Current <sup>(1)</sup> (low range)      |  |  |

|                              |                                                                     | —                                                                                                                                 | 275  | 350 | μΑ     | 3.0        |                                               |  |  |

|                              |                                                                     | —                                                                                                                                 | 355  | 450 | μΑ     | 4.5        |                                               |  |  |

| D026E                        |                                                                     | —                                                                                                                                 | 140  | 205 | μΑ     | 2.0        | T1OSC Current <sup>(1)</sup> , 32.768 kHz     |  |  |

|                              |                                                                     | _                                                                                                                                 | 220  | 290 | μΑ     | 3.0        |                                               |  |  |

|                              |                                                                     | —                                                                                                                                 | 270  | 360 | μA     | 4.5        |                                               |  |  |

| D027E                        |                                                                     | —                                                                                                                                 | 210  | 280 | μA     | 3.0        | A/D Current <sup>(1)</sup> , no conversion in |  |  |

|                              |                                                                     | _                                                                                                                                 | 260  | 350 | μA     | 4.5        | progress                                      |  |  |

#### 16.7 DC Characteristics: PIC12HV609/615-E (Extended)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 4.5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

**2:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

3: Shunt regulator is always on and always draws operating current.

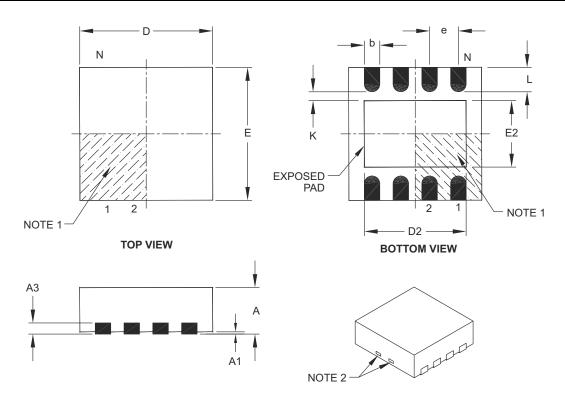

#### 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |          |      |      |  |

|------------------------|-------------|----------|------|------|--|

| Dimension Limits       |             | MIN      | NOM  | MAX  |  |

| Number of Pins         | Ν           | 8        |      |      |  |

| Pitch                  | е           | 0.80 BSC |      |      |  |

| Overall Height         | А           | 0.80     | 0.90 | 1.00 |  |

| Standoff               | A1          | 0.00     | 0.02 | 0.05 |  |

| Contact Thickness      | A3          | 0.20 REF |      |      |  |

| Overall Length         | D           | 4.00 BSC |      |      |  |

| Exposed Pad Width      | E2          | 0.00     | 2.20 | 2.80 |  |

| Overall Width          |             | 4.00 BSC |      |      |  |

| Exposed Pad Length     | D2          | 0.00     | 3.00 | 3.60 |  |

| Contact Width          | b           | 0.25     | 0.30 | 0.35 |  |

| Contact Length         | L           | 0.30     | 0.40 | 0.50 |  |

| Contact-to-Exposed Pad |             | 0.20     | -    | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-131D

### **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:                       | Technical Publications Manager                                                       | Total Pages Sent                                 |  |  |  |  |  |  |

|---------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------|--|--|--|--|--|--|

| RE:                       | Reader Response                                                                      |                                                  |  |  |  |  |  |  |

| Fror                      | n: Name                                                                              |                                                  |  |  |  |  |  |  |

|                           | Company                                                                              |                                                  |  |  |  |  |  |  |

|                           |                                                                                      |                                                  |  |  |  |  |  |  |

|                           |                                                                                      |                                                  |  |  |  |  |  |  |

|                           | Telephone: ()                                                                        | FAX: ()                                          |  |  |  |  |  |  |

| Application (optional):   |                                                                                      |                                                  |  |  |  |  |  |  |

| Would you like a reply?YN |                                                                                      |                                                  |  |  |  |  |  |  |

| Dev                       | ice: PIC12F609/615/617/12HV609/615                                                   | Literature Number: DS41302D                      |  |  |  |  |  |  |

| Questions:                |                                                                                      |                                                  |  |  |  |  |  |  |

| 1.                        | What are the best features of this documen                                           | t?                                               |  |  |  |  |  |  |

|                           |                                                                                      |                                                  |  |  |  |  |  |  |

|                           |                                                                                      |                                                  |  |  |  |  |  |  |

| 2.                        | 2. How does this document meet your hardware and software development needs?         |                                                  |  |  |  |  |  |  |

|                           |                                                                                      |                                                  |  |  |  |  |  |  |

|                           |                                                                                      |                                                  |  |  |  |  |  |  |

| 3.                        | Do you find the organization of this document easy to follow? If not, why?           |                                                  |  |  |  |  |  |  |

|                           |                                                                                      |                                                  |  |  |  |  |  |  |

| 4                         | What additions to the document do you thin                                           | k would enhance the structure and subject?       |  |  |  |  |  |  |

| ч.                        | What additions to the document do you think would enhance the structure and subject? |                                                  |  |  |  |  |  |  |

|                           |                                                                                      |                                                  |  |  |  |  |  |  |

| 5.                        | What deletions from the document could be                                            | e made without affecting the overall usefulness? |  |  |  |  |  |  |

|                           |                                                                                      |                                                  |  |  |  |  |  |  |

|                           |                                                                                      |                                                  |  |  |  |  |  |  |

| 6.                        | Is there any incorrect or misleading information (what and where)?                   |                                                  |  |  |  |  |  |  |

|                           |                                                                                      |                                                  |  |  |  |  |  |  |

|                           |                                                                                      |                                                  |  |  |  |  |  |  |

| 7.                        | How would you improve this document?                                                 |                                                  |  |  |  |  |  |  |

|                           |                                                                                      |                                                  |  |  |  |  |  |  |

|                           |                                                                                      |                                                  |  |  |  |  |  |  |