# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64 × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-VDFN Exposed Pad                                                        |

| Supplier Device Package    | 8-DFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12hv609-i-md |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

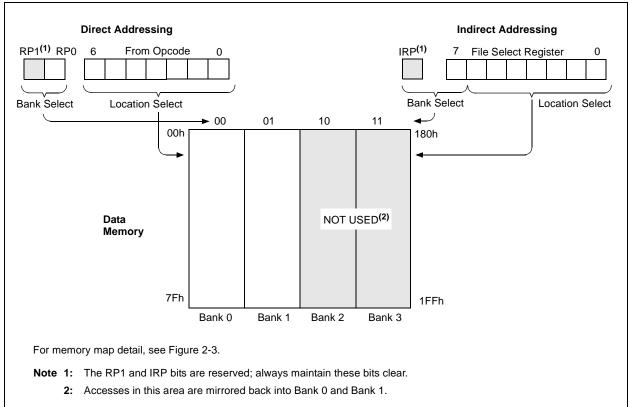

### FIGURE 2-6: DIRECT/INDIRECT ADDRESSING PIC12F609/615/617/12HV609/615

#### REGISTER 3-1: PMDATL: PROGRAM MEMORY DATA REGISTER

| R/W-0   | R/W-0              | R/W-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|---------|--------------------|-------|---------|---------|---------|---------|---------|

| PMDATL7 | PMDATL7 PMDATL6 PM |       | PMDATL4 | PMDATL3 | PMDATL2 | PMDATL1 | PMDATL0 |

| bit 7   |                    |       |         |         |         |         | bit 0   |

|         |                    |       |         |         |         |         |         |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | '0'                |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-0

-n = Value at POR

PMDATL<7:0>: 8 Least Significant Address bits to Write or Read from Program Memory

#### REGISTER 3-2: PMADRL: PROGRAM MEMORY ADDRESS REGISTER

| R/W-0            | R/W-0   | R/W-0           | R/W-0   | R/W-0                              | R/W-0   | R/W-0   | R/W-0   |  |  |

|------------------|---------|-----------------|---------|------------------------------------|---------|---------|---------|--|--|

| PMADRL7          | PMADRL6 | PMADRL5         | PMADRL4 | PMADRL3                            | PMADRL2 | PMADRL1 | PMADRL0 |  |  |

| bit 7            |         |                 |         |                                    |         |         | bit 0   |  |  |

|                  |         |                 |         |                                    |         |         |         |  |  |

| Legend:          |         |                 |         |                                    |         |         |         |  |  |

| R = Readable bit |         | W = Writable bi | t       | U = Unimplemented bit, read as '0' |         |         |         |  |  |

'0' = Bit is cleared

bit 7-0 **PMADRL<7:0>**: 8 Least Significant Address bits for Program Memory Read/Write Operation

#### REGISTER 3-3: PMDATH: PROGRAM MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|-------|---------|---------|---------|---------|---------|

| —     |     |       | PMDATH4 | PMDATH3 | PMDATH2 | PMDATH1 | PMDATH0 |

| bit 7 |     |       |         |         |         |         | bit 0   |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | '0'              |                      |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 PMDATH<5:0>: 6 Most Significant Data bits from Program Memory

'1' = Bit is set

#### REGISTER 3-4: PMADRH: PROGRAM MEMORY ADDRESS HIGH BYTE REGISTER

| U-0                                                     | U-0 | U-0 | U-0 | U-0                                 | R/W-0              | R/W-0   | R/W-0   |  |  |  |

|---------------------------------------------------------|-----|-----|-----|-------------------------------------|--------------------|---------|---------|--|--|--|

| _                                                       | —   | —   | —   | _                                   | PMADRH2            | PMADRH1 | PMADRH0 |  |  |  |

| bit 7 bit 0                                             |     |     |     |                                     |                    |         |         |  |  |  |

|                                                         |     |     |     |                                     |                    |         |         |  |  |  |

| Legend:                                                 |     |     |     |                                     |                    |         |         |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit |     |     |     |                                     | ented bit, read as | '0'     |         |  |  |  |

|                                                         |     |     |     | '0' = Bit is cleared x = Bit is unk |                    |         |         |  |  |  |

bit 3 Unimplemented: Read as '0'

bit 2-0 **PMADRH<2:0>**: Specifies the 3 Most Significant Address bits or high bits for program memory reads.

x = Bit is unknown

### 4.2 Clock Source Modes

Clock Source modes can be classified as external or internal.

- External Clock modes rely on external circuitry for the clock source. Examples are: Oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

- Internal clock sources are contained internally within the Oscillator module. The Oscillator module has two selectable clock frequencies: 4 MHz and 8 MHz

The system clock can be selected between external or internal clock sources via the FOSC<2:0> bits of the Configuration Word register.

## 4.3 External Clock Modes

#### 4.3.1 OSCILLATOR START-UP TIMER (OST)

If the Oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the Oscillator module. When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 4-1.

| Switch From | From Switch To Frequen |                  | Oscillator Delay                 |

|-------------|------------------------|------------------|----------------------------------|

| Sleep/POR   | INTOSC                 | 125 kHz to 8 MHz | Oscillator Warm-Up Delay (TWARM) |

| Sleep/POR   | EC, RC                 | DC – 20 MHz      | 2 instruction cycles             |

| Sleep/POR   | LP, XT, HS             | 32 kHz to 20 MHz | 1024 Clock Cycles (OST)          |

### TABLE 4-1: OSCILLATOR DELAY EXAMPLES

### 4.3.2 EC MODE

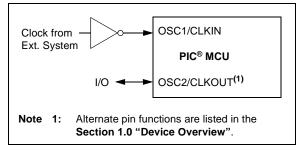

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input and the OSC2 is available for general purpose I/O. Figure 4-2 shows the pin connections for EC mode.

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### FIGURE 4-2: EXTERNAL CLOCK (EC) MODE OPERATION

#### 7.10 **ECCP Special Event Trigger** (PIC12F615/617/HV615 only)

If a ECCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The ECCP module may still be configured to generate a ECCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

Timer1 should be synchronized to the Fosc to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the ECCP, the write will take precedence.

For more information, see Section 11.0 "Enhanced Capture/Compare/PWM (With Auto-Shutdown and Dead Band) Module (PIC12F615/617/HV615 only)".

#### 7.11 **Comparator Synchronization**

The same clock used to increment Timer1 can also be used to synchronize the comparator output. This feature is enabled in the Comparator module.

When using the comparator for Timer1 gate, the comparator output should be synchronized to Timer1. This ensures Timer1 does not miss an increment if the comparator changes.

For more information, see Section 9.0 "Comparator Module".

NOTES:

| U-0               | R/W-0                        | R/W-0                                             | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |  |  |

|-------------------|------------------------------|---------------------------------------------------|---------------|-------------------|-----------------|-----------------|---------|--|--|--|--|--|--|

| _                 | TOUTPS3                      | TOUTPS2                                           | TOUTPS1       | TOUTPS0           | TMR2ON          | T2CKPS1         | T2CKPS0 |  |  |  |  |  |  |

| oit 7             |                              |                                                   |               |                   |                 |                 | bit     |  |  |  |  |  |  |

|                   |                              |                                                   |               |                   |                 |                 |         |  |  |  |  |  |  |

| Legend:           |                              |                                                   |               |                   |                 |                 |         |  |  |  |  |  |  |

| R = Readab        |                              | W = Writable                                      |               | -                 | nented bit, rea | d as '0'        |         |  |  |  |  |  |  |

| -n = Value at POR |                              | '1' = Bit is set                                  |               | '0' = Bit is clea | ared            | x = Bit is unki | nown    |  |  |  |  |  |  |

|                   |                              |                                                   |               |                   |                 |                 |         |  |  |  |  |  |  |

| oit 7             | Unimplemen                   | ted: Read as '                                    | 0'            |                   |                 |                 |         |  |  |  |  |  |  |

| oit 6-3           | TOUTPS<3:0                   | TOUTPS<3:0>: Timer2 Output Postscaler Select bits |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   | 0000 =1:1 Po                 |                                                   |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   |                              | 0001 =1:2 Postscaler                              |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   |                              | 0010 =1:3 Postscaler<br>0011 =1:4 Postscaler      |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   |                              | 0100 =1:5 Postscaler                              |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   | 0100 = 1.5 PC                |                                                   |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   |                              | 0110 =1:7 Postscaler                              |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   |                              | 0111 =1:8 Postscaler                              |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   | 1000 <b>=1:9</b> Po          | 1000 =1:9 Postscaler                              |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   | 1001 =1:10 F                 | 1001 =1:10 Postscaler                             |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   |                              | 1010 =1:11 Postscaler                             |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   | 1011 =1:12 F                 |                                                   |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   | 1100 =1:13 F                 |                                                   |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   | 1101 =1:14 F<br>1110 =1:15 F |                                                   |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   | 1110 =1:15 F                 |                                                   |               |                   |                 |                 |         |  |  |  |  |  |  |

| oit 2             | <b>TMR2ON:</b> Tir           |                                                   |               |                   |                 |                 |         |  |  |  |  |  |  |

| 511 2             |                              |                                                   |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   |                              | 1 = Timer2 is on<br>0 = Timer2 is off             |               |                   |                 |                 |         |  |  |  |  |  |  |

| oit 1-0           | T2CKPS<1:0                   | >: Timer2 Cloc                                    | k Prescale Se | lect bits         |                 |                 |         |  |  |  |  |  |  |

|                   | 00 =Prescale                 | eris 1                                            |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   | 01 =Prescale                 |                                                   |               |                   |                 |                 |         |  |  |  |  |  |  |

|                   | 1x =Prescaler is 16          |                                                   |               |                   |                 |                 |         |  |  |  |  |  |  |

#### **REGISTER 8-1: T2CON: TIMER 2 CONTROL REGISTER**

#### **TABLE 8-1:** SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2

| Name                 | Bit 7     | Bit 6               | Bit 5                 | Bit 4    | Bit 3                               | Bit 2 | Bit 1                 | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |  |

|----------------------|-----------|---------------------|-----------------------|----------|-------------------------------------|-------|-----------------------|--------|----------------------|---------------------------------|--|

| INTCON               | GIE       | PEIE                | TOIE                  | INTE     | GPIE                                | T0IF  | INTF                  | GPIF   | 0000 0000            | 0000 0000                       |  |

| PIE1                 | _         | ADIE <sup>(1)</sup> | CCP1IE <sup>(1)</sup> | _        | CMIE                                | _     | TMR2IE <sup>(1)</sup> | TMR1IE | -00- 0-00            | -00-0-00                        |  |

| PIR1                 | —         | ADIF <sup>(1)</sup> | CCP1IF <sup>(1)</sup> | _        | CMIF                                | _     | TMR2IF <sup>(1)</sup> | TMR1IF | -00- 0-00            | -00-0-00                        |  |

| PR2 <sup>(1)</sup>   | Timer2 M  | lodule Period       | Register              |          |                                     |       |                       |        | 1111 1111            | 1111 1111                       |  |

| TMR2 <sup>(1)</sup>  | Holding F | Register for the    | e 8-bit TMR2          | Register |                                     |       |                       |        | 0000 0000            | 0000 0000                       |  |

| T2CON <sup>(1)</sup> | —         | TOUTPS3             | TOUTPS2               | TOUTPS1  | TPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 |       |                       |        |                      | -000 0000                       |  |

| Lanandi              |           |                     |                       |          |                                     |       |                       |        |                      |                                 |  |

Legend:x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.Note1:For PIC12F615/617/HV615 only.

### REGISTER 12-1: CONFIG: CONFIGURATION WORD REGISTER (ADDRESS: 2007h) FOR PIC12F609/615/HV609/615 ONLY

| U-1           | U-1     | U-1     | U-1                | R/P-1                                | R/P-1                 | R/P-1        | R/P-1             | R/P-1                | R/P-1        | R/P-1     | R/P-1    | R/P-1      | R/P-1     |

|---------------|---------|---------|--------------------|--------------------------------------|-----------------------|--------------|-------------------|----------------------|--------------|-----------|----------|------------|-----------|

| —             | _       | _       | _                  | BOREN1 <sup>(1)</sup>                | BOREN0 <sup>(1)</sup> | IOSCFS       | CP <sup>(2)</sup> | MCLRE <sup>(3)</sup> | PWRTE        | WDTE      | FOSC2    | FOSC1      | FOSC      |

| oit 13        | 3       |         |                    |                                      |                       |              |                   | I                    |              |           |          |            | bit       |

| 000           | ndu     |         |                    |                                      |                       |              |                   |                      |              |           |          |            |           |

| Lege<br>R = F | Readat  | ole bit |                    | W = Writable                         | e bit                 | P = Prog     | rammab            | le                   |              | U = Uni   | mplement | ed bit, re | ad as '0' |

| -n = \        | Value a | at POR  |                    | '1' = Bit is se                      | et                    | '0' = Bit is | s cleared         | ł                    |              | x = Bit i | s unknow | n          |           |

| bit 13        | 8-10    | Un      | implen             | nented: Read                         | as '1'                |              |                   |                      |              |           |          |            |           |

| bit 9-        |         |         | •                  | I:0>: Brown-o                        |                       | ction hits(  | 1)                |                      |              |           |          |            |           |

| Sit 0         | 0       |         |                    | enabled                              |                       |              |                   |                      |              |           |          |            |           |

|               |         |         |                    | enabled durir                        | ig operation a        | and disable  | ed in Sle         | ер                   |              |           |          |            |           |

|               |         |         |                    | disabled                             |                       |              |                   |                      |              |           |          |            |           |

| bit 7         |         |         |                    | Internal Oscilla                     | ator Frequence        | cy Select b  | it                |                      |              |           |          |            |           |

|               |         |         | = 8 MHz<br>= 4 MHz |                                      |                       |              |                   |                      |              |           |          |            |           |

| h:+ C         |         | -       |                    | Protection bit                       | (2)                   |              |                   |                      |              |           |          |            |           |

| bit 6         |         |         |                    | am memory co                         |                       | ic dicabla   | d                 |                      |              |           |          |            |           |

|               |         |         | •                  | am memory co                         | •                     |              |                   |                      |              |           |          |            |           |

| bit 5         |         |         | °_                 | ICLR Pin Fun                         | •                     | (-)          |                   |                      |              |           |          |            |           |

|               |         |         |                    | pin function is                      |                       |              |                   |                      |              |           |          |            |           |

|               |         |         |                    | pin function is                      |                       | MCLR inte    | ernally tie       | ed to VDD            |              |           |          |            |           |

| bit 4         |         | PW      | RTE: P             | ower-up Time                         | r Enable bit          |              |                   |                      |              |           |          |            |           |

|               |         | 1 =     | PWRT               | disabled                             |                       |              |                   |                      |              |           |          |            |           |

|               |         | 0 =     | PWRT               | enabled                              |                       |              |                   |                      |              |           |          |            |           |

| bit 3         |         | WD      | DTE: Wa            | atchdog Timer                        | Enable bit            |              |                   |                      |              |           |          |            |           |

|               |         |         | WDT e              |                                      |                       |              |                   |                      |              |           |          |            |           |

|               |         |         | WDT d              |                                      |                       |              |                   |                      |              |           |          |            |           |

| bit 2-        | 0       |         |                    | >: Oscillator S                      |                       | 0040         | 000/01            |                      |              |           |          |            |           |

|               |         |         |                    | scillator: CLK(<br>) oscillator: I/C |                       |              |                   |                      |              |           |          |            |           |

|               |         |         |                    | SC oscillator: (                     |                       |              |                   |                      |              |           | IIN      |            |           |

|               |         |         |                    | 5/OSC1/CLK                           |                       |              |                   |                      | .,           |           |          |            |           |

|               |         | 100     |                    | SCIO oscillat<br>5/OSC1/CLK          |                       | on on GP4    | /OSC2/0           | CLKOUT pin           | , I/O functi | on on     |          |            |           |

|               |         | 011     |                    | O function on                        |                       | CI KOUT n    | in. CI K          | IN on GP5/C          | DSC1/CLK     | IN        |          |            |           |

|               |         |         |                    | scillator: High-                     |                       |              |                   |                      |              |           | C1/CLKIN |            |           |

|               |         | 001     | = XT o             | scillator: Crys                      | tal/resonator         | on GP4/O     | SC2/CLI           | KOUT and G           | GP5/OSC1     | /CLKIN    |          |            |           |

|               |         | 000     | = LP o             | scillator: Low-                      | power crystal         | on GP4/C     | SC2/CL            | KOUT and             | GP5/OSC      | 1/CLKIN   |          |            |           |

| Note          | 1.      | Enabli  | na Brow            | n-out Reset d                        | nes not autor         | natically o  | nahla D/          | wor-un Tim           | or           |           |          |            |           |

| NOLE          | 2:      |         | 0                  | gram memory                          |                       | -            |                   | •                    |              |           |          |            |           |

|               |         |         |                    | J                                    |                       |              | P                 |                      |              |           |          |            |           |

3: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

#### 12.3.5 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows:

- PWRT time-out is invoked after POR has expired.

- OST is activated after the PWRT time-out has expired.

The total time-out will vary based on oscillator configuration and PWRTE bit status. For example, in EC mode with PWRTE bit erased (PWRT disabled), there will be no time-out at all. Figure 12-4, Figure 12-5 and Figure 12-6 depict time-out sequences.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then, bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 12-5). This is useful for testing purposes or to synchronize more than one PIC12F609/615/617/12HV609/615 device operating in parallel.

Table 12-6 shows the Reset conditions for some special registers, while Table 12-5 shows the Reset conditions for all the registers.

#### 12.3.6 POWER CONTROL (PCON) REGISTER

The Power Control register PCON (address 8Eh) has two Status bits to indicate what type of Reset occurred last.

Bit 0 is  $\overline{\text{BOR}}$  (Brown-out).  $\overline{\text{BOR}}$  is unknown on Poweron Reset. It must then be set by the user and checked on subsequent Resets to see if  $\overline{\text{BOR}} = 0$ , indicating that a Brown-out has occurred. The  $\overline{\text{BOR}}$  Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (BOREN<1:0> = 00 in the Configuration Word register).

Bit 1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent Reset, if POR is '0', it will indicate that a Power-on Reset has occurred (i.e., VDD may have gone too low).

For more information, see Section 12.3.4 "Brown-out Reset (BOR)".

| Oscillator Configuration | Powe                   | er-up            | Brown-o                | ut Reset         | Wake-up from |

|--------------------------|------------------------|------------------|------------------------|------------------|--------------|

| Oscillator Configuration | <b>PWRTE</b> = 0       | <b>PWRTE</b> = 1 | <b>PWRTE</b> = 0       | <b>PWRTE</b> = 1 | Sleep        |

| XT, HS, LP               | TPWRT + 1024 •<br>Tosc | 1024 • Tosc      | TPWRT + 1024 •<br>Tosc | 1024 • Tosc      | 1024 • Tosc  |

| RC, EC, INTOSC           | TPWRT                  | —                | TPWRT                  | —                | —            |

#### TABLE 12-1: TIME-OUT IN VARIOUS SITUATIONS

### TABLE 12-2: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD | Condition                          |  |  |  |

|-----|-----|----|----|------------------------------------|--|--|--|

| 0   | х   | 1  | 1  | Power-on Reset                     |  |  |  |

| u   | 0   | 1  | 1  | Brown-out Reset                    |  |  |  |

| u   | u   | 0  | u  | WDT Reset                          |  |  |  |

| u   | u   | 0  | 0  | WDT Wake-up                        |  |  |  |

| u   | u   | u  | u  | MCLR Reset during normal operation |  |  |  |

| u   | u   | 1  | 0  | MCLR Reset during Sleep            |  |  |  |

**Legend:** u = unchanged, x = unknown

#### TABLE 12-3: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT RESET

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|----------------------|------------------------------------------------|

| PCON   |       | _     | _     | _     |       | _     | POR   | BOR   | dd                   | uu                                             |

| STATUS | IRP   | RP1   | RP0   | TO    | PD    | Z     | DC    | С     | 0001 1xxx            | 000q quuu                                      |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition. Shaded cells are not used by BOR.

**Note 1:** Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

| TABLE 12-5: | INITIALIZATION CONDITION FOR REGISTERS (PIC12F615/617/HV615) |

|-------------|--------------------------------------------------------------|

|-------------|--------------------------------------------------------------|

| Register               | Address | Power-on Reset | MCLR Reset<br>WDT Reset<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep through<br>Interrupt<br>Wake-up from Sleep through<br>WDT Time-out |  |  |

|------------------------|---------|----------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|

| W                      |         | xxxx xxxx      | uuuu uuuu                                                 | սսսս սսսս                                                                             |  |  |

| INDF                   | 00h/80h | XXXX XXXX      | xxxx xxxx                                                 | uuuu uuuu                                                                             |  |  |

| TMR0                   | 01h     | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |  |  |

| PCL                    | 02h/82h | 0000 0000      | 0000 0000                                                 | PC + 1 <sup>(3)</sup>                                                                 |  |  |

| STATUS                 | 03h/83h | 0001 1xxx      | 000q quuu <b>(4)</b>                                      | uuuq quuu <sup>(4)</sup>                                                              |  |  |

| FSR                    | 04h/84h | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |  |  |

| GPIO                   | 05h     | x0 x000        | u0 u000                                                   | uu uuuu                                                                               |  |  |

| PCLATH                 | 0Ah/8Ah | 0 0000         | 0 0000                                                    | u uuuu                                                                                |  |  |

| INTCON                 | 0Bh/8Bh | 0000 0000      | 0000 0000                                                 | uuuu uuuu <sup>(2)</sup>                                                              |  |  |

| PIR1                   | 0Ch     | -000 0-00      | -000 0-00                                                 | -uuu u-uu <b>(2)</b>                                                                  |  |  |

| TMR1L                  | 0Eh     | xxxx xxxx      | uuuu uuuu                                                 | սսսս սսսս                                                                             |  |  |

| TMR1H                  | 0Fh     | xxxx xxxx      | uuuu uuuu                                                 | սսսս սսսս                                                                             |  |  |

| T1CON                  | 10h     | 0000 0000      | uuuu uuuu                                                 | -uuu uuuu                                                                             |  |  |

| TMR2 <sup>(1)</sup>    | 11h     | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |  |  |

| T2CON <sup>(1)</sup>   | 12h     | -000 0000      | -000 0000                                                 | -uuu uuuu                                                                             |  |  |

| CCPR1L <sup>(1)</sup>  | 13h     | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |  |  |

| CCPR1H <sup>(1)</sup>  | 14h     | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |  |  |

| CCP1CON <sup>(1)</sup> | 15h     | 0-00 0000      | 0-00 0000                                                 | u-uu uuuu                                                                             |  |  |

| PWM1CON <sup>(1)</sup> | 16h     | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |  |  |

| ECCPAS <sup>(1)</sup>  | 17h     | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |  |  |

| VRCON                  | 19h     | 0-00 0000      | 0-00 0000                                                 | u-uu uuuu                                                                             |  |  |

| CMCON0                 | 1Ah     | 0000 -0-0      | 0000 -0-0                                                 | uuuu -u-u                                                                             |  |  |

| CMCON1                 | 1Ch     | 0 0-10         | 0 0-10                                                    | u u-qu                                                                                |  |  |

| ADRESH <sup>(1)</sup>  | 1Eh     | xxxx xxxx      | uuuu uuuu                                                 | սսսս սսսս                                                                             |  |  |

| ADCON0 <sup>(1)</sup>  | 1Fh     | 00-0 0000      | 00-0 0000                                                 | uu-u uuuu                                                                             |  |  |

| OPTION_REG             | 81h     | 1111 1111      | 1111 1111                                                 | uuuu uuuu                                                                             |  |  |

| TRISIO                 | 85h     | 11 1111        | 11 1111                                                   | uu uuuu                                                                               |  |  |

| PIE1                   | 8Ch     | -00-0-00       | -00-0-00                                                  | -uu- u-uu                                                                             |  |  |

| PCON                   | 8Eh     | 0x             | (1, 5)                                                    |                                                                                       |  |  |

| OSCTUNE                | 90h     | 0 0000         | u uuuu                                                    | u uuuu                                                                                |  |  |

| PR2                    | 92h     | 1111 1111      | 1111 1111                                                 | 1111 1111                                                                             |  |  |

| APFCON                 | 93h     | 000            | 000                                                       | uuu                                                                                   |  |  |

| WPU                    | 95h     | 11 -111        | 11 -111                                                   | uu -uuu                                                                               |  |  |

| IOC                    | 96h     | 00 0000        | 00 0000                                                   | uu uuuu                                                                               |  |  |

| PMCON1 <sup>(6)</sup>  | 98h     | 000            | 000                                                       | uuu                                                                                   |  |  |

| PMCON2 <sup>(6)</sup>  | 99h     |                |                                                           |                                                                                       |  |  |

| PMADRL <sup>(6)</sup>  | 9Ah     | 0000 0000      | 0000 0000                                                 | սսսս սսսս                                                                             |  |  |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 12-6 for Reset value for specific condition.

5: If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

6: For PIC12F617 only.

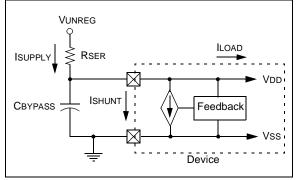

# 13.0 VOLTAGE REGULATOR

The PIC12HV609/HV615 devices include a permanent internal 5 volt (nominal) shunt regulator in parallel with the VDD pin. This eliminates the need for an external voltage regulator in systems sourced by an unregulated supply. All external devices connected directly to the VDD pin will share the regulated supply voltage and contribute to the total VDD supply current (ILOAD).

### 13.1 Regulator Operation

A shunt regulator generates a specific supply voltage by creating a voltage drop across a pass resistor RSER. The voltage at the VDD pin of the microcontroller is monitored and compared to an internal voltage reference. The current through the resistor is then adjusted, based on the result of the comparison, to produce a voltage drop equal to the difference between the supply voltage VUNREG and the VDD of the microcontroller. See Figure 13-1 for voltage regulator schematic.

An external current limiting resistor, RSER, located between the unregulated supply, VUNREG, and the VDD pin, drops the difference in voltage between VUNREG and VDD. RSER must be between RMAX and RMIN as defined by Equation 13-1.

### EQUATION 13-1: RSER LIMITING RESISTOR

$$RMAX = \frac{(VUMIN - 5V)}{1.05 \cdot (4 MA + ILOAD)}$$

$$RMIN = \frac{(VUMAX - 5V)}{0.95 \cdot (50 \text{ MA})}$$

Where:

RMAX = maximum value of RSER (ohms)

RMIN = minimum value of RSER (ohms)

VUMIN = minimum value of VUNREG

VUMAX = maximum value of VUNREG

VDD = regulated voltage (5V nominal)

- ILOAD = maximum expected load current in mA including I/O pin currents and external circuits connected to VDD.

- 1.05 = compensation for +5% tolerance of RSER

- 0.95 = compensation for -5% tolerance of RSER

## 13.2 Regulator Considerations

The supply voltage VUNREG and load current are not constant. Therefore, the current range of the regulator is limited. Selecting a value for RSER must take these three factors into consideration.

Since the regulator uses the band gap voltage as the regulated voltage reference, this voltage reference is permanently enabled in the PIC12HV609/HV615 devices.

The shunt regulator will still consume current when below operating voltage range for the shunt regulator.

## 13.3 Design Considerations

For more information on using the shunt regulator and managing current load, see Application Note AN1035, "*Designing with HV Microcontrollers*" (DS01035).

NOTES:

### 16.8 DC Characteristics: PIC12F609/615/617/12HV609/615-I (Industrial) PIC12F609/615/617/12HV609/615-E (Extended)

| DC CHARACTERISTICS |      |                                          | Standard Operat<br>Operating temper | ditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |          |       |                                                                    |  |

|--------------------|------|------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------|-------|--------------------------------------------------------------------|--|

| Param<br>No.       | Sym  | Characteristic                           | Min                                 | Тур†                                                                                                                           | Мах      | Units | Conditions                                                         |  |

|                    | VIL  | Input Low Voltage                        |                                     |                                                                                                                                |          |       |                                                                    |  |

|                    |      | I/O port:                                |                                     |                                                                                                                                |          |       |                                                                    |  |

| D030               |      | with TTL buffer                          | Vss                                 | —                                                                                                                              | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                   |  |

| D030A              |      |                                          | Vss                                 | —                                                                                                                              | 0.15 Vdd | V     | $2.0V \leq V \text{DD} \leq 4.5 \text{V}$                          |  |

| D031               |      | with Schmitt Trigger buffer              | Vss                                 | _                                                                                                                              | 0.2 Vdd  | V     | $2.0V \le VDD \le 5.5V$                                            |  |

| D032               |      | MCLR, OSC1 (RC mode)                     | Vss                                 | _                                                                                                                              | 0.2 Vdd  | V     | (NOTE 1)                                                           |  |

| D033               |      | OSC1 (XT and LP modes)                   | Vss                                 | _                                                                                                                              | 0.3      | V     |                                                                    |  |

| D033A              |      | OSC1 (HS mode)                           | Vss                                 | —                                                                                                                              | 0.3 VDD  | V     |                                                                    |  |

|                    | VIH  | Input High Voltage                       |                                     |                                                                                                                                |          |       |                                                                    |  |

|                    |      | I/O ports:                               |                                     | _                                                                                                                              |          |       |                                                                    |  |

| D040               |      | with TTL buffer                          | 2.0                                 | _                                                                                                                              | Vdd      | V     | $4.5V \leq V \text{DD} \leq 5.5V$                                  |  |

| D040A              |      |                                          | 0.25 VDD + 0.8                      | —                                                                                                                              | Vdd      | V     | $2.0V \leq V \text{DD} \leq 4.5 \text{V}$                          |  |

| D041               |      | with Schmitt Trigger buffer              | 0.8 Vdd                             | —                                                                                                                              | Vdd      | V     | $2.0V \leq V \text{DD} \leq 5.5 \text{V}$                          |  |

| D042               |      | MCLR                                     | 0.8 Vdd                             | —                                                                                                                              | Vdd      | V     |                                                                    |  |

| D043               |      | OSC1 (XT and LP modes)                   | 1.6                                 | —                                                                                                                              | Vdd      | V     |                                                                    |  |

| D043A              |      | OSC1 (HS mode)                           | 0.7 Vdd                             | _                                                                                                                              | Vdd      | V     |                                                                    |  |

| D043B              |      | OSC1 (RC mode)                           | 0.9 Vdd                             | —                                                                                                                              | Vdd      | V     | (NOTE 1)                                                           |  |

|                    | lı∟  | Input Leakage Current <sup>(2,3)</sup>   |                                     |                                                                                                                                |          |       |                                                                    |  |

| D060               |      | I/O ports                                | _                                   | ± 0.1                                                                                                                          | ± 1      | μΑ    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance                   |  |

| D061               |      | GP3/MCLR <sup>(3,4)</sup>                | —                                   | $\pm0.7$                                                                                                                       | $\pm5$   | μΑ    | $V\text{SS} \leq V\text{PIN} \leq V\text{DD}$                      |  |

| D063               |      | OSC1                                     | —                                   | ± 0.1                                                                                                                          | ± 5      | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration |  |

| D070*              | IPUR | GPIO Weak Pull-up Current <sup>(5)</sup> | 50                                  | 250                                                                                                                            | 400      | μΑ    | VDD = 5.0V, VPIN = VSS                                             |  |

|                    | Vol  | Output Low Voltage                       | _                                   | _                                                                                                                              | 0.6      | V     | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                       |  |

| D080               |      | I/O ports                                | _                                   | -                                                                                                                              | 0.6      | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                        |  |

|                    | Vон  | Output High Voltage                      | Vdd - 0.7                           | —                                                                                                                              | —        | V     | IOH = -2.5mA, VDD = 4.5V,<br>-40°С to +125°С                       |  |

| D090               |      | I/O ports <sup>(2)</sup>                 | Vdd - 0.7                           | -                                                                                                                              | -        | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                       |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: This specification applies to GP3/MCLR configured as GP3 with the internal weak pull-up disabled.

5: This specification applies to all weak pull-up pins, including the weak pull-up found on GP3/MCLR. When GP3/MCLR is configured as MCLR reset pin, the weak pull-up is always enabled.

6: Applies to PIC12F617 only.

### 16.11 AC Characteristics: PIC12F609/615/617/12HV609/615 (Industrial, Extended)

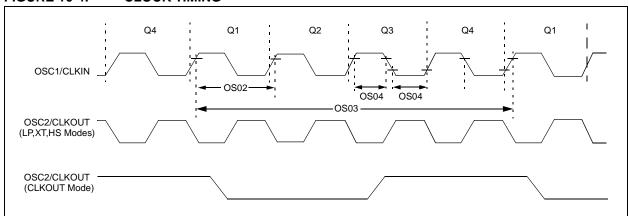

#### FIGURE 16-4: CLOCK TIMING

### TABLE 16-1: CLOCK OSCILLATOR TIMING REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |       |                                         |     |        |          |       |                    |  |

|----------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------|-----|--------|----------|-------|--------------------|--|

| Param<br>No.                                                                                                         | Sym   | Characteristic                          | Min | Тур†   | Max      | Units | Conditions         |  |

| OS01                                                                                                                 | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC  | —      | 37       | kHz   | LP Oscillator mode |  |

|                                                                                                                      |       |                                         | DC  | —      | 4        | MHz   | XT Oscillator mode |  |

|                                                                                                                      |       |                                         | DC  | _      | 20       | MHz   | HS Oscillator mode |  |

|                                                                                                                      |       |                                         | DC  | —      | 20       | MHz   | EC Oscillator mode |  |

|                                                                                                                      |       | Oscillator Frequency <sup>(1)</sup>     | _   | 32.768 | _        | kHz   | LP Oscillator mode |  |

|                                                                                                                      |       |                                         | 0.1 | _      | 4        | MHz   | XT Oscillator mode |  |

|                                                                                                                      |       |                                         | 1   | —      | 20       | MHz   | HS Oscillator mode |  |

|                                                                                                                      |       |                                         | DC  | —      | 4        | MHz   | RC Oscillator mode |  |

| OS02                                                                                                                 | Tosc  | External CLKIN Period <sup>(1)</sup>    | 27  | _      | ×        | μS    | LP Oscillator mode |  |

|                                                                                                                      |       |                                         | 250 | —      | ×        | ns    | XT Oscillator mode |  |

|                                                                                                                      |       |                                         | 50  | —      | ×        | ns    | HS Oscillator mode |  |

|                                                                                                                      |       |                                         | 50  | —      | $\infty$ | ns    | EC Oscillator mode |  |

|                                                                                                                      |       | Oscillator Period <sup>(1)</sup>        | —   | 30.5   | —        | μS    | LP Oscillator mode |  |

|                                                                                                                      |       |                                         | 250 | —      | 10,000   | ns    | XT Oscillator mode |  |

|                                                                                                                      |       |                                         | 50  | _      | 1,000    | ns    | HS Oscillator mode |  |

|                                                                                                                      |       |                                         | 250 | —      | —        | ns    | RC Oscillator mode |  |

| OS03                                                                                                                 | Тсү   | Instruction Cycle Time <sup>(1)</sup>   | 200 | Тсү    | DC       | ns    | Tcy = 4/Fosc       |  |

| OS04*                                                                                                                | TosH, | External CLKIN High,                    | 2   | —      | —        | μS    | LP oscillator      |  |

|                                                                                                                      | TosL  | External CLKIN Low                      | 100 | -      | —        | ns    | XT oscillator      |  |

|                                                                                                                      |       |                                         | 20  | —      |          | ns    | HS oscillator      |  |

| OS05*                                                                                                                | TosR, | External CLKIN Rise,                    | 0   | —      | ~        | ns    | LP oscillator      |  |

|                                                                                                                      | TosF  | External CLKIN Fall                     | 0   | -      | $\infty$ | ns    | XT oscillator      |  |

|                                                                                                                      |       |                                         | 0   |        | ×        | ns    | HS oscillator      |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note** 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

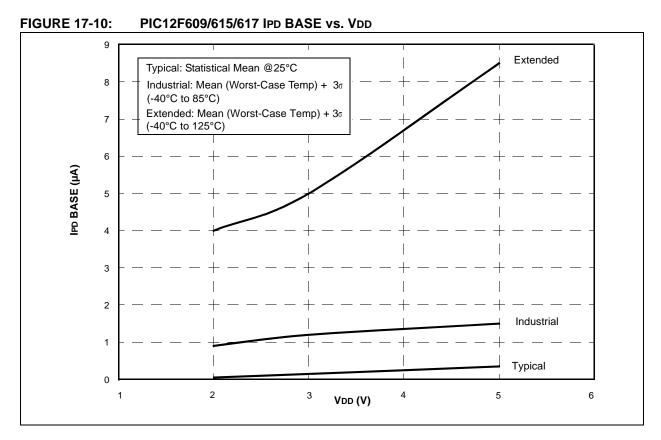

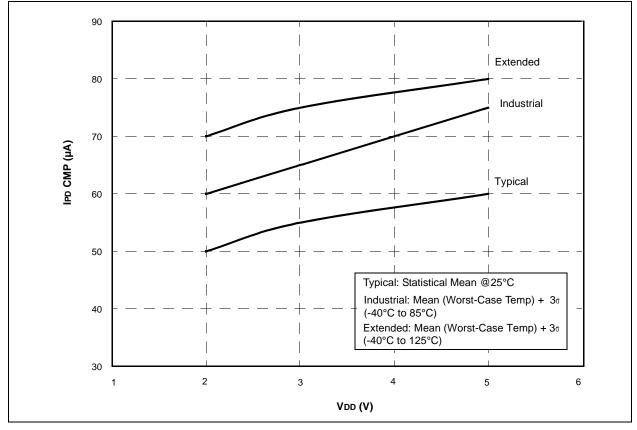

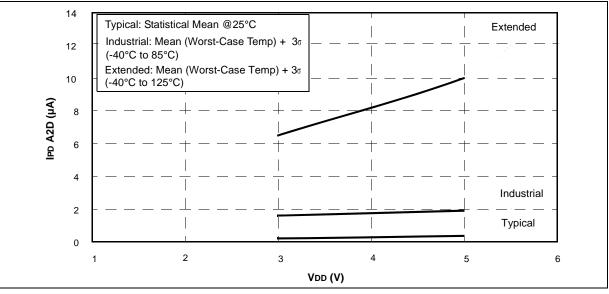

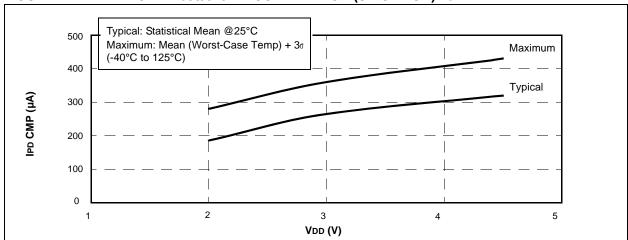

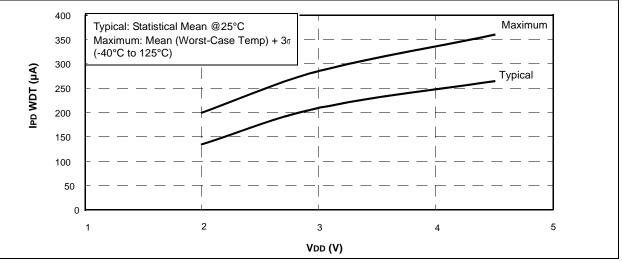

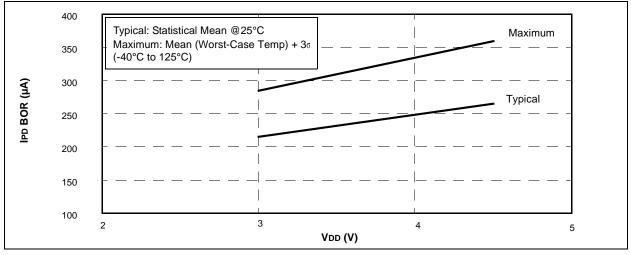

### FIGURE 17-27: PIC12HV609/615 IPD COMPARATOR (SINGLE ON) vs. VDD

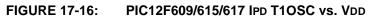

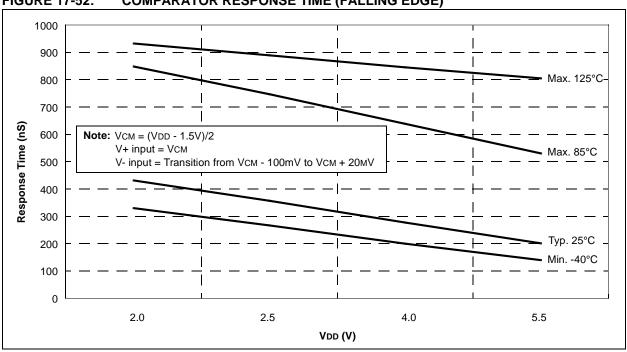

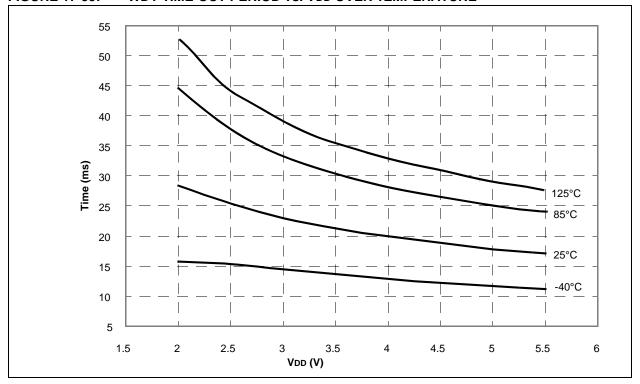

FIGURE 17-52: COMPARATOR RESPONSE TIME (FALLING EDGE)

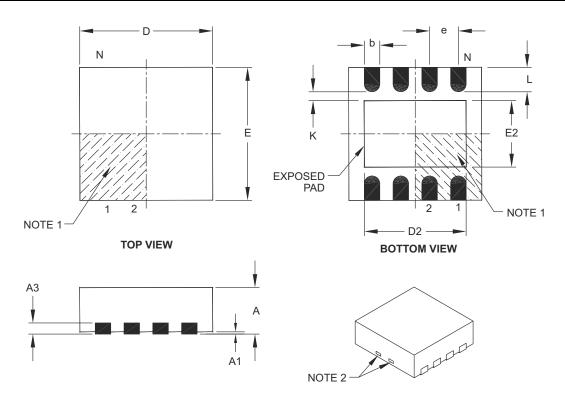

### 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |          |          |      |  |  |  |

|------------------------|------------------|----------|----------|------|--|--|--|

| Dimensio               | Dimension Limits |          |          |      |  |  |  |

| Number of Pins         | Ν                | 8        |          |      |  |  |  |

| Pitch                  | е                |          | 0.80 BSC |      |  |  |  |

| Overall Height         | А                | 0.80     | 0.90     | 1.00 |  |  |  |

| Standoff               | A1               | 0.00     | 0.02     | 0.05 |  |  |  |

| Contact Thickness      | A3               | 0.20 REF |          |      |  |  |  |

| Overall Length         |                  | 4.00 BSC |          |      |  |  |  |

| Exposed Pad Width      | E2               | 0.00     | 2.20     | 2.80 |  |  |  |

| Overall Width          | E                | 4.00 BSC |          |      |  |  |  |

| Exposed Pad Length     | D2               | 0.00     | 3.00     | 3.60 |  |  |  |

| Contact Width          | b                | 0.25     | 0.30     | 0.35 |  |  |  |

| Contact Length         | L                | 0.30     | 0.40     | 0.50 |  |  |  |

| Contact-to-Exposed Pad | K                | 0.20     | -        | -    |  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-131D

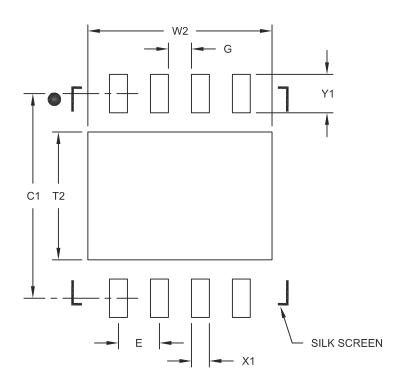

## 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |      |          |      |  |  |

|----------------------------|-------------|------|----------|------|--|--|

| Dimensior                  | MIN         | NOM  | MAX      |      |  |  |

| Contact Pitch              | E           |      | 0.80 BSC |      |  |  |

| Optional Center Pad Width  | W2          |      |          | 3.60 |  |  |

| Optional Center Pad Length | T2          |      |          | 2.50 |  |  |

| Contact Pad Spacing        | C1          |      | 4.00     |      |  |  |

| Contact Pad Width (X8)     | X1          |      |          | 0.35 |  |  |

| Contact Pad Length (X8)    | Y1          |      |          | 0.75 |  |  |

| Distance Between Pads      | G           | 0.45 |          |      |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2131B