# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 64 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                    |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-VDFN Exposed Pad                                                         |

| Supplier Device Package    | 8-DFN (4x4)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12hv609t-i-md |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Device     | Program<br>Memory | Data Memory  | Self Read/ | 1/0 | 10-bit A/D | Comparators | ECCP | Timers   | Voltago Bango     |

|------------|-------------------|--------------|------------|-----|------------|-------------|------|----------|-------------------|

| Device     | Flash<br>(words)  | SRAM (bytes) | Self Write | 10  | (ch)       | Comparators | ECCP | 8/16-bit | Voltage Range     |

| PIC12F609  | 1024              | 64           | —          | 5   | 0          | 1           | _    | 1/1      | 2.0V-5.5V         |

| PIC12HV609 | 1024              | 64           | —          | 5   | 0          | 1           |      | 1/1      | 2.0V-user defined |

| PIC12F615  | 1024              | 64           | —          | 5   | 4          | 1           | YES  | 2/1      | 2.0V-5.5V         |

| PIC12HV615 | 1024              | 64           | —          | 5   | 4          | 1           | YES  | 2/1      | 2.0V-user defined |

| PIC12F617  | 2048              | 128          | YES        | 5   | 4          | 1           | YES  | 2/1      | 2.0V-5.5V         |

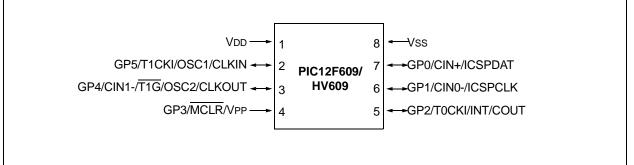

## 8-Pin Diagram, PIC12F609/HV609 (PDIP, SOIC, MSOP, DFN)

## TABLE 1: PIC12F609/HV609 PIN SUMMARY (PDIP, SOIC, MSOP, DFN)

| I/O                | Pin | Comparators | Timer | Interrupts | Pull-ups | Basic       |

|--------------------|-----|-------------|-------|------------|----------|-------------|

| GP0                | 7   | CIN+        | _     | IOC        | Y        | ICSPDAT     |

| GP1                | 6   | CIN0-       | —     | IOC        | Y        | ICSPCLK     |

| GP2                | 5   | COUT        | TOCKI | INT/IOC    | Y        | —           |

| GP3 <sup>(1)</sup> | 4   | _           |       | IOC        | Y(2)     | MCLR/VPP    |

| GP4                | 3   | CIN1-       | T1G   | IOC        | Y        | OSC2/CLKOUT |

| GP5                | 2   | —           | T1CKI | IOC        | Y        | OSC1/CLKIN  |

| _                  | 1   | -           |       | _          |          | Vdd         |

|                    | 8   | _           | _     | _          | _        | Vss         |

Note 1: Input only.

2: Only when pin is configured for external MCLR.

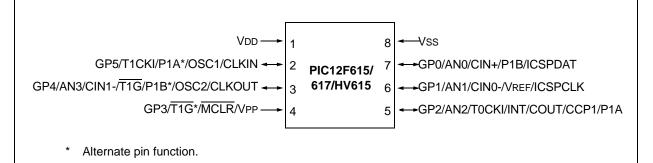

## 8-Pin Diagram, PIC12F615/617/HV615 (PDIP, SOIC, MSOP, DFN)

### TABLE 2: PIC12F615/617/HV615 PIN SUMMARY (PDIP, SOIC, MSOP, DFN)

| I/O                | Pin      | Analog                     | Comparator<br>s | Timer | ССР      | Interrupts | Pull-ups | Basic        |

|--------------------|----------|----------------------------|-----------------|-------|----------|------------|----------|--------------|

| GP0                | 7        | AN0                        | CIN+            | _     | P1B      | IOC        | Y        | ICSPDAT      |

| GP1                | 6        | AN1                        | CIN0-           | —     | —        | IOC        | Y        | ICSPCLK/VREF |

| GP2                | 5        | AN2                        | COUT            | T0CKI | CCP1/P1A | INT/IOC    | Y        | —            |

| GP3 <sup>(1)</sup> | 4        |                            | —               | T1G*  | _        | IOC        | Y(2)     | MCLR/Vpp     |

| GP4                | 3        | AN3                        | CIN1-           | T1G   | P1B*     | IOC        | Y        | OSC2/CLKOUT  |

| GP5                | 2        | -                          | —               | T1CKI | P1A*     | IOC        | Y        | OSC1/CLKIN   |

| —                  | 1        | —                          | —               | —     | —        | —          | —        | Vdd          |

| —                  | 8        |                            | —               | _     | _        | _          | —        | Vss          |

|                    | * ^ 14 - | and a first for the second |                 |       |          |            |          |              |

\* Alternate pin function.

Note 1: Input only.

2: Only when pin is configured for external MCLR.

| Name                                   | Function | Input<br>Type | Output<br>Type | Description                                                        |

|----------------------------------------|----------|---------------|----------------|--------------------------------------------------------------------|

| GP0/AN0/CIN+/P1B/ICSPDAT               | GP0      | TTL           | CMOS           | General purpose I/O with prog. pull-up and interrupt-on-<br>change |

|                                        | AN0      | AN            |                | A/D Channel 0 input                                                |

|                                        | CIN+     | AN            | _              | Comparator non-inverting input                                     |

|                                        | P1B      | _             | CMOS           | PWM output                                                         |

|                                        | ICSPDAT  | ST            | CMOS           | Serial Programming Data I/O                                        |

| GP1/AN1/CIN0-/VREF/ICSPCLK             | GP1      | TTL           | CMOS           | General purpose I/O with prog. pull-up and interrupt-on-<br>change |

|                                        | AN1      | AN            | —              | A/D Channel 1 input                                                |

|                                        | CIN0-    | AN            | _              | Comparator inverting input                                         |

|                                        | VREF     | AN            | _              | External Voltage Reference for A/D                                 |

|                                        | ICSPCLK  | ST            | _              | Serial Programming Clock                                           |

| GP2/AN2/T0CKI/INT/COUT/CCP1/<br>P1A    | GP2      | ST            | CMOS           | General purpose I/O with prog. pull-up and interrupt-on-<br>change |

|                                        | AN2      | AN            | —              | A/D Channel 2 input                                                |

|                                        | TOCKI    | ST            | _              | Timer0 clock input                                                 |

|                                        | INT      | ST            | —              | External Interrupt                                                 |

|                                        | COUT     | _             | CMOS           | Comparator output                                                  |

|                                        | CCP1     | ST            | CMOS           | Capture input/Compare input/PWM output                             |

|                                        | P1A      | —             | CMOS           | PWM output                                                         |

| GP3/T1G*/MCLR/VPP                      | GP3      | TTL           | —              | General purpose input with interrupt-on-change                     |

|                                        | T1G*     | ST            | _              | Timer1 gate (count enable), alternate pin                          |

|                                        | MCLR     | ST            |                | Master Clear w/internal pull-up                                    |

|                                        | Vpp      | HV            | _              | Programming voltage                                                |

| GP4/AN3/CIN1-/T1G/P1B*/OSC2/<br>CLKOUT | GP4      | TTL           | CMOS           | General purpose I/O with prog. pull-up and interrupt-on-<br>change |

|                                        | AN3      | AN            |                | A/D Channel 3 input                                                |

|                                        | CIN1-    | AN            | _              | Comparator inverting input                                         |

|                                        | T1G      | ST            |                | Timer1 gate (count enable)                                         |

|                                        | P1B*     | _             | CMOS           | PWM output, alternate pin                                          |

|                                        | OSC2     | _             | XTAL           | Crystal/Resonator                                                  |

|                                        | CLKOUT   | _             | CMOS           | Fosc/4 output                                                      |

| GP5/T1CKI/P1A*/OSC1/CLKIN              | GP5      | TTL           | CMOS           | General purpose I/O with prog. pull-up and interrupt-on-<br>change |

|                                        | T1CKI    | ST            | _              | Timer1 clock input                                                 |

|                                        | P1A*     | _             | CMOS           | PWM output, alternate pin                                          |

|                                        | OSC1     | XTAL          | _              | Crystal/Resonator                                                  |

|                                        | CLKIN    | ST            | _              | External clock input/RC oscillator connection                      |

| Vdd                                    | Vdd      | Power         | _              | Positive supply                                                    |

| Vss                                    | Vss      | Power         |                | Ground reference                                                   |

#### **TABLE 1-2:** PIC12F615/617/HV615 PINOUT DESCRIPTION

\* Alternate pin function.

Legend: AN=Analog input or output

CMOS=CMOS compatible input or output HV= High Voltage ST=Schmitt Trigger input with CMOS levels TTL = TTL compatible input

XTAL=Crystal

| Addr   | Name   | Bit 7              | Bit 6              | Bit 5          | Bit 4          | Bit 3           | Bit 2          | Bit 1          | Bit 0    | Value on<br>POR, BOR | Page    |

|--------|--------|--------------------|--------------------|----------------|----------------|-----------------|----------------|----------------|----------|----------------------|---------|

| Bank 0 |        |                    |                    |                |                |                 |                |                |          |                      |         |

| 00h    | INDF   | Addressing         | this location      | uses content   | ts of FSR to a | address data    | memory (not    | t a physical r | egister) | xxxx xxxx            | 25, 119 |

| 01h    | TMR0   | Timer0 Mod         | lule's Registe     | er             |                |                 |                |                |          | xxxx xxxx            | 53, 11  |

| 02h    | PCL    | Program Co         | ounter's (PC)      | Least Signifi  | cant Byte      |                 | _              |                |          | 0000 0000            | 25, 11  |

| 03h    | STATUS | IRP <sup>(1)</sup> | RP1 <sup>(1)</sup> | RP0            | ТО             | PD              | Z              | DC             | С        | 0001 1xxx            | 18, 11  |

| 04h    | FSR    | Indirect Dat       | a Memory Ac        | dress Pointe   | er             |                 |                |                |          | xxxx xxxx            | 25, 11  |

| 05h    | GPIO   | -                  | _                  | GP5            | GP4            | GP3             | GP2            | GP1            | GP0      | x0 x000              | 43, 11  |

| 06h    | _      | Unimpleme          | nted               |                |                |                 |                |                |          | —                    | —       |

| 07h    | _      | Unimpleme          | nted               |                |                |                 |                |                |          | —                    | —       |

| 08h    | _      | Unimpleme          | nted               |                |                |                 |                |                |          | —                    | —       |

| 09h    | _      | Unimpleme          | nted               |                |                |                 |                |                |          | —                    | —       |

| 0Ah    | PCLATH | _                  | _                  | _              | Write          | e Buffer for up | oper 5 bits of | Program Co     | unter    | 0 0000               | 25, 11  |

| 0Bh    | INTCON | GIE                | PEIE               | T0IE           | INTE           | GPIE            | T0IF           | INTF           | GPIF     | 0000 0000            | 20, 11  |

| 0Ch    | PIR1   | _                  | _                  | _              | _              | CMIF            | -              | _              | TMR1IF   | 00                   | 22, 11  |

| 0Dh    | —      | Unimpleme          | nted               |                |                |                 |                |                |          | —                    | _       |

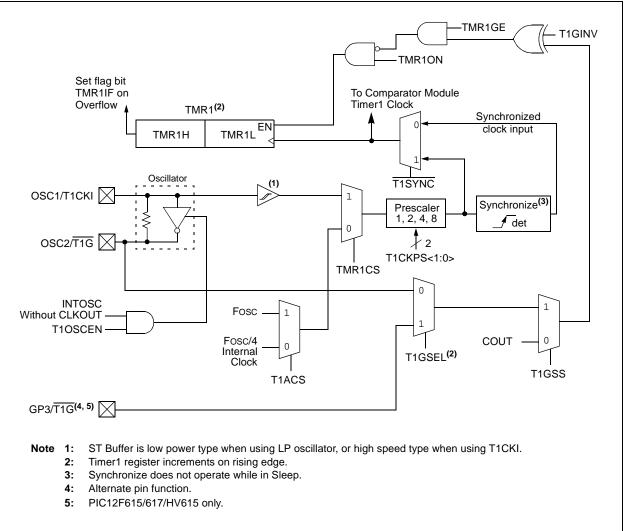

| 0Eh    | TMR1L  | Holding Reg        | gister for the     | Least Signific | cant Byte of t | he 16-bit TM    | R1 Register    |                |          | xxxx xxxx            | 57, 11  |

| 0Fh    | TMR1H  | Holding Reg        | gister for the     | Most Signific  | ant Byte of th | ne 16-bit TMF   | R1 Register    |                |          | xxxx xxxx            | 57, 11  |

| 10h    | T1CON  | T1GINV             | TMR1GE             | T1CKPS1        | T1CKPS0        | T1OSCEN         | T1SYNC         | TMR1CS         | TMR10N   | 0000 0000            | 62, 11  |

| 11h    | _      | Unimpleme          | nted               |                | •              |                 |                | •              | •        | _                    |         |

| 12h    | _      | Unimpleme          | nted               |                |                |                 |                |                |          | _                    |         |

| 13h    | _      | Unimpleme          | nted               |                |                |                 |                |                |          | _                    |         |

| 14h    | —      | Unimpleme          | nted               |                |                |                 |                |                |          | —                    |         |

| 15h    | —      | Unimpleme          | nted               |                |                |                 |                |                |          | —                    |         |

| 16h    | —      | Unimpleme          | nted               |                |                |                 |                |                |          | —                    |         |

| 17h    | —      | Unimpleme          | nted               |                |                |                 |                |                |          | —                    |         |

| 18h    | —      | Unimpleme          | nted               |                |                |                 |                |                |          | —                    |         |

| 19h    | VRCON  | CMVREN             | _                  | VRR            | FVREN          | VR3             | VR2            | VR1            | VR0      | 0-00 0000            | 76, 11  |

| 1Ah    | CMCON0 | CMON               | COUT               | CMOE           | CMPOL          | —               | CMR            | —              | CMCH     | 0000 -0-0            | 72, 11  |

| 1Bh    | —      |                    |                    |                |                | —               |                | —              |          | —                    |         |

| 1Ch    | CMCON1 | _                  | _                  | _              | T1ACS          | CMHYS           | _              | T1GSS          | CMSYNC   | 0 0-10               | 73, 11  |

| 1Dh    | —      | Unimpleme          | nted               |                |                |                 |                |                |          | _                    | —       |

| 1Eh    | _      | Unimpleme          | nted               |                |                |                 |                |                |          | _                    | _       |

| 1Fh    | _      | Unimpleme          | nted               |                |                |                 |                |                |          | _                    |         |

#### **TABLE 2-1:** PIC12F609/HV609 SPECIAL FUNCTION REGISTERS SUMMARY BANK 0

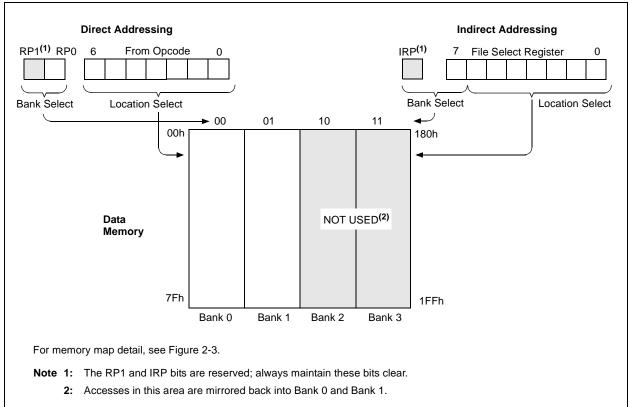

IRP and RP1 bits are reserved, always maintain these bits clear. 1:

2: Read only register.

### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, GPIO change and external GP2/INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | GPIE  | T0IF  | INTF  | GPIF  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | GIE: Global Interrupt Enable bit<br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts                                                                                        |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                      |

| bit 5 | <b>TolE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                    |

| bit 4 | INTE: GP2/INT External Interrupt Enable bit<br>1 = Enables the GP2/INT external interrupt<br>0 = Disables the GP2/INT external interrupt                                                      |

| bit 3 | <b>GPIE:</b> GPIO Change Interrupt Enable bit <sup>(1)</sup><br>1 = Enables the GPIO change interrupt<br>0 = Disables the GPIO change interrupt                                               |

| bit 2 | <b>T0IF:</b> Timer0 Overflow Interrupt Flag bit <sup>(2)</sup><br>1 = Timer0 register has overflowed (must be cleared in software)<br>0 = Timer0 register did not overflow                    |

| bit 1 | INTF: GP2/INT External Interrupt Flag bit<br>1 = The GP2/INT external interrupt occurred (must be cleared in software)<br>0 = The GP2/INT external interrupt did not occur                    |

| bit 0 | <b>GPIF:</b> GPIO Change Interrupt Flag bit<br>1 = When at least one of the GPIO <5:0> pins changed state (must be cleared in software)<br>0 = None of the GPIO <5:0> pins have changed state |

**Note 1:** IOC register must also be enabled.

2: T0IF bit is set when TMR0 rolls over. TMR0 is unchanged on Reset and should be initialized before clearing T0IF bit.

### 2.2.2.4 PIE1 Register

The PIE1 register contains the Peripheral Interrupt Enable bits, as shown in Register 2-4.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

#### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| U-0   | R/W-0               | R/W-0                 | U-0 | R/W-0 | U-0 | R/W-0                 | R/W-0  |

|-------|---------------------|-----------------------|-----|-------|-----|-----------------------|--------|

| —     | ADIE <sup>(1)</sup> | CCP1IE <sup>(1)</sup> | _   | CMIE  | —   | TMR2IE <sup>(1)</sup> | TMR1IE |

| bit 7 |                     |                       |     |       |     |                       | bit 0  |

| Legend:    |             |                                                                 |                                    |                    |  |  |  |  |

|------------|-------------|-----------------------------------------------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Reada  | able bit    | W = Writable bit                                                | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value | at POR      | '1' = Bit is set                                                | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

|            |             |                                                                 |                                    |                    |  |  |  |  |

| bit 7      | -           | emented: Read as '0'                                            |                                    |                    |  |  |  |  |

| bit 6      | ADIE: A     | D Converter (ADC) Interrupt                                     | Enable bit <sup>(1)</sup>          |                    |  |  |  |  |

|            |             | bles the ADC interrupt bles the ADC interrupt                   |                                    |                    |  |  |  |  |

| bit 5      | CCP1IE      | CCP1 Interrupt Enable bit <sup>(1)</sup>                        | )                                  |                    |  |  |  |  |

|            |             | bles the CCP1 interrupt<br>bles the CCP1 interrupt              |                                    |                    |  |  |  |  |

| bit 4      | Unimple     | mented: Read as '0'                                             |                                    |                    |  |  |  |  |

| bit 3      | CMIE: C     | omparator Interrupt Enable b                                    | bit                                |                    |  |  |  |  |

|            |             | bles the Comparator interrupt<br>bles the Comparator interrup   |                                    |                    |  |  |  |  |

| bit 2      | Unimple     | mented: Read as '0'                                             |                                    |                    |  |  |  |  |

| bit 1      | TMR2IE      | Timer2 to PR2 Match Interr                                      | upt Enable bit <sup>(1)</sup>      |                    |  |  |  |  |

|            |             | bles the Timer2 to PR2 match<br>bles the Timer2 to PR2 matc     | 1                                  |                    |  |  |  |  |

| bit 0      | TMR1IE      | : Timer1 Overflow Interrupt E                                   | nable bit                          |                    |  |  |  |  |

|            |             | bles the Timer1 overflow inter<br>bles the Timer1 overflow inte | •                                  |                    |  |  |  |  |

| Note 1:    | PIC12F615/6 | 617/HV615 only. PIC12F609/                                      | HV609 unimplemented, read          | as '0'.            |  |  |  |  |

### FIGURE 2-6: DIRECT/INDIRECT ADDRESSING PIC12F609/615/617/12HV609/615

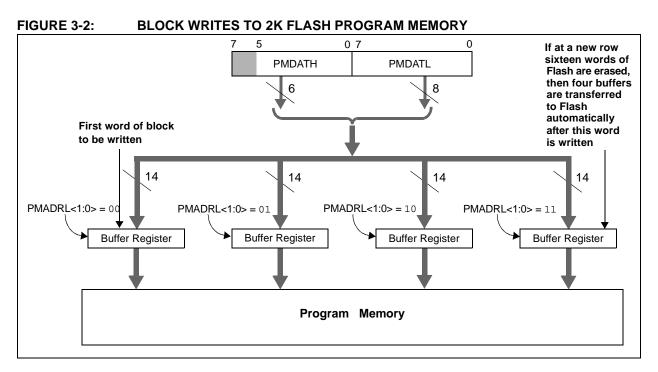

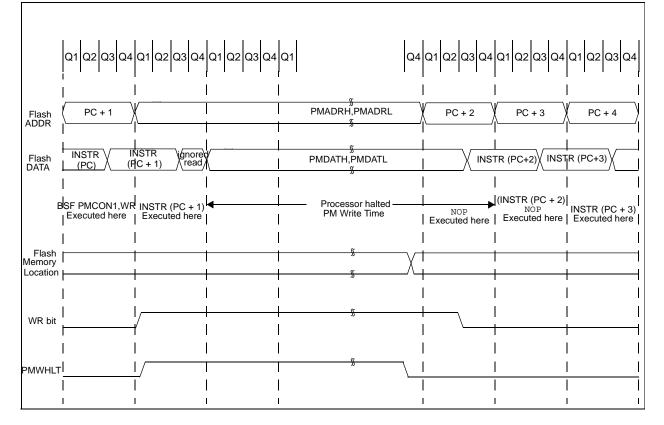

#### TABLE 3-1: SUMMARY OF REGISTERS ASSOCIATED WITH PROGRAM MEMORY

| Name   | Bit 7      | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|------------|--------------|---------|---------|---------|---------|---------|---------|----------------------|---------------------------------|

| PMCON1 | —          | _            | _       | -       | -       | WREN    | WR      | RD      | 000                  | 000                             |

| PMCON2 | Program Me | emory Contro |         |         |         |         |         |         |                      |                                 |

| PMADRL | PMADRL7    | PMADRL6      | PMADRL5 | PMADRL4 | PMADRL3 | PMADRL2 | PMADRL1 | PMADRL0 | 0000 0000            | 0000 0000                       |

| PMADRH | _          | _            | -       | -       |         | PMADRH2 | PMADRH1 | PMADRH0 | 000                  | 000                             |

| PMDATL | PMDATL7    | PMDATL6      | PMDATL5 | PMDATL4 | PMDATL3 | PMDATL2 | PMDATL1 | PMDATL0 | 0000 0000            | 0000 0000                       |

| PMDATH | _          | _            | PMDATH5 | PMDATH4 | PMDATH3 | PMDATH2 | PMDATH1 | PMDATH0 | 00 0000              | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by Program Memory module.

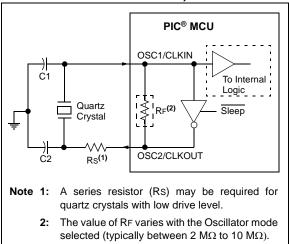

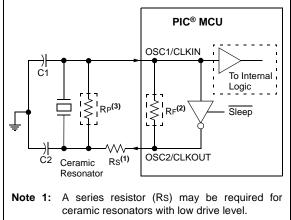

### 4.3.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 4-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 4-3 and Figure 4-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

#### FIGURE 4-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

#### CERAMIC RESONATOR OPERATION (XT OR HS MODE)

- 2: The value of RF varies with the Oscillator mode selected (typically between 2 M $\Omega$  to 10 M $\Omega$ ).

- **3:** An additional parallel feedback resistor (RP) may be required for proper ceramic resonator operation.

### TABLE 5-1:SUMMARY OF REGISTERS ASSOCIATED WITH GPIO

| Name                   | Bit 7  | Bit 6                | Bit 5                | Bit 4                | Bit 3   | Bit 2               | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|----------------------|----------------------|----------------------|---------|---------------------|---------|---------|----------------------|---------------------------------|

| ANSEL                  | —      | ADCS2 <sup>(1)</sup> | ADCS1 <sup>(1)</sup> | ADCS0 <sup>(1)</sup> | ANS3    | ANS2 <sup>(1)</sup> | ANS1    | ANS0    | -000 1111            | -000 1111                       |

| CMCON0                 | CMON   | COUT                 | CMOE                 | CMPOL                | _       | CMR                 | _       | CMCH    | 0000 -0-0            | 0000 -0-0                       |

| INTCON                 | GIE    | PEIE                 | TOIE                 | INTE                 | GPIE    | T0IF                | INTF    | GPIF    | 0000 0000            | 0000 0000                       |

| IOC                    | _      | _                    | IOC5                 | IOC4                 | IOC3    | IOC2                | IOC1    | IOC0    | 00 0000              | 00 0000                         |

| OPTION_REG             | GPPU   | INTEDG               | TOCS                 | T0SE                 | PSA     | PS2                 | PS1     | PS0     | 1111 1111            | 1111 1111                       |

| GPIO                   | _      | _                    | GP5                  | GP4                  | GP3     | GP2                 | GP1     | GP0     | xx xxxx              | u0 u000                         |

| TRISIO                 | _      | _                    | TRISIO5              | TRISIO4              | TRISIO3 | TRISIO2             | TRISIO1 | TRISIO0 | 11 1111              | 11 1111                         |

| WPU                    | _      | _                    | WPU5                 | WPU4                 | WPU3    | WPU2                | WPU1    | WPU0    | 11 1111              | 11 -111                         |

| T1CON                  | T1GINV | TMR1GE               | TICKPS1              | T1CKPS0              | T1OSCEN | T1SYNC              | TMR1CS  | TMR10N  | 0000 0000            | uuuu uuuu                       |

| CCP1CON <sup>(1)</sup> | P1M    | _                    | DC1B1                | DC1B0                | CCP1M3  | CCP1M2              | CCP1M1  | CCP1M0  | 0-00 0000            | 0-00 0000                       |

| APFCON <sup>(1)</sup>  | —      | —                    | _                    | T1GSEL               | —       | —                   | P1BSEL  | P1ASEL  | 000                  | 000                             |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by GPIO. Note 1: PIC12F615/617/HV615 only.

### FIGURE 7-1: TIMER1 BLOCK DIAGRAM

### 10.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- Results formatting

#### 10.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. See the corresponding port section for more information.

| Note: | Analog voltages on any pin that is defined |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | as a digital input may cause the input     |  |  |  |  |  |  |  |  |

|       | buffer to conduct excess current.          |  |  |  |  |  |  |  |  |

#### 10.1.2 CHANNEL SELECTION

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 10.2 "ADC Operation"** for more information.

### 10.1.3 ADC VOLTAGE REFERENCE

The VCFG bit of the ADCON0 register provides control of the positive voltage reference. The positive voltage reference can be either VDD or an external voltage source. The negative voltage reference is always connected to the ground reference.

### 10.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ANSEL register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11 TAD periods as shown in Figure 10-3.

For correct conversion, the appropriate TAD specification must be met. See A/D conversion requirements in **Section 16.0** "**Electrical Specifications**" for more information. Table 10-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

### 11.3 PWM Mode

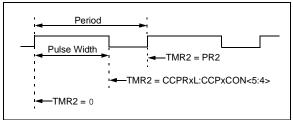

The PWM mode generates a Pulse-Width Modulated signal on the CCP1 pin. The duty cycle, period and resolution are determined by the following registers:

- PR2

- T2CON

- CCPR1L

- CCP1CON

In Pulse-Width Modulation (PWM) mode, the CCP module produces up to a 10-bit resolution PWM output on the CCP1 pin. Since the CCP1 pin is multiplexed with the PORT data latch, the TRIS for that pin must be cleared to enable the CCP1 pin output driver.

| Note: | Clearing   | the | CCP1CON         | register | will |

|-------|------------|-----|-----------------|----------|------|

|       | relinquish | CCP | 1 control of th | ne CCP1  | pin. |

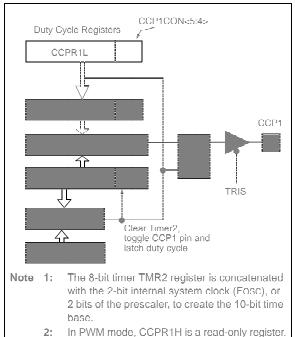

Figure 11-3 shows a simplified block diagram of PWM operation.

Figure 11-4 shows a typical waveform of the PWM signal.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 11.3.7** "Setup for PWM Operation".

FIGURE 11-3: SIMPLIFIED PWM BLOCK DIAGRAM

The PWM output (Figure 11-4) has a time base (period) and a time that the output stays high (duty cycle).

FIGURE 11-4: CCP PWM OUTPUT

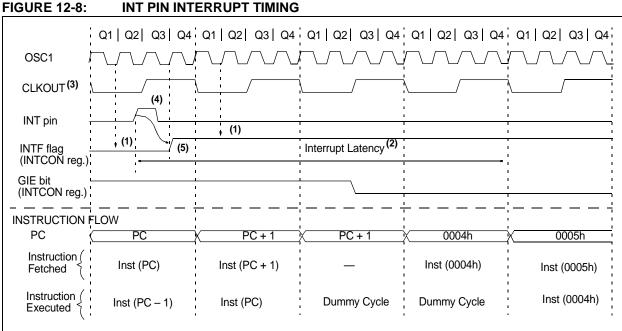

Note 1: INTF flag is sampled here (every Q1).

- 2: Asynchronous interrupt latency = 3-4 TCY. Synchronous latency = 3 TCY, where TCY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is available only in INTOSC and RC Oscillator modes.

- 4: For minimum width of INT pulse, refer to AC specifications in Section 16.0 "Electrical Specifications".

- 5: INTF is enabled to be set any time during the Q4-Q1 cycles.

### TABLE 12-7: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name   | Bit 7 | Bit 6               | Bit 5                 | Bit 4 | Bit 3 | Bit 2 | Bit 1                 | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |  |

|--------|-------|---------------------|-----------------------|-------|-------|-------|-----------------------|--------|----------------------|---------------------------------|--|

| INTCON | GIE   | PEIE                | TOIE                  | INTE  | GPIE  | T0IF  | INTF                  | GPIF   | 0000 0000            | 0000 0000                       |  |

| IOC    |       | _                   | IOC5                  | IOC4  | IOC3  | IOC2  | IOC1                  | IOC0   | 00 0000              | 00 0000                         |  |

| PIR1   | _     | ADIF <sup>(1)</sup> | CCP1IF <sup>(1)</sup> | —     | CMIF  | _     | TMR2IF <sup>(1)</sup> | TMR1IF | -00- 0-00            | -000 0-00                       |  |

| PIE1   | _     | ADIE <sup>(1)</sup> | CCP1IE <sup>(1)</sup> | —     | CMIE  |       | TMR2IE <sup>(1)</sup> | TMR1IE | -00- 0-00            | -000 0-00                       |  |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by the interrupt module.

Note 1: PIC12F615/617/HV615 only.

| Mnem   | onic, | Description                  | Cycles       |       | 14-Bit | Opcode | Status | Nata     |         |  |

|--------|-------|------------------------------|--------------|-------|--------|--------|--------|----------|---------|--|

| Opera  |       | Description                  |              | MSb   |        |        | LSb    | Affected | Notes   |  |

|        |       | BYTE-ORIENTED FILE RE        | GISTER OPE   | RATIO | NS     |        |        |          |         |  |

| ADDWF  | f, d  | Add W and f                  | 1            | 00    | 0111   | dfff   | ffff   | C, DC, Z | 1, 2    |  |

| ANDWF  | f, d  | AND W with f                 | 1            | 00    | 0101   | dfff   | ffff   | Z        | 1, 2    |  |

| CLRF   | f     | Clear f                      | 1            | 00    | 0001   | lfff   | ffff   | Z        | 2       |  |

| CLRW   | -     | Clear W                      | 1            | 00    | 0001   | 0xxx   | xxxx   | Z        |         |  |

| COMF   | f, d  | Complement f                 | 1            | 00    | 1001   | dfff   | ffff   | Z        | 1, 2    |  |

| DECF   | f, d  | Decrement f                  | 1            | 00    | 0011   | dfff   | ffff   | Z        | 1, 2    |  |

| DECFSZ | f, d  | Decrement f, Skip if 0       | 1 <b>(2)</b> | 00    | 1011   | dfff   | ffff   |          | 1, 2, 3 |  |

| INCF   | f, d  | Increment f                  | 1            | 00    | 1010   | dfff   | ffff   | Z        | 1, 2    |  |

| INCFSZ | f, d  | Increment f, Skip if 0       | 1 <b>(2)</b> | 00    | 1111   | dfff   | ffff   |          | 1, 2, 3 |  |

| IORWF  | f, d  | Inclusive OR W with f        | 1            | 00    | 0100   | dfff   | ffff   | Z        | 1, 2    |  |

| MOVF   | f, d  | Move f                       | 1            | 00    | 1000   | dfff   | ffff   | Z        | 1, 2    |  |

| MOVWF  | f     | Move W to f                  | 1            | 00    | 0000   | lfff   | ffff   |          | -       |  |

| NOP    | _     | No Operation                 | 1            | 00    | 0000   | 0xx0   | 0000   |          |         |  |

| RLF    | f, d  | Rotate Left f through Carry  | 1            | 00    | 1101   | dfff   | ffff   | С        | 1, 2    |  |

| RRF    | f, d  | Rotate Right f through Carry | 1            | 00    | 1100   | dfff   | ffff   | С        | 1, 2    |  |

| SUBWF  | f, d  | Subtract W from f            | 1            | 00    | 0010   |        | ffff   | C, DC, Z | 1, 2    |  |

| SWAPF  | f, d  | Swap nibbles in f            | 1            | 00    | 1110   | dfff   | ffff   |          | 1, 2    |  |

| XORWF  | f, d  | Exclusive OR W with f        | 1            | 00    | 0110   | dfff   | ffff   | Z        | 1, 2    |  |

|        |       | BIT-ORIENTED FILE REC        |              |       | IS     |        |        |          |         |  |

| BCF    | f, b  | Bit Clear f                  | 1            | 01    | 00bb   | bfff   | ffff   |          | 1, 2    |  |

| BSF    | f, b  | Bit Set f                    | 1            | 01    |        | bfff   |        |          | 1, 2    |  |

| BTFSC  | f, b  | Bit Test f, Skip if Clear    | 1 (2)        | 01    | 10bb   |        |        |          | 3       |  |

| BTFSS  | f, b  | Bit Test f, Skip if Set      | 1 (2)        | 01    | 11bb   | bfff   | ffff   |          | 3       |  |

|        |       | LITERAL AND CONT             |              | IONS  |        |        |        |          |         |  |

| ADDLW  | k     | Add literal and W            | 1            | 11    | 111x   | kkkk   | kkkk   | C, DC, Z |         |  |

| ANDLW  | k     | AND literal with W           | 1            | 11    | 1001   | kkkk   | kkkk   | Z        |         |  |

| CALL   | k     | Call Subroutine              | 2            | 10    | 0kkk   | kkkk   | kkkk   |          |         |  |

| CLRWDT | _     | Clear Watchdog Timer         | 1            | 00    | 0000   | 0110   | 0100   | TO, PD   |         |  |

| GOTO   | k     | Go to address                | 2            | 10    | 1kkk   | kkkk   | kkkk   |          |         |  |

| IORLW  | k     | Inclusive OR literal with W  | 1            | 11    | 1000   | kkkk   | kkkk   | Z        |         |  |

| MOVLW  | k     | Move literal to W            | 1            | 11    | 00xx   | kkkk   | kkkk   |          |         |  |

| RETFIE | _     | Return from interrupt        | 2            | 00    | 0000   | 0000   | 1001   |          |         |  |

| RETLW  | k     | Return with literal in W     | 2            | 11    | 01xx   | kkkk   | kkkk   |          |         |  |

| RETURN | _     | Return from Subroutine       | 2            | 00    | 0000   | 0000   | 1000   |          |         |  |

| SLEEP  | _     | Go into Standby mode         | 1            | 00    | 0000   | 0110   | 0011   | TO, PD   |         |  |

| SUBLW  | k     | Subtract W from literal      | 1            | 11    | 110x   | kkkk   | kkkk   | C, DC, Z |         |  |

| XORLW  | k     | Exclusive OR literal with W  | 1            | 11    | 1010   | kkkk   | kkkk   | Z        |         |  |

### TABLE 14-2: PIC12F609/615/617/12HV609/615 INSTRUCTION SET

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF GPIO, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

**3:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

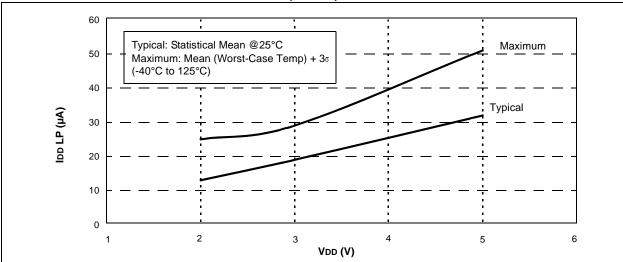

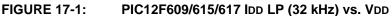

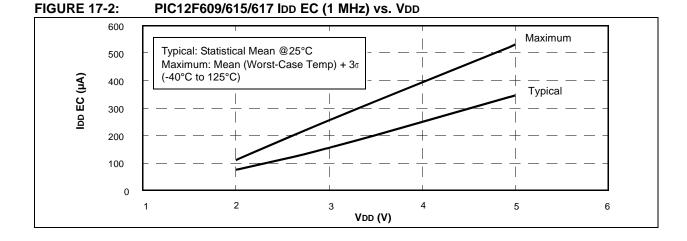

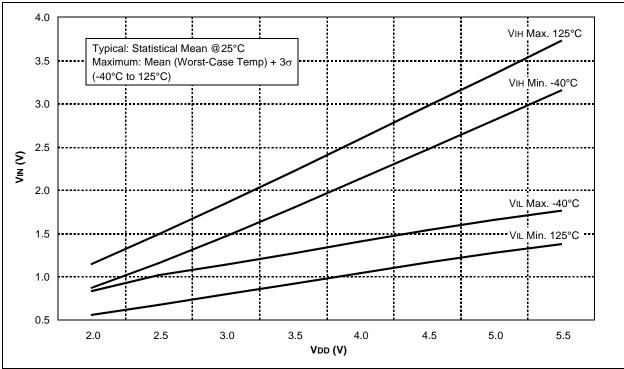

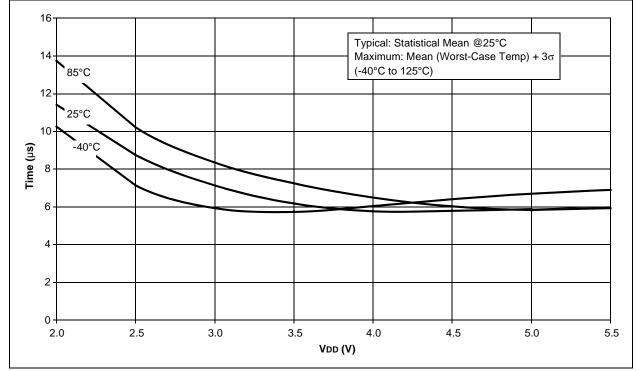

# 17.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where s is a standard deviation, over each temperature range.

NOTES:

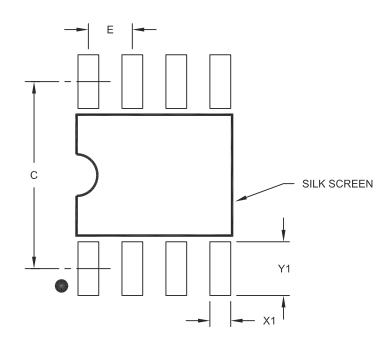

### 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                         | Units | N   | IILLIMETER | S    |

|-------------------------|-------|-----|------------|------|

| Dimension               | MIN   | NOM | MAX        |      |

| Contact Pitch           | E     |     | 1.27 BSC   |      |

| Contact Pad Spacing     | С     |     | 5.40       |      |

| Contact Pad Width (X8)  | X1    |     |            | 0.60 |

| Contact Pad Length (X8) | Y1    |     |            | 1.55 |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A