Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 64 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                    |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-TSSOP, 8-MSOP (0.118", 3.00mm Width)                                     |

| Supplier Device Package    | 8-MSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12hv609t-i-ms |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, PIC<sup>32</sup> logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL00® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# Міскоснір PIC12F609/615/617/12HV609/615

8-Pin Flash-Based, 8-Bit CMOS Microcontrollers

#### High-Performance RISC CPU:

- Only 35 Instructions to Learn:

- All single-cycle instructions except branches

- Operating Speed:

- DC 20 MHz oscillator/clock input

- DC 200 ns instruction cycle

- Interrupt Capability

- 8-Level Deep Hardware Stack

- Direct, Indirect and Relative Addressing modes

#### **Special Microcontroller Features:**

- Precision Internal Oscillator:

- Factory calibrated to ±1%, typical

- Software selectable frequency: 4 MHz or 8 MHz

- Power-Saving Sleep mode

- Voltage Range:

- PIC12F609/615/617: 2.0V to 5.5V

- PIC12HV609/615: 2.0V to user defined maximum (see note)

- Industrial and Extended Temperature Range

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Watchdog Timer (WDT) with independent Oscillator for Reliable Operation

- Multiplexed Master Clear with Pull-up/Input Pin

- Programmable Code Protection

- High Endurance Flash:

- 100,000 write Flash endurance

- Flash retention: > 40 years

- Self Read/ Write Program Memory (PIC12F617 only)

#### Low-Power Features:

- Standby Current:

- 50 nA @ 2.0V, typical

- Operating Current:

- 11 μA @ 32 kHz, 2.0V, typical

- 260 μA @ 4 MHz, 2.0V, typical

- Watchdog Timer Current:

- 1 μA @ 2.0V, typical

- Note: Voltage across the shunt regulator should not exceed 5V.

#### **Peripheral Features:**

- Shunt Voltage Regulator (PIC12HV609/615 only):

- 5 volt regulation

- 4 mA to 50 mA shunt range

- 5 I/O Pins and 1 Input Only

- High Current Source/Sink for Direct LED Drive

- Interrupt-on-pin change or pins

- Individually programmable weak pull-ups

- Analog Comparator module with:

- One analog comparator

- Programmable on-chip voltage reference (CVREF) module (% of VDD)

- Comparator inputs and output externally accessible

- Built-In Hysteresis (software selectable)

- Timer0: 8-Bit Timer/Counter with 8-Bit Programmable Prescaler

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Timer1 Gate (count enable)

- Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator if INTOSC mode selected

- Option to use system clock as Timer1

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

#### PIC12F615/617/HV615 ONLY:

- Enhanced Capture, Compare, PWM module:

- 16-bit Capture, max. resolution 12.5 ns

- Compare, max. resolution 200 ns

- 10-bit PWM with 1 or 2 output channels, 1 output channel programmable "dead time," max. frequency 20 kHz, auto-shutdown

- A/D Converter:

- 10-bit resolution and 4 channels, samples internal voltage references

- Timer2: 8-Bit Timer/Counter with 8-Bit Period Register, Prescaler and Postscaler

## PIC12F609/615/617/12HV609/615

#### **Table of Contents**

| 1.0   | Device Overview                                                                                   | 7   |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------|-----|--|--|--|--|

| 2.0   | Memory Organization                                                                               |     |  |  |  |  |

| 3.0   | Flash Program Memory Self Read/Self Write Control (PIC12F617 only)                                | 27  |  |  |  |  |

| 4.0   | Oscillator Module                                                                                 | 37  |  |  |  |  |

| 5.0   | I/O Port                                                                                          | 43  |  |  |  |  |

| 6.0   | Timer0 Module                                                                                     | 53  |  |  |  |  |

| 7.0   | Timer1 Module with Gate Control                                                                   | 57  |  |  |  |  |

| 8.0   | Timer2 Module (PIC12F615/617/HV615 only)                                                          | 65  |  |  |  |  |

| 9.0   | Comparator Module                                                                                 |     |  |  |  |  |

| 10.0  | Analog-to-Digital Converter (ADC) Module (PIC12F615/617/HV615 only)                               | 79  |  |  |  |  |

| 11.0  | Enhanced Capture/Compare/PWM (With Auto-Shutdown and Dead Band) Module (PIC12F615/617/HV615 only) | 89  |  |  |  |  |

| 12.0  | Special Features of the CPU                                                                       | 107 |  |  |  |  |

| 13.0  | Voltage Regulator                                                                                 | 127 |  |  |  |  |

| 14.0  | Instruction Set Summary                                                                           | 129 |  |  |  |  |

| 15.0  | Development Support                                                                               |     |  |  |  |  |

| 16.0  | Electrical Specifications                                                                         | 143 |  |  |  |  |

| 17.0  | DC and AC Characteristics Graphs and Tables                                                       | 171 |  |  |  |  |

| 18.0  | Packaging Information                                                                             | 195 |  |  |  |  |

|       | ndix A: Data Sheet Revision History                                                               |     |  |  |  |  |

| Appe  | ndix B: Migrating from other PIC <sup>®</sup> Devices                                             | 203 |  |  |  |  |

| Index | <                                                                                                 | 205 |  |  |  |  |

| The N | /icrochip Web Site                                                                                | 209 |  |  |  |  |

| Custo | mer Change Notification Service                                                                   | 209 |  |  |  |  |

| Custo | Customer Support                                                                                  |     |  |  |  |  |

| Read  | Reader Response                                                                                   |     |  |  |  |  |

| Produ | Product Identification System                                                                     |     |  |  |  |  |

| World | lwide Sales and Service                                                                           | 212 |  |  |  |  |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## PIC12F609/615/617/12HV609/615

| Addr   | Name   | Bit 7                                                                       | Bit 6                                                                                          | Bit 5         | Bit 4     | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Page    |  |  |

|--------|--------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------|-----------|---------|--------|--------|--------|----------------------|---------|--|--|

| Bank 0 |        |                                                                             |                                                                                                |               |           |         |        |        |        |                      |         |  |  |

| 00h    | INDF   | Addressing                                                                  | Addressing this location uses contents of FSR to address data memory (not a physical register) |               |           |         |        |        |        |                      |         |  |  |

| 01h    | TMR0   | Timer0 Mod                                                                  | imer0 Module's Register xxxx xxxx 53, 115                                                      |               |           |         |        |        |        |                      |         |  |  |

| 02h    | PCL    | Program Co                                                                  | ounter's (PC)                                                                                  | Least Signifi | cant Byte |         |        |        |        | 0000 0000            | 25, 115 |  |  |

| 03h    | STATUS | IRP <sup>(1)</sup>                                                          | RP1 <sup>(1)</sup>                                                                             | RP0           | TO        | PD      | Z      | DC     | С      | 0001 1xxx            | 18, 115 |  |  |

| 04h    | FSR    | Indirect Dat                                                                | ndirect Data Memory Address Pointer xxxx xxxx 25, 115                                          |               |           |         |        |        |        |                      |         |  |  |

| 05h    | GPIO   | _                                                                           | _                                                                                              | GP5           | GP4       | GP3     | GP2    | GP1    | GP0    | x0 x000              | 43, 115 |  |  |

| 06h    | _      | Unimpleme                                                                   | nimplemented — —                                                                               |               |           |         |        |        |        |                      |         |  |  |

| 07h    | _      | Unimpleme                                                                   | nted                                                                                           |               |           |         |        |        |        | _                    | _       |  |  |

| 08h    | _      | Unimpleme                                                                   | nimplemented — —                                                                               |               |           |         |        |        |        |                      |         |  |  |

| 09h    | _      | Unimpleme                                                                   | nimplemented — —                                                                               |               |           |         |        |        |        |                      |         |  |  |

| 0Ah    | PCLATH | _                                                                           | — — — Write Buffer for upper 5 bits of Program Counter0 0000 25, 115                           |               |           |         |        |        |        |                      |         |  |  |

| 0Bh    | INTCON | GIE                                                                         | PEIE                                                                                           | T0IE          | INTE      | GPIE    | T0IF   | INTF   | GPIF   | 0000 0000            | 20, 115 |  |  |

| 0Ch    | PIR1   | —                                                                           | _                                                                                              | _             | _         | CMIF    | -      | _      | TMR1IF | 00 22                | :, 115  |  |  |

| 0Dh    | _      | Unimplemented                                                               |                                                                                                |               |           |         |        |        |        |                      | —       |  |  |

| 0Eh    | TMR1L  | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                                                                                                |               |           |         |        |        |        |                      | 57, 115 |  |  |

| 0Fh    | TMR1H  | Holding Reg                                                                 | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register xxxx>               |               |           |         |        |        |        |                      | 57, 115 |  |  |

| 10h    | T1CON  | T1GINV                                                                      | TMR1GE                                                                                         | T1CKPS1       | T1CKPS0   | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 0000 0000            | 62, 115 |  |  |

| 11h    | _      | Unimpleme                                                                   | nted                                                                                           |               |           |         |        |        |        | _                    | _       |  |  |

| 12h    | _      | Unimpleme                                                                   | nted                                                                                           |               |           |         |        |        |        | _                    | _       |  |  |

| 13h    | _      | Unimpleme                                                                   | nted                                                                                           |               |           |         |        |        |        | _                    | _       |  |  |

| 14h    | _      | Unimpleme                                                                   | nted                                                                                           |               |           |         |        |        |        | _                    | _       |  |  |

| 15h    | _      | Unimpleme                                                                   | nted                                                                                           |               |           |         |        |        |        | _                    | _       |  |  |

| 16h    | —      | Unimpleme                                                                   | nted                                                                                           |               |           |         |        |        |        | -                    | _       |  |  |

| 17h    | _      | Unimpleme                                                                   | nted                                                                                           |               |           |         |        |        |        | _                    | _       |  |  |

| 18h    | _      | Unimpleme                                                                   | nted                                                                                           |               |           |         |        |        |        | _                    | _       |  |  |

| 19h    | VRCON  | CMVREN                                                                      | —                                                                                              | VRR           | FVREN     | VR3     | VR2    | VR1    | VR0    | 0-00 0000            | 76, 116 |  |  |

| 1Ah    | CMCON0 | CMON                                                                        | COUT                                                                                           | CMOE          | CMPOL     | _       | CMR    | _      | CMCH   | 0000 -0-0            | 72, 116 |  |  |

| 1Bh    | _      |                                                                             |                                                                                                |               |           | _       |        | —      |        | _                    |         |  |  |

| 1Ch    | CMCON1 | _                                                                           | —                                                                                              | _             | T1ACS     | CMHYS   | _      | T1GSS  | CMSYNC | 0 0-10 7             | 3, 116  |  |  |

| 1Dh    | —      | Unimpleme                                                                   | nted                                                                                           |               |           |         |        |        |        | _                    | _       |  |  |

| 1Eh    | _      | Unimpleme                                                                   | Unimplemented                                                                                  |               |           |         |        |        |        | _                    | _       |  |  |

| 1Fh    |        | Unimplemented                                                               |                                                                                                |               |           |         |        |        | _      | _                    |         |  |  |

#### **TABLE 2-1:** PIC12F609/HV609 SPECIAL FUNCTION REGISTERS SUMMARY BANK 0

IRP and RP1 bits are reserved, always maintain these bits clear. 1:

2: Read only register.

| Addr   | Name                     | Bit 7                                                                                                      | Bit 6                                                                                                           | Bit 5         | Bit 4    | Bit 3        | Bit 2          | Bit 1      | Bit 0   | Value on<br>POR, BOR | Page        |  |  |

|--------|--------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------|----------|--------------|----------------|------------|---------|----------------------|-------------|--|--|

| Bank 0 |                          |                                                                                                            |                                                                                                                 |               |          |              |                |            |         |                      |             |  |  |

| 00h    | INDF                     | Addressing                                                                                                 | ddressing this location uses contents of FSR to address data memory (not a physical register) xxxx xxxx 25, 116 |               |          |              |                |            |         |                      |             |  |  |

| 01h    | TMR0                     | Timer0 Mod                                                                                                 | imer0 Module's Register xxxx x53, 116                                                                           |               |          |              |                |            |         |                      |             |  |  |

| 02h    | PCL                      | Program Co                                                                                                 | rogram Counter's (PC) Least Significant Byte 0000 0000 25, 11                                                   |               |          |              |                |            |         |                      |             |  |  |

| 03h    | STATUS                   | IRP <sup>(1)</sup>                                                                                         | RP1 <sup>(1)</sup>                                                                                              | RP0           | TO       | PD           | Z              | DC         | С       | 0001 1xxx            | 8, 116      |  |  |

| 04h    | FSR                      | Indirect Data                                                                                              | a Memory Ad                                                                                                     | dress Pointe  | r        |              |                |            |         | XXXX XXXX 2          | 5, 116      |  |  |

| 05h    | GPIO                     | _                                                                                                          | _                                                                                                               | GP5           | GP4      | GP3          | GP2            | GP1        | GP0     | x0 x000 4            | 8, 116      |  |  |

| 06h    | _                        | Unimplemer                                                                                                 | nimplemented — —                                                                                                |               |          |              |                |            |         |                      |             |  |  |

| 07h    | _                        | Unimplemen                                                                                                 | nted                                                                                                            |               |          |              |                |            |         | _                    | _           |  |  |

| 08h    | _                        | Unimplemen                                                                                                 | nted                                                                                                            |               |          |              |                |            |         | _                    | _           |  |  |

| 09h    | _                        | Unimplemen                                                                                                 | nted                                                                                                            |               |          |              |                |            |         | _                    | _           |  |  |

| 0Ah    | PCLATH                   | _                                                                                                          | _                                                                                                               | _             | Write    | Buffer for u | oper 5 bits of | Program Co | unter   | 0 0000 2             | 5, 116      |  |  |

| 0Bh    | INTCON                   | GIE                                                                                                        | PEIE                                                                                                            | T0IE          | INTE     | GPIE         | T0IF           | INTF       | GPIF    | 0000 0000            | 20, 116     |  |  |

| 0Ch    | PIR1                     | _                                                                                                          | ADIF                                                                                                            | CCP1IF        | _        | CMIF         | —              | TMR2IF     | TMR1IF  | -00-0-00 2           | 2, 116      |  |  |

| 0Dh    | _                        | Unimplemented — —                                                                                          |                                                                                                                 |               |          |              |                |            |         |                      |             |  |  |

| 0Eh    | TMR1L                    | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register xxxx xxxx 57, 116              |                                                                                                                 |               |          |              |                |            |         |                      |             |  |  |

| 0Fh    | TMR1H                    | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register                                 |                                                                                                                 |               |          |              |                |            |         | XXXX XXXX 5          | 7, 116      |  |  |

| 10h    | T1CON                    | T1GINV                                                                                                     | TMR1GE                                                                                                          | T1CKPS1       | T1CKPS0  | T1OSCEN      | T1SYNC         | TMR1CS     | TMR1ON  | 0000 0000            | 62, 116     |  |  |

| 11h    | TMR2 <sup>(3)</sup>      | Timer2 Mod                                                                                                 | ule Register                                                                                                    |               |          |              |                |            |         | 0000 0000            | 65, 116     |  |  |

| 12h    | T2CON <sup>(3)</sup>     | _                                                                                                          | TOUTPS3                                                                                                         | TOUTPS2       | TOUTPS1  | TOUTPS0      | TMR2ON         | T2CKPS1    | T2CKPS0 | -000 0000            | 6, 116      |  |  |

| 13h    | CCPR1L <sup>(3)</sup>    | Capture/Cor                                                                                                | mpare/PWM                                                                                                       | Register 1 Lo | ow Byte  |              |                |            |         | XXXX XXXX            | 90, 116     |  |  |

| 14h    | CCPR1H <sup>(3)</sup>    | Capture/Cor                                                                                                | mpare/PWM                                                                                                       | Register 1 H  | igh Byte |              |                |            |         | XXXX XXXX            | 90, 116     |  |  |

| 15h    | CCP1CON <sup>(3)</sup>   | P1M                                                                                                        | _                                                                                                               | DC1B1         | DC1B0    | CCP1M3       | CCP1M2         | CCP1M1     | CCP1M0  | 0-00 0000            | 9, 116      |  |  |

| 16h    | PWM1CON <sup>(3)</sup>   | PRSEN                                                                                                      | PDC6                                                                                                            | PDC5          | PDC4     | PDC3         | PDC2           | PDC1       | PDC0    | 0000 0000            | 105,<br>116 |  |  |

| 17h    | ECCPAS <sup>(3)</sup>    | ECCPASE                                                                                                    | ECCPAS2                                                                                                         | ECCPAS1       | ECCPAS0  | PSSAC1       | PSSAC0         | PSSBD1     | PSSBD0  | 0000 0000            | 102,<br>116 |  |  |

| 18h    | _                        | Unimplemented                                                                                              |                                                                                                                 |               |          |              |                |            |         |                      | —           |  |  |

| 19h    | VRCON                    | CMVREN                                                                                                     | _                                                                                                               | VRR           | FVREN    | VR3          | VR2            | VR1        | VR0     | 0-00 0000            | 6, 116      |  |  |

| 1Ah    | CMCON0                   | CMON                                                                                                       | COUT                                                                                                            | CMOE          | CMPOL    |              | CMR            |            | CMCH    | 0000 -0-0 7          | 2, 116      |  |  |

| 1Bh    | _                        |                                                                                                            |                                                                                                                 |               |          | _            |                | _          |         | —                    | _           |  |  |

| 1Ch    | CMCON1                   | _                                                                                                          | -                                                                                                               | _             | T1ACS    | CMHYS        | _              | T1GSS      | CMSYNC  | 0 0-10 73            | , 116       |  |  |

| 1Dh    | _                        | Unimplemen                                                                                                 | nted                                                                                                            |               |          |              |                |            |         | _                    | _           |  |  |

| 1Eh    | ADRESH <sup>(2, 3)</sup> | Most Significant 8 bits of the left shifted A/D result or 2 bits of right shifted result xxxx xxxx 85, 116 |                                                                                                                 |               |          |              |                |            |         |                      |             |  |  |

| 1Fh    | ADCON0 <sup>(3)</sup>    | ADFM                                                                                                       | VCFG                                                                                                            | —             | CHS2     | CHS1         | CHS0           | GO/DONE    | ADON    | 00-0 0000            | 34, 116     |  |  |

#### TABLE 2-2: PIC12F615/617/HV615 SPECIAL FUNCTION REGISTERS SUMMARY BANK 0

Legend: -= Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note 1:** IRP and RP1 bits are reserved, always maintain these bits clear.

2: Read only register.

3: PIC12F615/617/HV615 only.

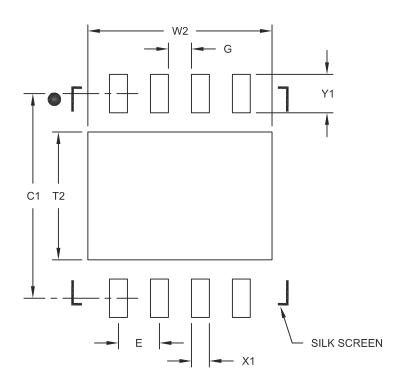

#### 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |      |      |      |  |

|----------------------------|-------------|------|------|------|--|

| Dimensior                  | MIN         | NOM  | MAX  |      |  |

| Contact Pitch              | 0.80 BSC    |      |      |      |  |

| Optional Center Pad Width  | W2          |      |      | 3.60 |  |

| Optional Center Pad Length | T2          |      |      | 2.50 |  |

| Contact Pad Spacing        | C1          |      | 4.00 |      |  |

| Contact Pad Width (X8)     | X1          |      |      | 0.35 |  |

| Contact Pad Length (X8)    | Y1          |      |      | 0.75 |  |

| Distance Between Pads      | G           | 0.45 |      |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2131B