# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

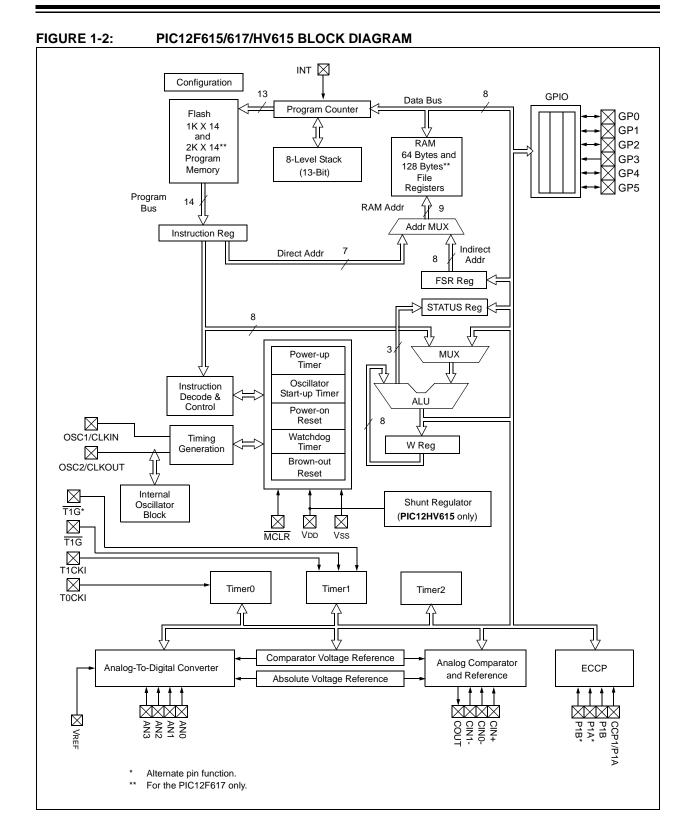

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                   |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-VDFN Exposed Pad                                                        |

| Supplier Device Package    | 8-DFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12hv615-e-md |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                 | Function | Input<br>Type | Output<br>Type | Description                                                    |  |  |

|----------------------|----------|---------------|----------------|----------------------------------------------------------------|--|--|

| GP0/CIN+/ICSPDAT     | GP0      | TTL           | CMOS           | General purpose I/O with prog. pull-up and interrupt-on-change |  |  |

|                      | CIN+     | AN            | —              | Comparator non-inverting input                                 |  |  |

|                      | ICSPDAT  | ST            | CMOS           | Serial Programming Data I/O                                    |  |  |

| GP1/CIN0-/ICSPCLK    | GP1      | TTL           | CMOS           | General purpose I/O with prog. pull-up and interrupt-on-change |  |  |

|                      | CIN0-    | AN            | —              | Comparator inverting input                                     |  |  |

|                      | ICSPCLK  | ST            | _              | Serial Programming Clock                                       |  |  |

| GP2/T0CKI/INT/COUT   | GP2      | ST            | CMOS           | General purpose I/O with prog. pull-up and interrupt-on-change |  |  |

|                      | TOCKI    | ST            | —              | Timer0 clock input                                             |  |  |

|                      | INT      | ST            | _              | External Interrupt                                             |  |  |

|                      | COUT     | —             | CMOS           | Comparator output                                              |  |  |

| GP3/MCLR/Vpp         | GP3      | TTL           | _              | General purpose input with interrupt-on-change                 |  |  |

|                      | MCLR     | ST            | _              | Master Clear w/internal pull-up                                |  |  |

|                      | Vpp      | ΗV            | —              | Programming voltage                                            |  |  |

| GP4/CIN1-/T1G/OSC2/  | GP4      | TTL           | CMOS           | General purpose I/O with prog. pull-up and interrupt-on-change |  |  |

| CLKOUT               | CIN1-    | AN            | —              | Comparator inverting input                                     |  |  |

|                      | T1G      | ST            | _              | Timer1 gate (count enable)                                     |  |  |

|                      | OSC2     | _             | XTAL           | Crystal/Resonator                                              |  |  |

|                      | CLKOUT   | _             | CMOS           | Fosc/4 output                                                  |  |  |

| GP5/T1CKI/OSC1/CLKIN | GP5      | TTL           | CMOS           | General purpose I/O with prog. pull-up and interrupt-on-change |  |  |

|                      | T1CKI    | ST            | _              | Timer1 clock input                                             |  |  |

|                      | OSC1     | XTAL          | _              | Crystal/Resonator                                              |  |  |

|                      | CLKIN    | ST            | —              | External clock input/RC oscillator connection                  |  |  |

| Vdd                  | Vdd      | Power         | _              | Positive supply                                                |  |  |

| Vss                  | Vss      | Power         | _              | Ground reference                                               |  |  |

#### PIC12F609/HV609 PINOUT DESCRIPTION **TABLE 1-1:**

**Legend:** AN=Analog input or output ST=Schmitt Trigger input with CMOS levels TTL = TTL compatible input

CMOS = CMOS compatible input or output HV= High Voltage XTAL=Crystal

## 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, GPIO change and external GP2/INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | GPIE  | T0IF  | INTF  | GPIF  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | GIE: Global Interrupt Enable bit<br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts                                                                                        |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                      |

| bit 5 | <b>TolE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                    |

| bit 4 | INTE: GP2/INT External Interrupt Enable bit<br>1 = Enables the GP2/INT external interrupt<br>0 = Disables the GP2/INT external interrupt                                                      |

| bit 3 | <b>GPIE:</b> GPIO Change Interrupt Enable bit <sup>(1)</sup><br>1 = Enables the GPIO change interrupt<br>0 = Disables the GPIO change interrupt                                               |

| bit 2 | <b>T0IF:</b> Timer0 Overflow Interrupt Flag bit <sup>(2)</sup><br>1 = Timer0 register has overflowed (must be cleared in software)<br>0 = Timer0 register did not overflow                    |

| bit 1 | INTF: GP2/INT External Interrupt Flag bit<br>1 = The GP2/INT external interrupt occurred (must be cleared in software)<br>0 = The GP2/INT external interrupt did not occur                    |

| bit 0 | <b>GPIF:</b> GPIO Change Interrupt Flag bit<br>1 = When at least one of the GPIO <5:0> pins changed state (must be cleared in software)<br>0 = None of the GPIO <5:0> pins have changed state |

**Note 1:** IOC register must also be enabled.

2: T0IF bit is set when TMR0 rolls over. TMR0 is unchanged on Reset and should be initialized before clearing T0IF bit.

### 2.2.2.4 PIE1 Register

The PIE1 register contains the Peripheral Interrupt Enable bits, as shown in Register 2-4.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

#### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| U-0   | R/W-0               | R/W-0                 | U-0 | R/W-0 | U-0 | R/W-0                 | R/W-0  |

|-------|---------------------|-----------------------|-----|-------|-----|-----------------------|--------|

| —     | ADIE <sup>(1)</sup> | CCP1IE <sup>(1)</sup> | _   | CMIE  | —   | TMR2IE <sup>(1)</sup> | TMR1IE |

| bit 7 |                     |                       |     |       |     |                       | bit 0  |

| Legend:                            |                                                                                                                           |                                               |                               |                    |  |  |  |  |  |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------|--------------------|--|--|--|--|--|

| R = Reada                          | able bit                                                                                                                  | W = Writable bit                              | U = Unimplemented bit,        | read as '0'        |  |  |  |  |  |

| -n = Value at POR '1' = Bit is set |                                                                                                                           |                                               | '0' = Bit is cleared          | x = Bit is unknown |  |  |  |  |  |

|                                    |                                                                                                                           |                                               |                               |                    |  |  |  |  |  |

| bit 7                              | -                                                                                                                         | Unimplemented: Read as '0'                    |                               |                    |  |  |  |  |  |

| bit 6                              | ADIE: A                                                                                                                   | D Converter (ADC) Interrupt                   | Enable bit <sup>(1)</sup>     |                    |  |  |  |  |  |

|                                    |                                                                                                                           | bles the ADC interrupt bles the ADC interrupt |                               |                    |  |  |  |  |  |

| bit 5                              | CCP1IE                                                                                                                    | CCP1 Interrupt Enable bit <sup>(1)</sup>      | )                             |                    |  |  |  |  |  |

|                                    | <ul> <li>1 = Enables the CCP1 interrupt</li> <li>0 = Disables the CCP1 interrupt</li> </ul>                               |                                               |                               |                    |  |  |  |  |  |

| bit 4                              | Unimple                                                                                                                   | Unimplemented: Read as '0'                    |                               |                    |  |  |  |  |  |

| bit 3                              | CMIE: C                                                                                                                   | CMIE: Comparator Interrupt Enable bit         |                               |                    |  |  |  |  |  |

|                                    | <ul> <li>1 = Enables the Comparator interrupt</li> <li>0 = Disables the Comparator interrupt</li> </ul>                   |                                               |                               |                    |  |  |  |  |  |

| bit 2                              | Unimplemented: Read as '0'                                                                                                |                                               |                               |                    |  |  |  |  |  |

| bit 1                              | TMR2IE                                                                                                                    | Timer2 to PR2 Match Interr                    | upt Enable bit <sup>(1)</sup> |                    |  |  |  |  |  |

|                                    | <ul> <li>1 = Enables the Timer2 to PR2 match interrupt</li> <li>0 = Disables the Timer2 to PR2 match interrupt</li> </ul> |                                               |                               |                    |  |  |  |  |  |

| bit 0                              | TMR1IE                                                                                                                    | TMR1IE: Timer1 Overflow Interrupt Enable bit  |                               |                    |  |  |  |  |  |

|                                    | <ul> <li>1 = Enables the Timer1 overflow interrupt</li> <li>0 = Disables the Timer1 overflow interrupt</li> </ul>         |                                               |                               |                    |  |  |  |  |  |

| Note 1:                            | PIC12F615/6                                                                                                               | 617/HV615 only. PIC12F609/                    | HV609 unimplemented, read     | as '0'.            |  |  |  |  |  |

#### 2.2.2.5 PIR1 Register

The PIR1 register contains the Peripheral Interrupt flag bits, as shown in Register 2-5.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| U-0   | R/W-0               | R/W-0                 | U-0 | R/W-0 | U-0 | R/W-0                 | R/W-0  |

|-------|---------------------|-----------------------|-----|-------|-----|-----------------------|--------|

| —     | ADIF <sup>(1)</sup> | CCP1IF <sup>(1)</sup> | _   | CMIF  | —   | TMR2IF <sup>(1)</sup> | TMR1IF |

| bit 7 |                     |                       |     |       |     |                       | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                                                                                           |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ADIF: A/D Interrupt Flag bit <sup>(1)</sup>                                                                                          |

|       | 1 = A/D conversion complete                                                                                                          |

|       | 0 = A/D conversion has not completed or has not been started                                                                         |

| bit 5 | CCP1IF: CCP1 Interrupt Flag bit <sup>(1)</sup>                                                                                       |

|       | Capture mode:                                                                                                                        |

|       | <ul><li>1 = A TMR1 register capture occurred (must be cleared in software)</li><li>0 = No TMR1 register capture occurred</li></ul>   |

|       | <u>Compare mode</u> :<br>1 = A TMR1 register compare match occurred (must be cleared in software)                                    |

|       | 0 = No TMR1 register compare match occurred                                                                                          |

|       | <u>PWM mode</u> :                                                                                                                    |

|       | Unused in this mode                                                                                                                  |

| bit 4 | Unimplemented: Read as '0'                                                                                                           |

| bit 3 | CMIF: Comparator Interrupt Flag bit                                                                                                  |

|       | 1 = Comparator output has changed (must be cleared in software)                                                                      |

|       | 0 = Comparator output has not changed                                                                                                |

| bit 2 | Unimplemented: Read as '0'                                                                                                           |

| bit 1 | TMR2IF: Timer2 to PR2 Match Interrupt Flag bit <sup>(1)</sup>                                                                        |

|       | <ul> <li>1 = Timer2 to PR2 match occurred (must be cleared in software)</li> <li>0 = Timer2 to PR2 match has not occurred</li> </ul> |

| bit 0 | TMR1IF: Timer1 Overflow Interrupt Flag bit                                                                                           |

|       | 1 = Timer1 register overflowed (must be cleared in software)                                                                         |

|       | 0 = Timer1 has not overflowed                                                                                                        |

Note 1: PIC12F615/617/HV615 only. PIC12F609/HV609 unimplemented, read as '0'.

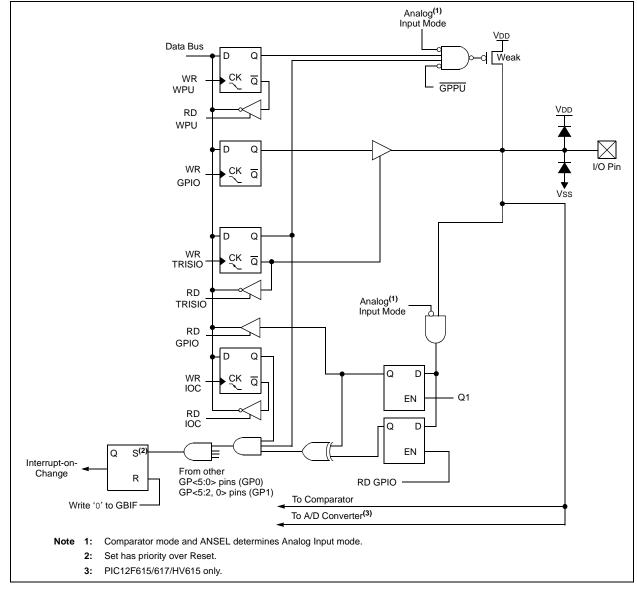

## 5.0 I/O PORT

There are as many as six general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

## 5.1 GPIO and the TRISIO Registers

GPIO is a 6-bit wide port with 5 bidirectional and 1 inputonly pin. The corresponding data direction register is TRISIO (Register 5-2). Setting a TRISIO bit (= 1) will make the corresponding GPIO pin an input (i.e., disable the output driver). Clearing a TRISIO bit (= 0) will make the corresponding GPIO pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is GP3, which is input only and its TRIS bit will always read as '1'. Example 5-1 shows how to initialize GPIO.

| Note: | GPIO = PORTA   |

|-------|----------------|

|       | TRISIO = TRISA |

Reading the GPIO register (Register 5-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch. GP3 reads '0' when MCLRE = 1.

The TRISIO register controls the direction of the GPIO pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISIO register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

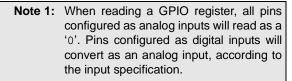

Note: The ANSEL register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0' and cannot generate an interrupt.

#### EXAMPLE 5-1: INITIALIZING GPIO

| BANKSEL | GPIO   | ;                                |

|---------|--------|----------------------------------|

| CLRF    | GPIO   | ;Init GPIO                       |

| BANKSEL | ANSEL  | ;                                |

| CLRF    | ANSEL  | ;digital I/O, ADC clock          |

|         |        | <pre>;setting `don't care'</pre> |

| MOVLW   | 0Ch    | ;Set GP<3:2> as inputs           |

| MOVWF   | TRISIO | ;and set GP<5:4,1:0>             |

|         |        | ;as outputs                      |

#### REGISTER 5-1: GPIO: GPIO REGISTER

| U-0                                                                  | U-0 | R/W-x | R/W-x | R-x | R/W-x | R/W-x | R/W-x |

|----------------------------------------------------------------------|-----|-------|-------|-----|-------|-------|-------|

| _                                                                    | _   | GP5   | GP4   | GP3 | GP2   | GP1   | GP0   |

| bit 7                                                                |     |       |       |     |       |       | bit C |

|                                                                      |     |       |       |     |       |       |       |

| Legend:                                                              |     |       |       |     |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |       |       |     |       |       |       |

| R = Readable bit                                                     |     |       |       |     | ,     |       |       |

| bit 7-6 | Unimplemented: | Read as '0' |

|---------|----------------|-------------|

|---------|----------------|-------------|

bit 5-0 **GP<5:0>**: GPIO I/O Pin bit

1 = GPIO pin is > VIH 0 = GPIO pin is < VIL

## 5.2.4 PIN DESCRIPTIONS AND DIAGRAMS

Each GPIO pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the Comparator or the ADC, refer to the appropriate section in this data sheet.

## 5.2.4.1 GP0/AN0<sup>(1)</sup>/CIN+/P1B<sup>(1)</sup>/ICSPDAT

Figure 5-1 shows the diagram for this pin. The GP0 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

- an analog non-inverting input to the comparator

- a PWM output<sup>(1)</sup>

- In-Circuit Serial Programming data

## 5.2.4.2 GP1/AN1<sup>(1)</sup>/CIN0-/VREF<sup>(1)</sup>/ICSPCLK

Figure 5-1 shows the diagram for this pin. The GP1 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

- an analog inverting input to the comparator

- a voltage reference input for the ADC<sup>(1)</sup>

- In-Circuit Serial Programming clock

#### Note 1: PIC12F615/617/HV615 only.

## FIGURE 5-1: BLOCK DIAGRAM OF GP<1:0>

NOTES:

## 7.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- 3-bit prescaler

- Optional LP oscillator

- Synchronous or asynchronous operation

- Timer1 gate (count enable) via comparator or  $\overline{\text{T1G}}$  pin

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function

- Special Event Trigger (with ECCP)

- Comparator output synchronization to Timer1 clock

Figure 7-1 is a block diagram of the Timer1 module.

## 7.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer. When used with an external clock source, the module can be used as either a timer or counter.

## 7.2 Clock Source Selection

The TMR1CS bit of the T1CON register is used to select the clock source. When TMR1CS = 0, the clock source is FOSC/4. When TMR1CS = 1, the clock source is supplied externally.

| Clock Source | TMR1CS | T1ACS |

|--------------|--------|-------|

| Fosc/4       | 0      | 0     |

| Fosc         | 0      | 1     |

| T1CKI pin    | 1      | x     |

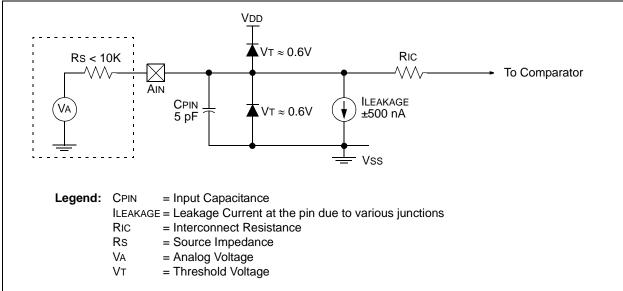

### 9.2 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 9-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

### FIGURE 9-3: ANALOG INPUT MODEL

Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

## 12.3.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, simply connect the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See **Section 16.0** "**Electrical Specifications**" for details. If the BOR is enabled, the maximum rise time specification does not apply. The BOR circuitry will keep the device in Reset until VDD reaches VBOR (see **Section 12.3.4** "**Brown-out Reset (BOR)**").

Note: The POR circuit does not produce an internal Reset when VDD declines. To reenable the POR, VDD must reach Vss for a minimum of 100 μs.

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure proper operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

## 12.3.2 MCLR

PIC12F609/615/617/12HV609/615 has a noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

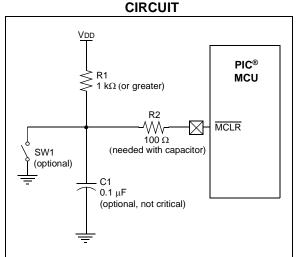

Voltages applied to the MCLR pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 12-2, is suggested.

An internal  $\overline{\text{MCLR}}$  option is enabled by clearing the MCLRE bit in the Configuration Word register. When MCLRE = 0, the Reset signal to the chip is generated internally. When the MCLRE = 1, the GP3/MCLR pin becomes an external Reset input. In this mode, the GP3/MCLR pin has a weak pull-up to VDD.

## FIGURE 12-2: RECOMMENDED MCLR

## 12.3.3 POWER-UP TIMER (PWRT)

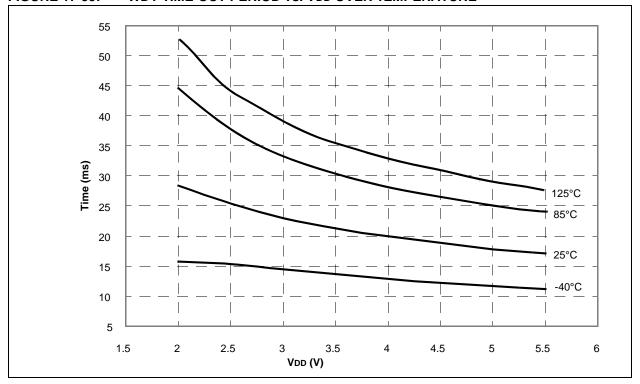

The Power-up Timer provides a fixed 64 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates from an internal RC oscillator. For more information, see **Section 4.4** "**Internal Clock Modes**". The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A Configuration bit, PWRTE, can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should be enabled when Brown-out Reset is enabled, although it is not required.

The Power-up Timer delay will vary from chip-to-chip due to:

- VDD variation

- Temperature variation

- Process variation

See DC parameters for details (Section 16.0 "Electrical Specifications").

| Note: | Voltage spikes below Vss at the MCLR          |

|-------|-----------------------------------------------|

|       | pin, inducing currents greater than 80 mA,    |

|       | may cause latch-up. Thus, a series resis-     |

|       | tor of 50-100 $\Omega$ should be used when    |

|       | applying a "low" level to the MCLR pin,       |

|       | rather than pulling this pin directly to Vss. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                     |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                            |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                                 |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', then a NOP is<br>executed instead, making it a<br>two-cycle instruction. |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                       |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                            |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a two-cycle<br>instruction. |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                             |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                             |  |  |  |  |

| Operation:       | $k \rightarrow PC < 10:0>$<br>PCLATH<4:3> $\rightarrow PC < 12:11>$                                                                                                                              |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                             |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                               |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                       |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |  |  |  |  |

| Status Affected: | Z                                                                                                                         |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the<br>W register. |  |  |  |  |

| INCF             | Increment f                                                                                                                                                                |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                          |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |

## 16.0 ELECTRICAL SPECIFICATIONS

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                | 40° to +125°C             |

|---------------------------------------------------------------------------------------------------------------|---------------------------|

| Storage temperature                                                                                           | 65°C to +150°C            |

| Voltage on VDD with respect to Vss                                                                            | -0.3V to +6.5V            |

| Voltage on MCLR with respect to Vss                                                                           | -0.3V to +13.5V           |

| Voltage on all other pins with respect to Vss                                                                 | 0.3V to (VDD + 0.3V)      |

| Total power dissipation <sup>(1)</sup>                                                                        |                           |

| Maximum current out of Vss pin                                                                                | 95 mA                     |

| Maximum current into Vod pin                                                                                  | 95 mA                     |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                  | ± 20 mA                   |

| Output clamp current, Iок (Vo < 0 or Vo >VDD)                                                                 | ± 20 mA                   |

| Maximum output current sunk by any I/O pin                                                                    | 25 mA                     |

| Maximum output current sourced by any I/O pin                                                                 | 25 mA                     |

| Maximum current sunk by GPIO                                                                                  | 90 mA                     |

| Maximum current sourced GPIO                                                                                  | 90 mA                     |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $-\sum$ IOH} + $\sum$ {(VD IOL). | ⊡ – Vон) х Iон} + ∑(Vol х |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

### 16.2 DC Characteristics: PIC12F609/615/617-I (Industrial) PIC12F609/615/617-E (Extended)

| DC CHA                       | ARACTERISTICS                          | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |       |       |       |            |                                     |

|------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------------|-------------------------------------|

| Param Device Characteristics |                                        | Min                                                                                                                                                                                     | Тур†  | Max   | Units | Conditions |                                     |

| No.                          | Device Characteristics                 |                                                                                                                                                                                         | וקעי  | IVIAN | Units | Vdd        | Note                                |

| D010                         | Supply Current (IDD) <sup>(1, 2)</sup> |                                                                                                                                                                                         | 13    | 25    | μA    | 2.0        | Fosc = 32 kHz                       |

|                              | PIC12F609/615/617                      |                                                                                                                                                                                         | 19    | 29    | μA    | 3.0        | LP Oscillator mode                  |

|                              |                                        |                                                                                                                                                                                         | 32    | 51    | μA    | 5.0        |                                     |

| D011*                        |                                        |                                                                                                                                                                                         | 135   | 225   | μA    | 2.0        | Fosc = 1 MHz                        |

|                              |                                        |                                                                                                                                                                                         | 185   | 285   | μA    | 3.0        | XT Oscillator mode                  |

|                              |                                        | _                                                                                                                                                                                       | 300   | 405   | μA    | 5.0        |                                     |

| D012                         |                                        | —                                                                                                                                                                                       | 240   | 360   | μA    | 2.0        | Fosc = 4 MHz                        |

|                              |                                        |                                                                                                                                                                                         | 360   | 505   | μA    | 3.0        | XT Oscillator mode                  |

|                              |                                        |                                                                                                                                                                                         | 0.66  | 1.0   | mA    | 5.0        |                                     |

| D013*                        |                                        |                                                                                                                                                                                         | 75    | 110   | μA    | 2.0        | Fosc = 1 MHz                        |

|                              |                                        |                                                                                                                                                                                         | 155   | 255   | μA    | 3.0        | EC Oscillator mode                  |

|                              |                                        |                                                                                                                                                                                         | 345   | 530   | μA    | 5.0        |                                     |

| D014                         |                                        |                                                                                                                                                                                         | 185   | 255   | μA    | 2.0        | Fosc = 4 MHz                        |

|                              |                                        |                                                                                                                                                                                         | 325   | 475   | μA    | 3.0        | EC Oscillator mode                  |

|                              |                                        |                                                                                                                                                                                         | 0.665 | 1.0   | mA    | 5.0        |                                     |

| D016*                        |                                        |                                                                                                                                                                                         | 245   | 340   | μA    | 2.0        | Fosc = 4 MHz                        |

|                              |                                        |                                                                                                                                                                                         | 360   | 485   | μA    | 3.0        | INTOSC mode                         |

|                              |                                        |                                                                                                                                                                                         | 0.620 | 0.845 | mA    | 5.0        |                                     |

| D017                         |                                        |                                                                                                                                                                                         | 395   | 550   | μA    | 2.0        | Fosc = 8 MHz                        |

|                              |                                        |                                                                                                                                                                                         | 0.620 | 0.850 | mA    | 3.0        | INTOSC mode                         |

|                              |                                        |                                                                                                                                                                                         | 1.2   | 1.6   | mA    | 5.0        |                                     |

| D018                         |                                        |                                                                                                                                                                                         | 175   | 235   | μA    | 2.0        | Fosc = 4 MHz                        |

|                              |                                        |                                                                                                                                                                                         | 285   | 390   | μA    | 3.0        | EXTRC mode <sup>(3)</sup>           |

|                              |                                        | —                                                                                                                                                                                       | 530   | 750   | μA    | 5.0        |                                     |

| D019                         |                                        | _                                                                                                                                                                                       | 2.2   | 3.1   | mA    | 4.5        | Fosc = 20 MHz<br>HS Oscillator mode |

|                              |                                        |                                                                                                                                                                                         | 2.8   | 3.35  | mA    | 5.0        |                                     |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-torail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in KOhms (KΩ).

### 16.5 DC Characteristics: PIC12F609/615/617 - E (Extended)

| DC CHARACTERISTICS           |                              | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |     |       |            |                                               |  |

|------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|------------|-----------------------------------------------|--|

| Param Device Characteristics |                              | Min                                                                                                                               | Turt |     | Unite | Conditions |                                               |  |

| No.                          | Device Characteristics       | WIIN                                                                                                                              | Тур† | Max | Units | Vdd        | Note                                          |  |

| D020E                        | Power-down Base              | _                                                                                                                                 | 0.05 | 4.0 | μΑ    | 2.0        | WDT, BOR, Comparator, VREF and                |  |

|                              | Current (IPD) <sup>(2)</sup> | —                                                                                                                                 | 0.15 | 5.0 | μΑ    | 3.0        | T1OSC disabled                                |  |

|                              | PIC12F609/615/617            | _                                                                                                                                 | 0.35 | 8.5 | μΑ    | 5.0        |                                               |  |

| D021E                        |                              | —                                                                                                                                 | 0.5  | 5.0 | μΑ    | 2.0        | WDT Current <sup>(1)</sup>                    |  |

|                              |                              | —                                                                                                                                 | 2.5  | 8.0 | μΑ    | 3.0        |                                               |  |

|                              |                              | _                                                                                                                                 | 9.5  | 19  | μΑ    | 5.0        |                                               |  |

| D022E                        |                              | _                                                                                                                                 | 5.0  | 15  | μΑ    | 3.0        | BOR Current <sup>(1)</sup>                    |  |

|                              |                              | —                                                                                                                                 | 6.0  | 19  | μΑ    | 5.0        |                                               |  |

| D023E                        |                              | _                                                                                                                                 | 50   | 70  | μΑ    | 2.0        | Comparator Current <sup>(1)</sup> , single    |  |

|                              |                              | —                                                                                                                                 | 55   | 75  | μΑ    | 3.0        | comparator enabled                            |  |

|                              |                              | —                                                                                                                                 | 60   | 80  | μΑ    | 5.0        |                                               |  |

| D024E                        |                              | _                                                                                                                                 | 30   | 40  | μΑ    | 2.0        | CVREF Current <sup>(1)</sup> (high range)     |  |

|                              |                              | —                                                                                                                                 | 45   | 60  | μΑ    | 3.0        |                                               |  |

|                              |                              | —                                                                                                                                 | 75   | 105 | μΑ    | 5.0        |                                               |  |

| D025E*                       |                              | —                                                                                                                                 | 39   | 50  | μΑ    | 2.0        | CVREF Current <sup>(1)</sup> (low range)      |  |

|                              |                              | —                                                                                                                                 | 59   | 80  | μΑ    | 3.0        |                                               |  |

|                              |                              | —                                                                                                                                 | 98   | 130 | μΑ    | 5.0        |                                               |  |

| D026E                        |                              | _                                                                                                                                 | 5.5  | 16  | μΑ    | 2.0        | T1OSC Current <sup>(1)</sup> , 32.768 kHz     |  |

|                              |                              | _                                                                                                                                 | 7.0  | 18  | μΑ    | 3.0        |                                               |  |

|                              |                              | _                                                                                                                                 | 8.5  | 22  | μΑ    | 5.0        |                                               |  |

| D027E                        |                              | —                                                                                                                                 | 0.2  | 6.5 | μA    | 3.0        | A/D Current <sup>(1)</sup> , no conversion in |  |

|                              |                              | _                                                                                                                                 | 0.36 | 10  | μΑ    | 5.0        | progress                                      |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral  $\Delta$  current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

\*

## TABLE 16-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET PARAMETERS

|              | r <b>d Opera</b><br>ng Tempe | ting Conditions (unless otherwi<br>erature -40°C ≤ TA ≤ +125°C | se state | ed)      |          |          |                                                       |

|--------------|------------------------------|----------------------------------------------------------------|----------|----------|----------|----------|-------------------------------------------------------|

| Param<br>No. | Sym                          | Characteristic                                                 | Min      | Тур†     | Max      | Units    | Conditions                                            |

| 30           | ТмсL                         | MCLR Pulse Width (low)                                         | 2<br>5   | _        |          | μs<br>μs | VDD = 5V, -40°C to +85°C<br>VDD = 5V, -40°C to +125°C |

| 31*          | Twdt                         | Watchdog Timer Time-out<br>Period (No Prescaler)               | 10<br>10 | 20<br>20 | 30<br>35 | ms<br>ms | VDD = 5V, -40°C to +85°C<br>VDD = 5V, -40°C to +125°C |

| 32           | Тоѕт                         | Oscillation Start-up Timer<br>Period <sup>(1, 2)</sup>         |          | 1024     | —        | Tosc     | (NOTE 3)                                              |

| 33*          | TPWRT                        | Power-up Timer Period                                          | 40       | 65       | 140      | ms       |                                                       |

| 34*          | Tioz                         | I/O High-impedance from<br>MCLR Low or Watchdog Timer<br>Reset | —        | _        | 2.0      | μs       |                                                       |

| 35           | VBOR                         | Brown-out Reset Voltage                                        | 2.0      | 2.15     | 2.3      | V        | (NOTE 4)                                              |

| 36*          | VHYST                        | Brown-out Reset Hysteresis                                     |          | 100      | —        | mV       |                                                       |

| 37*          | TBOR                         | Brown-out Reset Minimum<br>Detection Period                    | 100      | —        | _        | μS       | $VDD \leq VBOR$                                       |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: By design.

- **3:** Period of the slower clock.

- 4: To ensure these voltage tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

## TABLE 16-11: PIC12F615/617/HV615 A/D CONVERTER (ADC) CHARACTERISTICS:

| Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                      |            |      |          |       |                                                                     |

|--------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------|------------|------|----------|-------|---------------------------------------------------------------------|

| Param<br>No.                                                                                                             | Sym  | Characteristic                                       | Min        | Тур† | Max      | Units | Conditions                                                          |

| AD01                                                                                                                     | Nr   | Resolution                                           | _          | _    | 10 bits  | bit   |                                                                     |

| AD02                                                                                                                     | EIL  | Integral Error                                       | —          | _    | ±1       | LSb   | VREF = 5.12V <sup>(5)</sup>                                         |

| AD03                                                                                                                     | Edl  | Differential Error                                   | _          | —    | ±1       | LSb   | No missing codes to 10 bits<br>VREF = 5.12V <sup>(5)</sup>          |

| AD04                                                                                                                     | EOFF | Offset Error                                         |            | +1.5 | +2.0     | LSb   | Vref = 5.12V <sup>(5)</sup>                                         |

| AD07                                                                                                                     | Egn  | Gain Error                                           |            | _    | ±1       | LSb   | VREF = 5.12V <sup>(5)</sup>                                         |

| AD06<br>AD06A                                                                                                            | Vref | Reference Voltage <sup>(3)</sup>                     | 2.2<br>2.5 | _    | —<br>Vdd | V     | Absolute minimum to ensure 1 LSb<br>accuracy                        |

| AD07                                                                                                                     | VAIN | Full-Scale Range                                     | Vss        | _    | VREF     | V     |                                                                     |

| AD08                                                                                                                     | ZAIN | Recommended<br>Impedance of Analog<br>Voltage Source | —          | _    | 10       | kΩ    |                                                                     |

| AD09*                                                                                                                    | IREF | VREF Input Current <sup>(3)</sup>                    | 10         | —    | 1000     | μΑ    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN. |

|                                                                                                                          |      |                                                      |            |      | 50       | μA    | During A/D conversion cycle.                                        |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error includes integral, differential, offset and gain errors.

- 2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

- **3:** ADC VREF is from external VREF or VDD pin, whichever is selected as reference input.

- 4: When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

**5:** VREF = 5V for PIC12HV615.

## 16.12 High Temperature Operation

This section outlines the specifications for the <u>PIC12F615</u> device operating in a temperature range <u>between -40°C and 150°C</u>.<sup>(4)</sup> The specifications between -40°C and 150°C<sup>(4)</sup> are identical to those shown in DS41288 and DS80329.

| Note 1:                                                                                                                                                                        | Writes are <u>not allowed</u> for Flash<br>Program Memory above 125°C.                                                                                                                                                                                        |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2:                                                                                                                                                                             | All AC timing specifications are increased<br>by 30%. This derating factor will include<br>parameters such as TPWRT.                                                                                                                                          |  |  |  |

| 3:                                                                                                                                                                             | The temperature range indicator in the part number is "H" for -40°C to 150°C. <sup>(4)</sup>                                                                                                                                                                  |  |  |  |

| Example: PIC12F615T-H/ST indicates the device is shipped in a TAPE and reel configuration, in the MSOP package, and is rated for operation from -40°C to 150°C. <sup>(4)</sup> |                                                                                                                                                                                                                                                               |  |  |  |

| 4:                                                                                                                                                                             | AEC-Q100 reliability testing for devices<br>intended to operate at 150°C is 1,000<br>hours. Any design in which the total oper-<br>ating time from 125°C to 150°C will be<br>greater than 1,000 hours is not warranted<br>without prior written approval from |  |  |  |

Microchip Technology Inc.

| Parameter                    | Source/Sink | Value | Units |

|------------------------------|-------------|-------|-------|

| Max. Current: VDD            | Source      | 20    | mA    |

| Max. Current: Vss            | Sink        | 50    | mA    |

| Max. Current: PIN            | Source      | 5     | mA    |

| Max. Current: PIN            | Sink        | 10    | mA    |

| Pin Current: at VOH          | Source      | 3     | mA    |

| Pin Current: at VoL          | Sink        | 8.5   | mA    |

| Port Current: GPIO           | Source      | 20    | mA    |

| Port Current: GPIO           | Sink        | 50    | mA    |

| Maximum Junction Temperature |             | 155   | °C    |

#### TABLE 16-13: ABSOLUTE MAXIMUM RATINGS

**Note:** Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

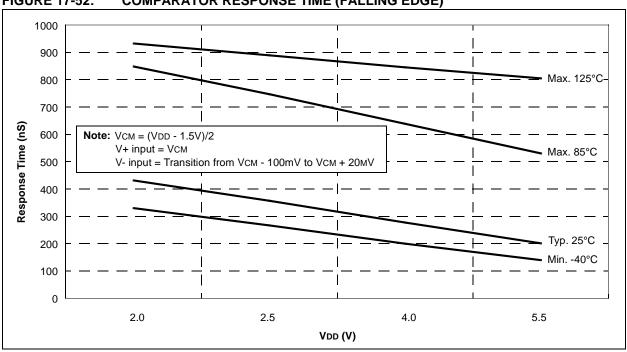

FIGURE 17-52: COMPARATOR RESPONSE TIME (FALLING EDGE)

| RLF                                      | 136      |

|------------------------------------------|----------|

| RRF                                      | 136      |

| SLEEP                                    |          |

| SUBLW                                    | 136      |

| SUBWF                                    |          |

| SWAPF                                    |          |

| XORLW                                    |          |

| XORWF                                    |          |

| Summary Table                            |          |

| INTCON Register                          |          |

| Internal Oscillator Block                |          |

| INTOSC                                   |          |

| Specifications                           | 157. 158 |

| Internal Sampling Switch (Rss) Impedance |          |

| Internet Address                         |          |

| Interrupts                               |          |

| ADC                                      |          |

| Associated Registers                     |          |

| Context Saving                           |          |

| GP2/INT                                  |          |

| GPIO Interrupt-on-Change                 |          |

| Interrupt-on-Change                      |          |

| Timer0                                   |          |

| TMR1                                     |          |

|                                          |          |

| INTOSC Specifications                    |          |

| IOC Register                             |          |

|                                          |          |

## L

| Load Conditions155 |

|--------------------|

|--------------------|

## Μ

| MCLR 111                                              |

|-------------------------------------------------------|