Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                   |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-VDFN Exposed Pad                                                        |

| Supplier Device Package    | 8-DFN (3x3)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12hv615-e-mf |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

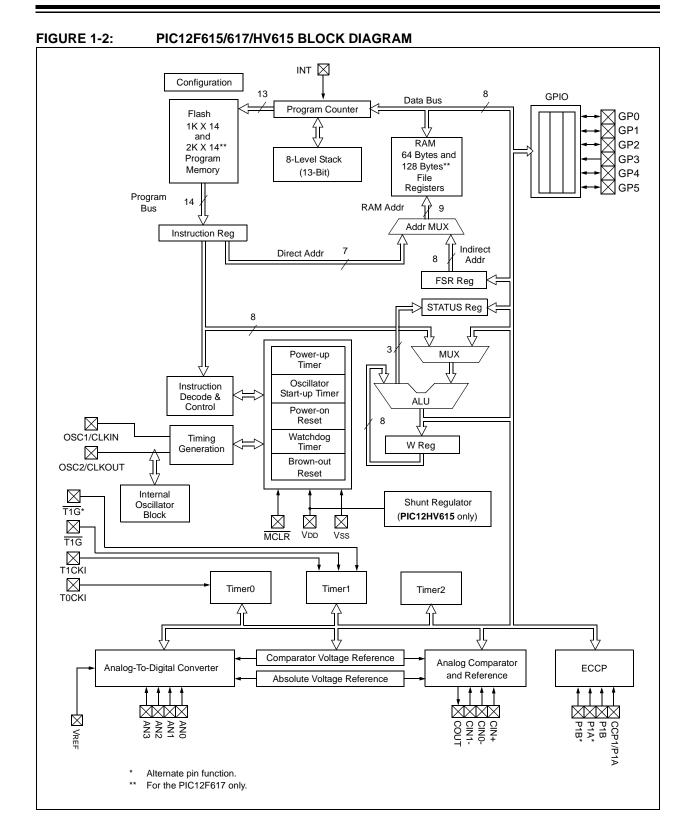

| Device     | Program<br>Memory | Data Memory  | Self Read/ | 1/0       | 10-bit A/D | Comparators | ECCP | Timers   | Voltago Bango     |

|------------|-------------------|--------------|------------|-----------|------------|-------------|------|----------|-------------------|

| Device     | Flash<br>(words)  | SRAM (bytes) | Self Write | elf Write |            | Comparators | ECCP | 8/16-bit | Voltage Range     |

| PIC12F609  | 1024              | 64           | —          | 5         | 0          | 1           | _    | 1/1      | 2.0V-5.5V         |

| PIC12HV609 | 1024              | 64           | —          | 5         | 0          | 1           |      | 1/1      | 2.0V-user defined |

| PIC12F615  | 1024              | 64           | —          | 5         | 4          | 1           | YES  | 2/1      | 2.0V-5.5V         |

| PIC12HV615 | 1024              | 64           | —          | 5         | 4          | 1           | YES  | 2/1      | 2.0V-user defined |

| PIC12F617  | 2048              | 128          | YES        | 5         | 4          | 1           | YES  | 2/1      | 2.0V-5.5V         |

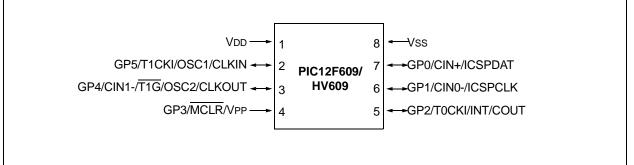

### 8-Pin Diagram, PIC12F609/HV609 (PDIP, SOIC, MSOP, DFN)

### TABLE 1: PIC12F609/HV609 PIN SUMMARY (PDIP, SOIC, MSOP, DFN)

| I/O                | Pin | Comparators | Timer | Interrupts | Pull-ups | Basic       |

|--------------------|-----|-------------|-------|------------|----------|-------------|

| GP0                | 7   | CIN+        | _     | IOC        | Y        | ICSPDAT     |

| GP1                | 6   | CIN0-       | —     | IOC        | Y        | ICSPCLK     |

| GP2                | 5   | COUT        | TOCKI | INT/IOC    | Y        | —           |

| GP3 <sup>(1)</sup> | 4   | _           |       | IOC        | Y(2)     | MCLR/VPP    |

| GP4                | 3   | CIN1-       | T1G   | IOC        | Y        | OSC2/CLKOUT |

| GP5                | 2   | —           | T1CKI | IOC        | Y        | OSC1/CLKIN  |

| _                  | 1   | -           |       | _          |          | Vdd         |

|                    | 8   | _           | _     | _          | _        | Vss         |

Note 1: Input only.

2: Only when pin is configured for external MCLR.

#### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

REGISTER 2-1:

the bank select bits for data memory (RAM)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

STATUS: STATUS REGISTER

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, see the Section 14.0 "Instruction Set Summary".

- Note 1: Bits IRP and RP1 of the STATUS register are not used by the PIC12F609/615/617/ 12HV609/615 and should be maintained as clear. Use of these bits is not recommended, since this may affect upward compatibility with future products.

- 2: The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| Reserved | Reserved | R/W-0 | R-1 | R-1 | R/W-x | R/W-x | R/W-x |

|----------|----------|-------|-----|-----|-------|-------|-------|

| IRP      | RP1      | RP0   | TO  | PD  | Z     | DC    | С     |

| bit 7    |          |       |     |     |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | IRP: This bit is reserved and should be maintained as '0'                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | RP1: This bit is reserved and should be maintained as '0'                                                                                                               |

| bit 5   | RP0: Register Bank Select bit (used for direct addressing)                                                                                                              |

|         | 1 = Bank 1 (80h – FFh)<br>0 = Bank 0 (00h – 7Fh)                                                                                                                        |

| bit 4   | TO: Time-out bit                                                                                                                                                        |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                                              |

| bit 3   | PD: Power-down bit                                                                                                                                                      |

|         | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                                                  |

| bit 2   | Z: Zero bit                                                                                                                                                             |

|         | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                  |

| bit 1   | DC: Digit Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions), For Borrow, the polarity is reversed.                                                             |

|         | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul>                |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions)                                                                                            |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the                                                                   |

Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the Note 1: second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the Peripheral Interrupt Enable bits, as shown in Register 2-4.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

#### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| U-0   | R/W-0               | R/W-0                 | U-0 | R/W-0 | U-0 | R/W-0                 | R/W-0  |

|-------|---------------------|-----------------------|-----|-------|-----|-----------------------|--------|

| —     | ADIE <sup>(1)</sup> | CCP1IE <sup>(1)</sup> | _   | CMIE  | —   | TMR2IE <sup>(1)</sup> | TMR1IE |

| bit 7 |                     |                       |     |       |     |                       | bit 0  |

| Legend:    |                                                                                                                           |                                                                 |                               |                    |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------|--------------------|--|--|--|

| R = Reada  | able bit                                                                                                                  | W = Writable bit                                                | U = Unimplemented bit,        | read as '0'        |  |  |  |

| -n = Value | at POR                                                                                                                    | '1' = Bit is set                                                | '0' = Bit is cleared          | x = Bit is unknown |  |  |  |

|            |                                                                                                                           |                                                                 |                               |                    |  |  |  |

| bit 7      | -                                                                                                                         | emented: Read as '0'                                            |                               |                    |  |  |  |

| bit 6      | ADIE: A                                                                                                                   | D Converter (ADC) Interrupt                                     | Enable bit <sup>(1)</sup>     |                    |  |  |  |

|            | <ul> <li>1 = Enables the ADC interrupt</li> <li>0 = Disables the ADC interrupt</li> </ul>                                 |                                                                 |                               |                    |  |  |  |

| bit 5      | CCP1IE                                                                                                                    | CCP1 Interrupt Enable bit <sup>(1)</sup>                        | )                             |                    |  |  |  |

|            |                                                                                                                           | bles the CCP1 interrupt<br>bles the CCP1 interrupt              |                               |                    |  |  |  |

| bit 4      | Unimple                                                                                                                   | Unimplemented: Read as '0'                                      |                               |                    |  |  |  |

| bit 3      | CMIE: C                                                                                                                   | CMIE: Comparator Interrupt Enable bit                           |                               |                    |  |  |  |

|            |                                                                                                                           | bles the Comparator interrupt<br>bles the Comparator interrup   |                               |                    |  |  |  |

| bit 2      | Unimple                                                                                                                   | mented: Read as '0'                                             |                               |                    |  |  |  |

| bit 1      | TMR2IE                                                                                                                    | Timer2 to PR2 Match Interr                                      | upt Enable bit <sup>(1)</sup> |                    |  |  |  |

|            | <ul> <li>1 = Enables the Timer2 to PR2 match interrupt</li> <li>0 = Disables the Timer2 to PR2 match interrupt</li> </ul> |                                                                 |                               |                    |  |  |  |

| bit 0      | TMR1IE                                                                                                                    | Timer1 Overflow Interrupt E                                     | nable bit                     |                    |  |  |  |

|            |                                                                                                                           | bles the Timer1 overflow inter<br>bles the Timer1 overflow inte | •                             |                    |  |  |  |

| Note 1:    | PIC12F615/6                                                                                                               | 617/HV615 only. PIC12F609/                                      | HV609 unimplemented, read     | as '0'.            |  |  |  |

NOTES:

| U-0   | U-0 | U-0 | U-0 | R/W-1 | U-0 | R/W-1 | R/W-1 |

|-------|-----|-----|-----|-------|-----|-------|-------|

| —     | —   | —   | —   | ANS3  | —   | ANS1  | ANS0  |

| bit 7 |     |     |     |       |     |       | bit 0 |

|       |     |     |     |       |     |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                                                                             |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | ANS3: Analog Select Between Analog or Digital Function on Pin GP4<br>1 = Analog input. Pin is assigned as analog input <sup>(1)</sup> .<br>0 = Digital I/O. Pin is assigned to port or special function.                               |

| bit 2   | Unimplemented: Read as '0'                                                                                                                                                                                                             |

| bit 1   | <ul> <li>ANS1: Analog Select Between Analog or Digital Function on Pin GP1</li> <li>1 = Analog input. Pin is assigned as analog input.<sup>(1)</sup></li> <li>0 = Digital I/O. Pin is assigned to port or special function.</li> </ul> |

| bit 0   | <ul> <li>ANS0: Analog Select Between Analog or Digital Function on Pin GP0</li> <li>0 = Digital I/O. Pin is assigned to port or special function.</li> <li>1 = Analog input. Pin is assigned as analog input.<sup>(1)</sup></li> </ul> |

**Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-onchange if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### REGISTER 5-4: ANSEL: ANALOG SELECT REGISTER (PIC12F615/617/HV615)

| U-0   | R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| —     | ADCS2 | ADCS1 | ADCS0 | ANS3  | ANS2  | ANS1  | ANS0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | <b>Unimplemented</b> : Read as '0'                                                                                                                                                                                                                                  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | ADCS<2:0>: A/D Conversion Clock Select bits<br>000 = Fosc/2<br>001 = Fosc/8<br>010 = Fosc/32                                                                                                                                                                        |

|         | x11 = FRC (clock derived from a dedicated internal oscillator = 500 kHz max)<br>100 = Fosc/4<br>101 = Fosc/16<br>110 = Fosc/64                                                                                                                                      |

| bit 3-0 | <b>ANS&lt;3:0&gt;</b> : Analog Select Between Analog or Digital Function on Pins GP4, GP2, GP1, GP0, respectively.<br>1 = Analog input. Pin is assigned as analog input <sup>(1)</sup> .<br>0 = Digital I/O. Pin is assigned to port or special function.           |

| Note 1: | Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-on-<br>change if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of<br>the voltage on the pin. |

NOTES:

| U-0         | R/W-0                  | R/W-0                                          | R/W-0          | R/W-0             | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |

|-------------|------------------------|------------------------------------------------|----------------|-------------------|-----------------|-----------------|---------|--|--|--|--|

| _           | TOUTPS3                | TOUTPS2                                        | TOUTPS1        | TOUTPS0           | TMR2ON          | T2CKPS1         | T2CKPS0 |  |  |  |  |

| oit 7       |                        |                                                |                |                   |                 |                 | bit     |  |  |  |  |

|             |                        |                                                |                |                   |                 |                 |         |  |  |  |  |

| Legend:     |                        |                                                |                |                   |                 |                 |         |  |  |  |  |

| R = Readab  |                        | W = Writable                                   |                | -                 | nented bit, rea | d as '0'        |         |  |  |  |  |

| n = Value a | It POR                 | '1' = Bit is set                               |                | '0' = Bit is clea | ared            | x = Bit is unki | nown    |  |  |  |  |

|             |                        |                                                |                |                   |                 |                 |         |  |  |  |  |

| oit 7       | Unimplemen             | ted: Read as '                                 | 0'             |                   |                 |                 |         |  |  |  |  |

| oit 6-3     | TOUTPS<3:0             | )>: Timer2 Output                              | out Postscaler | Select bits       |                 |                 |         |  |  |  |  |

|             | 0000 =1:1 Po           |                                                |                |                   |                 |                 |         |  |  |  |  |

|             |                        | 0001 =1:2 Postscaler                           |                |                   |                 |                 |         |  |  |  |  |

|             |                        | 010 =1:3 Postscaler                            |                |                   |                 |                 |         |  |  |  |  |

|             |                        | 0011 =1:4 Postscaler                           |                |                   |                 |                 |         |  |  |  |  |

|             |                        | 0100 =1:5 Postscaler<br>0101 =1:6 Postscaler   |                |                   |                 |                 |         |  |  |  |  |

|             |                        | 0101 = 1.6 Postscaler                          |                |                   |                 |                 |         |  |  |  |  |

|             | 0111 =1:8 Pc           |                                                |                |                   |                 |                 |         |  |  |  |  |

|             | 1000 <b>=1:9</b> Po    | 1000 =1:9 Postscaler                           |                |                   |                 |                 |         |  |  |  |  |

|             | 1001 =1:10 F           | 1001 =1:10 Postscaler                          |                |                   |                 |                 |         |  |  |  |  |

|             | 1010 =1:11 Postscaler  |                                                |                |                   |                 |                 |         |  |  |  |  |

|             | 1011 =1:12 Postscaler  |                                                |                |                   |                 |                 |         |  |  |  |  |

|             | 1100 =1:13 Postscaler  |                                                |                |                   |                 |                 |         |  |  |  |  |

|             |                        | 1101 =1:14 Postscaler<br>1110 =1:15 Postscaler |                |                   |                 |                 |         |  |  |  |  |

|             | 1110 = 1:16 Postscaler |                                                |                |                   |                 |                 |         |  |  |  |  |

| oit 2       |                        |                                                |                |                   |                 |                 |         |  |  |  |  |

| 511 2       |                        | TMR2ON: Timer2 On bit<br>1 = Timer2 is on      |                |                   |                 |                 |         |  |  |  |  |

|             | 0 = Timer2 is          |                                                |                |                   |                 |                 |         |  |  |  |  |

| oit 1-0     | T2CKPS<1:0             | T2CKPS<1:0>: Timer2 Clock Prescale Select bits |                |                   |                 |                 |         |  |  |  |  |

|             | 00 =Prescale           | eris 1                                         |                |                   |                 |                 |         |  |  |  |  |

|             | 01 =Prescale           |                                                |                |                   |                 |                 |         |  |  |  |  |

|             | 1x =Prescale           | ric 16                                         |                |                   |                 |                 |         |  |  |  |  |

#### **REGISTER 8-1: T2CON: TIMER 2 CONTROL REGISTER**

#### **TABLE 8-1:** SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2

| Name                 | Bit 7                                                            | Bit 6               | Bit 5                 | Bit 4   | Bit 3   | Bit 2  | Bit 1                 | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|----------------------|------------------------------------------------------------------|---------------------|-----------------------|---------|---------|--------|-----------------------|-----------|----------------------|---------------------------------|

| INTCON               | GIE                                                              | PEIE                | TOIE                  | INTE    | GPIE    | T0IF   | INTF                  | GPIF      | 0000 0000            | 0000 0000                       |

| PIE1                 | _                                                                | ADIE <sup>(1)</sup> | CCP1IE <sup>(1)</sup> | _       | CMIE    | _      | TMR2IE <sup>(1)</sup> | TMR1IE    | -00- 0-00            | -00-0-00                        |

| PIR1                 | —                                                                | ADIF <sup>(1)</sup> | CCP1IF <sup>(1)</sup> | _       | CMIF    | _      | TMR2IF <sup>(1)</sup> | TMR1IF    | -00- 0-00            | -00-0-00                        |

| PR2 <sup>(1)</sup>   | Timer2 Module Period Register                                    |                     |                       |         |         |        |                       | 1111 1111 | 1111 1111            |                                 |

| TMR2 <sup>(1)</sup>  | Holding Register for the 8-bit TMR2 Register 0000 0000 0000 0000 |                     |                       |         |         |        | 0000 0000             |           |                      |                                 |

| T2CON <sup>(1)</sup> | —                                                                | TOUTPS3             | TOUTPS2               | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1               | T2CKPS0   | -000 0000            | -000 0000                       |

|                      |                                                                  |                     |                       |         |         |        |                       |           |                      |                                 |

Legend:x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.Note1:For PIC12F615/617/HV615 only.

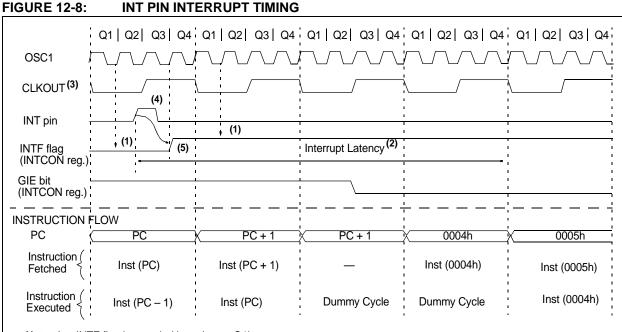

Note 1: INTF flag is sampled here (every Q1).

- 2: Asynchronous interrupt latency = 3-4 TCY. Synchronous latency = 3 TCY, where TCY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is available only in INTOSC and RC Oscillator modes.

- 4: For minimum width of INT pulse, refer to AC specifications in Section 16.0 "Electrical Specifications".

- 5: INTF is enabled to be set any time during the Q4-Q1 cycles.

#### TABLE 12-7: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name   | Bit 7 | Bit 6               | Bit 5                 | Bit 4 | Bit 3 | Bit 2 | Bit 1                 | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|---------------------|-----------------------|-------|-------|-------|-----------------------|--------|----------------------|---------------------------------|

| INTCON | GIE   | PEIE                | TOIE                  | INTE  | GPIE  | T0IF  | INTF                  | GPIF   | 0000 0000            | 0000 0000                       |

| IOC    |       | _                   | IOC5                  | IOC4  | IOC3  | IOC2  | IOC1                  | IOC0   | 00 0000              | 00 0000                         |

| PIR1   | _     | ADIF <sup>(1)</sup> | CCP1IF <sup>(1)</sup> | —     | CMIF  | _     | TMR2IF <sup>(1)</sup> | TMR1IF | -00- 0-00            | -000 0-00                       |

| PIE1   | _     | ADIE <sup>(1)</sup> | CCP1IE <sup>(1)</sup> | —     | CMIE  |       | TMR2IE <sup>(1)</sup> | TMR1IE | -00- 0-00            | -000 0-00                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by the interrupt module.

Note 1: PIC12F615/617/HV615 only.

NOTES:

### 14.0 INSTRUCTION SET SUMMARY

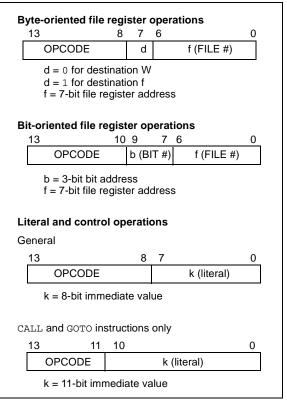

The PIC12F609/615/617/12HV609/615 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 14-1, while the various opcode fields are summarized in Table 14-1.

Table 14-2 lists the instructions recognized by the  $MPASM^{TM}$  assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8-bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

#### 14.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (RMW) operation. The register is read, the data is modified, and the result is stored according to either the instruction or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF GPIO instruction will read GPIO, clear all the data bits, then write the result back to GPIO. This example would have the unintended consequence of clearing the condition that set the GPIF flag.

#### TABLE 14-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                             |

| PC    | Program Counter                                                                                                                                                                 |

| TO    | Time-out bit                                                                                                                                                                    |

| С     | Carry bit                                                                                                                                                                       |

| DC    | Digit carry bit                                                                                                                                                                 |

| Z     | Zero bit                                                                                                                                                                        |

| PD    | Power-down bit                                                                                                                                                                  |

#### FIGURE 14-1: GENERAL FORMAT FOR INSTRUCTIONS

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                               |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>two-cycle instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                                                      |

| Operands:        | None                                                                                                                                                                                |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{WDT} \\ 0 \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}} \\ 1 \rightarrow \overline{\text{PD}} \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                                              |

| Description:     | CLRWDT instruction resets the<br>Watchdog Timer. It also resets<br>the prescaler of the WDT.<br>Status bits TO and PD are set.                                                      |

| CALL             | Call Subroutine                                                                                                                                                                                                                               |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                          |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0>, \\ (PCLATH < 4:3>) \rightarrow PC < 12:11> \end{array}$                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                          |

| Description:     | Call Subroutine. First, return<br>address (PC + 1) is pushed onto<br>the stack. The eleven-bit<br>immediate address is loaded into<br>PC bits <10:0>. The upper bits of<br>the PC are loaded from PCLATH.<br>CALL is a two-cycle instruction. |

| COMF             | Complement f                                                                                                                                                   |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] COMF f,d                                                                                                                                               |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                    |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                     |  |  |  |

| Status Affected: | Z                                                                                                                                                              |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in W. If 'd' is '1',<br>the result is stored back in<br>register 'f'. |  |  |  |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [ label ] CLRF f                                                      |

| Operands:        | $0 \leq f \leq 127$                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are<br>cleared and the Z bit is set.     |

| CLRW             | Clear W                                                                                    |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                                               |

| Operands:        | None                                                                                       |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow \text{(W)} \\ 1 \rightarrow \text{Z} \end{array}$ |

| Status Affected: | Z                                                                                          |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                |

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                   |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

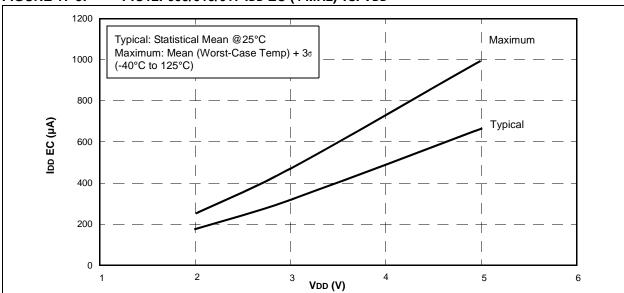

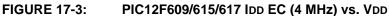

#### **16.9** Thermal Considerations

| Param<br>No. | Sym       | Characteristic             | Тур    | Units                   | Conditions                                                                                          |

|--------------|-----------|----------------------------|--------|-------------------------|-----------------------------------------------------------------------------------------------------|

| TH01         | θJA       | Thermal Resistance         | 84.6*  | C/W                     | 8-pin PDIP package                                                                                  |

|              |           | Junction to Ambient        | 149.5* | C/W                     | 8-pin SOIC package                                                                                  |

|              |           |                            | 211*   | C/W                     | 8-pin MSOP package                                                                                  |

|              |           |                            | 60*    | C/W                     | 8-pin DFN 3x3mm package                                                                             |

|              |           |                            | 44*    | C/W                     | 8-pin DFN 4x4mm package                                                                             |

| TH02         | θJC       | Thermal Resistance         | 41.2*  | C/W                     | 8-pin PDIP package                                                                                  |

|              |           | Junction to Case           | 39.9*  | C/W                     | 8-pin SOIC package                                                                                  |

|              |           |                            | 39*    | C/W                     | 8-pin MSOP package                                                                                  |

|              |           |                            | 9*     | C/W                     | 8-pin DFN 3x3mm package                                                                             |

|              |           | 3.0*                       | C/W    | 8-pin DFN 4x4mm package |                                                                                                     |

| TH03         | TDIE      | Die Temperature            | 150*   | С                       |                                                                                                     |

| TH04         | PD        | Power Dissipation          | —      | W                       | PD = PINTERNAL + PI/O                                                                               |

| TH05         | PINTERNAL | Internal Power Dissipation | —      | W                       | PINTERNAL = IDD x VDD<br>(NOTE 1)                                                                   |

| TH06         | Pi/o      | I/O Power Dissipation      | —      | W                       | $\begin{array}{l} PI/O = \Sigma \ (IOL \ ^* \ VOL) + \Sigma \ (IOH \ ^* \ (VDD - VOH)) \end{array}$ |

| TH07         | Pder      | Derated Power              | —      | W                       | Pder = PDmax (Tdie - Ta)/θja<br>(NOTE 2)                                                            |

\* These parameters are characterized but not tested.

**Note 1:** IDD is current to run the chip alone without driving any load on the output pins.

**2:**  $T_A$  = Ambient temperature.

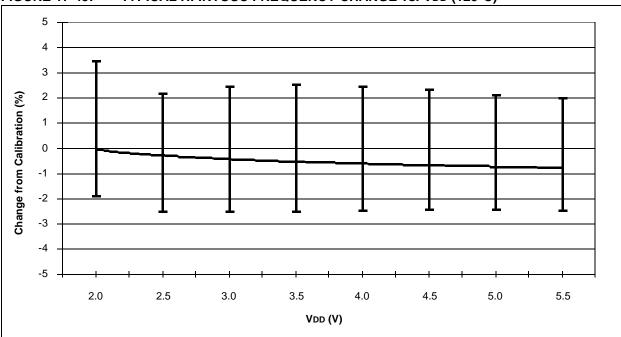

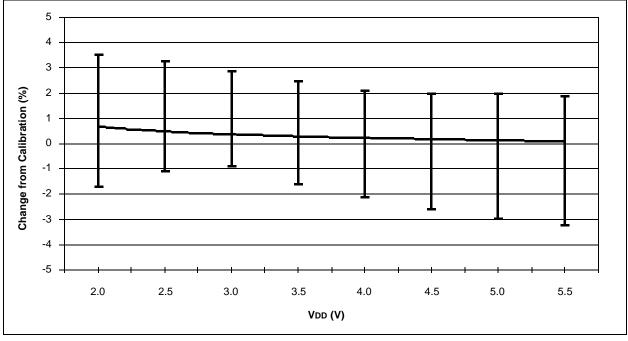

#### FIGURE 17-45: TYPICAL HFINTOSC FREQUENCY CHANGE vs. VDD (125°C)

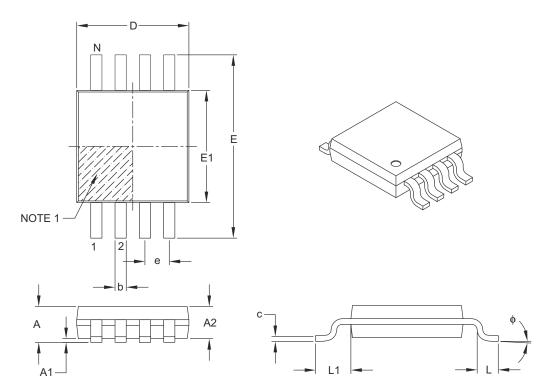

#### 8-Lead Plastic Micro Small Outline Package (MS) [MSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          |      | MILLIMETERS |  |  |  |

|--------------------------|------------------|----------|------|-------------|--|--|--|

|                          | Dimension Limits |          | NOM  | MAX         |  |  |  |

| Number of Pins           | N                | 8        |      |             |  |  |  |

| Pitch                    | е                | 0.65 BSC |      |             |  |  |  |

| Overall Height           | A                | -        | -    | 1.10        |  |  |  |

| Molded Package Thickness | A2               | 0.75     | 0.85 | 0.95        |  |  |  |

| Standoff                 | A1               | 0.00     | -    | 0.15        |  |  |  |

| Overall Width            | E                | 4.90 BSC |      |             |  |  |  |

| Molded Package Width     | E1               | 3.00 BSC |      |             |  |  |  |

| Overall Length           | D                | 3.00 BSC |      |             |  |  |  |

| Foot Length              | L                | 0.40     | 0.60 | 0.80        |  |  |  |

| Footprint                | L1               | 0.95 REF |      |             |  |  |  |

| Foot Angle               | φ                | 0°       | -    | 8°          |  |  |  |

| Lead Thickness           | С                | 0.08     | -    | 0.23        |  |  |  |

| Lead Width               | b                | 0.22     | -    | 0.40        |  |  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-111B

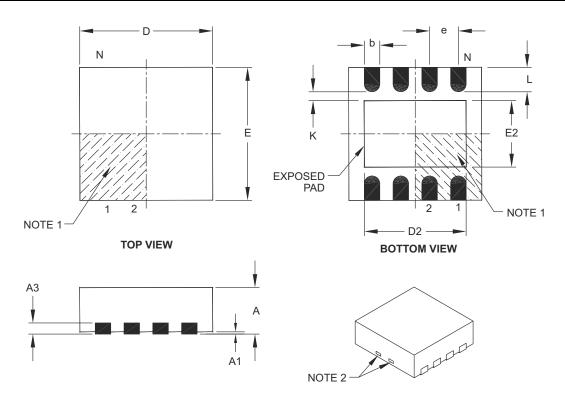

#### 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |                |          |      |  |

|------------------------|-------------|----------------|----------|------|--|

| Dimensio               | n Limits    | MIN            | NOM      | MAX  |  |

| Number of Pins         | Ν           | 8              |          |      |  |

| Pitch                  | е           |                | 0.80 BSC |      |  |

| Overall Height         | А           | 0.80           | 0.90     | 1.00 |  |

| Standoff               | A1          | 0.00           | 0.02     | 0.05 |  |

| Contact Thickness      | A3          | 0.20 REF       |          |      |  |

| Overall Length         | D           | 4.00 BSC       |          |      |  |

| Exposed Pad Width      | E2          | 0.00 2.20 2.80 |          |      |  |

| Overall Width          | E           | 4.00 BSC       |          |      |  |

| Exposed Pad Length     | D2          | 0.00           | 3.00     | 3.60 |  |

| Contact Width          | b           | 0.25           | 0.30     | 0.35 |  |

| Contact Length         | L           | 0.30           | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad | K           | 0.20           | -        | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-131D

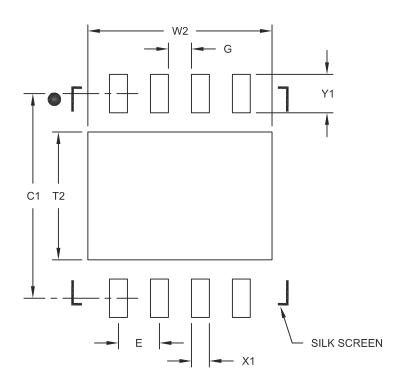

#### 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |      |      |      |

|----------------------------|-------------|------|------|------|

| Dimension Limits           |             | MIN  | NOM  | MAX  |

| Contact Pitch              | E           |      |      |      |

| Optional Center Pad Width  | W2          |      |      | 3.60 |

| Optional Center Pad Length | T2          |      |      | 2.50 |

| Contact Pad Spacing        | C1          |      | 4.00 |      |

| Contact Pad Width (X8)     | X1          |      |      | 0.35 |

| Contact Pad Length (X8)    | Y1          |      |      | 0.75 |

| Distance Between Pads      | G           | 0.45 |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2131B

### WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

**Santa Clara** Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-6578-300 Fax: 886-3-6578-370

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

01/05/10