Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                   |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

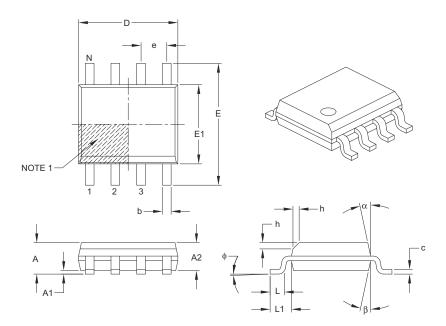

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-TSSOP, 8-MSOP (0.118", 3.00mm Width)                                    |

| Supplier Device Package    | 8-MSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12hv615-i-ms |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

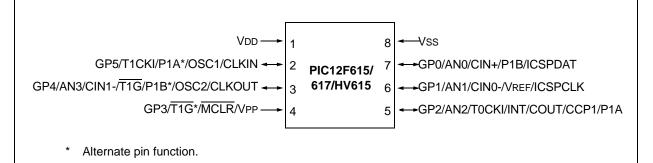

# 8-Pin Diagram, PIC12F615/617/HV615 (PDIP, SOIC, MSOP, DFN)

## TABLE 2: PIC12F615/617/HV615 PIN SUMMARY (PDIP, SOIC, MSOP, DFN)

| I/O                | Pin | Analog | Comparator<br>s | Timer | ССР      | Interrupts | Pull-ups | Basic        |

|--------------------|-----|--------|-----------------|-------|----------|------------|----------|--------------|

| GP0                | 7   | AN0    | CIN+            | _     | P1B      | IOC        | Y        | ICSPDAT      |

| GP1                | 6   | AN1    | CIN0-           | —     | —        | IOC        | Y        | ICSPCLK/VREF |

| GP2                | 5   | AN2    | COUT            | T0CKI | CCP1/P1A | INT/IOC    | Y        | —            |

| GP3 <sup>(1)</sup> | 4   |        | —               | T1G*  | _        | IOC        | Y(2)     | MCLR/Vpp     |

| GP4                | 3   | AN3    | CIN1-           | T1G   | P1B*     | IOC        | Y        | OSC2/CLKOUT  |

| GP5                | 2   | -      | —               | T1CKI | P1A*     | IOC        | Y        | OSC1/CLKIN   |

| —                  | 1   | —      | —               | —     | —        | —          | —        | Vdd          |

| —                  | 8   |        | —               | _     | _        | _          | —        | Vss          |

|                    |     |        |                 |       |          |            |          |              |

\* Alternate pin function.

Note 1: Input only.

2: Only when pin is configured for external MCLR.

| Name                 | Function | Input<br>Type | Output<br>Type | Description                                                    |

|----------------------|----------|---------------|----------------|----------------------------------------------------------------|

| GP0/CIN+/ICSPDAT     | GP0      | TTL           | CMOS           | General purpose I/O with prog. pull-up and interrupt-on-change |

|                      | CIN+     | AN            | —              | Comparator non-inverting input                                 |

|                      | ICSPDAT  | ST            | CMOS           | Serial Programming Data I/O                                    |

| GP1/CIN0-/ICSPCLK    | GP1      | TTL           | CMOS           | General purpose I/O with prog. pull-up and interrupt-on-change |

|                      | CIN0-    | AN            | —              | Comparator inverting input                                     |

|                      | ICSPCLK  | ST            | _              | Serial Programming Clock                                       |

| GP2/T0CKI/INT/COUT   | GP2      | ST            | CMOS           | General purpose I/O with prog. pull-up and interrupt-on-change |

|                      | TOCKI    | ST            | —              | Timer0 clock input                                             |

|                      | INT      | ST            | _              | External Interrupt                                             |

|                      | COUT     | —             | CMOS           | Comparator output                                              |

| GP3/MCLR/Vpp         | GP3      | TTL           | _              | General purpose input with interrupt-on-change                 |

|                      | MCLR     | ST            | _              | Master Clear w/internal pull-up                                |

|                      | Vpp      | ΗV            | —              | Programming voltage                                            |

| GP4/CIN1-/T1G/OSC2/  | GP4      | TTL           | CMOS           | General purpose I/O with prog. pull-up and interrupt-on-change |

| CLKOUT               | CIN1-    | AN            | —              | Comparator inverting input                                     |

|                      | T1G      | ST            | _              | Timer1 gate (count enable)                                     |

|                      | OSC2     | _             | XTAL           | Crystal/Resonator                                              |

|                      | CLKOUT   | _             | CMOS           | Fosc/4 output                                                  |

| GP5/T1CKI/OSC1/CLKIN | GP5      | TTL           | CMOS           | General purpose I/O with prog. pull-up and interrupt-on-change |

|                      | T1CKI    | ST            | _              | Timer1 clock input                                             |

|                      | OSC1     | XTAL          | _              | Crystal/Resonator                                              |

|                      | CLKIN    | ST            | —              | External clock input/RC oscillator connection                  |

| Vdd                  | Vdd      | Power         | _              | Positive supply                                                |

| Vss                  | Vss      | Power         | _              | Ground reference                                               |

#### PIC12F609/HV609 PINOUT DESCRIPTION **TABLE 1-1:**

**Legend:** AN=Analog input or output ST=Schmitt Trigger input with CMOS levels TTL = TTL compatible input

CMOS = CMOS compatible input or output HV= High Voltage XTAL=Crystal

| Addr   | Name                     | Bit 7              | Bit 6                                                                                         | Bit 5            | Bit 4          | Bit 3                  | Bit 2           | Bit 1       | Bit 0               | Value on<br>POR, BOR | Page    |

|--------|--------------------------|--------------------|-----------------------------------------------------------------------------------------------|------------------|----------------|------------------------|-----------------|-------------|---------------------|----------------------|---------|

| Bank 1 |                          |                    |                                                                                               |                  |                |                        |                 |             |                     |                      |         |

| 80h    | INDF                     | Addressing         | ddressing this location uses contents of FSR to address data memory (not a physical register) |                  |                |                        |                 |             | gister)             | xxxx xxxx            | 25, 116 |

| 81h    | OPTION_REG               | GPPU               | INTEDG                                                                                        | TOCS             | T0SE           | PSA                    | PS2             | PS1         | PS0                 | 1111 1111            | 19, 116 |

| 82h    | PCL                      | Program Co         | ounter's (PC)                                                                                 | Least Signifi    | icant Byte     |                        |                 |             |                     | 0000 0000            | 25, 116 |

| 83h    | STATUS                   | IRP <sup>(1)</sup> | RP1 <sup>(1)</sup>                                                                            | RP0              | TO             | PD                     | Z               | DC          | С                   | 0001 1xxx            | 18, 116 |

| 84h    | FSR                      | Indirect Data      | a Memory Ac                                                                                   | Idress Pointe    | er             |                        |                 |             |                     | xxxx xxxx            | 25, 116 |

| 85h    | TRISIO                   |                    |                                                                                               | TRISIO5          | TRISIO4        | TRISIO3 <sup>(4)</sup> | TRISIO2         | TRISIO1     | TRISIO0             | 11 1111              | 44, 116 |

| 86h    | _                        | Unimplemen         | nted                                                                                          |                  |                |                        |                 |             |                     | _                    | _       |

| 87h    | _                        | Unimplemen         | nted                                                                                          |                  |                |                        |                 |             |                     | _                    | _       |

| 88h    | _                        | Unimplemen         | nted                                                                                          |                  |                |                        |                 |             |                     | _                    | _       |

| 89h    | _                        | Unimplemen         | nted                                                                                          |                  |                |                        |                 |             |                     | —                    | —       |

| 8Ah    | PCLATH                   | _                  | _                                                                                             | _                | Writ           | e Buffer for u         | pper 5 bits of  | Program Cou | unter               | 0 0000               | 25, 116 |

| 8Bh    | INTCON                   | GIE                | PEIE                                                                                          | T0IE             | INTE           | GPIE                   | T0IF            | INTF        | GPIF <sup>(3)</sup> | 0000 0000            | 20, 116 |

| 8Ch    | PIE1                     | _                  | ADIE                                                                                          | CCP1IE           | _              | CMIE                   | _               | TMR2IE      | TMR1IE              | -00- 0-00            | 21, 116 |

| 8Dh    | _                        | Unimplemer         | nted                                                                                          |                  |                |                        |                 |             |                     | —                    | —       |

| 8Eh    | PCON                     | _                  | —                                                                                             | —                | —              | _                      | —               | POR         | BOR                 | dd                   | 23, 116 |

| 8Fh    | _                        | Unimplemen         | nted                                                                                          |                  |                |                        |                 |             |                     | _                    | _       |

| 90h    | OSCTUNE                  | _                  | _                                                                                             | _                | TUN4           | TUN3                   | TUN2            | TUN1        | TUN0                | 0 0000               | 41, 116 |

| 91h    | _                        | Unimplemen         | nted                                                                                          |                  |                |                        |                 |             |                     | _                    | _       |

| 92h    | PR2                      | Timer2 Mod         | ule Period R                                                                                  | egister          |                |                        |                 |             |                     | 1111 1111            | 65, 116 |

| 93h    | APFCON                   | _                  | _                                                                                             | _                | T1GSEL         | _                      | _               | P1BSEL      | P1ASEL              | 000                  | 21, 116 |

| 94h    | _                        | Unimplemen         | nted                                                                                          |                  |                |                        |                 |             |                     | _                    | _       |

| 95h    | WPU <sup>(2)</sup>       | _                  | _                                                                                             | WPU5             | WPU4           | _                      | WPU2            | WPU1        | WPU0                | 11 -111              | 46, 116 |

| 96h    | IOC                      | _                  | _                                                                                             | IOC5             | IOC4           | IOC3                   | IOC2            | IOC1        | IOC0                | 00 0000              | 46, 116 |

| 97h    | _                        | Unimplemen         | nted                                                                                          |                  |                |                        |                 |             |                     | _                    | _       |

| 98h    | PMCON1 <sup>(7)</sup>    | _                  | —                                                                                             | —                | —              | _                      | WREN            | WR          | RD                  | 000                  | 29      |

| 99h    | PMCON2 <sup>(7)</sup>    | Program Me         | emory Contro                                                                                  | l Register 2     | (not a physic  | al register).          |                 |             |                     |                      | —       |

| 9Ah    | PMADRL <sup>(7)</sup>    | PMADRL7            | PMADRL6                                                                                       | PMADRL5          | PMADRL4        | PMADRL3                | PMADRL2         | PMADRL1     | PMADRL0             | 0000 0000            | 28      |

| 9Bh    | PMADRH <sup>(7)</sup>    | _                  | _                                                                                             | _                | —              | _                      | PMADRH2         | PMADRH1     | PMADRH0             | 000                  | 28      |

| 9Ch    | PMDATL <sup>(7)</sup>    | PMDATL7            | PMDATL6                                                                                       | PMDATL5          | PMDATL4        | PMDATL3                | PMDATL2         | PMDATL1     | PMDATL0             | 0000 0000            | 28      |

| 9Dh    | PMDATH <sup>(7)</sup>    | —                  | — Program Memory Data Register High Byte.                                                     |                  |                |                        |                 |             |                     | 00 0000              | 28      |

| 9Eh    | ADRESL <sup>(5, 6)</sup> | Least Signif       | icant 2 bits o                                                                                | f the left shift | ed result or 8 | bits of the rig        | ght shifted res | sult        |                     | xxxx xxxx            | 85, 117 |

| 9Fh    | ANSEL                    | —                  | ADCS2                                                                                         | ADCS1            | ADCS0          | ANS3                   | ANS2            | ANS1        | ANS0                | -000 1111            | 45, 117 |

| Logon  |                          |                    | sations road :                                                                                |                  |                | l                      |                 | l           | 1                   | 1                    | ·       |

#### **TABLE 2-4:** PIC12F615/617/HV615 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

- = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented IRP and RP1 bits are reserved, always maintain these bits clear. GP3 pull-up is enabled when MCLRE is '1' in the Configuration Word register. Legend: Note 1:

2:

MCLR and WDT Reset does not affect the previous value data latch. The GPIF bit will clear upon Reset but will set again if the mismatch 3: exists.

TRISIO3 always reads as '1' since it is an input only pin. 4:

Read only register. 5:

PIC12F615/617/HV615 only. 6:

7: PIC12F617 only.

### 2.2.2.5 PIR1 Register

The PIR1 register contains the Peripheral Interrupt flag bits, as shown in Register 2-5.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| U-0   | R/W-0               | R/W-0                 | U-0 | R/W-0 | U-0 | R/W-0                 | R/W-0  |

|-------|---------------------|-----------------------|-----|-------|-----|-----------------------|--------|

| —     | ADIF <sup>(1)</sup> | CCP1IF <sup>(1)</sup> | _   | CMIF  | —   | TMR2IF <sup>(1)</sup> | TMR1IF |

| bit 7 |                     |                       |     |       |     |                       | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                                                                                           |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ADIF: A/D Interrupt Flag bit <sup>(1)</sup>                                                                                          |

|       | 1 = A/D conversion complete                                                                                                          |

|       | 0 = A/D conversion has not completed or has not been started                                                                         |

| bit 5 | CCP1IF: CCP1 Interrupt Flag bit <sup>(1)</sup>                                                                                       |

|       | Capture mode:                                                                                                                        |

|       | <ul><li>1 = A TMR1 register capture occurred (must be cleared in software)</li><li>0 = No TMR1 register capture occurred</li></ul>   |

|       | <u>Compare mode</u> :<br>1 = A TMR1 register compare match occurred (must be cleared in software)                                    |

|       | 0 = No TMR1 register compare match occurred                                                                                          |

|       | <u>PWM mode</u> :                                                                                                                    |

|       | Unused in this mode                                                                                                                  |

| bit 4 | Unimplemented: Read as '0'                                                                                                           |

| bit 3 | CMIF: Comparator Interrupt Flag bit                                                                                                  |

|       | 1 = Comparator output has changed (must be cleared in software)                                                                      |

|       | 0 = Comparator output has not changed                                                                                                |

| bit 2 | Unimplemented: Read as '0'                                                                                                           |

| bit 1 | TMR2IF: Timer2 to PR2 Match Interrupt Flag bit <sup>(1)</sup>                                                                        |

|       | <ul> <li>1 = Timer2 to PR2 match occurred (must be cleared in software)</li> <li>0 = Timer2 to PR2 match has not occurred</li> </ul> |

| bit 0 | TMR1IF: Timer1 Overflow Interrupt Flag bit                                                                                           |

|       | 1 = Timer1 register overflowed (must be cleared in software)                                                                         |

|       | 0 = Timer1 has not overflowed                                                                                                        |

Note 1: PIC12F615/617/HV615 only. PIC12F609/HV609 unimplemented, read as '0'.

# 2.2.2.6 PCON Register

The Power Control (PCON) register (see Table 12-2) contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the software enable of the  $\overline{\text{BOR}}.$

The PCON register bits are shown in Register 2-6.

# REGISTER 2-6: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 <sup>(1)</sup> |

|-------|-----|-----|-----|-----|-----|-------|----------------------|

| —     | —   | —   | _   | -   | -   | POR   | BOR                  |

| bit 7 |     |     |     |     |     |       | bit 0                |

| Legend:           |                                                                                       |                                 |                        |                    |  |

|-------------------|---------------------------------------------------------------------------------------|---------------------------------|------------------------|--------------------|--|

| R = Readable bit  |                                                                                       | W = Writable bit                | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR |                                                                                       | '1' = Bit is set                | '0' = Bit is cleared   | x = Bit is unknown |  |

|                   |                                                                                       |                                 |                        |                    |  |

| bit 7-2           | 7-2 Unimplemented: Read as '0'                                                        |                                 |                        |                    |  |

| bit 1             | POR: Po                                                                               | POR: Power-on Reset Status bit  |                        |                    |  |

|                   | 1 = No Power-on Reset occurred                                                        |                                 |                        |                    |  |

|                   | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs) |                                 |                        |                    |  |

| bit 0             | BOR: Br                                                                               | BOR: Brown-out Reset Status bit |                        |                    |  |

|                   |                                                                                       |                                 |                        |                    |  |

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

**Note 1:** Reads as '0' if Brown-out Reset is disabled.

# 7.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of TCY as determined by the Timer1 prescaler.

## 7.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When counting, Timer1 is incremented on the rising edge of the external clock input T1CKI. In addition, the Counter mode clock can be synchronized to the microcontroller system clock or run asynchronously.

If an external clock oscillator is needed (and the microcontroller is using the INTOSC without CLKOUT), Timer1 can use the LP oscillator as a clock source.

In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after one or more of the following conditions:

- Timer1 is enabled after POR or BOR Reset

- A write to TMR1H or TMR1L

- T1CKI is high when Timer1 is disabled and when Timer1 is re-enabled T1CKI is low. See Figure 7-2.

# 7.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 7.4 Timer1 Oscillator

A low-power 32.768 kHz crystal oscillator is built-in between pins OSC1 (input) and OSC2 (output). The oscillator is enabled by setting the T1OSCEN control bit of the T1CON register. The oscillator will continue to run during Sleep.

The Timer1 oscillator is shared with the system LP oscillator. Thus, Timer1 can use this mode only when the primary system clock is derived from the internal oscillator or when in LP oscillator mode. The user must provide a software time delay to ensure proper oscillator start-up.

TRISIO5 and TRISIO4 bits are set when the Timer1 oscillator is enabled. GP5 and GP4 bits read as '0' and TRISIO5 and TRISIO4 bits read as '1'.

| Note: | The oscillator requires a start-up and   |

|-------|------------------------------------------|

|       | stabilization time before use. Thus,     |

|       | T1OSCEN should be set and a suitable     |

|       | delay observed prior to enabling Timer1. |

# 7.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 7.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

- Note: When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce a single spurious increment.

- Note: In asynchronous counter mode or when using the internal oscillator and T1ACS=1, Timer1 can not be used as a time base for the capture or compare modes of the ECCP module (for PIC12F615/617/ HV615 only).

#### 7.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TTMR1L register pair.

# 7.6 Timer1 Gate

Timer1 gate source is software configurable to be the T1G pin (or the alternate T1G pin) or the output of the Comparator. This allows the device to directly time external events using T1G or analog events using the Comparator. See the CMCON1 Register (Register 9-2) for selecting the Timer1 gate source. This feature can simplify the software for a Delta-Sigma A/D converter and many other applications. For more information on Delta-Sigma A/D converters, see the Microchip web site (www.microchip.com).

Note: TMR1GE bit of the T1CON register must be set to use either T1G or COUT as the Timer1 gate source. See Register 9-2 for more information on selecting the Timer1 gate source.

Timer1 gate can be inverted using the T1GINV bit of the T1CON register, whether it originates from the T1G pin or the Comparator output. This configures Timer1 to measure either the active-high or active-low time between events.

# 7.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- Timer1 interrupt enable bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TTMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

# 7.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

The device will wake-up on an overflow and execute the next instruction. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

# 7.9 ECCP Capture/Compare Time Base (PIC12F615/617/HV615 only)

The ECCP module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

For more information, see Section 11.0 "Enhanced Capture/Compare/PWM (With Auto-Shutdown and Dead Band) Module (PIC12F615/617/HV615 only)".

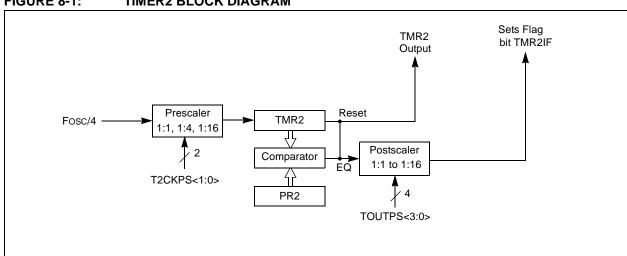

# 8.0 TIMER2 MODULE (PIC12F615/617/HV615 ONLY)

The Timer2 module is an 8-bit timer with the following features:

- 8-bit timer register (TMR2)

- 8-bit period register (PR2)

- Interrupt on TMR2 match with PR2

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

See Figure 8-1 for a block diagram of Timer2.

# 8.1 Timer2 Operation

The clock input to the Timer2 module is the system instruction clock (Fosc/4). The clock is fed into the Timer2 prescaler, which has prescale options of 1:1, 1:4 or 1:16. The output of the prescaler is then used to increment the TMR2 register.

The values of TMR2 and PR2 are constantly compared to determine when they match. TMR2 will increment from 00h until it matches the value in PR2. When a match occurs, two things happen:

- TMR2 is reset to 00h on the next increment cycle.

- The Timer2 postscaler is incremented

The match output of the Timer2/PR2 comparator is then fed into the Timer2 postscaler. The postscaler has postscale options of 1:1 to 1:16 inclusive. The output of the Timer2 postscaler is used to set the TMR2IF interrupt flag bit in the PIR1 register.

| FIGURE 8-1: | <b>TIMER2 BLOCK DIAGRAM</b> |

|-------------|-----------------------------|

|             |                             |

The TMR2 and PR2 registers are both fully readable and writable. On any Reset, the TMR2 register is set to 00h and the PR2 register is set to FFh.

Timer2 is turned on by setting the TMR2ON bit in the T2CON register to a '1'. Timer2 is turned off by clearing the TMR2ON bit to a '0'.

The Timer2 prescaler is controlled by the T2CKPS bits in the T2CON register. The Timer2 postscaler is controlled by the TOUTPS bits in the T2CON register. The prescaler and postscaler counters are cleared when:

- A write to TMR2 occurs.

- A write to T2CON occurs.

- Any device Reset occurs (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset).

Note: TMR2 is not cleared when T2CON is written.

# 9.3 Comparator Control

The comparator has two control and Configuration registers: CMCON0 and CMCON1. The CMCON1 register is used for controlling the interaction with Timer1 and simultaneously reading the comparator output.

The CMCON0 register (Register 9-1) contain the control and Status bits for the following:

- Enable

- Input selection

- Reference selection

- · Output selection

- Output polarity

#### 9.3.1 COMPARATOR ENABLE

Setting the CMON bit of the CMCON0 register enables the comparator for operation. Clearing the CMON bit disables the comparator for minimum current consumption.

#### 9.3.2 COMPARATOR INPUT SELECTION

The CMCH bit of the CMCON0 register directs one of four analog input pins to the comparator inverting input.

Note: To use CIN+ and CIN- pins as analog inputs, the appropriate bits must be set in the ANSEL register and the corresponding TRIS bits must also be set to disable the output drivers.

#### 9.3.3 COMPARATOR REFERENCE SELECTION

Setting the CMR bit of the CMxCON0 register directs an internal voltage reference or an analog input pin to the non-inverting input of the comparator. See **Section 9.10 "Comparator Voltage Reference"** for more information on the internal voltage reference module.

#### 9.3.4 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the COUT bit of the CMCON0 register. In order to make the output available for an external connection, the following conditions must be true:

- CMOE bit of the CMxCON0 register must be set

- Corresponding TRIS bit must be cleared

- CMON bit of the CMCON0 register must be set.

| Note 1: | The CMOE bit overrides the PORT data  |  |  |  |

|---------|---------------------------------------|--|--|--|

|         | latch. Setting the CMON has no impact |  |  |  |

|         | on the port override.                 |  |  |  |

2: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

### 9.3.5 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CMPOL bit of the CMCON0 register. Clearing CMPOL results in a non-inverted output. A complete table showing the output state versus input conditions and the polarity bit is shown in Table 9-1.

| Input Conditions | CMPOL | COUT |  |  |

|------------------|-------|------|--|--|

| CMVIN- > CMVIN+  | 0     | 0    |  |  |

| CMVIN- < CMVIN+  | 0     | 1    |  |  |

| CMVIN- > CMVIN+  | 1     | 1    |  |  |

| CMVIN- < CMVIN+  | 1     | 0    |  |  |

#### TABLE 9-1: OUTPUT STATE VS. INPUT CONDITIONS

**Note:** COUT refers to both the register bit and output pin.

# 9.4 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See **Section 16.0 "Electrical Specifications"** for more details.

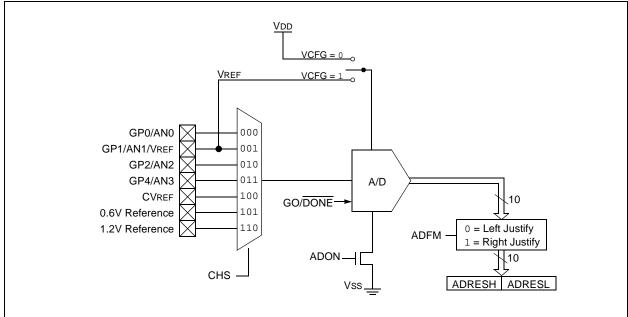

# 10.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE (PIC12F615/617/HV615 ONLY)

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESL and ADRESH).

The ADC voltage reference is software selectable to either VDD or a voltage applied to the external reference pins.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

Figure 10-1 shows the block diagram of the ADC.

# FIGURE 10-1: ADC BLOCK DIAGRAM

Note: The ADRESL and ADRESH registers are Read Only.

# 10.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- Results formatting

### 10.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. See the corresponding port section for more information.

| Note: | Analog voltages on any pin that is defined |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | as a digital input may cause the input     |  |  |  |  |  |

|       | buffer to conduct excess current.          |  |  |  |  |  |

#### 10.1.2 CHANNEL SELECTION

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 10.2 "ADC Operation"** for more information.

# 10.1.3 ADC VOLTAGE REFERENCE

The VCFG bit of the ADCON0 register provides control of the positive voltage reference. The positive voltage reference can be either VDD or an external voltage source. The negative voltage reference is always connected to the ground reference.

## 10.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ANSEL register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11 TAD periods as shown in Figure 10-3.

For correct conversion, the appropriate TAD specification must be met. See A/D conversion requirements in **Section 16.0 "Electrical Specifications"** for more information. Table 10-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

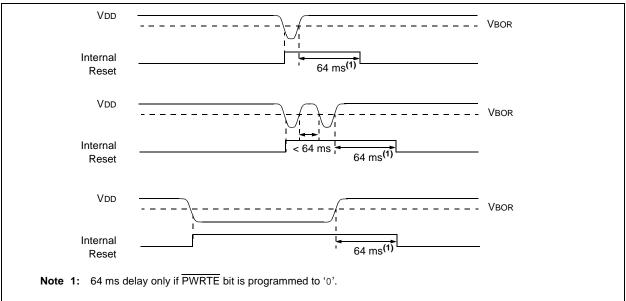

# 12.3.4 BROWN-OUT RESET (BOR)

The BOREN0 and BOREN1 bits in the Configuration Word register select one of three BOR modes. One mode has been added to allow control of the BOR enable for lower current during Sleep. By selecting BOREN<1:0> = 10, the BOR is automatically disabled in Sleep to conserve power and enabled on wake-up. See Register 12-1 for the Configuration Word definition.

A brown-out occurs when VDD falls below VBOR for greater than parameter TBOR (see Section 16.0 "Electrical Specifications"). The brown-out condition will reset the device. This will occur regardless of VDD slew rate. A Brown-out Reset may not occur if VDD falls below VBOR for less than parameter TBOR.

On any Reset (Power-on, Brown-out Reset, Watchdog timer, etc.), the chip will remain in Reset until VDD rises above VBOR (see Figure 12-3). If enabled, the Power-up Timer will be invoked by the Reset and keep the chip in Reset an additional 64 ms.

| Note: | The Power-up Timer is enabled by the |

|-------|--------------------------------------|

|       | PWRTE bit in the Configuration Word  |

|       | register.                            |

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

#### FIGURE 12-3: BROWN-OUT SITUATIONS

| ADDLW            | Add literal and W                                                                                                          |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the<br>W register. |  |  |

| 14.2 Instruction | Descriptions |

|------------------|--------------|

|------------------|--------------|

| BCF              | Bit Clear f                                                         |  |  |

|------------------|---------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] BCF f,b                                                   |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |  |

| Operation:       | $0 \rightarrow (f < b >)$                                           |  |  |

| Status Affected: | None                                                                |  |  |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |  |  |

| ADDWF            | Add W and f                                                                                                                                                                        |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] ADDWF f,d                                                                                                                                                                |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                           |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |  |  |  |  |

| BSF              | Bit Set f                                                           |  |  |  |

|------------------|---------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] BSF f,b                                                   |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |  |  |

| Operation:       | $1 \rightarrow (f < b >)$                                           |  |  |  |

| Status Affected: | None                                                                |  |  |  |

| Description:     | Bit 'b' in register 'f' is set.                                     |  |  |  |

| ANDLW            | AND literal with W                                                                                                     |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] ANDLW k                                                                                                      |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |

| Status Affected: | Z                                                                                                                      |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                           |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |  |  |  |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                                          |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                          |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b' in register 'f' is '0', the next<br>instruction is discarded, and a NOP<br>is executed instead, making this a<br>two-cycle instruction. |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                    |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] ANDWF f,d                                                                                                                                             |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |

# 16.2 DC Characteristics: PIC12F609/615/617-I (Industrial) PIC12F609/615/617-E (Extended)

| DC CHA | ARACTERISTICS                          | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |       |       |     |                                     |

|--------|----------------------------------------|------------------------------------------------------|-------|-------|-------|-----|-------------------------------------|

| Param  | Device Characteristics                 | Min                                                  | Тур†  | Max   | Units |     | Conditions                          |

| No.    | Device Characteristics                 |                                                      | וקעי  | IVIAN | Units | Vdd | Note                                |

| D010   | Supply Current (IDD) <sup>(1, 2)</sup> |                                                      | 13    | 25    | μA    | 2.0 | Fosc = 32 kHz                       |

|        | PIC12F609/615/617                      |                                                      | 19    | 29    | μA    | 3.0 | LP Oscillator mode                  |

|        |                                        |                                                      | 32    | 51    | μA    | 5.0 |                                     |

| D011*  |                                        |                                                      | 135   | 225   | μA    | 2.0 | Fosc = 1 MHz                        |

|        |                                        |                                                      | 185   | 285   | μA    | 3.0 | XT Oscillator mode                  |

|        |                                        | _                                                    | 300   | 405   | μA    | 5.0 |                                     |

| D012   |                                        | —                                                    | 240   | 360   | μA    | 2.0 | Fosc = 4 MHz                        |

|        |                                        |                                                      | 360   | 505   | μA    | 3.0 | XT Oscillator mode                  |

|        |                                        |                                                      | 0.66  | 1.0   | mA    | 5.0 |                                     |

| D013*  |                                        |                                                      | 75    | 110   | μA    | 2.0 | Fosc = 1 MHz                        |

|        |                                        |                                                      | 155   | 255   | μA    | 3.0 | EC Oscillator mode                  |

|        |                                        |                                                      | 345   | 530   | μA    | 5.0 |                                     |

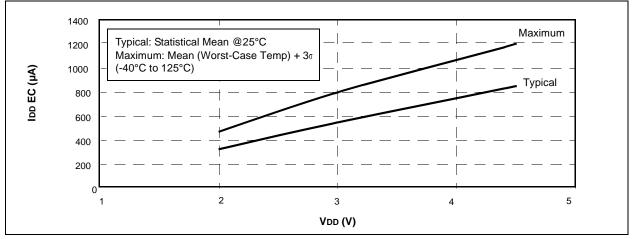

| D014   |                                        |                                                      | 185   | 255   | μA    | 2.0 | Fosc = 4 MHz                        |

|        |                                        |                                                      | 325   | 475   | μA    | 3.0 | EC Oscillator mode                  |

|        |                                        |                                                      | 0.665 | 1.0   | mA    | 5.0 |                                     |

| D016*  |                                        |                                                      | 245   | 340   | μA    | 2.0 | Fosc = 4 MHz                        |

|        |                                        |                                                      | 360   | 485   | μA    | 3.0 | INTOSC mode                         |

|        |                                        |                                                      | 0.620 | 0.845 | mA    | 5.0 |                                     |

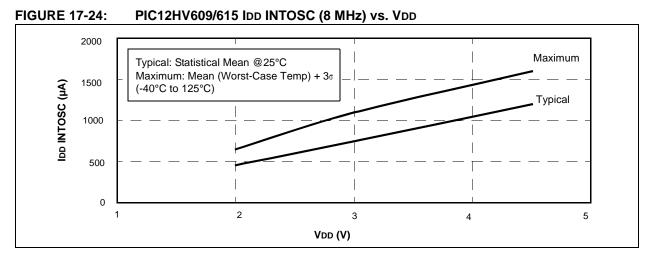

| D017   |                                        |                                                      | 395   | 550   | μA    | 2.0 | Fosc = 8 MHz                        |

|        |                                        |                                                      | 0.620 | 0.850 | mA    | 3.0 | INTOSC mode                         |

|        |                                        |                                                      | 1.2   | 1.6   | mA    | 5.0 |                                     |

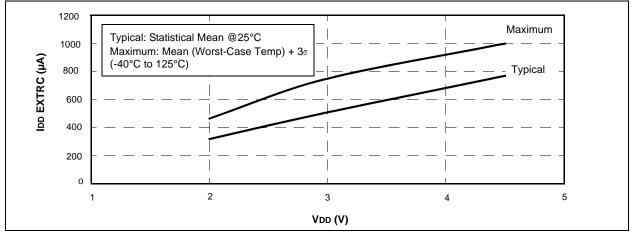

| D018   |                                        |                                                      | 175   | 235   | μA    | 2.0 | Fosc = 4 MHz                        |

|        |                                        |                                                      | 285   | 390   | μA    | 3.0 | EXTRC mode <sup>(3)</sup>           |

|        |                                        | —                                                    | 530   | 750   | μA    | 5.0 |                                     |

| D019   |                                        | _                                                    | 2.2   | 3.1   | mA    | 4.5 | Fosc = 20 MHz<br>HS Oscillator mode |

|        |                                        |                                                      | 2.8   | 3.35  | mA    | 5.0 |                                     |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-torail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in KOhms (KΩ).

# 16.6 DC Characteristics: PIC12HV609/615 - I (Industrial)

| DC CHARACTERISTICS           |                                                   | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |       |     |       |            |                                               |  |

|------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------------|-----------------------------------------------|--|

| Param Device Characteristics |                                                   | Min                                                                                                                                | Turnt | Мах | Units | Conditions |                                               |  |

| No.                          | Device Characteristics                            | IVIIII                                                                                                                             | Тур†  | wax | Units | Vdd        | Note                                          |  |

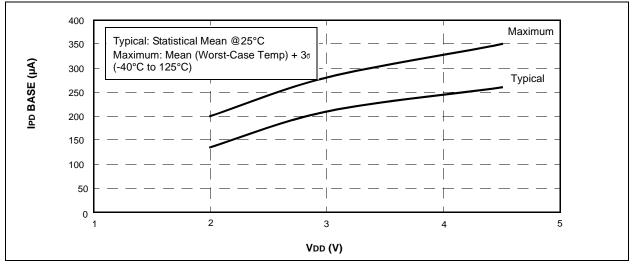

| D020                         | Power-down Base<br>Current (IPD) <sup>(2,3)</sup> | —                                                                                                                                  | 135   | 200 | μΑ    | 2.0        | WDT, BOR, Comparator, VREF and T1OSC disabled |  |

|                              |                                                   | _                                                                                                                                  | 210   | 280 | μΑ    | 3.0        | 7                                             |  |

|                              | PIC12HV609/615                                    | _                                                                                                                                  | 260   | 350 | μΑ    | 4.5        |                                               |  |

| D021                         |                                                   | —                                                                                                                                  | 135   | 200 | μΑ    | 2.0        | WDT Current <sup>(1)</sup>                    |  |

|                              |                                                   | _                                                                                                                                  | 210   | 285 | μΑ    | 3.0        |                                               |  |

|                              |                                                   | _                                                                                                                                  | 265   | 360 | μΑ    | 4.5        | 1                                             |  |

| D022                         |                                                   | —                                                                                                                                  | 215   | 285 | μΑ    | 3.0        | BOR Current <sup>(1)</sup>                    |  |

|                              |                                                   | _                                                                                                                                  | 265   | 360 | μΑ    | 4.5        | 1                                             |  |

| D023                         |                                                   | —                                                                                                                                  | 185   | 270 | μΑ    | 2.0        | Comparator Current <sup>(1)</sup> , single    |  |

|                              |                                                   | —                                                                                                                                  | 265   | 350 | μΑ    | 3.0        | comparator enabled                            |  |

|                              |                                                   | —                                                                                                                                  | 320   | 430 | μΑ    | 4.5        |                                               |  |

| D024                         |                                                   | —                                                                                                                                  | 165   | 235 | μΑ    | 2.0        | CVREF Current <sup>(1)</sup> (high range)     |  |

|                              |                                                   | —                                                                                                                                  | 255   | 330 | μΑ    | 3.0        |                                               |  |

|                              |                                                   | _                                                                                                                                  | 330   | 430 | μΑ    | 4.5        |                                               |  |

| D025*                        |                                                   | —                                                                                                                                  | 175   | 245 | μΑ    | 2.0        | CVREF Current <sup>(1)</sup> (low range)      |  |

|                              |                                                   | —                                                                                                                                  | 275   | 350 | μΑ    | 3.0        |                                               |  |

|                              |                                                   | —                                                                                                                                  | 355   | 450 | μΑ    | 4.5        |                                               |  |

| D026                         |                                                   | _                                                                                                                                  | 140   | 205 | μA    | 2.0        | T1OSC Current <sup>(1)</sup> , 32.768 kHz     |  |

|                              |                                                   | _                                                                                                                                  | 220   | 290 | μΑ    | 3.0        | ]                                             |  |

|                              |                                                   | —                                                                                                                                  | 270   | 360 | μA    | 4.5        |                                               |  |

| D027                         |                                                   | _                                                                                                                                  | 210   | 280 | μΑ    | 3.0        | A/D Current <sup>(1)</sup> , no conversion in |  |

|                              |                                                   | —                                                                                                                                  | 260   | 350 | μΑ    | 4.5        | progress                                      |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 4.5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral  $\Delta$  current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

3: Shunt regulator is always on and always draws operating current.

# 16.8 DC Characteristics: PIC12F609/615/617/12HV609/615-I (Industrial) PIC12F609/615/617/12HV609/615-E (Extended)

| DC CHARACTERISTICS |                       |                                          | Standard Operating Con<br>Operating temperature |          | ditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |       |                                                                    |

|--------------------|-----------------------|------------------------------------------|-------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------|

| Param<br>No.       | Sym                   | Characteristic                           | Min                                             | Тур†     | Max                                                                                                                            | Units | Conditions                                                         |

|                    | VIL Input Low Voltage |                                          |                                                 |          |                                                                                                                                |       |                                                                    |

|                    |                       | I/O port:                                |                                                 |          |                                                                                                                                |       |                                                                    |

| D030               |                       | with TTL buffer                          | Vss                                             | —        | 0.8                                                                                                                            | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                   |

| D030A              |                       |                                          | Vss                                             | —        | 0.15 Vdd                                                                                                                       | V     | $2.0V \leq V \text{DD} \leq 4.5 \text{V}$                          |

| D031               |                       | with Schmitt Trigger buffer              | Vss                                             | _        | 0.2 Vdd                                                                                                                        | V     | $2.0V \le VDD \le 5.5V$                                            |

| D032               |                       | MCLR, OSC1 (RC mode)                     | Vss                                             | _        | 0.2 Vdd                                                                                                                        | V     | (NOTE 1)                                                           |

| D033               |                       | OSC1 (XT and LP modes)                   | Vss                                             | _        | 0.3                                                                                                                            | V     |                                                                    |

| D033A              |                       | OSC1 (HS mode)                           | Vss                                             | —        | 0.3 Vdd                                                                                                                        | V     |                                                                    |

|                    | VIH                   | Input High Voltage                       |                                                 |          |                                                                                                                                |       |                                                                    |

|                    |                       | I/O ports:                               |                                                 | _        |                                                                                                                                |       |                                                                    |

| D040               |                       | with TTL buffer                          | 2.0                                             | _        | Vdd                                                                                                                            | V     | $4.5V \leq V \text{DD} \leq 5.5V$                                  |

| D040A              |                       |                                          | 0.25 VDD + 0.8                                  | —        | Vdd                                                                                                                            | V     | $2.0V \leq V \text{DD} \leq 4.5 \text{V}$                          |

| D041               |                       | with Schmitt Trigger buffer              | 0.8 Vdd                                         | —        | Vdd                                                                                                                            | V     | $2.0V \leq V \text{DD} \leq 5.5 \text{V}$                          |

| D042               |                       | MCLR                                     | 0.8 Vdd                                         | —        | Vdd                                                                                                                            | V     |                                                                    |

| D043               |                       | OSC1 (XT and LP modes)                   | 1.6                                             | —        | Vdd                                                                                                                            | V     |                                                                    |

| D043A              |                       | OSC1 (HS mode)                           | 0.7 Vdd                                         | _        | Vdd                                                                                                                            | V     |                                                                    |

| D043B              |                       | OSC1 (RC mode)                           | 0.9 Vdd                                         | —        | Vdd                                                                                                                            | V     | (NOTE 1)                                                           |

|                    | lı∟                   | Input Leakage Current <sup>(2,3)</sup>   |                                                 |          |                                                                                                                                |       |                                                                    |

| D060               |                       | I/O ports                                | _                                               | ± 0.1    | ± 1                                                                                                                            | μΑ    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance                   |

| D061               |                       | GP3/MCLR <sup>(3,4)</sup>                | —                                               | $\pm0.7$ | ± 5                                                                                                                            | μΑ    | $V\text{SS} \leq V\text{PIN} \leq V\text{DD}$                      |

| D063               |                       | OSC1                                     | —                                               | ± 0.1    | ± 5                                                                                                                            | μA    | VSS $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration |

| D070*              | IPUR                  | GPIO Weak Pull-up Current <sup>(5)</sup> | 50                                              | 250      | 400                                                                                                                            | μΑ    | VDD = 5.0V, VPIN = VSS                                             |

|                    | Vol                   | Output Low Voltage                       | _                                               | _        | 0.6                                                                                                                            | V     | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                       |

| D080               |                       | I/O ports                                | _                                               | -        | 0.6                                                                                                                            | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                        |

|                    | Vон                   | Output High Voltage                      | Vdd - 0.7                                       | —        | —                                                                                                                              | V     | IOH = -2.5mA, VDD = 4.5V,<br>-40°С to +125°С                       |