Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 5                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 64 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                    |

| Data Converters            | A/D 4x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-TSSOP, 8-MSOP (0.118", 3.00mm Width)                                     |

| Supplier Device Package    | 8-MSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12hv615t-i-ms |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, GPIO change and external GP2/INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | GPIE  | T0IF  | INTF  | GPIF  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | GIE: Global Interrupt Enable bit<br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts                                                                                        |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                      |

| bit 5 | <b>TolE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                    |

| bit 4 | INTE: GP2/INT External Interrupt Enable bit<br>1 = Enables the GP2/INT external interrupt<br>0 = Disables the GP2/INT external interrupt                                                      |

| bit 3 | <b>GPIE:</b> GPIO Change Interrupt Enable bit <sup>(1)</sup><br>1 = Enables the GPIO change interrupt<br>0 = Disables the GPIO change interrupt                                               |

| bit 2 | <b>T0IF:</b> Timer0 Overflow Interrupt Flag bit <sup>(2)</sup><br>1 = Timer0 register has overflowed (must be cleared in software)<br>0 = Timer0 register did not overflow                    |

| bit 1 | INTF: GP2/INT External Interrupt Flag bit<br>1 = The GP2/INT external interrupt occurred (must be cleared in software)<br>0 = The GP2/INT external interrupt did not occur                    |

| bit 0 | <b>GPIF:</b> GPIO Change Interrupt Flag bit<br>1 = When at least one of the GPIO <5:0> pins changed state (must be cleared in software)<br>0 = None of the GPIO <5:0> pins have changed state |

**Note 1:** IOC register must also be enabled.

2: T0IF bit is set when TMR0 rolls over. TMR0 is unchanged on Reset and should be initialized before clearing T0IF bit.

## 3.0 FLASH PROGRAM MEMORY SELF READ/SELF WRITE CONTROL (FOR PIC12F617 ONLY)

The Flash program memory is readable and writable during normal operation (full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers (see Registers 3-1 to 3-5). There are six SFRs used to read and write this memory:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When interfacing the program memory block, the PMDATL and PMDATH registers form a two-byte word which holds the 14-bit data for read/write, and the PMADRL and PMADRH registers form a two-byte word which holds the 13-bit address of the Flash location being accessed. These devices have 2K words of program Flash with an address range from 0000h to 07FFh.

The program memory allows single word read and a by four word write. A four word write automatically erases the row of the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

When the device is code-protected, the CPU may continue to read and write the Flash program memory.

Depending on the settings of the Flash Program Memory Enable (WRT<1:0>) bits, the device may or may not be able to write certain blocks of the program memory, however, reads of the program memory are allowed.

When the Flash program memory Code Protection  $(\overline{CP})$  bit in the Configuration Word register is enabled, the program memory is code-protected, and the device programmer (ICSP<sup>TM</sup>) cannot access data or program memory.

#### 3.1 PMADRH and PMADRL Registers

The PMADRH and PMADRL registers can address up to a maximum of 8K words of program memory.

When selecting a program address value, the Most Significant Byte (MSB) of the address is written to the PMADRH register and the Least Significant Byte (LSB) is written to the PMADRL register.

## 3.2 PMCON1 and PMCON2 Registers

PMCON1 is the control register for the data program memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear.

PMCON2 is not a physical register. Reading PMCON2 will read all '0's. The PMCON2 register is used exclusively in the Flash memory write sequence.

## 4.0 OSCILLATOR MODULE

### 4.1 Overview

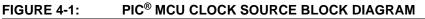

The Oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 4-1 illustrates a block diagram of the Oscillator module.

Clock sources can be configured from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be configured with a choice of two selectable speeds: internal or external system clock source.

The Oscillator module can be configured in one of eight clock modes.

- 3. EC External clock with I/O on OSC2/CLKOUT.

- 4. LP 32 kHz Low-Power Crystal mode.

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode.

- 6. HS High Gain Crystal or Ceramic Resonator mode.

- 7. RC External Resistor-Capacitor (RC) with FOSC/4 output on OSC2/CLKOUT.

- 8. RCIO External Resistor-Capacitor (RC) with I/O on OSC2/CLKOUT.

- 9. INTOSC Internal oscillator with Fosc/4 output on OSC2 and I/O on OSC1/CLKIN.

- 10. INTOSCIO Internal oscillator with I/O on OSC1/CLKIN and OSC2/CLKOUT.

Clock Source modes are configured by the FOSC<2:0> bits in the Configuration Word register (CONFIG). The Internal Oscillator module provides a selectable system clock mode of either 4 MHz (Postscaler) or 8 MHz (INTOSC).

NOTES:

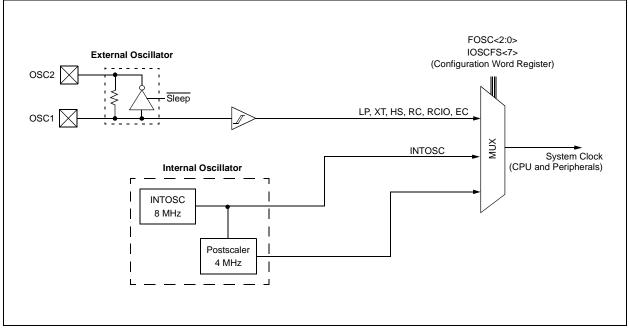

## 5.2.4.6 GP5/T1CKI/P1A<sup>(1, 2)</sup>/OSC1/CLKIN

Figure 5-5 shows the diagram for this pin. The GP5 pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 clock input

- PWM output, alternate pin<sup>(1, 2)</sup>

- a crystal/resonator connection

- a clock input

2: PIC12F615/617/HV615 only.

## FIGURE 5-5: BLOCK DIAGRAM OF GP5

### 9.2 Analog Input Connection Considerations

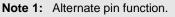

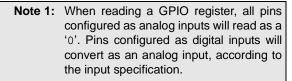

A simplified circuit for an analog input is shown in Figure 9-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

#### FIGURE 9-3: ANALOG INPUT MODEL

Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

## TABLE 9-2:SUMMARY OF REGISTERS ASSOCIATED WITH THE COMPARATOR AND<br/>VOLTAGE REFERENCE MODULES

| Name   | Bit 7  | Bit 6                | Bit 5                 | Bit 4                | Bit 3   | Bit 2               | Bit 1                 | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|--------|----------------------|-----------------------|----------------------|---------|---------------------|-----------------------|---------|----------------------|---------------------------------|

| ANSEL  | _      | ADCS2 <sup>(1)</sup> | ADCS1 <sup>(1)</sup>  | ADCS0 <sup>(1)</sup> | ANS3    | ANS2 <sup>(1)</sup> | ANS1                  | ANS0    | -000 1111            | -000 1111                       |

| CMCON0 | CMON   | COUT                 | CMOE                  | CMPOL                | _       | CMR                 | _                     | CMCH    | 0000 -000            | 0000 -000                       |

| CMCON1 | _      | _                    | _                     | T1ACS                | CMHYS   | —                   | T1GSS                 | CMSYNC  | 0000 0000            | 0000 0000                       |

| INTCON | GIE    | PEIE                 | T0IE                  | INTE                 | GPIE    | T0IF                | INTF                  | GPIF    | 0000 000x            | 0000 000x                       |

| PIE1   | _      | ADIE <sup>(1)</sup>  | CCP1IE <sup>(1)</sup> | _                    | CMIE    | —                   | TMR2IE <sup>(1)</sup> | TMR1IE  | -00-0-00             | -00-0-00                        |

| PIR1   | _      | ADIF <sup>(1)</sup>  | CCP1IF <sup>(1)</sup> | _                    | CMIF    | —                   | TMR2IF <sup>(1)</sup> | TMR1IF  | -00-0-00             | -00-0-00                        |

| GPIO   | _      | _                    | GP5                   | GP4                  | GP3     | GP2                 | GP1                   | GP0     | xx xxxx              | uu uuuu                         |

| TRISIO | _      | _                    | TRISIO5               | TRISIO4              | TRISIO3 | TRISIO2             | TRISIO1               | TRISIO0 | 11 1111              | 11 1111                         |

| VRCON  | CMVREN |                      | VRR                   | FVREN                | VR3     | VR2                 | VR1                   | VR0     | 0-00 0000            | 0-00 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for comparator.

**Note 1:** For PIC12F615/617/HV615 only.

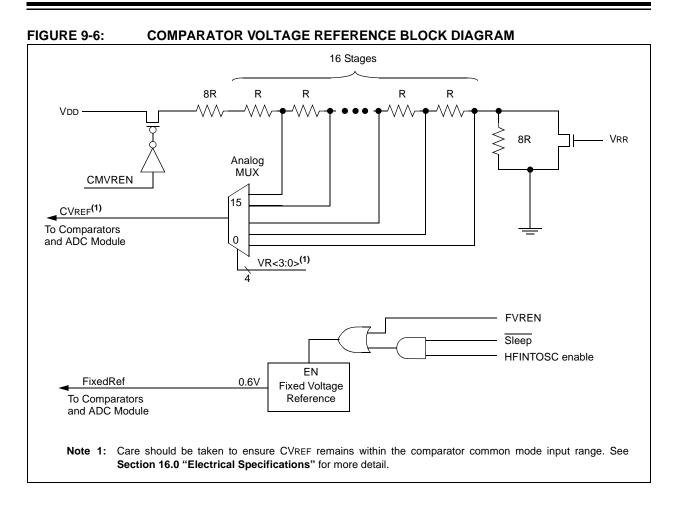

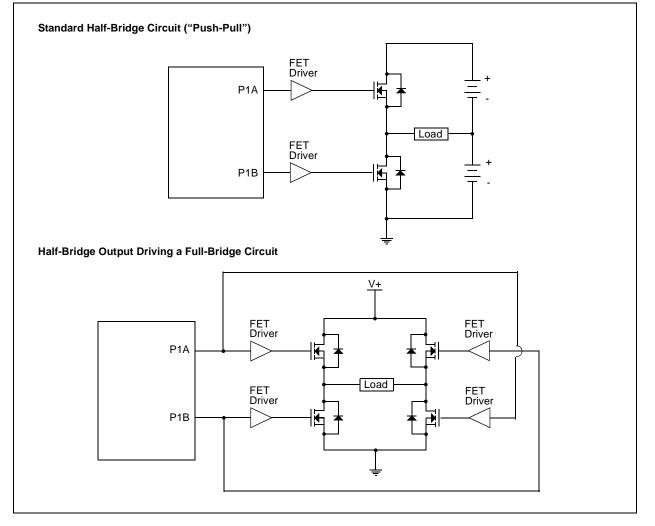

### 11.4.1 HALF-BRIDGE MODE

In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the CCP1/P1A pin, while the complementary PWM output signal is output on the P1B pin (see Figure 11-8). This mode can be used for Half-Bridge applications, as shown in Figure 11-9, or for Full-Bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge mode, the programmable dead-band delay can be used to prevent shoot-through current in Half-Bridge power devices. The value of the PDC<6:0> bits of the PWM1CON register sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 11.4.6 "Programmable Dead-Band Delay mode"** for more details of the dead-band delay operations. Since the P1A and P1B outputs are multiplexed with the PORT data latches, the associated TRIS bits must be cleared to configure P1A and P1B as outputs.

#### FIGURE 11-8: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

### FIGURE 11-9: EXAMPLE OF HALF-BRIDGE APPLICATIONS

## 12.5 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W and STATUS registers). This must be implemented in software.

Temporary holding registers W\_TEMP and STATUS\_TEMP should be placed in the last 16 bytes of GPR (see Figure 2-3). These 16 locations are common to all banks and do not require banking. This makes context save and restore operations simpler. The code shown in Example 12-1 can be used to:

- Store the W register

- Store the STATUS register

- Execute the ISR code

- Restore the Status (and Bank Select Bit register)

- Restore the W register

| Note: | The PIC12F609/615/617/12HV609/615      |

|-------|----------------------------------------|

|       | does not require saving the PCLATH.    |

|       | However, if computed GOTOs are used in |

|       | both the ISR and the main code, the    |

|       | PCLATH must be saved and restored in   |

|       | the ISR.                               |

#### EXAMPLE 12-1: SAVING STATUS AND W REGISTERS IN RAM

| MOVWF<br>SWAPF | W_TEMP<br>STATUS,W | ;Copy W to TEMP register<br>;Swap status to be saved into W                                                  |

|----------------|--------------------|--------------------------------------------------------------------------------------------------------------|

| MOVWF          | STATUS TEMP        | ;Swaps are used because they do not affect the status bits<br>;Save status to bank zero STATUS_TEMP register |

| :              |                    |                                                                                                              |

| :(ISR)         | )                  | ;Insert user code here                                                                                       |

| SWAPF          | STATUS_TEMP,W      | ;Swap STATUS_TEMP register into W<br>;(sets bank to original state)                                          |

| MOVWF          | STATUS             | ;Move W into STATUS register                                                                                 |

| SWAPF          | W_TEMP,F           | ;Swap W_TEMP                                                                                                 |

| SWAPF          | W_TEMP,W           | ;Swap W_TEMP into W                                                                                          |

## 12.6 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator, which requires no external components. This RC oscillator is separate from the external RC oscillator of the CLKIN pin and INTOSC. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device has been stopped (for example, by execution of a SLEEP instruction). During normal operation, a WDT time out generates a device Reset. If the device is in Sleep mode, a WDT time out causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the Configuration bit, WDTE, as clear (Section 12.1 "Configuration Bits").

## 12.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the prescaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time out.

| MOVF             | Move f                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                            |  |  |  |  |  |

| Operation:       | (f) $\rightarrow$ (dest)                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Description:     | The contents of register 'f' is<br>moved to a destination dependent<br>upon the status of 'd'. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register 'f'<br>itself. $d = 1$ is useful to test a file<br>register since Status flag Z is<br>affected. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                                 |  |  |  |  |  |

| MOVWF            | Move W to f                                                          |

|------------------|----------------------------------------------------------------------|

| Syntax:          | [label] MOVWF f                                                      |

| Operands:        | $0 \leq f \leq 127$                                                  |

| Operation:       | $(W) \rightarrow (f)$                                                |

| Status Affected: | None                                                                 |

| Description:     | Move data from W register to<br>register 'f'.                        |

| Words:           | 1                                                                    |

| Cycles:          | 1                                                                    |

| Example:         | MOVW OPTION<br>F                                                     |

|                  | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction |

|                  | $\begin{array}{rcl} OPTION = & 0x4F \\ W & = & 0x4F \end{array}$     |

| MOVLW            | Move literal to W                                                                                   |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                            |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                   |  |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                                 |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                |  |  |  |  |  |  |  |

| Description:     | The eight-bit literal 'k' is loaded into<br>W register. The "don't cares" will<br>assemble as '0's. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                   |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                   |  |  |  |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                          |  |  |  |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                                       |  |  |  |  |  |  |  |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

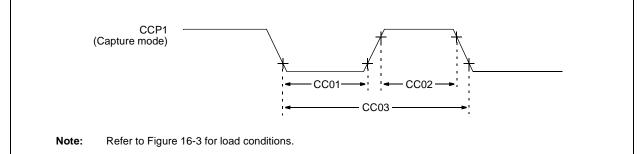

### FIGURE 16-9: PIC12F615/617/HV615 CAPTURE/COMPARE/PWM TIMINGS (ECCP)

#### TABLE 16-6: PIC12F615/617/HV615 CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP)

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                        |                |                       |   |   |    |                                       |

|--------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------|----------------|-----------------------|---|---|----|---------------------------------------|

| Param<br>No.                                                                                                             | Sym  | Characteristic Min Typ† Max Units Cond |                |                       |   |   |    | Conditions                            |

| CC01*                                                                                                                    | TccL | CCP1 Input Low Time                    | No Prescaler   | 0.5Tcy + 20           | - | — | ns |                                       |

|                                                                                                                          |      |                                        | With Prescaler | 20                    | — | — | ns |                                       |

| CC02*                                                                                                                    | ТссН | CCP1 Input High Time                   | No Prescaler   | 0.5Tcy + 20           | — | — | ns |                                       |

|                                                                                                                          |      |                                        | With Prescaler | 20                    | — | — | ns |                                       |

| CC03*                                                                                                                    | TccP | CCP1 Input Period                      |                | <u>3Tcy + 40</u><br>N | — | _ | ns | N = prescale<br>value (1, 4 or<br>16) |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### TABLE 16-7: COMPARATOR SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |         |                                        |        |     |       |           |       |          |

|--------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------|--------|-----|-------|-----------|-------|----------|

| Param<br>No.                                                                                                             | Sym     | Characteristics                        |        | Min | Тур†  | Мах       | Units | Comments |

| CM01                                                                                                                     | Vos     | Input Offset Voltage <sup>(2)</sup>    |        |     | ± 5.0 | ± 10      | mV    |          |

| CM02                                                                                                                     | Vсм     | Input Common Mode Voltage              |        |     | —     | Vdd - 1.5 | V     |          |

| CM03*                                                                                                                    | CMRR    | Common Mode Rejection Ratio            |        |     | —     | —         | dB    |          |

| CM04*                                                                                                                    | Trt     | Response Time <sup>(1)</sup> Falling   |        | _   | 150   | 600       | ns    |          |

|                                                                                                                          |         |                                        | Rising | _   | 200   | 1000      | ns    |          |

| CM05*                                                                                                                    | TMC2COV | Comparator Mode Change to Output Valid |        | _   | _     | 10        | μS    |          |

| CM06*                                                                                                                    | VHYS    | Input Hysteresis Voltage               |        | _   | 45    | 60        | mV    |          |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Response time is measured with one comparator input at (VDD - 1.5)/2 - 100 mV to (VDD - 1.5)/2 + 20 mV. The other input is at (VDD -1.5)/2.

2: Input offset voltage is measured with one comparator input at (VDD - 1.5V)/2.

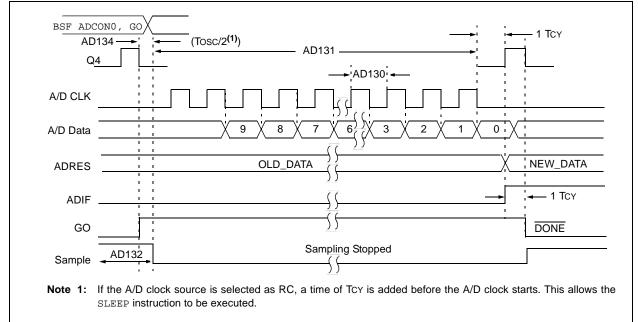

#### TABLE 16-12: PIC12F615/617/HV615 A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                                                        | Min | Тур†            | Мах | Units | Conditions                                                                                                                                       |

|--------------|------|-----------------------------------------------------------------------|-----|-----------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| AD130*       | TAD  | A/D Clock Period                                                      | 1.6 | -               | 9.0 | μS    | Tosc-based, VREF $\geq$ 3.0V                                                                                                                     |

|              |      |                                                                       | 3.0 | —               | 9.0 | μS    | Tosc-based, VREF full range <sup>(3)</sup>                                                                                                       |

|              |      | A/D Internal RC<br>Oscillator Period                                  | 3.0 | 6.0             | 9.0 | μS    | ADCS<1:0> = 11 (ADRC mode)<br>At VDD = 2.5V                                                                                                      |

|              |      |                                                                       | 1.6 | 4.0             | 6.0 | μS    | At VDD = 5.0V                                                                                                                                    |

| AD131        | TCNV | Conversion Time<br>(not including<br>Acquisition Time) <sup>(1)</sup> | _   | 11              | _   | Tad   | Set GO/DONE bit to new data in A/D<br>Result register                                                                                            |

| AD132*       | TACQ | Acquisition Time                                                      |     | 11.5            | _   | μS    |                                                                                                                                                  |

| AD133*       | TAMP | Amplifier Settling Time                                               |     | _               | 5   | μS    |                                                                                                                                                  |

| AD134        | Tgo  | Q4 to A/D Clock Start                                                 | _   | Tosc/2          | —   | —     |                                                                                                                                                  |

|              |      |                                                                       | _   | Tosc/2 +<br>Tcy | -   | _     | If the A/D clock source is selected as RC, a time of TcY is added before the A/D clock starts. This allows the SLEEP instruction to be executed. |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRESH and ADRESL registers may be read on the following TCY cycle.

- 2: See Section 10.3 "A/D Acquisition Requirements" for minimum conditions.

- 3: Full range for PIC12HV609/HV615 powered by the shunt regulator is the 5V regulated voltage.

#### FIGURE 16-10: PIC12F615/617/HV615 A/D CONVERSION TIMING (NORMAL MODE)

## 16.12 High Temperature Operation

This section outlines the specifications for the <u>PIC12F615</u> device operating in a temperature range <u>between -40°C and 150°C</u>.<sup>(4)</sup> The specifications between -40°C and 150°C<sup>(4)</sup> are identical to those shown in DS41288 and DS80329.

| Note 1: | Writes are <u>not allowed</u> for Flash<br>Program Memory above 125°C.                                                                                                                                                                                        |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 2:      | All AC timing specifications are increased<br>by 30%. This derating factor will include<br>parameters such as TPWRT.                                                                                                                                          |  |  |  |  |  |  |

| 3:      | <b>3:</b> The temperature range indicator in the part number is "H" for -40°C to 150°C. <sup>(4)</sup>                                                                                                                                                        |  |  |  |  |  |  |

| i       | Example: PIC12F615T-H/ST indicates the device is shipped in a TAPE and reel configuration, in the MSOP package, and is rated for operation from -40°C to 150°C. <sup>(4)</sup>                                                                                |  |  |  |  |  |  |

| 4:      | AEC-Q100 reliability testing for devices<br>intended to operate at 150°C is 1,000<br>hours. Any design in which the total oper-<br>ating time from 125°C to 150°C will be<br>greater than 1,000 hours is not warranted<br>without prior written approval from |  |  |  |  |  |  |

Microchip Technology Inc.

| Parameter                    | Source/Sink | Value | Units |

|------------------------------|-------------|-------|-------|

| Max. Current: VDD            | Source      | 20    | mA    |

| Max. Current: Vss            | Sink        | 50    | mA    |

| Max. Current: PIN            | Source      | 5     | mA    |

| Max. Current: PIN            | Sink        | 10    | mA    |

| Pin Current: at VOH          | Source      | 3     | mA    |

| Pin Current: at VoL          | Sink        | 8.5   | mA    |

| Port Current: GPIO           | Source      | 20    | mA    |

| Port Current: GPIO           | Sink        | 50    | mA    |

| Maximum Junction Temperature |             | 155   | °C    |

#### TABLE 16-13: ABSOLUTE MAXIMUM RATINGS

**Note:** Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

| Param<br>No. | Device               | Units | Min | Turn  | Max  | Condition |                     |  |  |

|--------------|----------------------|-------|-----|-------|------|-----------|---------------------|--|--|

|              | Characteristics      |       |     | Тур   |      | Vdd       | Note                |  |  |

| D010         |                      |       | _   | 13    | 58   | 2.0       |                     |  |  |

|              | Supply Current (IDD) | μA    | _   | 19    | 67   | 3.0       | IDD LP OSC (32 kHz) |  |  |

|              |                      |       | _   | 32    | 92   | 5.0       |                     |  |  |

| D011         |                      |       |     | 135   | 316  | 2.0       |                     |  |  |

|              |                      | μA    | _   | 185   | 400  | 3.0       | IDD XT OSC (1 MHz)  |  |  |

|              |                      |       | _   | 300   | 537  | 5.0       |                     |  |  |

| D012         |                      |       | _   | 240   | 495  | 2.0       |                     |  |  |

|              |                      | μA    | _   | 360   | 680  | 3.0       | IDD XT OSC (4 MHz)  |  |  |

|              |                      | mA    | _   | 0.660 | 1.20 | 5.0       |                     |  |  |

| D013         |                      |       | _   | 75    | 158  | 2.0       |                     |  |  |

|              |                      | μΑ    | _   | 155   | 338  | 3.0       | IDD EC OSC (1 MHz)  |  |  |

|              |                      |       | _   | 345   | 792  | 5.0       |                     |  |  |

| D014         |                      | μA    |     | 185   | 357  | 2.0       |                     |  |  |

|              |                      | μΛ    |     | 325   | 625  | 3.0       | IDD EC OSC (4 MHz)  |  |  |

|              |                      | mA    | _   | 0.665 | 1.30 | 5.0       |                     |  |  |

| D016         |                      | 1     |     | 245   | 476  | 2.0       |                     |  |  |

|              |                      | μΑ    | _   | 360   | 672  | 3.0       | IDD INTOSC (4 MHz)  |  |  |

|              |                      |       | _   | 620   | 1.10 | 5.0       |                     |  |  |

| D017         |                      | μΑ    |     | 395   | 757  | 2.0       |                     |  |  |

|              |                      | mA    | _   | 0.620 | 1.20 | 3.0       | IDD INTOSC (8 MHz)  |  |  |

|              |                      | 1117  | _   | 1.20  | 2.20 | 5.0       |                     |  |  |

| D018         |                      |       |     | 175   | 332  | 2.0       |                     |  |  |

|              |                      | μΑ    | _   | 285   | 518  | 3.0       | IDD EXTRC (4 MHz)   |  |  |

|              |                      |       |     | 530   | 972  | 5.0       |                     |  |  |

| D019         |                      | mA    | —   | 2.20  | 4.10 | 4.5       | IDD HS OSC (20 MHz) |  |  |

|              |                      |       |     | 2.80  | 4.80 | 5.0       | (20 אוועב) אוויעטו  |  |  |

#### TABLE 16-14: DC CHARACTERISTICS FOR IDD SPECIFICATIONS FOR PIC12F615-H (High Temp.)

| TABLE TO TO. OUDILLATOR TARAIN |        |                                                |                        | 012101 | <u>9-11 (11</u> | gii i ciii | P-) |                                                                                                                                  |

|--------------------------------|--------|------------------------------------------------|------------------------|--------|-----------------|------------|-----|----------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                   | Sym    | Characteristic                                 | Frequency<br>Tolerance | Units  | Min             | Тур        | Max | Conditions                                                                                                                       |

| OS08                           | INTosc | Int. Calibrated INTOSC<br>Freq. <sup>(1)</sup> | ±10%                   | MHz    | 7.2             | 8.0        | 8.8 | $\begin{array}{l} 2.0V \leq V \text{DD} \leq 5.5V \\ \textbf{-40^{\circ}C} \leq T \text{A} \leq 150^{\circ}\text{C} \end{array}$ |

## TABLE 16-18: OSCILLATOR PARAMETERS FOR PIC12F615-H (High Temp.)

**Note 1:** To ensure these oscillator frequency tolerances, Vdd and Vss must be capacitively decoupled as close to the device as possible. 0.1 µF and 0.01 µF values in parallel are recommended.

#### TABLE 16-19: COMPARATOR SPECIFICATIONS FOR PIC12F615-H (High Temp.)

| Param<br>No. | Sym | Characteristic       | Units | Min | Тур | Max | Conditions    |

|--------------|-----|----------------------|-------|-----|-----|-----|---------------|

| CM01         | Vos | Input Offset Voltage | mV    | _   | ±5  | ±20 | (Vdd - 1.5)/2 |

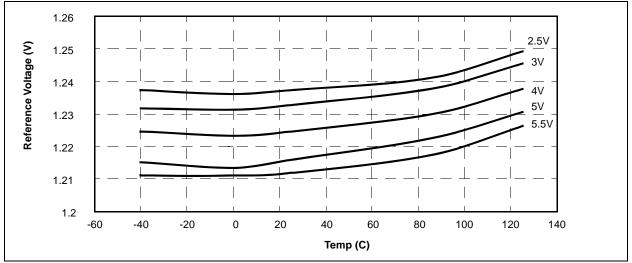

FIGURE 17-48: 1.2V REFERENCE VOLTAGE vs. TEMP (TYPICAL)

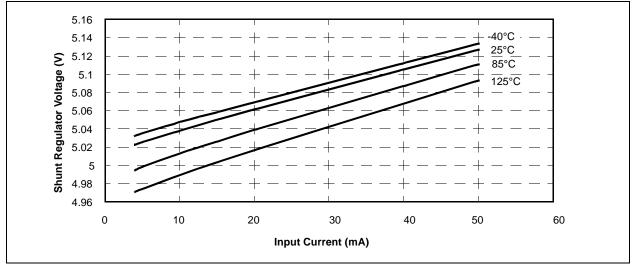

FIGURE 17-49: SHUNT REGULATOR VOLTAGE vs. INPUT CURRENT (TYPICAL)

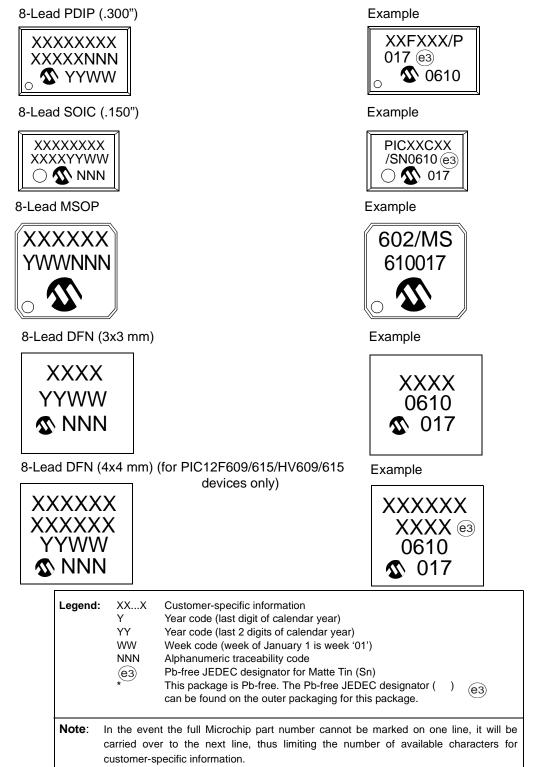

## **18.0 PACKAGING INFORMATION**

## **18.1** Package Marking Information

Standard PIC device marking consists of Microchip part number, year code, week code, and traceability code. For PIC device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.              | <u>x /xx xxx</u>                                                                                                                                                                                                                                                          | Examples:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                | Temperature<br>Range         Package         Pattern           PIC12F609, PIC12F609T <sup>(1)</sup> , PIC12HV609, PIC12HV609T <sup>(1)</sup> ,<br>PIC12F615, PIC12F615T <sup>(1)</sup> , PIC12HV615, PIC12HV615T <sup>(1)</sup> ,<br>PIC12F617, PIC12F617T <sup>(1)</sup> | <ul> <li>a) PIC12F615-E/P 301 = Extended Temp., PDIP package, 20 MHz, QTP pattern #301</li> <li>b) PIC12F615-I/SN = Industrial Temp., SOIC package, 20 MHz</li> <li>c) PIC12F615T-E/MF = Tape and Reel, Extended Temp., 3x3 DFN, 20 MHz</li> <li>d) PIC12F609T-E/MF = Tape and Reel, Extended Temp., 3x3 DFN, 20 MHz</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Temperature<br>Range: | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                      | <ul> <li>e) PIC12HV615T-E/MF = Tape and Reel,<br/>Extended Temp., 3x3 DFN, 20 MHz</li> <li>f) PIC12HV609T-E/MF = Tape and Reel,<br/>Extended Temp., 3x3 DFN, 20 MHz</li> <li>g) PIC12F617T-E/MF = Tape and Reel, Extended<br/>Temp., 3x3 DFN, 20 MHz</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Package:              | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                      | <ul> <li>h) PIC12F617-I/P = Industrial Temp., PDIP package, 20 MHz</li> <li>i) PIC12F615-H/SN = High Temp., SOIC package, 20 MHz</li> <li>Note 1: T = in tape and reel for MSOP, SOIC and DFN packages only.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Pattern:              | QTP, SQTP or ROM Code; Special Requirements (blank otherwise)                                                                                                                                                                                                             | <ol> <li>Proposition of the provide of the prov</li></ol> |