Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx110f016b-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              |                        | Pin Nu                                      | mber <sup>(1)</sup> |                                 |             | -                   |                                                            |

|--------------|------------------------|---------------------------------------------|---------------------|---------------------------------|-------------|---------------------|------------------------------------------------------------|

| Pin Name     | 28-pin<br>QFN          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type      | Description                                                |

| RC0          | —                      | —                                           | 3                   | 25                              | I/O         | ST                  | PORTC is a bidirectional I/O port                          |

| RC1          | —                      | —                                           | 4                   | 26                              | I/O         | ST                  |                                                            |

| RC2          | —                      | —                                           | _                   | 27                              | I/O         | ST                  |                                                            |

| RC3          | —                      | —                                           | 11                  | 36                              | I/O         | ST                  | _                                                          |

| RC4          | —                      | —                                           | _                   | 37                              | I/O         | ST                  | _                                                          |

| RC5          | —                      |                                             |                     | 38                              | I/O         | ST                  | _                                                          |

| RC6          |                        | —                                           | _                   | 2                               | I/O         | ST                  | _                                                          |

| RC7          | —                      |                                             | —                   | 3                               | I/O         | ST                  | 4                                                          |

| RC8          | —                      | —                                           | —                   | 4                               | I/O         | ST                  | _                                                          |

| RC9          |                        | - 40                                        | 20                  | 5                               | I/O         | ST                  | Time and an element all all in must                        |

| T1CK<br>T2CK | 9<br>PPS               | 12                                          | 10                  | 34                              |             | ST                  | Timer1 external clock input                                |

| T3CK         | PPS<br>PPS             | PPS<br>PPS                                  | PPS<br>PPS          | PPS<br>PPS                      |             | ST<br>ST            | Timer2 external clock input<br>Timer3 external clock input |

| T4CK         | PPS                    | PPS                                         | PPS                 | PPS                             | 1           | ST                  | Timer4 external clock input                                |

| T5CK         | PPS                    | PPS                                         | PPS                 | PPS                             |             | ST                  | Timer5 external clock input                                |

|              | PPS                    | PPS                                         | PPS                 | PPS                             |             | ST                  | UART1 clear to send                                        |

| U1RTS        | PPS                    | PPS                                         | PPS                 | PPS                             |             | 51                  |                                                            |

| U1RX         | PPS<br>PPS             | PPS<br>PPS                                  | PPS<br>PPS          | PPS<br>PPS                      | 0           | ST                  | UART1 ready to send<br>UART1 receive                       |

| U1TX         | PPS                    | PPS                                         | PPS                 | PPS                             | -           |                     |                                                            |

|              |                        |                                             |                     |                                 | 0           |                     | UART1 transmit                                             |

| U2CTS        | PPS                    | PPS                                         | PPS                 | PPS                             | I           | ST                  | UART2 clear to send                                        |

| U2RTS        | PPS                    | PPS                                         | PPS                 | PPS                             | 0           |                     | UART2 ready to send                                        |

| U2RX         | PPS                    | PPS                                         | PPS                 | PPS                             | I           | ST                  | UART2 receive                                              |

| U2TX         | PPS                    | PPS                                         | PPS                 | PPS                             | 0           |                     | UART2 transmit                                             |

| SCK1         | 22                     | 25                                          | 28                  | 14                              | I/O         | ST                  | Synchronous serial clock input/output for SPI1             |

| SDI1         | PPS                    | PPS                                         | PPS                 | PPS                             | I           | ST                  | SPI1 data in                                               |

| SDO1         | PPS                    | PPS                                         | PPS                 | PPS                             | 0           | _                   | SPI1 data out                                              |

| SS1          | PPS                    | PPS                                         | PPS                 | PPS                             | I/O         | ST                  | SPI1 slave synchronization or frame pulse I/O              |

| SCK2         | 23                     | 26                                          | 29                  | 15                              | I/O         | ST                  | Synchronous serial clock input/output for SPI2             |

| SDI2         | PPS                    | PPS                                         | PPS                 | PPS                             |             | ST                  | SPI2 data in                                               |

| SDO2         | PPS                    | PPS                                         | PPS                 | PPS                             | 0           | _                   | SPI2 data out                                              |

| SS2          | PPS                    | PPS                                         | PPS                 | PPS                             | I/O         | ST                  | SPI2 slave synchronization or frame pulse I/O              |

| SCL1         | 14                     | 17                                          | 18                  | 44                              | I/O         | ST                  | Synchronous serial clock input/output for<br>I2C1          |

|              | ST = Schm<br>TTL = TTL | MOS compa<br>itt Trigger in<br>input buffer | put with CN         | MOS levels                      |             | O = Outp<br>PPS = P | Analog input P = Power                                     |

####

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

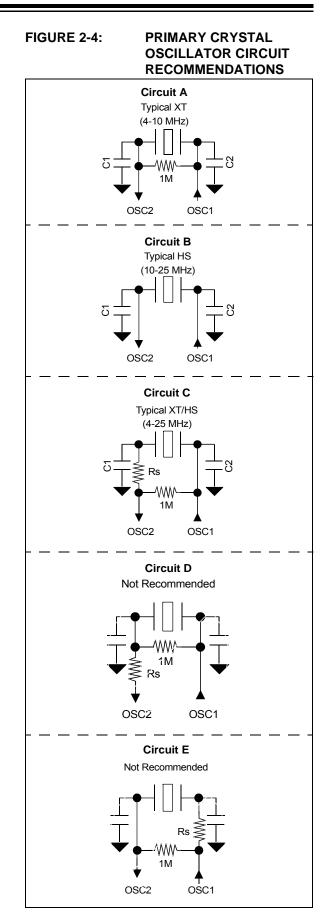

# 2.8.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

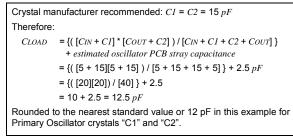

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32\_OSC2\_Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

#### EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator. The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

- Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to ~VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with ≤ 1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

#### 2.8.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849 "Basic PICmicro<sup>®</sup> Oscillator Design"

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | —                 |                  | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 | -                 | _                 | —                 |                  | _                |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |

| 15:8         |                   |                   |                   | BMXDU             | PBA<15:8>         |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | BMXDU             | PBA<7:0>          |                   |                  |                  |

### REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

# Legend:

| Legena.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 **BMXDUPBA<9:0>:** Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

NOTES:

# TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP (CONTINUED)

| ess                         |                                 | ē             |        |       |       |       | -      |       |      | Bi     | ts      |        |        |        |              |        |        |        | s          |

|-----------------------------|---------------------------------|---------------|--------|-------|-------|-------|--------|-------|------|--------|---------|--------|--------|--------|--------------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3         | 18/2   | 17/1   | 16/0   | All Resets |

| 3280                        | DCH2CPTR                        | 31:16         | —      | _     | _     | _     |        | _     |      | —      |         | _      | _      |        |              | _      | _      |        | 0000       |

| 5200                        | DONZOFIK                        | 15:0          |        |       |       |       |        |       |      | CHCPT  | R<15:0> |        |        |        |              |        |        |        | 0000       |

| 3290                        | DCH2DAT                         | 31:16         | _      | _     | —     | —     |        | _     |      | —      | _       | _      | —      | _      | —            | _      | _      |        | 0000       |

| 3290                        | DCHZDAI                         | 15:0          | _      |       | _     | _     |        | -     |      | -      |         |        |        | CHPDA  | AT<7:0>      |        |        |        | 0000       |

| 2240                        | DCH3CON                         | 31:16         | _      | _     | _     | _     | _      | _     | _    | _      | _       | _      | _      | _      | _            | _      | _      | _      | 0000       |

| 32A0                        | DCH3CON                         | 15:0          | CHBUSY | _     | _     | _     |        |       |      | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  | —            | CHEDET | CHPR   | l<1:0> | 0000       |

| 3280                        | DCH3ECON                        | 31:16         | —      |       |       |       |        |       |      |        |         |        |        | OOFF   |              |        |        |        |            |

| 5200                        |                                 | 15:0          |        |       |       | CHSIR | Q<7:0> |       |      |        | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN       | _      | _      | _      | FF00       |

| 32C0                        | DCH3INT                         | 31:16         | —      | —     | —     | —     | -      | _     | -    | —      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE       | CHCCIE | CHTAIE | CHERIE | 0000       |

| 0200                        |                                 | 15:0          | —      |       |       | _     | —      | _     | —    | —      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF       | CHCCIF | CHTAIF | CHERIF | 0000       |

| 32D0                        | DCH3SSA                         | 31:16<br>15:0 |        |       |       |       |        |       |      | CHSSA  | <31:0>  |        |        |        |              |        |        |        | 0000       |

|                             |                                 | 31:16         |        |       |       |       |        |       |      |        |         |        |        |        |              |        |        |        | 0000       |

| 32E0                        | DCH3DSA                         | 15:0          |        |       |       |       |        |       |      | CHDSA  | <31:0>  |        |        |        |              |        |        |        | 0000       |

| 0050                        | 00100017                        | 31:16         |        | _     |       |       | _      | _     | _    |        |         |        |        |        |              | _      |        | _      | 0000       |

| 32FU                        | DCH3SSIZ                        | 15:0          |        |       |       |       |        |       |      | CHSSIZ | 2<15:0> |        |        |        |              |        |        |        | 0000       |

| 2200                        | DCH3DSIZ                        | 31:16         | —      | —     | —     | —     | _      | —     | _    | —      | _       | —      | —      | —      | —            | _      | —      | _      | 0000       |

| 3300                        | DCH3D3IZ                        | 15:0          |        |       |       |       |        |       |      | CHDSIZ | 2<15:0> |        |        |        |              |        |        |        | 0000       |

| 3310                        | DCH3SPTR                        | 31:16         | —      | _     | _     | _     |        |       |      | _      | —       |        | _      |        | _            |        |        |        | 0000       |

| 3310                        | DOI IJOF I K                    | 15:0          |        |       |       |       |        |       |      | CHSPTF | ۲<15:0> |        |        |        |              |        |        |        | 0000       |

| 3320                        | DCH3DPTR                        | 31:16         | —      | —     | —     | —     | _      | _     | _    | —      | _       | _      | —      | —      | —            | _      | —      | _      | 0000       |

| 0020                        |                                 | 15:0          |        |       |       |       |        |       |      | CHDPT  | R<15:0> |        |        |        |              |        |        |        | 0000       |

| 3330                        | <b>DCH3CSIZ</b>                 | 31:16         | —      | _     | —     | —     | —      | —     | —    | —      | —       | —      | —      | —      | —            | —      | —      | —      | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      | CHCSIZ | 2<15:0> |        |        |        |              |        |        |        | 0000       |

| 3340                        | DCH3CPTR                        | 31:16         | _      | —     | —     | —     | _      | —     | _    | —      | _       | —      | —      | —      | —            | —      | —      | _      | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      | CHCPT  | ≺<15:0> |        |        |        |              |        |        |        | 0000       |

| 3350                        | DCH3DAT                         | 31:16         | —      | _     | —     | _     | _      | _     | —    | _      | _       | —      | —      | -      | —<br>T :7 0: | —      | —      | —      | 0000       |

| <u> </u>                    |                                 | 15:0          | —      | —     | —     | —     | —      | —     | —    | _      |         |        |        | CHPDA  | AT<7:0>      |        |        |        | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | _                 | —                 | —                 | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

#### **REGISTER 9-9:** DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER

# Legend:

| •                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31-24  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| bit 23     | CHSDIE: Channel Source Done Interrupt Enable bit<br>1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| bit 22     | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| DIL 22     | CHSHIE: Channel Source Half Empty Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| bit 21     | <b>CHDDIE:</b> Channel Destination Done Interrupt Enable bit<br>1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|            | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| bit 20     | CHDHIE: Channel Destination Half Full Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| bit 19     | <b>CHBCIE:</b> Channel Block Transfer Complete Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| bit 18     | CHCCIE: Channel Cell Transfer Complete Interrupt Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|            | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| bit 17     | CHTAIE: Channel Transfer Abort Interrupt Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|            | <ul><li>1 = Interrupt is enabled</li><li>0 = Interrupt is disabled</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| bit 16     | CHERIE: Channel Address Error Interrupt Enable bit<br>1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| bit 15-8   | 0 = Interrupt is disabled<br>Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| bit 7      | CHSDIF: Channel Source Done Interrupt Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|            | <ul> <li>1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)</li> <li>0 = No interrupt is pending</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| bit 6      | <b>CHSHIF:</b> Channel Source Half Empty Interrupt Flag bit<br>1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2)<br>0 = No interrupt is pending                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | )   |

| bit 5      | <b>CHDDIF:</b> Channel Destination Done Interrupt Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|            | <ul> <li>1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSI</li> <li>0 = No interrupt is pending</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IZ) |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| © 2011-201 | 16 Microchip Technology Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DS  |

| 2 2011 20  | is more any restricted from the second s | 20  |

DS60001168J-page 95

### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       | - /   |       |      |      | Bit  | s    |      |          |        |        |         |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |      | _    | —    | —        | —      | _      | —       | —      | 0000       |

| 5590                        | UIEF9                           | 15:0      |       |       | —     | —     | —     | —     | _    | —    |      |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5240                        | U1EP10                          | 31:16     | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | —        | _      | _      | —       | _      | 0000       |

| 53A0                        | UIEPIU                          | 15:0      |       | _     | _     | -     | _     | _     | _    | -    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 53BU                        | UIEPII                          | 15:0      | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEFIZ                          | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEF 13                         | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     |       | _     | _     |       | -     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | —        | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | —    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

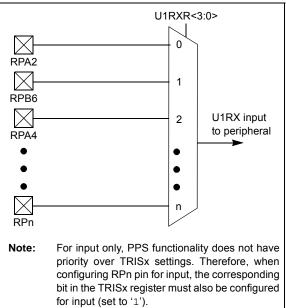

# 11.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin-count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only option.

The Peripheral Pin Select (PPS) configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

### 11.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

### 11.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digitalonly peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the PPS feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin.

Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.3.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

# 11.3.4 INPUT MAPPING

The inputs of the PPS options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 11-1, are used to configure peripheral input mapping (see Register 11-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 11-1.

For example, Figure 11-2 illustrates the remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT EXAMPLE FOR U1RX

#### TABLE 11-4: PORTB REGISTER MAP

| ess                         |                  |           |               |               |               |                              |               |               |              | Bits         |              |                             |              |              |              |              |              |              |            |

|-----------------------------|------------------|-----------|---------------|---------------|---------------|------------------------------|---------------|---------------|--------------|--------------|--------------|-----------------------------|--------------|--------------|--------------|--------------|--------------|--------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range | 31/15         | 30/14         | 29/13         | 28/12                        | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6                        | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All Resets |

|                             |                  | 31:16     | _             |               | —             |                              | _             | —             | —            | —            | _            | —                           | _            |              | —            | _            | —            | —            | 0000       |

| 0100                        | ANGLED           | 15:0      | ANSB15        | ANSB14        | ANSB13        | ANSB12 <sup>(2)</sup>        | —             | _             | —            | —            | _            | _                           | _            | _            | ANSB3        | ANSB2        | ANSB1        | ANSB0        | EOOF       |

| 6110                        | TRISB            | 31:16     | -             | _             | _             | 1                            | _             | —             | —            | —            | -            | —                           | -            | -            | —            | -            | _            | _            | 0000       |

| 0110                        | IIKIOD           | 15:0      | TRISB15       | TRISB14       | TRISB13       | TRISB12 <sup>(2)</sup>       | TRISB11       | TRISB10       | TRISB9       | TRISB8       | TRISB7       | TRISB6 <sup>(2)</sup>       | TRISB5       | TRISB4       | TRISB3       | TRISB2       | TRISB1       | TRISB0       | FFFF       |

| 6120                        | PORTB            | 31:16     | _             | _             | _             |                              | _             | _             | _            | _            |              | _                           | -            |              |              |              |              |              | 0000       |

| 0120                        | FORTB            | 15:0      | RB15          | RB14          | RB13          | RB12 <sup>(2)</sup>          | RB11          | RB10          | RB9          | RB8          | RB7          | RC6 <sup>(2)</sup>          | RB5          | RB4          | RB3          | RB2          | RB1          | RB0          | xxxx       |

| 6130                        | LATB             | 31:16     | -             | _             | _             |                              | -             | _             | _            | _            |              | _                           |              |              | _            |              | _            | _            | 0000       |

| 0150                        | LAID             | 15:0      | LATB15        | LATB14        | LATB13        | LATB12 <sup>(2)</sup>        | LATB11        | LATB10        | LATB9        | LATB8        | LATB7        | LATB6 <sup>(2)</sup>        | LATB5        | LATB4        | LATB3        | LATB2        | LATB1        | LATB0        | xxxx       |

| C1 4 0                      | 0000             | 31:16     |               | _             | —             | —                            | _             | _             | _            | —            | _            | _                           |              | —            | _            | —            | _            | —            | 0000       |

| 6140                        | ODCB             | 15:0      | ODCB15        | ODCB14        | ODCB13        | ODCB12 <sup>(2)</sup>        | ODCB11        | ODCB10        | ODCB9        | ODCB8        | ODCB7        | ODCB6                       | ODCB5        | ODCB4        | ODCB3        | ODCB2        | ODCB1        | ODCB0        | 0000       |

| 6150                        |                  | 31:16     | -             | —             | —             | -                            | _             | _             | _            | —            | -            | _                           | _            | _            | _            | -            | _            | —            | 0000       |

| 6150                        | CNPUB            | 15:0      | CNPUB15       | CNPUB14       | CNPUB13       | CNPUB12 <sup>(2)</sup>       | CNPUB11       | CNPUB10       | CNPUB9       | CNPUB8       | CNPUB7       | CNPUB6 <sup>(2)</sup>       | CNPUB5       | CNPUB4       | CNPUB3       | CNPUB2       | CNPUB1       | CNPUB0       | 0000       |

| 6160                        | CNPDB            | 31:16     | -             | _             | _             |                              | -             | _             | _            | _            |              | _                           |              |              | _            |              | _            | _            | 0000       |

| 0100                        | CNPDB            | 15:0      | CNPDB15       | CNPDB14       | CNPDB13       | CNPDB12 <sup>(2)</sup>       | CNPDB11       | CNPDB10       | CNPDB9       | CNPDB8       | CNPDB7       | CNPDB6 <sup>(2)</sup>       | CNPDB5       | CNPDB4       | CNPDB3       | CNPDB2       | CNPDB1       | CNPDB0       | 0000       |

| 6170                        | CNCONB           | 31:16     | -             | _             | _             |                              | -             | _             | _            | _            |              | _                           |              |              | _            |              | _            | _            | 0000       |

| 0170                        | CINCOINE         | 15:0      | ON            | _             | SIDL          |                              | -             | _             | _            | _            |              | _                           |              |              | _            |              | _            | _            | 0000       |

| C400                        |                  | 31:16     |               | —             | —             | -                            | —             | —             | —            | _            |              | —                           | Ι            | -            | —            | -            | —            | -            | 0000       |

| 6180                        | CNENB            | 15:0      | CNIEB15       | CNIEB14       | CNIEB13       | CNIEB11 <sup>(2)</sup>       | CNIEB11       | CNIEB10       | CNIEB9       | CNIEB8       | CNIEB7       | CNIEB6(2)                   | CNIEB5       | CNIEB4       | CNIEB3       | CNIEB2       | CNIEB1       | CNIEB0       | 0000       |

|                             |                  | 31:16     | —             |               | —             |                              | _             | —             | —            | —            | _            | —                           | _            | _            | —            | _            | _            | —            | 0000       |

| 6190                        | CNSTATB          | 15:0      | CN<br>STATB15 | CN<br>STATB14 | CN<br>STATB13 | CN<br>STATB12 <sup>(2)</sup> | CN<br>STATB11 | CN<br>STATB10 | CN<br>STATB9 | CN<br>STATB8 | CN<br>STATB7 | CN<br>STATB6 <sup>(2)</sup> | CN<br>STATB5 | CN<br>STATB4 | CN<br>STATB3 | CN<br>STATB2 | CN<br>STATB1 | CN<br>STATB0 | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This bit is not available on PIC32MX2XX devices. The reset value for the TRISB register when this bit is not available is 0x0000EFBF.

| TABL                        | .E 11-6:         | PEF       | RIPHER | AL PIN | SELEC | T INPU | T REGI | STER M | AP (CC | NTINU | ED)  |      |      |      |      |       |          |      |            |

|-----------------------------|------------------|-----------|--------|--------|-------|--------|--------|--------|--------|-------|------|------|------|------|------|-------|----------|------|------------|

| sse                         |                  |           |        |        |       |        |        |        |        | В     | its  |      |      |      |      |       |          |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15  | 30/14  | 29/13 | 28/12  | 27/11  | 26/10  | 25/9   | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1     | 16/0 | All Resets |

| 5454                        |                  | 31:16     | _      | —      | —     | —      | —      | —      | -      | —     | —    | -    | -    | -    | -    | -     | —        | —    | 0000       |