Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| )etails                   |                                                                                |

|---------------------------|--------------------------------------------------------------------------------|

|                           | B abb.                                                                         |

| roduct Status             | Active                                                                         |

| Core Processor            | MIPS32® M4K™                                                                   |

| Core Size                 | 32-Bit Single-Core                                                             |

| peed                      | 40MHz                                                                          |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| eripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| lumber of I/O             | 21                                                                             |

| rogram Memory Size        | 16KB (16K x 8)                                                                 |

| rogram Memory Type        | FLASH                                                                          |

| EPROM Size                | -                                                                              |

| AM Size                   | 4K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| ata Converters            | A/D 10x10b                                                                     |

| scillator Type            | Internal                                                                       |

| perating Temperature      | -40°C ~ 105°C (TA)                                                             |

| ounting Type              | Through Hole                                                                   |

| ackage / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| upplier Device Package    | 28-SPDIP                                                                       |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx110f016b-v-sp |

### TABLE 5: PIN NAMES FOR 28-PIN GENERAL PURPOSE DEVICES

28-PIN QFN (TOP VIEW)(1,2,3.4)

PIC32MX110F016B PIC32MX120F032B PIC32MX130F064B PIC32MX130F256B PIC32MX150F128B PIC32MX170F256B

28

1

| Pin # | Full Pin Name                         |

|-------|---------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0  |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1 |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2  |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3    |

| 5     | Vss                                   |

| 6     | OSC1/CLKI/RPA2/RA2                    |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3               |

| 8     | SOSCI/RPB4/RB4                        |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4        |

| 10    | VDD                                   |

| 11    | PGED3/RPB5/PMD7/RB5                   |

| 12    | PGEC3/RPB6/PMD6/RB6                   |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7          |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8         |

| Pin# | Full Pin Name                                  |

|------|------------------------------------------------|

| 15   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 16   | Vss                                            |

| 17   | VCAP                                           |

| 18   | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 19   | PGEC2/TMS/RPB11/PMD1/RB11                      |

| 20   | AN12/PMD0/RB12                                 |

| 21   | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 22   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 23   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 24   | AVss                                           |

| 25   | AVDD                                           |

| 26   | MCLR                                           |

| 27   | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 28   | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: Shaded pins are 5V tolerant.

### TABLE 8: PIN NAMES FOR 36-PIN USB DEVICES

**36-PIN VTLA (TOP VIEW)**(1,2,3,5)

PIC32MX210F016C PIC32MX220F032C PIC32MX230F064C PIC32MX250F128C

36

1

| Pin# | Full Pin Name                             |

|------|-------------------------------------------|

| 1    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3    | PGED4 <sup>(4)</sup> /AN6/RPC0/RC0        |

| 4    | PGEC4 <sup>(4)</sup> /AN7/RPC1/RC1        |

| 5    | VDD                                       |

| 6    | Vss                                       |

| 7    | OSC1/CLKI/RPA2/RA2                        |

| 8    | OSC2/CLKO/RPA3/PMA0/RA3                   |

| 9    | SOSCI/RPB4/RB4                            |

| 10   | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4            |

| 11   | AN12/RPC3/RC3                             |

| 12   | Vss                                       |

| 13   | VDD                                       |

| 14   | VDD                                       |

| 15   | TMS/RPB5/USBID/RB5                        |

| 16   | VBUS                                      |

| 17   | TDI/RPB7/CTED3/PMD5/INT0/RB7              |

| 18   | TCK/RPB8/SCL1/CTED10/PMD4/RB8             |

| Pin# | Full Pin Name                                    |

|------|--------------------------------------------------|

| 19   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 20   | RPC9/CTED7/RC9                                   |

| 21   | Vss                                              |

| 22   | VCAP                                             |

| 23   | VDD                                              |

| 24   | PGED2/RPB10/D+/CTED11/RB10                       |

| 25   | PGEC2/RPB11/D-/RB11                              |

| 26   | Vusb3v3                                          |

| 27   | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 28   | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 29   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 30   | AVss                                             |

| 31   | AVDD                                             |

| 32   | MCLR                                             |

| 33   | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 34   | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

| 35   | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        |

| 36   | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3** "**Peripheral Pin Select**" for restrictions.

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: This pin function is not available on PIC32MX210F016C and PIC32MX120F032C devices.

- 5: Shaded pins are 5V tolerant.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                   | Pin Nu                            | mber <sup>(1)</sup>               | •                 |             |                |                                                                         |  |  |

|----------|-------------------|-----------------------------------|-----------------------------------|-------------------|-------------|----------------|-------------------------------------------------------------------------|--|--|

| Pin Name | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin QFN/<br>VTLA TQFP/<br>VTLA |                   | Pin<br>Type | Buffer<br>Type | Description                                                             |  |  |

| USBID    | 11 <sup>(3)</sup> | 14 <sup>(3)</sup>                 | 15 <sup>(3)</sup>                 | 41(3)             | ı           | ST             | USB OTG ID detect                                                       |  |  |

| CTED1    | 27                | 2                                 | 33                                | 19                | I           | ST             | CTMU External Edge Input                                                |  |  |

| CTED2    | 28                | 3                                 | 34                                | 20                | I           | ST             | 1                                                                       |  |  |

| CTED3    | 13                | 16                                | 17                                | 43                | I           | ST             | 1                                                                       |  |  |

| CTED4    | 15                | 18                                | 19                                | 1                 | I           | ST             | 1                                                                       |  |  |

| CTED5    | 22                | 25                                | 28                                | 14                | I           | ST             | 1                                                                       |  |  |

| CTED6    | 23                | 26                                | 29                                | 15                | I           | ST             | 1                                                                       |  |  |

| CTED7    | _                 | _                                 | 20                                | 5                 | I           | ST             | 1                                                                       |  |  |

| CTED8    | _                 | _                                 | -                                 | 13                | I           | ST             | 1                                                                       |  |  |

| CTED9    | 9                 | 12                                | 10                                | 34                | I           | ST             | 1                                                                       |  |  |

| CTED10   | 14                | 17                                | 18                                | 44                | I           | ST             | 1                                                                       |  |  |

| CTED11   | 18                | 21                                | 24                                | 8                 | I           | ST             | 1                                                                       |  |  |

| CTED12   | 2                 | 5                                 | 36                                | 22                | I           | ST             | 1                                                                       |  |  |

| CTED13   | 3                 | 6                                 | 1                                 | 23                | I           | ST             | 1                                                                       |  |  |

| CTPLS    | 21                | 24                                | 27                                | 11                | 0           | _              | CTMU Pulse Output                                                       |  |  |

| PGED1    | 1                 | 4                                 | 35                                | 21                | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 1          |  |  |

| PGEC1    | 2                 | 5                                 | 36                                | 22                | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 1 |  |  |

| PGED2    | 18                | 21                                | 24                                | 8                 | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 2          |  |  |

| PGEC2    | 19                | 22                                | 25                                | 9                 | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 2 |  |  |

| PGED3    | 11 <sup>(2)</sup> | 14 <sup>(2)</sup>                 | 15 <sup>(2)</sup>                 | 41 <sup>(2)</sup> | I/O         | ST             | Data I/O pin for Programming/Debugging                                  |  |  |

| PGED3    | 27 <sup>(3)</sup> | 2 <sup>(3)</sup>                  | 33(3)                             | 19 <sup>(3)</sup> | 1/0         | 31             | Communication Channel 3                                                 |  |  |

| DCEC2    | 12 <sup>(2)</sup> | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup>                 | 42 <sup>(2)</sup> |             | ST             | Clock input pin for Programming/                                        |  |  |

| PGEC3    | 28 <sup>(3)</sup> | 3(3)                              | 34 <sup>(3)</sup>                 | 20 <sup>(3)</sup> | 1 '         | 31             | Debugging Communication Channel 3                                       |  |  |

| PGED4    | _                 | _                                 | 3                                 | 12                | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 4          |  |  |

| PGEC4    | _                 | _                                 | 4                                 | 13                | I           | ST             | Clock input pin for Programming/<br>Debugging Communication Channel 4   |  |  |

**Legend:** CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input O = Output P = Power I = Input

TTL = TTL input buffer

PPS = Peripheral Pin Select

--=N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

**3:** Pin number for PIC32MX2XX devices only.

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

| F         | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Exception | Description                                                                                                                             |

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error. Fetch reference to protected address.                                                                    |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a Corextend instruction when Corextend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error. Load reference to protected address.                                                                      |

| AdES      | Store address alignment error. Store to protected address.                                                                              |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

## 3.3 Power Management

The MIPS M4K processor core offers many power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

# 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see **Section 26.0** "Power-Saving Features".

## 3.4 EJTAG Debug Support

The MIPS M4K processor core provides an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| Interrupt Source <sup>(1)</sup>     | IRQ | Vector |          | Persistent |             |              |           |  |  |  |

|-------------------------------------|-----|--------|----------|------------|-------------|--------------|-----------|--|--|--|

| interrupt Source(*)                 | #   | #      | Flag     | Enable     | Priority    | Sub-priority | Interrupt |  |  |  |

| Highest Natural Order Priority      |     |        |          |            |             |              |           |  |  |  |

| CT – Core Timer Interrupt           | 0   | 0      | IFS0<0>  | IEC0<0>    | IPC0<4:2>   | IPC0<1:0>    | No        |  |  |  |

| CS0 – Core Software Interrupt 0     | 1   | 1      | IFS0<1>  | IEC0<1>    | IPC0<12:10> | IPC0<9:8>    | No        |  |  |  |

| CS1 – Core Software Interrupt 1     | 2   | 2      | IFS0<2>  | IEC0<2>    | IPC0<20:18> | IPC0<17:16>  | No        |  |  |  |

| INT0 – External Interrupt           | 3   | 3      | IFS0<3>  | IEC0<3>    | IPC0<28:26> | IPC0<25:24>  | No        |  |  |  |

| T1 – Timer1                         | 4   | 4      | IFS0<4>  | IEC0<4>    | IPC1<4:2>   | IPC1<1:0>    | No        |  |  |  |

| IC1E - Input Capture 1 Error        | 5   | 5      | IFS0<5>  | IEC0<5>    | IPC1<12:10> | IPC1<9:8>    | Yes       |  |  |  |

| IC1 – Input Capture 1               | 6   | 5      | IFS0<6>  | IEC0<6>    | IPC1<12:10> | IPC1<9:8>    | Yes       |  |  |  |

| OC1 – Output Compare 1              | 7   | 6      | IFS0<7>  | IEC0<7>    | IPC1<20:18> | IPC1<17:16>  | No        |  |  |  |

| INT1 – External Interrupt 1         | 8   | 7      | IFS0<8>  | IEC0<8>    | IPC1<28:26> | IPC1<25:24>  | No        |  |  |  |

| T2 – Timer2                         | 9   | 8      | IFS0<9>  | IEC0<9>    | IPC2<4:2>   | IPC2<1:0>    | No        |  |  |  |

| IC2E – Input Capture 2              | 10  | 9      | IFS0<10> | IEC0<10>   | IPC2<12:10> | IPC2<9:8>    | Yes       |  |  |  |

| IC2 – Input Capture 2               | 11  | 9      | IFS0<11> | IEC0<11>   | IPC2<12:10> | IPC2<9:8>    | Yes       |  |  |  |

| OC2 – Output Compare 2              | 12  | 10     | IFS0<12> | IEC0<12>   | IPC2<20:18> | IPC2<17:16>  | No        |  |  |  |

| INT2 – External Interrupt 2         | 13  | 11     | IFS0<13> | IEC0<13>   | IPC2<28:26> | IPC2<25:24>  | No        |  |  |  |

| T3 – Timer3                         | 14  | 12     | IFS0<14> | IEC0<14>   | IPC3<4:2>   | IPC3<1:0>    | No        |  |  |  |

| IC3E - Input Capture 3              | 15  | 13     | IFS0<15> | IEC0<15>   | IPC3<12:10> | IPC3<9:8>    | Yes       |  |  |  |

| IC3 – Input Capture 3               | 16  | 13     | IFS0<16> | IEC0<16>   | IPC3<12:10> | IPC3<9:8>    | Yes       |  |  |  |

| OC3 – Output Compare 3              | 17  | 14     | IFS0<17> | IEC0<17>   | IPC3<20:18> | IPC3<17:16>  | No        |  |  |  |

| INT3 – External Interrupt 3         | 18  | 15     | IFS0<18> | IEC0<18>   | IPC3<28:26> | IPC3<25:24>  | No        |  |  |  |

| T4 – Timer4                         | 19  | 16     | IFS0<19> | IEC0<19>   | IPC4<4:2>   | IPC4<1:0>    | No        |  |  |  |

| IC4E – Input Capture 4 Error        | 20  | 17     | IFS0<20> | IEC0<20>   | IPC4<12:10> | IPC4<9:8>    | Yes       |  |  |  |

| IC4 – Input Capture 4               | 21  | 17     | IFS0<21> | IEC0<21>   | IPC4<12:10> | IPC4<9:8>    | Yes       |  |  |  |

| OC4 – Output Compare 4              | 22  | 18     | IFS0<22> | IEC0<22>   | IPC4<20:18> | IPC4<17:16>  | No        |  |  |  |

| INT4 – External Interrupt 4         | 23  | 19     | IFS0<23> | IEC0<23>   | IPC4<28:26> | IPC4<25:24>  | No        |  |  |  |

| T5 – Timer5                         | 24  | 20     | IFS0<24> | IEC0<24>   | IPC5<4:2>   | IPC5<1:0>    | No        |  |  |  |

| IC5E – Input Capture 5 Error        | 25  | 21     | IFS0<25> | IEC0<25>   | IPC5<12:10> | IPC5<9:8>    | Yes       |  |  |  |

| IC5 – Input Capture 5               | 26  | 21     | IFS0<26> | IEC0<26>   | IPC5<12:10> | IPC5<9:8>    | Yes       |  |  |  |

| OC5 – Output Compare 5              | 27  | 22     | IFS0<27> | IEC0<27>   | IPC5<20:18> | IPC5<17:16>  | No        |  |  |  |

| AD1 – ADC1 Convert done             | 28  | 23     | IFS0<28> | IEC0<28>   | IPC5<28:26> | IPC5<25:24>  | Yes       |  |  |  |

| FSCM – Fail-Safe Clock Monitor      | 29  | 24     | IFS0<29> | IEC0<29>   | IPC6<4:2>   | IPC6<1:0>    | No        |  |  |  |

| RTCC – Real-Time Clock and Calendar | 30  | 25     | IFS0<30> | IEC0<30>   | IPC6<12:10> | IPC6<9:8>    | No        |  |  |  |

| FCE – Flash Control Event           | 31  | 26     | IFS0<31> | IEC0<31>   | IPC6<20:18> | IPC6<17:16>  | No        |  |  |  |

| CMP1 – Comparator Interrupt         | 32  | 27     | IFS1<0>  | IEC1<0>    | IPC6<28:26> | IPC6<25:24>  | No        |  |  |  |

| CMP2 – Comparator Interrupt         | 33  | 28     | IFS1<1>  | IEC1<1>    | IPC7<4:2>   | IPC7<1:0>    | No        |  |  |  |

| CMP3 – Comparator Interrupt         | 34  | 29     | IFS1<2>  | IEC1<2>    | IPC7<12:10> | IPC7<9:8>    | No        |  |  |  |

| USB – USB Interrupts                | 35  | 30     | IFS1<3>  | IEC1<3>    | IPC7<20:18> | IPC7<17:16>  | Yes       |  |  |  |

| SPI1E – SPI1 Fault                  | 36  | 31     | IFS1<4>  | IEC1<4>    | IPC7<28:26> | IPC7<25:24>  | Yes       |  |  |  |

| SPI1RX – SPI1 Receive Done          | 37  | 31     | IFS1<5>  | IEC1<5>    | IPC7<28:26> | IPC7<25:24>  | Yes       |  |  |  |

| SPI1TX – SPI1 Transfer Done         | 38  | 31     | IFS1<6>  | IEC1<6>    | IPC7<28:26> | IPC7<25:24>  | Yes       |  |  |  |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/36/44-Pin General Purpose Family Features" and TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features" for the lists of available peripherals.

| SS                          |                                 | _             |        | Bits  |            |       |       |       |      |         |                      |        |            |        |         |        |                                         |              |            |

|-----------------------------|---------------------------------|---------------|--------|-------|------------|-------|-------|-------|------|---------|----------------------|--------|------------|--------|---------|--------|-----------------------------------------|--------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13      | 28/12 | 27/11 | 26/10 | 25/9 | 24/8    | 23/7                 | 22/6   | 21/5       | 20/4   | 19/3    | 18/2   | 17/1                                    | 16/0         | All Resets |

| 3170                        | DCH1SSIZ                        | 31:16         | _      | I     | _          | I     | ı     | _     | _    | _       | _                    | ı      | I          | _      | _       | _      | -                                       | _            | 0000       |

| 3170                        | DCHTSSIZ                        | 15:0          |        |       |            |       |       |       |      | CHSSIZ  | <b>'&lt;15:0&gt;</b> |        |            |        |         |        |                                         |              | 0000       |

| 3180                        | DCH1DSIZ                        | 31:16         | _      | _     | _          | _     | _     | _     | _    | _       | _                    | _      | _          | _      |         | _      | _                                       | _            | 0000       |

| 3100                        | DOITIDGIZ                       | 15:0          |        |       |            |       |       |       |      | CHDSIZ  | <u>′</u> <15:0>      |        |            |        |         |        |                                         |              | 0000       |

| 3190                        | DCH1SPTR                        | 31:16         | _      | _     | _          | _     | _     | _     | _    | _       | _                    | _      | _          | _      |         | _      | _                                       | _            | 0000       |

|                             |                                 | 15:0          |        |       | 1          |       |       |       | 1    | CHSPTF  | R<15:0>              |        |            |        |         | 1      |                                         | ı            | 0000       |

| 31A0                        | DCH1DPTR                        | 31:16         | _      | _     | _          | _     | _     | _     | _    |         | _                    | _      | _          | _      | _       | _      | _                                       | _            | 0000       |

|                             |                                 | 15:0          |        |       |            |       |       |       |      | CHDPT   | R<15:0>              |        |            |        |         |        |                                         | 1            | 0000       |

| 31B0                        | DCH1CSIZ                        | 31:16         | _      | _     | _          | _     | _     | _     | _    |         |                      | _      | _          | _      |         | _      | _                                       | _            | 0000       |

|                             |                                 | 15:0          |        |       |            |       |       |       |      | CHCSIZ  | <u>′</u> <15:0>      |        |            |        |         |        |                                         |              | 0000       |

| 31C0                        | DCH1CPTR                        | 31:16         | _      | _     | _          |       |       | _     | _    | - CHODI | —<br>-               |        |            | _      |         | _      | _                                       | _            | 0000       |

|                             |                                 | 15:0          |        |       |            |       |       |       |      | CHCPTF  |                      |        |            |        |         |        |                                         |              | 0000       |

| 31D0                        | DCH1DAT                         | 31:16<br>15:0 | _      |       | _          | _     |       |       | _    | _       | _                    | _      |            | CHPDA  |         | _      | _                                       | _            | 0000       |

|                             |                                 | 31:16         | _      |       | _          |       |       | _     | _    | _       |                      |        |            | СПРОА  | 11<7.0> |        |                                         |              | _          |

| 31E0                        | DCH2CON                         |               | CHBUSY |       |            |       |       | _     | _    | CHCHNS  | CHEN                 | CHAED  | CHCHN      | CHAEN  |         | CHEDET | CHDE                                    | —<br>!I<1:0> | 0000       |

|                             |                                 | 31:16         | —      |       |            |       |       |       |      | _       | CHLIN                | CHALD  | CHOIN      | CHAIR  |         | CHEDET | Ciliii                                  | .1 < 1.0 >   | 0000       |

| 31F0                        | DCH2ECON                        | 15:0          |        |       |            | CHSIR |       |       |      |         | CFORCE               | CABORT | PATEN      | SIRQEN | AIRQEN  | _      | _                                       | _            | FF00       |

|                             |                                 | 31:16         | _      | _     | _          | _     | _     | _     | _    | _       | CHSDIE               | CHSHIE | CHDDIE     | CHDHIE | CHBCIE  | CHCCIE | CHTAIE                                  | CHERIE       | 0000       |

| 3200                        | DCH2INT                         | 15:0          | _      |       | _          |       |       |       | _    | _       | CHSDIF               | CHSHIF | CHDDIF     | CHDHIF | CHBCIF  | CHCCIF | CHTAIF                                  | CHERIF       | 0000       |

|                             |                                 | 31:16         | ļ      |       |            |       |       |       |      |         |                      |        | ********** |        |         |        | *************************************** |              | 0000       |

| 3210                        | DCH2SSA                         | 15:0          |        |       |            |       |       |       |      | CHSSA   | <31:0>               |        |            |        |         |        |                                         |              | 0000       |

| 2000                        | D.0110D.0.4                     | 31:16         |        |       |            |       |       |       |      | 011004  | 212                  |        |            |        |         |        |                                         |              | 0000       |

| 3220                        | DCH2DSA                         | 15:0          |        |       |            |       |       |       |      | CHDSA   | <31:0>               |        |            |        |         |        |                                         |              | 0000       |

| 2220                        | DOLINGOIZ                       | 31:16         | _      | _     | _          | _     | _     | _     | _    | _       | _                    | _      | _          | _      | _       | _      | _                                       | _            | 0000       |

| 3230                        | DCH2SSIZ                        | 15:0          | •      |       | •          |       |       |       | •    | CHSSIZ  | <b>'&lt;15:0&gt;</b> |        |            |        |         | •      |                                         |              | 0000       |

| 3240                        | DCH2DSIZ                        | 31:16         | _      |       | _          |       | -     | _     | _    | _       | _                    | -      |            | _      | _       | _      | _                                       | _            | 0000       |

| 3240                        | DCHZDSIZ                        | 15:0          |        |       |            |       |       |       |      | CHDSIZ  | <b>'&lt;15:0&gt;</b> |        |            |        |         |        |                                         |              | 0000       |

| 3250                        | DCH2SPTR                        | 31:16         | _      | _     | _          | _     | _     |       | _    | _       | _                    | _      | _          | _      | _       | _      | _                                       | _            | 0000       |

| 3230                        |                                 | 15:0          |        |       |            |       |       |       |      | CHSPTF  | R<15:0>              |        |            |        |         |        |                                         |              | 0000       |

| 3260                        | DCH2DPTR                        | 31:16         | _      | -     | _          | -     | _     | _     | _    | _       | _                    | _      | -          | _      | _       | _      | _                                       | _            | 0000       |

| 3200                        |                                 | 15:0          |        |       |            |       |       |       |      | CHDPT   | R<15:0>              |        |            |        |         |        |                                         |              | 0000       |

| 3270                        | DCH2CSIZ                        | 31:16         | _      | _     | _          | _     | _     | _     | _    | _       | _                    | _      | _          | _      | _       | _      | _                                       | _            | 0000       |

|                             |                                 | 15:0          |        |       | unimplomor |       |       |       |      | CHCSIZ  | <b>2</b> <15:0>      |        |            |        |         |        |                                         |              | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

## REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

- bit 6 CRCAPP: CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 CRCTYP: CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

### REGISTER 10-5: U1PWRC: USB POWER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 31.24        | _                 | -                 | -                 | _                 | _                      | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 13.6         | _                 | -                 | -                 | _                 | _                      | _                 | _                | _                |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0            |

| 7.0          | UACTPND           | -                 | 1                 | USLPGRD           | USBBUSY <sup>(1)</sup> | -                 | USUSPEND         | USBPWR           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 **UACTPND:** USB Activity Pending bit

1 = USB bus activity has been detected; however, an interrupt is pending, which has yet to be generated

0 = An interrupt is not pending

bit 6-5 **Unimplemented:** Read as '0'

bit 4 USLPGRD: USB Sleep Entry Guard bit

1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

0 = USB module does not block Sleep entry

bit 3 **USBBUSY:** USB Module Busy bit<sup>(1)</sup>

1 = USB module is active or disabled, but not ready to be enabled

0 = USB module is not active and is ready to be enabled

bit 2 Unimplemented: Read as '0'

bit 1 USUSPEND: USB Suspend Mode bit

1 = USB module is placed in Suspend mode

(The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

0 = USB module operates normally

bit 0 USBPWR: USB Operation Enable bit

1 = USB module is turned on

0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

**Note 1:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

TABLE 11-1: INPUT PIN SELECTION

| Peripheral Pin | [pin name]R SFR | [pin name]R bits | [pin name]R Value to<br>RPn Pin Selection                                              |

|----------------|-----------------|------------------|----------------------------------------------------------------------------------------|

| INT4           | INT4R           | INT4R<3:0>       | 0000 = RPA0<br>0001 = RPB3                                                             |

| T2CK           | T2CKR           | T2CKR<3:0>       | 0010 = RPB4<br>0011 = RPB15<br>0100 = RPB7                                             |

| IC4            | IC4R            | IC4R<3:0>        | 0101 = RPC7 <sup>(2)</sup><br>0110 = RPC0 <sup>(1)</sup><br>0111 = RPC5 <sup>(2)</sup> |

| SS1            | SS1R            | SS1R<3:0>        | 1000 = Reserved                                                                        |

| REFCLKI        | REFCLKIR        | REFCLKIR<3:0>    | 1111 = Reserved                                                                        |

| INT3           | INT3R           | INT3R<3:0>       | 0000 = RPA1<br>0001 = RPB5                                                             |

| T3CK           | T3CKR           | T3CKR<3:0>       | 0010 = RPB1<br>0011 = RPB11                                                            |

| IC3            | IC3R            | IC3R<3:0>        | 0100 = RPB8<br>0101 = RPA8 <sup>(2)</sup>                                              |

| U1CTS          | U1CTSR          | U1CTSR<3:0>      | 0110 = RPC8 <sup>(2)</sup><br>0111 = RPA9 <sup>(2)</sup>                               |

| U2RX           | U2RXR           | U2RXR<3:0>       | 1000 = Reserved                                                                        |

| SDI1           | SDI1R           | SDI1R<3:0>       | 1111 = Reserved                                                                        |

| INT2           | INT2R           | INT2R<3:0>       | 0000 = RPA2                                                                            |

| T4CK           | T4CKR           | T4CKR<3:0>       | 0001 = RPB6<br>0010 = RPA4                                                             |

| IC1            | IC1R            | IC1R<3:0>        | 0011 = RPB13<br>0100 = RPB2                                                            |

| IC5            | IC5R            | IC5R<3:0>        | 0101 = RPC6 <sup>(2)</sup>                                                             |

| U1RX           | U1RXR           | U1RXR<3:0>       | 0110 = RPC1 <sup>(1)</sup><br>0111 = RPC3 <sup>(1)</sup>                               |

| U2CTS          | U2CTSR          | U2CTSR<3:0>      | 1000 = Reserved                                                                        |

| SDI2           | SDI2R           | SDI2R<3:0>       | <b></b>                                                                                |

| OCFB           | OCFBR           | OCFBR<3:0>       | • 1111 = Reserved                                                                      |

| INT1           | INT1R           | INT1R<3:0>       | 0000 = RPA3<br>0001 = RPB14                                                            |

| T5CK           | T5CKR           | T5CKR<3:0>       | 0010 = RPB0<br>0011 = RPB10<br>0100 = RPB9                                             |

| IC2            | IC2R            | IC2R<3:0>        | 0101 = RPC9 <sup>(1)</sup><br>0110 = RPC2 <sup>(2)</sup><br>0111 = RPC4 <sup>(2)</sup> |

| SS2            | SS2R            | SS2R<3:0>        | 1000 = Reserved                                                                        |

| OCFA           | OCFAR           | OCFAR<3:0>       | 1111 = Reserved                                                                        |

Note 1: This pin is not available on 28-pin devices.

<sup>2:</sup> This pin is only available on 44-pin devices.

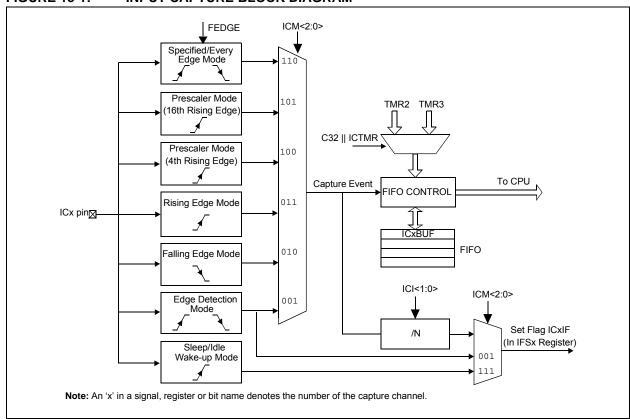

### 15.0 INPUT CAPTURE

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 15. "Input Capture"** (DS60001122), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- · Simple capture event modes:

- Capture timer value on every rising and falling edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- · Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values (interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled)

- Input capture can also be used to provide additional sources of external interrupts

Figure 15-1 illustrates a general block diagram of the Input Capture module.

FIGURE 15-1: INPUT CAPTURE BLOCK DIAGRAM

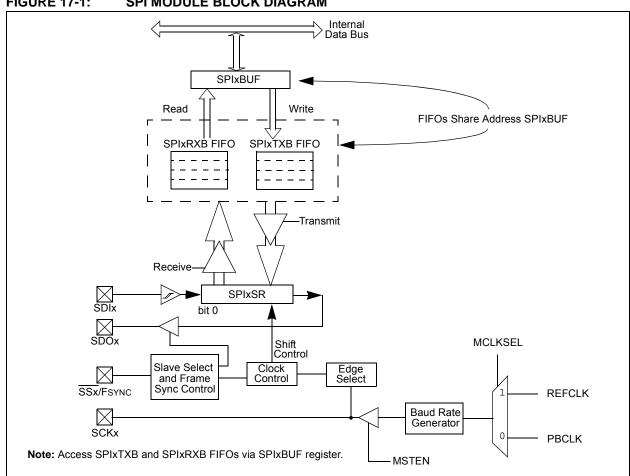

### SERIAL PERIPHERAL 17.0 **INTERFACE (SPI)**

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial **Peripheral** Interface (SPI)" (DS60001106), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontrollers. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters (ADC), etc. The PIC32 SPI module is compatible with Motorola® SPI and SIOP interfaces.

Some of the key features of the SPI module are:

- Master mode and Slave mode support

- · Four clock formats

- Enhanced Framed SPI protocol support

- · User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

- FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- · Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- · Operation during Sleep and Idle modes

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

**FIGURE 17-1:** SPI MODULE BLOCK DIAGRAM

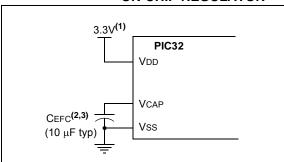

## 27.3 On-Chip Voltage Regulator

All PIC32MX1XX/2XX 28/36/44-pin Family devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX1XX/2XX 28/36/44-pin Family family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 30.1** "**DC Characteristics**".

**Note:** It is important that the low-ESR capacitor is placed as close as possible to the VCAP pin.

### 27.3.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

### 27.3.2 ON-CHIP REGULATOR AND BOR

PIC32MX1XX/2XX 28/36/44-pin Family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 30.1** "DC Characteristics".

FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

- Note 1: These are typical operating voltages. Refer to Section 30.1 "DC Characteristics" for the full operating ranges of VDD.

- **2:** It is important that the low-ESR capacitor is placed as close as possible to the VCAP pin.

- **3:** The typical voltage on the VCAP pin is 1.8V.

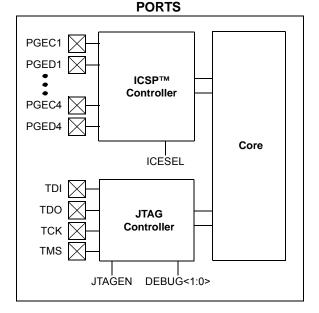

## 27.4 Programming and Diagnostics

PIC32MX1XX/2XX 28/36/44-pin Family devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming™ (ICSP™) interfaces

- · Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

Figure 27-2 illustrates a block diagram of the programming, debugging, and trace ports.

FIGURE 27-2: BLOCK DIAGRAM OF PROGRAMMING, DEBUGGING AND TRACE

### 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® X IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>TM</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- · In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- · Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- · Third-party development tools

# 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users

### Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

Project-Based Workspaces:

- · Multiple projects

- · Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- · Built-in support for Bugzilla issue tracker

### 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming™ (ICSP™).

### 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

### 30.1 DC Characteristics

TABLE 30-1: OPERATING MIPS VS. VOLTAGE

|                |                           | Temp. Range     | Max. Frequency                     |

|----------------|---------------------------|-----------------|------------------------------------|

| Characteristic | (in Volts) <sup>(1)</sup> | (in °C)         | PIC32MX1XX/2XX 28/36/44-pin Family |

| DC5            | 2.3-3.6V                  | -40°C to +85°C  | 40 MHz                             |

| DC5b           | 2.3-3.6V                  | -40°C to +105°C | 40 MHz                             |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 30-11 for BOR values.

## TABLE 30-2: THERMAL OPERATING CONDITIONS

| Rating                                                                         | Symbol | Min.        | Typical     | Max. | Unit |

|--------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| Industrial Temperature Devices                                                 |        |             |             |      |      |

| Operating Junction Temperature Range                                           | TJ     | -40         | _           | +125 | °C   |

| Operating Ambient Temperature Range                                            | TA     | -40         | _           | +85  | °C   |

| V-temp Temperature Devices                                                     |        |             |             |      |      |

| Operating Junction Temperature Range                                           | TJ     | -40         | _           | +140 | °C   |

| Operating Ambient Temperature Range                                            | TA     | -40         | _           | +105 | °C   |

| Power Dissipation: Internal Chip Power Dissipation: PINT = VDD x (IDD – S IOH) | PD     | PINT + PI/O |             |      | W    |

| I/O Pin Power Dissipation:<br>I/O = S (({VDD – VOн} x IOн) + S (VoL x IOL))    |        |             |             |      |      |

| Maximum Allowed Power Dissipation                                              | PDMAX  | (           | TJ – TA)/θJ | Α    | W    |

### TABLE 30-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristics                          | Symbol | Typical | Max. | Unit | Notes |

|------------------------------------------|--------|---------|------|------|-------|

| Package Thermal Resistance, 28-pin SSOP  | θЈА    | 71      | _    | °C/W | 1     |

| Package Thermal Resistance, 28-pin SOIC  | θЈА    | 50      |      | °C/W | 1     |

| Package Thermal Resistance, 28-pin SPDIP | θЈА    | 42      |      | °C/W | 1     |

| Package Thermal Resistance, 28-pin QFN   | θЈА    | 35      | _    | °C/W | 1     |

| Package Thermal Resistance, 36-pin VTLA  | θЈА    | 31      | _    | °C/W | 1     |

| Package Thermal Resistance, 44-pin QFN   | θЈА    | 32      | _    | °C/W | 1     |

| Package Thermal Resistance, 44-pin TQFP  | θЈА    | 45      | _    | °C/W | 1     |

| Package Thermal Resistance, 44-pin VTLA  | θЈА    | 30      | _    | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

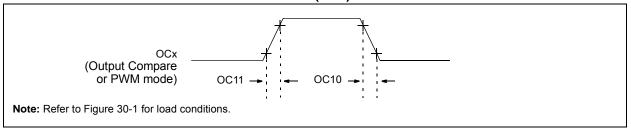

## FIGURE 30-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

### TABLE 30-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                        |      |       |                    |

|--------------------|--------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup> | Min.                                                                                                                                                                                                                                           | Typical <sup>(2)</sup> | Max. | Units | Conditions         |

| OC10               | TccF   | OCx Output Fall Time           | _                                                                                                                                                                                                                                              | _                      |      | ns    | See parameter DO32 |

| OC11               | TccR   | OCx Output Rise Time           |                                                                                                                                                                                                                                                | _                      | _    | ns    | See parameter DO31 |

- **Note 1:** These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

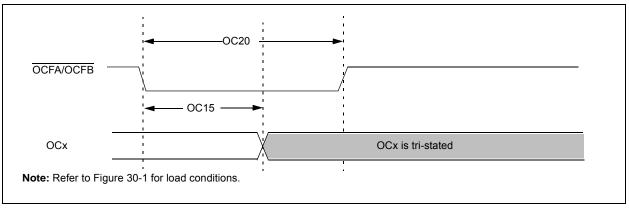

### FIGURE 30-9: OCx/PWM MODULE TIMING CHARACTERISTICS

### TABLE 30-27: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                        |     |       |            |  |

|--------------------|--------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-------|------------|--|

| Param<br>No.       | Symbol | Characteristics <sup>(1)</sup> | Min                                                                                                                                                                                                                                             | Typical <sup>(2)</sup> | Max | Units | Conditions |  |

| OC15               | TFD    | Fault Input to PWM I/O Change  | _                                                                                                                                                                                                                                               | _                      | 50  | ns    | _          |  |

| OC20               | TFLT   | Fault Input Pulse Width        | 50                                                                                                                                                                                                                                              | _                      | _   | ns    | _          |  |

- **Note 1:** These parameters are characterized, but not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

TABLE 31-8: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |          |                                                 | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |   |    |       |            |

|--------------------|----------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|-------|------------|

| Param.<br>No.      | Symbol   | Characteristics                                 | Min. Typ. Max. Unit                                                                                                                                                                                                                            |   |    | Units | Conditions |

| MSP70              | TscL     | SCKx Input Low Time (Note 1,2)                  | Tsck/2                                                                                                                                                                                                                                         | _ | _  | ns    | _          |

| MSP71              | TscH     | SCKx Input High Time (Note 1,2)                 | Tsck/2                                                                                                                                                                                                                                         | _ | _  | ns    |            |

| MSP51              | TssH2DoZ | SSx ↑ to SDOx Output<br>High-Impedance (Note 2) | 5                                                                                                                                                                                                                                              | _ | 25 | ns    | _          |

Note 1: These parameters are characterized, but not tested in manufacturing.

TABLE 31-9: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                 | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial |   |            |    |   |

|--------------------|--------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|----|---|

| Param.<br>No.      | Symbol | Characteristics                 | Min. Typical Max. Units                                                                                                                                                |   | Conditions |    |   |

| SP70               | TscL   | SCKx Input Low Time (Note 1,2)  | Tsck/2                                                                                                                                                                 | _ | _          | ns | _ |

| SP71               | TscH   | SCKx Input High Time (Note 1,2) | Tsck/2                                                                                                                                                                 | _ | _          | ns | _ |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

<sup>2:</sup> The minimum clock period for SCKx is 40 ns.

<sup>2:</sup> The minimum clock period for SCKx is 40 ns.

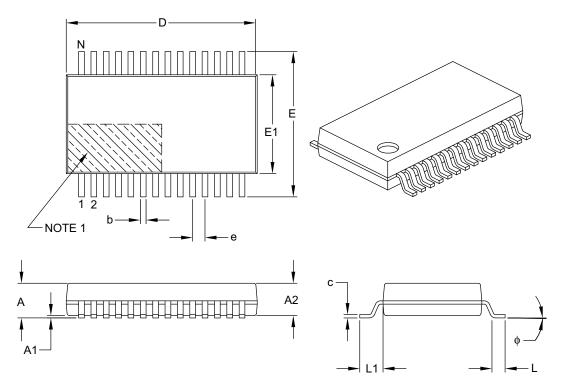

## 33.2 Package Details

This section provides the technical details of the packages.

## 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units      |          |          | 3     |  |  |

|--------------------------|------------|----------|----------|-------|--|--|

| Dimens                   | ion Limits | MIN      | NOM      | MAX   |  |  |

| Number of Pins           | N          | 28       |          |       |  |  |

| Pitch                    | е          |          | 0.65 BSC |       |  |  |

| Overall Height           | Α          | 2.0      |          |       |  |  |

| Molded Package Thickness | A2         | 1.65     | 1.75     | 1.85  |  |  |

| Standoff                 | A1         | 0.05     | _        | _     |  |  |

| Overall Width            | Е          | 7.40     | 7.80     | 8.20  |  |  |

| Molded Package Width     | E1         | 5.00     | 5.30     | 5.60  |  |  |

| Overall Length           | D          | 9.90     | 10.20    | 10.50 |  |  |

| Foot Length              | L          | 0.55     | 0.75     | 0.95  |  |  |

| Footprint                | L1         | 1.25 REF |          |       |  |  |

| Lead Thickness           | С          | 0.09     | _        | 0.25  |  |  |

| Foot Angle               | ф          | 0°       | 4°       | 8°    |  |  |

| Lead Width               | b          | 0.22     | _        | 0.38  |  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

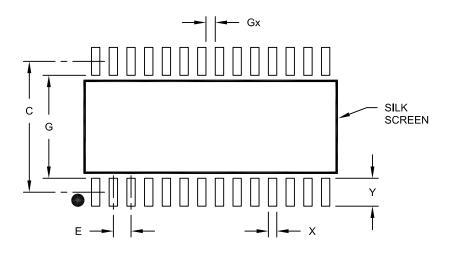

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**lote:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | Units            |          |      |      |

|--------------------------|------------------|----------|------|------|

| Dimension                | Dimension Limits |          |      | MAX  |

| Contact Pitch            |                  | 1.27 BSC |      |      |

| Contact Pad Spacing      | C                |          | 9.40 |      |

| Contact Pad Width (X28)  | Х                |          |      | 0.60 |

| Contact Pad Length (X28) | Υ                |          |      | 2.00 |

| Distance Between Pads    | Gx               | 0.67     |      |      |

| Distance Between Pads    | G                | 7.40     |      | ·    |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

## Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd.

Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support Web Address:

Web Address: www.microchip.com **Atlanta**

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

**Boston** Westborough, MA Tel: 774-760-0087

Fax: 774-760-0088 Chicago

Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Cleveland Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

Dallas Addison, TX Tel: 972-818-7423

Fax: 972-818-2924 **Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110 Canada - Toronto

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

**Australia - Sydney** Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Dongguan** Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

**India - Pune** Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore**Tel: 65-6334-8870

Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

**France - Paris** Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400 Germany - Karlsruhe

Tel: 49-721-625370 **Germany - Munich** Tel: 49-89-627-144-0

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice

Tel: 39-049-7625286

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340 Poland - Warsaw

Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91 **Sweden - Stockholm**

Tel: 46-8-5090-4654 **UK - Wokingham** Tel: 44-118-921-5800

Fax: 44-118-921-5820

07/14/15