#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K × 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx110f016bt-i-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                     |      |                                    |                  | Rem             | appab                                  | le Pe | riphe                | erals                              |                    |                     |                  |     | (                                        |      | ls)                          |      |          |      |                                 |

|---------------------|------|------------------------------------|------------------|-----------------|----------------------------------------|-------|----------------------|------------------------------------|--------------------|---------------------|------------------|-----|------------------------------------------|------|------------------------------|------|----------|------|---------------------------------|

| Device              | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/Compare | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | I <sup>2</sup> C | dMq | DMA Channels<br>(Programmable/Dedicated) | CTMU | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | Packages                        |

| PIC32MX210F016B     | 28   | 16+3                               | 4                | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX210F016C     | 36   | 16+3                               | 4                | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 25       | Y    | VTLA                            |

| PIC32MX210F016D     | 44   | 16+3                               | 4                | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX220F032B     | 28   | 32+3                               | 8                | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX220F032C     | 36   | 32+3                               | 8                | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA                            |

| PIC32MX220F032D     | 44   | 32+3                               | 8                | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX230F064B     | 28   | 64+3                               | 16               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F064C     | 36   | 64+3                               | 16               | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA                            |

| PIC32MX230F064D     | 44   | 64+3                               | 16               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX250F128B     | 28   | 128+3                              | 32               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX250F128C     | 36   | 128+3                              | 32               | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA<br>VTLA,                   |

| PIC32MX250F128D     | 44   | 128+3                              | 32               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | TQFP,<br>QFN                    |

| PIC32MX230F256B     | 28   | 256+3                              | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F256D     | 44   | 256+3                              | 16               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256B     | 28   | 256+3                              | 64               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX270F256D     | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256DB(4) | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

#### TABLE 2: PIC32MX2XX 28/36/44-PIN USB FAMILY FEATURES

Note 1: This device features 3 KB of boot Flash memory.

**2:** Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

4: This PIC32 device is targeted to specific audio software packages that are tracked for licensing royalty purposes. All peripherals and electrical characteristics are identical to their corresponding base part numbers.

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### TABLE 1-1: **PINOUT I/O DESCRIPTIONS**

|          |                   | Pin Nu                                      | nber <sup>(1)</sup>                    |                                        |             |                |                                                                                                                                                                                                |

|----------|-------------------|---------------------------------------------|----------------------------------------|----------------------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | SSOP/ 36-pin<br>SPDIP/ VTLA            |                                        | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                    |

| AN0      | 27                | 2                                           | 33                                     | 19                                     |             | Analog         | Analog input channels.                                                                                                                                                                         |

| AN1      | 28                | 3                                           | 34                                     | 20                                     | I           | Analog         |                                                                                                                                                                                                |

| AN2      | 1                 | 4                                           | 35                                     | 21                                     |             | Analog         |                                                                                                                                                                                                |

| AN3      | 2                 | 5                                           | 36                                     | 22                                     |             | Analog         |                                                                                                                                                                                                |

| AN4      | 3                 | 6                                           | 1                                      | 23                                     | I           | Analog         |                                                                                                                                                                                                |

| AN5      | 4                 | 7                                           | 2                                      | 24                                     | I           | Analog         |                                                                                                                                                                                                |

| AN6      | _                 | _                                           | 3                                      | 25                                     | I           | Analog         |                                                                                                                                                                                                |

| AN7      | _                 | _                                           | 4                                      | 26                                     | I           | Analog         |                                                                                                                                                                                                |

| AN8      | _                 | _                                           | _                                      | 27                                     | I           | Analog         |                                                                                                                                                                                                |

| AN9      | 23                | 26                                          | 29                                     | 15                                     | I           | Analog         |                                                                                                                                                                                                |

| AN10     | 22                | 25                                          | 28                                     | 14                                     | I           | Analog         |                                                                                                                                                                                                |

| AN11     | 21                | 24                                          | 27                                     | 11                                     | I           | Analog         |                                                                                                                                                                                                |

| AN12     | 20 <sup>(2)</sup> | 23 <sup>(2)</sup>                           | 26 <sup>(2)</sup><br>11 <sup>(3)</sup> | 10 <sup>(2)</sup><br>36 <sup>(3)</sup> | 1           | Analog         | *                                                                                                                                                                                              |

| CLKI     | 6                 | 9                                           | 7                                      | 30                                     | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                         |

| CLKO     | 7                 | 10                                          | 8                                      | 31                                     | 0           | _              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes. Always associated<br>with OSC2 pin function. |

| OSC1     | 6                 | 9                                           | 7                                      | 30                                     | I           | ST/CMOS        | -                                                                                                                                                                                              |

| OSC2     | 7                 | 10                                          | 8                                      | 31                                     | 0           | -              | Oscillator crystal output. Connects to<br>crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in<br>RC and EC modes.                                              |

| SOSCI    | 8                 | 11                                          | 9                                      | 33                                     | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal<br>input; CMOS otherwise.                                                                                                                              |

| SOSCO    | 9                 | 12                                          | 10                                     | 34                                     | 0           | —              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                |

| REFCLKI  | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | Reference Input Clock                                                                                                                                                                          |

| REFCLKO  | PPS               | PPS                                         | PPS                                    | PPS                                    | 0           | —              | Reference Output Clock                                                                                                                                                                         |

| IC1      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | Capture Inputs 1-5                                                                                                                                                                             |

| IC2      | PPS               | PPS                                         | PPS                                    | PPS                                    | 1           | ST             | 1                                                                                                                                                                                              |

| IC3      | PPS               | PPS                                         | PPS                                    | PPS                                    | 1           | ST             | 1                                                                                                                                                                                              |

| IC4      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | 1                                                                                                                                                                                              |

| IC5      | PPS               | PPS                                         | PPS                                    | PPS                                    |             | ST             | 1                                                                                                                                                                                              |

|          | ST = Schm         | MOS compa<br>itt Trigger in<br>input buffer |                                        |                                        | •           | O = Outp       | Analog inputP = PowerutI = Inputeripheral Pin Select— = N/A                                                                                                                                    |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability. 2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | —                 |                  | _                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                   | —                 | —                 | -                 | _                 | —                 |                  | _                |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |

| 15:8         |                   |                   |                   | BMXDU             | PBA<15:8>         |                   |                  |                  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          | BMXDUPBA<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |

## REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

## Legend:

| Legena.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 **BMXDUPBA<9:0>:** Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

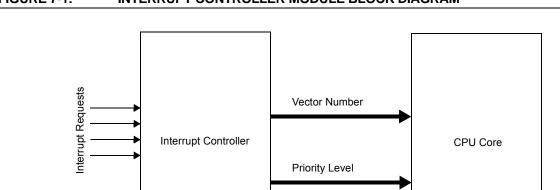

## 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX1XX/2XX 28/36/44-pin Family interrupt module includes the following features:

- Up to 64 interrupt sources

- · Up to 44 interrupt vectors

- · Single and multi-vector mode operations

- Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- · Software can generate any interrupt

- User-configurable Interrupt Vector Table (IVT) location

- User-configurable interrupt vector spacing

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

## FIGURE 7-1: INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

Note: The dedicated shadow register set is not present on PIC32MX1XX/2XX 28/36/44-pin Family devices.

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| bit 3   | CF: Clock Fail Detect bit                                                                                                                                      |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = FSCM has detected a clock failure                                                                                                                          |

|         | 0 = No clock failure has been detected                                                                                                                         |

| bit 2   | UFRCEN: USB FRC Clock Enable bit <sup>(1)</sup>                                                                                                                |

|         | <ul> <li>1 = Enable the FRC as the clock source for the USB clock source</li> <li>0 = Use the Primary Oscillator or USB PLL as the USB clock source</li> </ul> |

| bit 1   | SOSCEN: Secondary Oscillator (Sosc) Enable bit                                                                                                                 |

|         | 1 = Enable the Secondary Oscillator                                                                                                                            |

|         | 0 = Disable the Secondary Oscillator                                                                                                                           |

| bit 0   | OSWEN: Oscillator Switch Enable bit                                                                                                                            |

|         | <ul> <li>1 = Initiate an oscillator switch to selection specified by NOSC&lt;2:0&gt; bits</li> <li>0 = Oscillator switch is complete</li> </ul>                |

| Note 1: | This bit is only available on PIC32MX2XX devices.                                                                                                              |

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

## TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       | - /   |       |      |      | Bit  | s    |      |          |        |        |         |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |      | _    | —    | —        | —      | _      | —       | —      | 0000       |

| 5590                        | UIEF9                           | 15:0      |       |       | —     | —     | —     | —     | _    | —    |      |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5240                        | U1EP10                          | 31:16     | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | —        | _      | _      | —       | _      | 0000       |

| 53A0                        | UIEPIU                          | 15:0      |       | _     | _     | -     | _     | _     | _    | -    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 53BU                        | UIEPII                          | 15:0      | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEFIZ                          | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEF 13                         | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     |       | _     | _     |       | -     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | —        | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | —    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|----------------------|-------------------|-------------------|------------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 31.24        | —                 | -                 | —                    | -                    | —                 | —                 | _                      | -                |

| 23:16        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 23.10        | —                 | —                 | —                    | —                    | —                 | —                 | —                      | —                |

| 15:8         | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 15.0         | —                 | -                 | —                    | -                    | —                 | —                 | —                      | -                |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS       |

| 7:0          | BTSEF             | BMXEF             | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF           | CRC5EF <sup>(4)</sup>  | PIDEF            |

|              | DISEF             | DIVIALE           | DIVIALLY             | BIOLE                | DINOLF            | GIVE IDEF         | EOFEF <sup>(3,5)</sup> |                  |

## REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable b  | pit                |

|-------------------|-------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared      | x = Bit is unknown |

- bit 31-8 Unimplemented: Read as '0'

- bit 7 BTSEF: Bit Stuff Error Flag bit

- 1 = Packet rejected due to bit stuff error

- 0 = Packet accepted

- bit 6 BMXEF: Bus Matrix Error Flag bit

- 1 = The base address, of the Buffer Descriptor Table, or the address of an individual buffer pointed to by a Buffer Descriptor Table entry, is invalid.

- 0 = No address error

- bit 5 DMAEF: DMA Error Flag bit<sup>(1)</sup>

- 1 = USB DMA error condition detected

- 0 = No DMA error

- bit 4 BTOEF: Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup>

- 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out

- bit 3 **DFN8EF:** Data Field Size Error Flag bit

- 1 = Data field received is not an integral number of bytes

- 0 = Data field received is an integral number of bytes

- bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet rejected due to CRC16 error

- 0 = Data packet accepted

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 |                   | —                 | —                 |                   |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   | —                 | —                 |                   | -                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | _                 | —                 | _                 | —                 | —                 | -                 | -                | —                |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | UOEMON            | -                 | USBSIDL           | _                 | _                 | _                | UASUSPND         |

## REGISTER 10-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test is enabled

- 0 = Eye-Pattern Test is disabled

#### bit 6 **UOEMON:** USB OE Monitor Enable bit

1 = OE signal is active; it indicates intervals during which the D+/D- lines are driving

0 = OE signal is inactive

#### bit 5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

#### bit 3-1 Unimplemented: Read as '0'

## bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 10-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock.

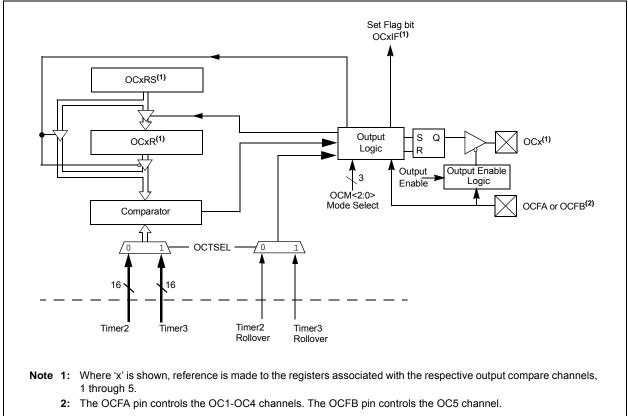

## 16.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Output Compare" (DS60001111), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation. The following are some of the key features:

- · Multiple Output Compare Modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31:24        |                   | _                 | _                 |                   | R                 | XBUFELM<4:        | 0>               |                  |

| 22:16        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        |                   | _                 | —                 |                   | Tک                | KBUFELM<4:0       | )>               |                  |

| 45.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |

| 15:8         |                   | —                 | _                 | FRMERR            | SPIBUSY           | —                 | —                | SPITUR           |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |

| 7:0          | SRMT              | SPIROV            | SPIRBE            | _                 | SPITBE            | —                 | SPITBF           | SPIRBF           |

## REGISTER 17-3: SPIxSTAT: SPI STATUS REGISTER

| Legend:           | C = Clearable bit | HS = Set in hardware     |                    |  |

|-------------------|-------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared     | x = Bit is unknown |  |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error detected

- 0 = No Frame error detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPITUR: Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 **SPIRBE:** RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR)

- 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

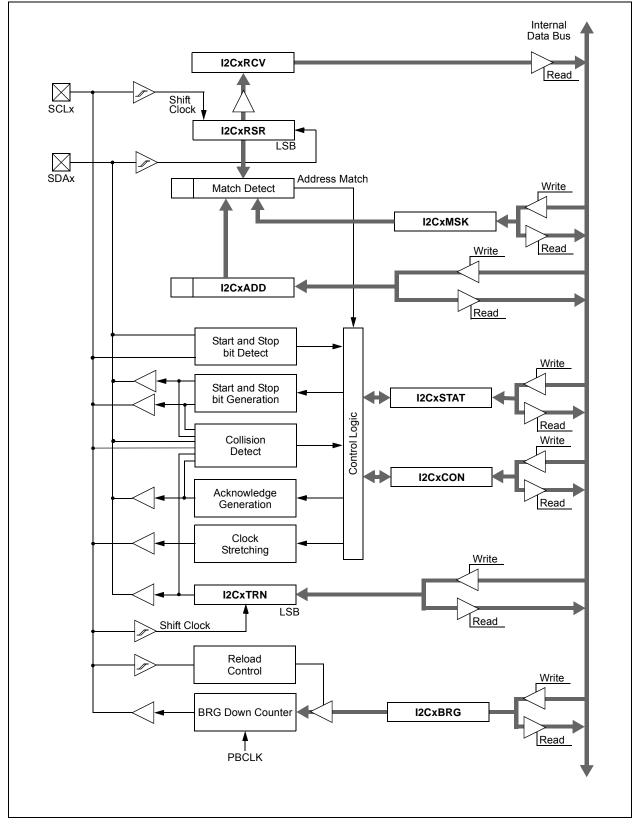

## FIGURE 18-1: I<sup>2</sup>C BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24        | _                 | _                 | HR10              | <1:0>             | HR01<3:0>         |                   |                  |                  |

| 00.40        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        |                   | MIN10<2:0>        |                   |                   | MIN01<3:0>        |                   |                  |                  |

| 45.0         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         |                   | SEC10<2:0>        |                   |                   | SEC01<3:0>        |                   |                  |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|              |                   |                   | 1                 |                   |                   |                   |                  |                  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |

### REGISTER 21-3: RTCTIME: RTC TIME VALUE REGISTER

# R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary-Coded Decimal Value of Hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 **HR01<3:0>:** Binary-Coded Decimal Value of Hours bits, 1s place digit; contains a value from 0 to 9 bit 23 **Unimplemented:** Read as '0'

bit 22-20 MIN10<2:0>: Binary-Coded Decimal Value of Minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 **MIN01<3:0>:** Binary-Coded Decimal Value of Minutes bits, 1s place digit; contains a value from 0 to 9 bit 15 **Unimplemented:** Read as '0'

bit 14-12 SEC10<2:0>: Binary-Coded Decimal Value of Seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 **SEC01<3:0>:** Binary-Coded Decimal Value of Seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

x = Bit is unknown

| REGISTER 21-4. RTCDATE. RTC DATE VALOE REGISTER |                   |                   |                   |                                    |                                         |                   |                  |                  |

|-------------------------------------------------|-------------------|-------------------|-------------------|------------------------------------|-----------------------------------------|-------------------|------------------|------------------|

| Bit<br>Range                                    | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4                  | Bit<br>27/19/11/3                       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04                                           | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |

| 31:24                                           |                   | YEAR1             | 0<3:0>            |                                    | YEAR01<3:0>                             |                   |                  |                  |

| 00.40                                           | U-0               | U-0               | U-0               | R/W-x                              | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |

| 23:16                                           |                   | —                 | _                 | MONTH10                            |                                         | MONTH             | 01<3:0>          |                  |

| 45.0                                            | U-0               | U-0               | R/W-x             | R/W-x                              | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |

| 15:8                                            |                   |                   | DAY10             | )<1:0>                             | DAY01<3:0>                              |                   |                  |                  |

| 7.0                                             | U-0               | U-0               | U-0               | U-0                                | U-0                                     | R/W-x             | R/W-x            | R/W-x            |

| 7:0                                             | —                 | _                 | _                 | _                                  | —                                       | — WDAY01<2:0>     |                  | >                |

|                                                 |                   |                   |                   |                                    |                                         |                   |                  |                  |

| Legend:                                         |                   |                   |                   |                                    |                                         |                   |                  |                  |

| R = Readable bit W = Writable bit               |                   |                   | e bit             | U = Unimplemented bit, read as '0' |                                         |                   |                  |                  |

| -n = Value                                      | e at POR          |                   | '1' = Bit is se   | t                                  | '0' = Bit is cleared x = Bit is unknown |                   |                  | known            |

## REGISTER 21-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10s place digit; contains a value from 0 to 9

bit 27-24 **YEAR01<3:0>:** Binary-Coded Decimal Value of Years bits, 1s place digit; contains a value from 0 to 9 bit 23-21 **Unimplemented:** Read as '0'

bit 20 **MONTH10:** Binary-Coded Decimal Value of Months bits, 10s place digit; contains a value of 0 or 1

bit 19-16 **MONTH01<3:0>:** Binary-Coded Decimal Value of Months bits, 1s place digit; contains a value from 0 to 9 bit 15-14 **Unimplemented:** Read as '0'

bit 13-12 DAY10<1:0>: Binary-Coded Decimal Value of Days bits, 10s place digit; contains a value of 0 to 3

bit 11-8 DAY01<3:0>: Binary-Coded Decimal Value of Days bits, 1s place digit; contains a value from 0 to 9

bit 7-3 **Unimplemented:** Read as '0'

bit 2-0 WDAY01<2:0>: Binary-Coded Decimal Value of Weekdays bits; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                     | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                   | _                 | _                 |                   | —                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | _                 | —                 | —                 | —                | COUT             |

| 7.0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            | _                   | CREF              | —                 | —                 | CCH              | <1:0>            |

### REGISTER 23-1: CMXCON: COMPARATOR CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | Writable bit U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|-------------------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                            | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 = Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 **EVPOL<1:0>:** Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

- bit 4 CREF: Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

#### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED) bit 24 EDG1STAT: Edge1 Status bit Indicates the status of Edge1 and can be written to control edge source 1 = Edge1 has occurred 0 = Edge1 has not occurred EDG2MOD: Edge2 Edge Sampling Select bit bit 23 1 = Input is edge-sensitive 0 = Input is level-sensitive bit 22 EDG2POL: Edge 2 Polarity Select bit 1 = Edge2 programmed for a positive edge response 0 = Edge2 programmed for a negative edge response bit 21-18 EDG2SEL<3:0>: Edge 2 Source Select bits 1111 = C3OUT pin is selected 1110 = C2OUT pin is selected 1101 = C1OUT pin is selected 1100 = PBCLK clock is selected 1011 = IC3 Capture Event is selected 1010 = IC2 Capture Event is selected 1001 = IC1 Capture Event is selected 1000 = CTED13 pin is selected 0111 = CTED12 pin is selected 0110 = CTED11 pin is selected 0101 = CTED10 pin is selected 0100 = CTED9 pin is selected 0011 = CTED1 pin is selected 0010 = CTED2 pin is selected 0001 = OC1 Compare Event is selected 0000 = Timer1 Event is selected bit 17-16 Unimplemented: Read as '0' bit 15 **ON:** ON Enable bit 1 = Module is enabled 0 = Module is disabled bit 14 Unimplemented: Read as '0' bit 13 CTMUSIDL: Stop in Idle Mode bit 1 = Discontinue module operation when the device enters Idle mode 0 = Continue module operation when the device enters Idle mode TGEN: Time Generation Enable bit<sup>(1)</sup> bit 12 1 = Enables edge delay generation 0 = Disables edge delay generation bit 11 EDGEN: Edge Enable bit 1 = Edges are not blocked 0 = Edges are blocked

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

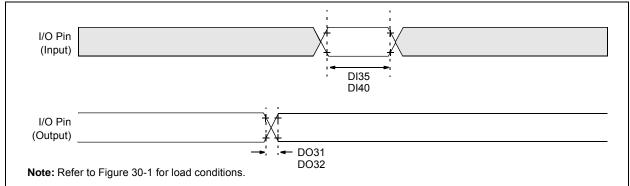

## FIGURE 30-3: I/O TIMING CHARACTERISTICS

## TABLE 30-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | (unless other | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                        |      |         |            |

|--------------------|--------|--------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|---------|------------|

| Param.<br>No.      | Symbol | Characteristics <sup>(2)</sup> |               | Min.                                                                                                                                                                                               | Typical <sup>(1)</sup> | Max. | Units   | Conditions |

| DO31               | TIOR   | Port Output Rise Time          |               |                                                                                                                                                                                                    | 5                      | 15   | ns      | Vdd < 2.5V |

|                    |        |                                |               |                                                                                                                                                                                                    | 5                      | 10   | ns      | Vdd > 2.5V |

| DO32               | TIOF   | Port Output Fall Time          |               | _                                                                                                                                                                                                  | 5                      | 15   | ns      | Vdd < 2.5V |

|                    |        |                                |               |                                                                                                                                                                                                    | 5                      | 10   | ns      | VDD > 2.5V |

| DI35               | Tinp   | INTx Pin High or Low Time      |               | 10                                                                                                                                                                                                 | _                      | _    | ns      | _          |

| DI40               | Trbp   | CNx High or Low Time (input)   |               | 2                                                                                                                                                                                                  | _                      |      | TSYSCLK |            |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: This parameter is characterized, but not tested in manufacturing.

## 33.0 PACKAGING INFORMATION

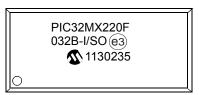

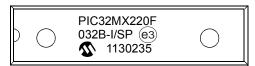

## 33.1 Package Marking Information

28-Lead SOIC

## 28-Lead SPDIP

Example

## Example

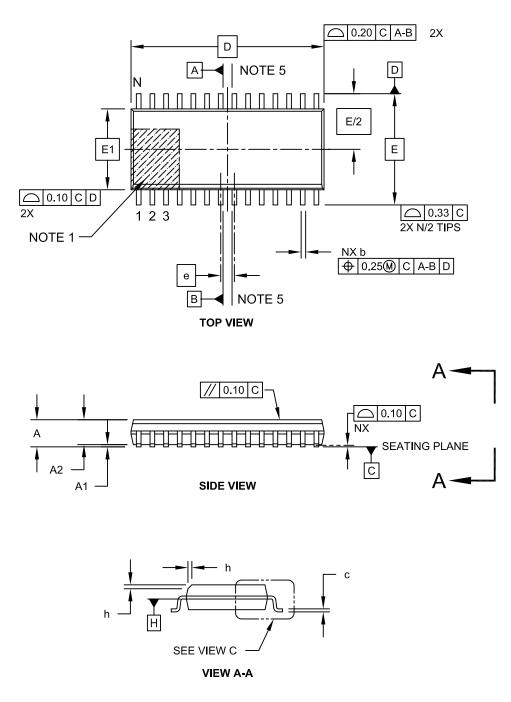

## 28-Lead SSOP

## 28-Lead QFN

Example

## Example

| Legenc | I: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (@3)<br>can be found on the outer packaging for this package. |

|--------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  |                                           | Aicrochip part number cannot be marked on one line, it is carried over to the next limiting the number of available characters for customer-specific information.                                                                                                                                                                                                            |

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

## **Revision D (February 2012)**

All occurrences of VUSB were changed to: VUSB3V3. In addition, text and formatting changes were incorporated throughout the document.

All other major changes are referenced by their respective section in Table A-3.

## TABLE A-3: MAJOR SECTION UPDATES

| Section                                                                                      | Update Description                                                                                                                                                                |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to 128                                                          | Corrected a part number error in all pin diagrams.                                                                                                                                |

| KB Flash and 32 KB SRAM) with<br>Audio and Graphics Interfaces, USB,<br>and Advanced Analog" | Updated the DMA Channels (Programmable/Dedicated) column in the PIC32MX1XX General Purpose Family Features (see Table 1).                                                         |

| 1.0 "Device Overview"                                                                        | Added the TQFP and VTLA packages to the 44-pin column heading and updated the pin numbers for the SCL1, SCL2, SDA1, and SDA2 pins in the Pinout I/O Descriptions (see Table 1-1). |

| 7.0 "Interrupt Controller"                                                                   | Updated the Note that follows the features.                                                                                                                                       |

|                                                                                              | Updated the Interrupt Controller Block Diagram (see Figure 7-1).                                                                                                                  |

| 29.0 "Electrical Characteristics"                                                            | Updated the Maximum values for parameters DC20-DC24, and the Minimum value for parameter DC21 in the Operating Current (IDD) DC Characteristics (see Table 29-5).                 |

|                                                                                              | Updated all Minimum and Maximum values for the Idle Current (IIDLE) DC Characteristics (see Table 29-6).                                                                          |

|                                                                                              | Updated the Maximum values for parameters DC40k, DC40l, DC40n, and DC40m in the Power-down Current (IPD) DC Characteristics (see Table 29-7).                                     |

|                                                                                              | Changed the minimum clock period for SCKx from 40 ns to 50 ns in Note 3 of the SPIx Master and Slave Mode Timing Requirements (see Table 29-26 through Table 29-29).              |

| 30.0 "DC and AC Device<br>Characteristics Graphs"                                            | Updated the Typical IIDLE Current @ VDD = 3.3V graph (see Figure 30-5).                                                                                                           |