Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32 ® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx110f016bt-v-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

## 3.2 Architecture Overview

The MIPS32 M4K processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- · Enhanced JTAG (EJTAG) Controller

#### 3.2.1 EXECUTION UNIT

The MIPS32 M4K processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- · 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter and store aligner

## 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32 M4K processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

# TABLE 3-1:MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGERMULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

| Opcode                  | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |

|-------------------------|------------------------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                                        | 2       | 2           |

| MUL                     | 16 bits                                        | 2       | 1           |

|                         | 32 bits                                        | 3       | 2           |

| DIV/DIVU                | 8 bits                                         | 12      | 11          |

|                         | 16 bits                                        | 19      | 18          |

|                         | 24 bits                                        | 26      | 25          |

|                         | 32 bits                                        | 33      | 32          |

## TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| (1)                                 | IRQ | Vector |              | Persistent     |             |              |           |

|-------------------------------------|-----|--------|--------------|----------------|-------------|--------------|-----------|

| Interrupt Source <sup>(1)</sup>     | #   | #      | Flag         | Enable         | Priority    | Sub-priority | Interrupt |

|                                     |     | Highes | st Natural C | order Priority | 1           |              | •         |

| CT – Core Timer Interrupt           | 0   | 0      | IFS0<0>      | IEC0<0>        | IPC0<4:2>   | IPC0<1:0>    | No        |

| CS0 – Core Software Interrupt 0     | 1   | 1      | IFS0<1>      | IEC0<1>        | IPC0<12:10> | IPC0<9:8>    | No        |

| CS1 – Core Software Interrupt 1     | 2   | 2      | IFS0<2>      | IEC0<2>        | IPC0<20:18> | IPC0<17:16>  | No        |

| INT0 – External Interrupt           | 3   | 3      | IFS0<3>      | IEC0<3>        | IPC0<28:26> | IPC0<25:24>  | No        |

| T1 – Timer1                         | 4   | 4      | IFS0<4>      | IEC0<4>        | IPC1<4:2>   | IPC1<1:0>    | No        |

| IC1E – Input Capture 1 Error        | 5   | 5      | IFS0<5>      | IEC0<5>        | IPC1<12:10> | IPC1<9:8>    | Yes       |

| IC1 – Input Capture 1               | 6   | 5      | IFS0<6>      | IEC0<6>        | IPC1<12:10> | IPC1<9:8>    | Yes       |

| OC1 – Output Compare 1              | 7   | 6      | IFS0<7>      | IEC0<7>        | IPC1<20:18> | IPC1<17:16>  | No        |

| INT1 – External Interrupt 1         | 8   | 7      | IFS0<8>      | IEC0<8>        | IPC1<28:26> | IPC1<25:24>  | No        |

| T2 – Timer2                         | 9   | 8      | IFS0<9>      | IEC0<9>        | IPC2<4:2>   | IPC2<1:0>    | No        |

| IC2E – Input Capture 2              | 10  | 9      | IFS0<10>     | IEC0<10>       | IPC2<12:10> | IPC2<9:8>    | Yes       |

| IC2 – Input Capture 2               | 11  | 9      | IFS0<11>     | IEC0<11>       | IPC2<12:10> | IPC2<9:8>    | Yes       |

| OC2 – Output Compare 2              | 12  | 10     | IFS0<12>     | IEC0<12>       | IPC2<20:18> | IPC2<17:16>  | No        |

| INT2 – External Interrupt 2         | 13  | 11     | IFS0<13>     | IEC0<13>       | IPC2<28:26> | IPC2<25:24>  | No        |

| T3 – Timer3                         | 14  | 12     | IFS0<14>     | IEC0<14>       | IPC3<4:2>   | IPC3<1:0>    | No        |

| IC3E – Input Capture 3              | 15  | 13     | IFS0<15>     | IEC0<15>       | IPC3<12:10> | IPC3<9:8>    | Yes       |

| IC3 – Input Capture 3               | 16  | 13     | IFS0<16>     | IEC0<16>       | IPC3<12:10> | IPC3<9:8>    | Yes       |

| OC3 – Output Compare 3              | 17  | 14     | IFS0<17>     | IEC0<17>       | IPC3<20:18> | IPC3<17:16>  | No        |

| INT3 – External Interrupt 3         | 18  | 15     | IFS0<18>     | IEC0<18>       | IPC3<28:26> | IPC3<25:24>  | No        |

| T4 – Timer4                         | 19  | 16     | IFS0<19>     | IEC0<19>       | IPC4<4:2>   | IPC4<1:0>    | No        |

| IC4E – Input Capture 4 Error        | 20  | 17     | IFS0<20>     | IEC0<20>       | IPC4<12:10> | IPC4<9:8>    | Yes       |

| IC4 – Input Capture 4               | 21  | 17     | IFS0<21>     | IEC0<21>       | IPC4<12:10> | IPC4<9:8>    | Yes       |

| OC4 – Output Compare 4              | 22  | 18     | IFS0<22>     | IEC0<22>       | IPC4<20:18> | IPC4<17:16>  | No        |

| INT4 – External Interrupt 4         | 23  | 19     | IFS0<23>     | IEC0<23>       | IPC4<28:26> | IPC4<25:24>  | No        |

| T5 – Timer5                         | 24  | 20     | IFS0<24>     | IEC0<24>       | IPC5<4:2>   | IPC5<1:0>    | No        |

| IC5E – Input Capture 5 Error        | 25  | 21     | IFS0<25>     | IEC0<25>       | IPC5<12:10> | IPC5<9:8>    | Yes       |

| IC5 – Input Capture 5               | 26  | 21     | IFS0<26>     | IEC0<26>       | IPC5<12:10> | IPC5<9:8>    | Yes       |

| OC5 – Output Compare 5              | 27  | 22     | IFS0<27>     | IEC0<27>       | IPC5<20:18> | IPC5<17:16>  | No        |

| AD1 – ADC1 Convert done             | 28  | 23     | IFS0<28>     | IEC0<28>       | IPC5<28:26> | IPC5<25:24>  | Yes       |

| FSCM – Fail-Safe Clock Monitor      | 29  | 24     | IFS0<29>     | IEC0<29>       | IPC6<4:2>   | IPC6<1:0>    | No        |

| RTCC – Real-Time Clock and Calendar | 30  | 25     | IFS0<30>     | IEC0<30>       | IPC6<12:10> | IPC6<9:8>    | No        |

| FCE – Flash Control Event           | 31  | 26     | IFS0<31>     | IEC0<31>       | IPC6<20:18> | IPC6<17:16>  | No        |

| CMP1 – Comparator Interrupt         | 32  | 27     | IFS1<0>      | IEC1<0>        | IPC6<28:26> | IPC6<25:24>  | No        |

| CMP2 – Comparator Interrupt         | 33  | 28     | IFS1<1>      | IEC1<1>        | IPC7<4:2>   | IPC7<1:0>    | No        |

| CMP3 – Comparator Interrupt         | 34  | 29     | IFS1<2>      | IEC1<2>        | IPC7<12:10> | IPC7<9:8>    | No        |

| USB – USB Interrupts                | 35  | 30     | IFS1<3>      | IEC1<3>        | IPC7<20:18> | IPC7<17:16>  | Yes       |

| SPI1E – SPI1 Fault                  | 36  | 31     | IFS1<4>      | IEC1<4>        | IPC7<28:26> | IPC7<25:24>  | Yes       |

| SPI1RX – SPI1 Receive Done          | 37  | 31     | IFS1<5>      | IEC1<5>        | IPC7<28:26> | IPC7<25:24>  | Yes       |

| SPI1TX – SPI1 Transfer Done         | 38  | 31     | IFS1<6>      | IEC1<6>        | IPC7<28:26> | IPC7<25:24>  | Yes       |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/36/44-Pin General Purpose Family Features" and TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features" for the lists of available peripherals.

| Interrupt Source <sup>(1)</sup>       | IRQ | Vector |          | Interru       | pt Bit Location |              | Persistent |

|---------------------------------------|-----|--------|----------|---------------|-----------------|--------------|------------|

| Interrupt Source.                     | #   | #      | Flag     | Enable        | Priority        | Sub-priority | Interrupt  |

| U1E – UART1 Fault                     | 39  | 32     | IFS1<7>  | IEC1<7>       | IPC8<4:2>       | IPC8<1:0>    | Yes        |

| U1RX – UART1 Receive Done             | 40  | 32     | IFS1<8>  | IEC1<8>       | IPC8<4:2>       | IPC8<1:0>    | Yes        |

| U1TX – UART1 Transfer Done            | 41  | 32     | IFS1<9>  | IEC1<9>       | IPC8<4:2>       | IPC8<1:0>    | Yes        |

| I2C1B – I2C1 Bus Collision Event      | 42  | 33     | IFS1<10> | IEC1<10>      | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| I2C1S – I2C1 Slave Event              | 43  | 33     | IFS1<11> | IEC1<11>      | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| I2C1M – I2C1 Master Event             | 44  | 33     | IFS1<12> | IEC1<12>      | IPC8<12:10>     | IPC8<9:8>    | Yes        |

| CNA – PORTA Input Change<br>Interrupt | 45  | 34     | IFS1<13> | IEC1<13>      | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| CNB – PORTB Input Change<br>Interrupt | 46  | 34     | IFS1<14> | IEC1<14>      | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| CNC – PORTC Input Change<br>Interrupt | 47  | 34     | IFS1<15> | IEC1<15>      | IPC8<20:18>     | IPC8<17:16>  | Yes        |

| PMP – Parallel Master Port            | 48  | 35     | IFS1<16> | IEC1<16>      | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| PMPE – Parallel Master Port Error     | 49  | 35     | IFS1<17> | IEC1<17>      | IPC8<28:26>     | IPC8<25:24>  | Yes        |

| SPI2E – SPI2 Fault                    | 50  | 36     | IFS1<18> | IEC1<18>      | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| SPI2RX – SPI2 Receive Done            | 51  | 36     | IFS1<19> | IEC1<19>      | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| SPI2TX – SPI2 Transfer Done           | 52  | 36     | IFS1<20> | IEC1<20>      | IPC9<4:2>       | IPC9<1:0>    | Yes        |

| U2E – UART2 Error                     | 53  | 37     | IFS1<21> | IEC1<21>      | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| U2RX – UART2 Receiver                 | 54  | 37     | IFS1<22> | IEC1<22>      | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| U2TX – UART2 Transmitter              | 55  | 37     | IFS1<23> | IEC1<23>      | IPC9<12:10>     | IPC9<9:8>    | Yes        |

| I2C2B – I2C2 Bus Collision Event      | 56  | 38     | IFS1<24> | IEC1<24>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| I2C2S – I2C2 Slave Event              | 57  | 38     | IFS1<25> | IEC1<25>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| I2C2M – I2C2 Master Event             | 58  | 38     | IFS1<26> | IEC1<26>      | IPC9<20:18>     | IPC9<17:16>  | Yes        |

| CTMU – CTMU Event                     | 59  | 39     | IFS1<27> | IEC1<27>      | IPC9<28:26>     | IPC9<25:24>  | Yes        |

| DMA0 – DMA Channel 0                  | 60  | 40     | IFS1<28> | IEC1<28>      | IPC10<4:2>      | IPC10<1:0>   | No         |

| DMA1 – DMA Channel 1                  | 61  | 41     | IFS1<29> | IEC1<29>      | IPC10<12:10>    | IPC10<9:8>   | No         |

| DMA2 – DMA Channel 2                  | 62  | 42     | IFS1<30> | IEC1<30>      | IPC10<20:18>    | IPC10<17:16> | No         |

| DMA3 – DMA Channel 3                  | 63  | 43     | IFS1<31> | IEC1<31>      | IPC10<28:26>    | IPC10<25:24> | No         |

|                                       |     | Lowes  |          | rder Priority | E 4. ((DIOOON)) |              |            |

#### TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/36/44-Pin General Purpose Family Features" and TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features" for the lists of available peripherals.

## TABLE 7-2: INTERRUPT REGISTER MAP (CONTINUED)

| ess                         |                                 | ¢,        |       | Bits  |       |       |             |       |        |        |      |      |      |               |             |        |        |                  |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------------|-------|--------|--------|------|------|------|---------------|-------------|--------|--------|------------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9   | 24/8   | 23/7 | 22/6 | 21/5 | 20/4          | 19/3        | 18/2   | 17/1   | 16/0             | All<br>Resets |

| 1100                        | 1007                            | 31:16     | _     | —     | —     |       | SPI1IP<2:0> |       | SPI1IS | S<1:0> | -    | —    | —    | US            | SBIP<2:0>(2 | :)     | USBIS  | <1:0> <b>(2)</b> | 0000          |

| 1100                        | IPC7                            | 15:0      | _     | -     | —     | (     | CMP3IP<2:0> |       | CMP3IS | S<1:0> | _    | _    | _    | CMP2IP<2:0>   |             | CMP2I  | S<1:0> | 0000             |               |

| 1110                        | IPC8                            | 31:16     | _     | _     | —     |       | PMPIP<2:0>  |       | PMPIS  | S<1:0> | _    | —    | _    | (             | CNIP<2:0>   |        | CNIS   | <1:0>            | 0000          |

| 1110                        | IPCo                            | 15:0      |       | —     | _     |       | I2C1IP<2:0> |       | I2C1IS | <1:0>  | —    | —    | _    | I             | J1IP<2:0>   |        | U1IS   | <1:0>            | 0000          |

| 1120                        | IPC9                            | 31:16     |       | —     | _     | (     | CTMUIP<2:0  | >     | CTMU   | S<1:0> | —    | —    | _    | 12            | 2C2IP<2:0>  |        | 12C218 | 6<1:0>           | 0000          |

| 1120                        | IFC9                            | 15:0      | -     | —     | _     |       | U2IP<2:0>   |       | U2IS<  | <1:0>  | _    | _    | _    | SPI2IP<2:0> S |             | SPI2IS | S<1:0> | 0000             |               |

| 1130                        | IPC10                           | 31:16     | —     | _     | —     | [     | DMA3IP<2:0> |       | DMA3IS | S<1:0> | _    | —    | _    | DI            | MA2IP<2:0>  | •      | DMA2I  | S<1:0>           | 0000          |

| 1130                        | IFC IU                          | 15:0      | _     | _     | _     | [     | DMA1IP<2:0> | >     | DMA1IS | S<1:0> | _    | _    | _    | DI            | VA0IP<2:0   | •      | DMA0I  | S<1:0>           | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX1XX devices.

3: This register does not have associated CLR, SET, INV registers.

## 8.1 Oscillator Control Regiters

| TABLE 8-1: OSCILLATOR CONTROL REGISTER MAP |                                 |           |       |              |          |       |           |       |                       |        |         |                      |                     |       |      |                       |        |       |                     |

|--------------------------------------------|---------------------------------|-----------|-------|--------------|----------|-------|-----------|-------|-----------------------|--------|---------|----------------------|---------------------|-------|------|-----------------------|--------|-------|---------------------|

| ess                                        |                                 |           |       |              |          |       |           |       |                       |        | Bits    |                      |                     |       |      |                       |        |       | ú                   |

| Virtual Address<br>(BF80_#)                | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14        | 29/13    | 28/12 | 27/11     | 26/10 | 25/9                  | 24/8   | 23/7    | 22/6                 | 21/5                | 20/4  | 19/3 | 18/2                  | 17/1   | 16/0  | All Reset           |

| F000                                       | OSCCON                          | 31:16     | —     | PLLODIV<2:0> |          |       |           |       | FRCDIV<2:0> — SOSCRD' |        |         | SOSCRDY              | PBDIVRDY PBDIV<1:0> |       |      | PLLMULT<2:0>          |        |       | x1xx <sup>(2)</sup> |

| FUUU                                       | 030001                          | 15:0      | —     |              | COSC<2:0 | V     | Ι         |       | NOSC<2:0              | >      | CLKLOCK | ULOCK <sup>(3)</sup> | SLOCK               | SLPEN | CF   | UFRCEN <sup>(3)</sup> | SOSCEN | OSWEN | xxxx(2)             |

| F010                                       | OSCTUN                          | 31:16     | _     | _            |          | _     | _         |       |                       | _      | _       | _                    | _                   | _     |      | _                     | —      | _     | 0000                |

| 1010                                       | 030101                          | 15:0      | _     | _            |          | _     | _         |       |                       | _      | _       | _                    |                     |       | TUN  | l<5:0>                |        |       | 0000                |

| 5000                                       |                                 | 31:16     | _     |              |          |       |           |       |                       |        | RODIV<1 | 4:0>                 |                     |       |      |                       |        |       | 0000                |

| F020                                       | REFOCON                         | 15:0      | ON    |              | SIDL     | OE    | RSLP      | -     | DIVSWEN               | ACTIVE | —       | —                    |                     |       |      | ROSE                  | _<3:0> |       | 0000                |

| F000                                       | DEFOTDIM                        | 31:16     |       |              |          | R     | OTRIM<8:0 | )>    | >                     |        |         |                      | _                   | _     | _    | _                     | _      | _     | 0000                |

| F030                                       | REFOTRIM                        | 15:0      | _     | _            |          | _     | _         |       |                       | -      | _       | _                    | _                   | _     |      | _                     | —      | _     | 0000                |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on PIC32MX2XX devices.

#### REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER

|              | -                 |                       |                   |                   |                    |                   |                  |                  |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0            |

| 31:24        | —                 | _                     | BYTC              | <1:0>             | WBO <sup>(1)</sup> | —                 | _                | BITO             |

| 22:16        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                     | —                 | _                 | —                  | —                 | _                | _                |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   | _                     | _                 |                   |                    | PLEN<4:0>         |                  |                  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | _                 | _                  | (                 | CRCCH<2:0>       |                  |

## Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-30 Unimplemented: Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

#### <u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

#### bit 23-13 Unimplemented: Read as '0'

bit 12-8 **PLEN<4:0>:** Polynomial Length bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| REGISTE | R 9-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | CHDHIF: Channel Destination Half Full Interrupt Flag bit                                                                                                                                   |

|         | <ul> <li>1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)</li> <li>0 = No interrupt is pending</li> </ul>                                           |

| bit 3   | CHBCIF: Channel Block Transfer Complete Interrupt Flag bit                                                                                                                                 |

|         | <ul> <li>1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs</li> <li>0 = No interrupt is pending</li> </ul> |

| bit 2   | CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit                                                                                                                                  |

|         | <ul><li>1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)</li><li>0 = No interrupt is pending</li></ul>                                                          |

| bit 1   | CHTAIF: Channel Transfer Abort Interrupt Flag bit                                                                                                                                          |

|         | <ul> <li>1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted</li> <li>0 = No interrupt is pending</li> </ul>                                          |

| bit 0   | CHERIF: Channel Address Error Interrupt Flag bit                                                                                                                                           |

|         | <ul> <li>1 = A channel address error has been detected (either the source or the destination address is invalid)</li> <li>0 = No interrupt is pending</li> </ul>                           |

DS60001168J-page 96

#### REGISTER 10-7: U1IE: USB INTERRUPT ENABLE REGISTER

|              |                   | •                 |                   |                   |                   |                   |                       |                                                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|--------------------------------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0                                 |

| 31:24        | U-0                   | U-0                                              |

| 51.24        | —                 | —                 | —                 | —                 | —                 | —                 | —                     | —                                                |

| 23:16        | U-0                   | U-0                                              |

| 23:10        | -                 | —                 | —                 | —                 | —                 | —                 | —                     | —                                                |

| 15:8         | U-0                   | U-0                                              |

| 15.0         | _                 | —                 | —                 | _                 | —                 | _                 | _                     | —                                                |

|              | R/W-0                 | R/W-0                                            |

| 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            | TRNIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup><br>DETACHIE <sup>(3)</sup> |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | STALLIE: STALL Handshake Interrupt Enable bit |

|-------|-----------------------------------------------|

|       |                                               |

- 1 = STALL interrupt is enabled

- 0 = STALL interrupt is disabled

- bit 6 ATTACHIE: ATTACH Interrupt Enable bit

- 1 = ATTACH interrupt is enabled 0 = ATTACH interrupt is disabled

- bit 5 **RESUMEIE:** RESUME Interrupt Enable bit

- 1 = RESUME interrupt is enabled

- 0 = RESUME interrupt is disabled

- bit 4 IDLEIE: Idle Detect Interrupt Enable bit

- 1 = Idle interrupt is enabled

- 0 = Idle interrupt is disabled

- bit 3 TRNIE: Token Processing Complete Interrupt Enable bit

- 1 = TRNIF interrupt is enabled

- 0 = TRNIF interrupt is disabled

- bit 2 SOFIE: SOF Token Interrupt Enable bit

- 1 = SOFIF interrupt is enabled

- 0 = SOFIF interrupt is disabled

- bit 1 UERRIE: USB Error Interrupt Enable bit<sup>(1)</sup>

- 1 = USB Error interrupt is enabled

- 0 = USB Error interrupt is disabled

- bit 0 URSTIE: USB Reset Interrupt Enable bit<sup>(2)</sup>

- 1 = URSTIF interrupt is enabled

- 0 = URSTIF interrupt is disabled

#### DETACHIE: USB Detach Interrupt Enable bit<sup>(3)</sup>

- 1 = DATTCHIF interrupt is enabled

- 0 = DATTCHIF interrupt is disabled

**Note 1:** For an interrupt to propagate USBIF, the UERRIE (U1IE<1>) bit must be set.

- 2: Device mode.

- 3: Host mode.

## 11.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin-count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only option.

The Peripheral Pin Select (PPS) configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

### 11.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

### 11.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digitalonly peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the PPS feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin.

Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.3.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

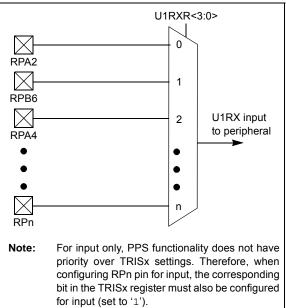

## 11.3.4 INPUT MAPPING

The inputs of the PPS options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 11-1, are used to configure peripheral input mapping (see Register 11-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 11-1.

For example, Figure 11-2 illustrates the remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT EXAMPLE FOR U1RX

### TABLE 11-1: INPUT PIN SELECTION

| Peripheral Pin | [pin name]R SFR | [pin name]R bits | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection                                     |

|----------------|-----------------|------------------|----------------------------------------------------------------------------------------|

| INT4           | INT4R           | INT4R<3:0>       | 0000 = RPA0<br>0001 = RPB3                                                             |

| T2CK           | T2CKR           | T2CKR<3:0>       | 0010 = RPB4<br>0011 = RPB15<br>0100 = RPB7                                             |

| IC4            | IC4R            | IC4R<3:0>        | 0101 = RPC7 <sup>(2)</sup><br>0110 = RPC0 <sup>(1)</sup><br>0111 = RPC5 <sup>(2)</sup> |

| SS1            | SS1R            | SS1R<3:0>        | 1000 = Reserved                                                                        |

| REFCLKI        | REFCLKIR        | REFCLKIR<3:0>    | :<br>1111 = Reserved                                                                   |

| INT3           | INT3R           | INT3R<3:0>       | 0000 = RPA1<br>0001 = RPB5                                                             |

| ТЗСК           | T3CKR           | T3CKR<3:0>       | 0010 = RPB1<br>0011 = RPB11                                                            |

| IC3            | IC3R            | IC3R<3:0>        | 0100 = RPB8<br>0101 = RPA8 <sup>(2)</sup>                                              |

| U1CTS          | U1CTSR          | U1CTSR<3:0>      | 0110 = RPC8 <sup>(2)</sup><br>0111 = RPA9 <sup>(2)</sup>                               |

| U2RX           | U2RXR           | U2RXR<3:0>       | 1000 = Reserved                                                                        |

| SDI1           | SDI1R           | SDI1R<3:0>       | •<br>1111 = Reserved                                                                   |

| INT2           | INT2R           | INT2R<3:0>       | 0000 = RPA2                                                                            |

| T4CK           | T4CKR           | T4CKR<3:0>       |                                                                                        |

| IC1            | IC1R            | IC1R<3:0>        | 0011 = RPB13<br>0100 = RPB2                                                            |

| IC5            | IC5R            | IC5R<3:0>        | 0101 = RPC6 <sup>(2)</sup>                                                             |

| U1RX           | U1RXR           | U1RXR<3:0>       | 0110 = RPC1 <sup>(1)</sup><br>0111 = RPC3 <sup>(1)</sup>                               |

| U2CTS          | U2CTSR          | U2CTSR<3:0>      | 1000 = Reserved                                                                        |

| SDI2           | SDI2R           | SDI2R<3:0>       | •                                                                                      |

| OCFB           | OCFBR           | OCFBR<3:0>       | •<br>1111 = Reserved                                                                   |

| INT1           | INT1R           | INT1R<3:0>       | 0000 = RPA3<br>0001 = RPB14                                                            |

| T5CK           | T5CKR           | T5CKR<3:0>       | 0010 = RPB0<br>0011 = RPB10<br>0100 = RPB9                                             |

| IC2            | IC2R            | IC2R<3:0>        | 0101 = RPC9 <sup>(1)</sup><br>0110 = RPC2 <sup>(2)</sup><br>0111 = RPC4 <sup>(2)</sup> |

| SS2            | SS2R            | SS2R<3:0>        | 1000 = Reserved                                                                        |

| OCFA           | OCFAR           | OCFAR<3:0>       | •<br>•<br>1111 = Reserved                                                              |

Note 1: This pin is not available on 28-pin devices.

2: This pin is only available on 44-pin devices.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 02:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | —                 | -                 | -                 | _                 | _                 | -                | —                |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | 0N <sup>(1)</sup> | —                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

## REGISTER 15-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER

## Legend:

| R = Readable bit                        | W = Writable bit | U = Unimplemented bit |                  |

|-----------------------------------------|------------------|-----------------------|------------------|

| -n = Bit Value at POR: ('0', '1', x = u | nknown)          | P = Programmable bit  | r = Reserved bit |

| bit 31-16 | Unimplemented: Read as '0'                                                                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ON:</b> Input Capture Module Enable bit <sup>(1)</sup>                                                                                                                                |

|           | 1 = Module is enabled                                                                                                                                                                    |

|           | 0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications                                                                                   |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 13    | SIDL: Stop in Idle Control bit                                                                                                                                                           |

|           | <ul> <li>1 = Halt in Idle mode</li> <li>0 = Continue to operate in Idle mode</li> </ul>                                                                                                  |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 9     | FEDGE: First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)                                                                                                               |

|           | 1 = Capture rising edge first                                                                                                                                                            |

|           | 0 = Capture falling edge first                                                                                                                                                           |

| bit 8     | C32: 32-bit Capture Select bit                                                                                                                                                           |

|           | 1 = 32-bit timer resource capture                                                                                                                                                        |

|           | 0 = 16-bit timer resource capture                                                                                                                                                        |

| bit 7     | ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')                                                                                                    |

|           | 0 = Timer3 is the counter source for capture                                                                                                                                             |

|           | 1 = Timer2 is the counter source for capture                                                                                                                                             |

| bit 6-5   | ICI<1:0>: Interrupt Control bits                                                                                                                                                         |

|           | <ul> <li>11 = Interrupt on every fourth capture event</li> <li>10 = Interrupt on every third capture event</li> </ul>                                                                    |

|           | 01 = Interrupt on every second capture event                                                                                                                                             |

|           | 00 = Interrupt on every capture event                                                                                                                                                    |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                                                 |

|           | 1 = Input capture overflow has occurred                                                                                                                                                  |

|           | 0 = No input capture overflow has occurred                                                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                                             |

|           | <ul> <li>1 = Input capture buffer is not empty; at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                                        |

| Note 1:   | When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. |

|           | STOCEN Gyole infinediately following the instruction that deals the module's ON bit.                                                                                                     |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   |                   | _                 | _                 | _                 | -                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 | _                 | -                 | -                 | _                 | _                | —                |

| 45.0         | R-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | BUSY              | IRQM              | <1:0>             | INCM              | <1:0>             | _                 | MODE             | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAITB             | <1:0> <b>(1)</b>  |                   | WAITM             | <3:0>(1)          |                   | WAITE            | <1:0>(1)         |

#### REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER

#### Legend:

| 3                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **BUSY:** Busy bit (Master mode only)

- 1 = Port is busy

- 0 = Port is not busy

#### bit 14-13 IRQM<1:0>: Interrupt Request Mode bits

- 11 = Reserved, do not use

- 10 = Interrupt generated when Read Buffer 3 is read or Write Buffer 3 is written (Buffered PSP mode) or on a read or write operation when PMA<1:0> =11 (Addressable Slave mode only)

- 01 = Interrupt generated at the end of the read/write cycle

- 00 = No Interrupt generated

#### bit 12-11 INCM<1:0>: Increment Mode bits

- 11 = Slave mode read and write buffers auto-increment (MODE<1:0> = 00 only)

- 10 = Decrement ADDR<10:2> and ADDR<14> by 1 every read/write cycle<sup>(2)</sup>

- 01 = Increment ADDR<10:2> and ADDR<14> by 1 every read/write cycle<sup>(2)</sup>

- 00 = No increment or decrement of address

- bit 10 Unimplemented: Read as '0'

- bit 9-8 MODE<1:0>: Parallel Port Mode Select bits

- 11 = Master mode 1 (PMCS1, PMRD/PMWR, PMENB, PMA<x:0>, and PMD<7:0>)

- 10 = Master mode 2 (PMCS1, PMRD, PMWR, PMA<x:0>, and PMD<7:0>)

- 01 = Enhanced Slave mode, control signals (PMRD, PMWR, PMCS1, PMD<7:0>, and PMA<1:0>)

- 00 = Legacy Parallel Slave Port, control signals (PMRD, PMWR, PMCS1, and PMD<7:0>)

- bit 7-6 WAITB<1:0>: Data Setup to Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Data wait of 4 TPB; multiplexed address phase of 4 TPB

- 10 = Data wait of 3 TPB; multiplexed address phase of 3 TPB

- 01 = Data wait of 2 TPB; multiplexed address phase of 2 TPB

- 00 = Data wait of 1 TPB; multiplexed address phase of 1 TPB (default)

#### bit 5-2 WAITM<3:0>: Data Read/Write Strobe Wait States bits<sup>(1)</sup>

- 1111 = Wait of 16 Трв •

- . 0001 = Wait of 2 Трв 0000 = Wait of 1 Трв (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

#### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED) bit 24 EDG1STAT: Edge1 Status bit Indicates the status of Edge1 and can be written to control edge source 1 = Edge1 has occurred 0 = Edge1 has not occurred EDG2MOD: Edge2 Edge Sampling Select bit bit 23 1 = Input is edge-sensitive 0 = Input is level-sensitive bit 22 EDG2POL: Edge 2 Polarity Select bit 1 = Edge2 programmed for a positive edge response 0 = Edge2 programmed for a negative edge response bit 21-18 EDG2SEL<3:0>: Edge 2 Source Select bits 1111 = C3OUT pin is selected 1110 = C2OUT pin is selected 1101 = C1OUT pin is selected 1100 = PBCLK clock is selected 1011 = IC3 Capture Event is selected 1010 = IC2 Capture Event is selected 1001 = IC1 Capture Event is selected 1000 = CTED13 pin is selected 0111 = CTED12 pin is selected 0110 = CTED11 pin is selected 0101 = CTED10 pin is selected 0100 = CTED9 pin is selected 0011 = CTED1 pin is selected 0010 = CTED2 pin is selected 0001 = OC1 Compare Event is selected 0000 = Timer1 Event is selected bit 17-16 Unimplemented: Read as '0' bit 15 **ON:** ON Enable bit 1 = Module is enabled 0 = Module is disabled bit 14 Unimplemented: Read as '0' bit 13 CTMUSIDL: Stop in Idle Mode bit 1 = Discontinue module operation when the device enters Idle mode 0 = Continue module operation when the device enters Idle mode TGEN: Time Generation Enable bit<sup>(1)</sup> bit 12 1 = Enables edge delay generation 0 = Disables edge delay generation bit 11 EDGEN: Edge Enable bit 1 = Edges are not blocked 0 = Edges are blocked

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

## TABLE 30-14: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHA        |         | STICS                                                       | (unless of        | therwise | ture -40°C≤        | TA ≤ +8  | <b>o 3.6V</b><br>5°C for Industrial<br>05°C for V-temp          |

|---------------|---------|-------------------------------------------------------------|-------------------|----------|--------------------|----------|-----------------------------------------------------------------|

| Param.<br>No. | Symbol  | Characteristics                                             | Min.              | Тур.     | Max.               | Comments |                                                                 |

| D312          | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time | _                 | _        | 10                 | μs       | See Note 1                                                      |

| D313          | DACREFH | CVREF Input Voltage                                         | AVss              | _        | AVDD               | V        | CVRSRC with CVRSS = 0                                           |

|               |         | Reference Range                                             | VREF-             | _        | VREF+              | V        | CVRSRC with CVRSS = 1                                           |

| D314          | DVREF   | CVREF Programmable<br>Output Range                          | 0                 | _        | 0.625 x<br>DACREFH | V        | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                 |

|               |         |                                                             | 0.25 x<br>DACREFH | _        | 0.719 x<br>DACREFH | V        | 0.25 x DACREFH to 0.719<br>DACREFH with<br>DACREFH/32 step size |

| D315          | DACRES  | Resolution                                                  | —                 | _        | DACREFH/24         |          | CVRCON <cvrr> = 1</cvrr>                                        |

|               |         |                                                             | _                 | —        | DACREFH/32         | _        | CVRCON <cvrr> = 0</cvrr>                                        |

| D316 DACACC   |         | Absolute Accuracy <sup>(2)</sup>                            |                   | _        | 1/4                | LSB      | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                         |

|               |         |                                                             |                   | _        | 1/2                | LSB      | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                         |

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

**2:** These parameters are characterized but not tested.

#### TABLE 30-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHA                               | DC CHARACTERISTICS |                                 |      | ard Operat<br>s otherwis<br>ing temper | e stated<br>ature | <b>1)</b><br>-40°C ≤ <sup>°</sup> | : <b>2.3V to 3.6V</b><br>TA $\leq$ +85°C for Industrial<br>TA $\leq$ +105°C for V-temp             |

|--------------------------------------|--------------------|---------------------------------|------|----------------------------------------|-------------------|-----------------------------------|----------------------------------------------------------------------------------------------------|

| Param.<br>No. Symbol Characteristics |                    |                                 | Min. | Typical                                | Max.              | Units                             | Comments                                                                                           |

| D321                                 | Cefc               | External Filter Capacitor Value | 8    | 10                                     |                   | μF                                | Capacitor must be low series<br>resistance (1 ohm). Typical<br>voltage on the VCAP pin is<br>1.8V. |

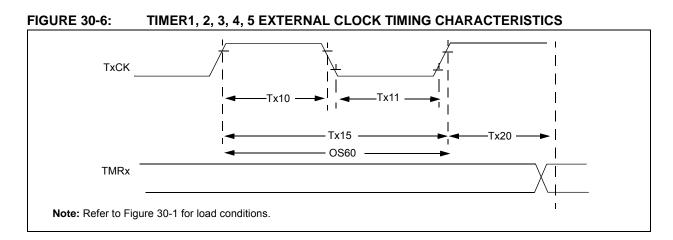

## TABLE 30-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHA        | ARACTERIS                | TICS <sup>(1)</sup>                                         |                               | (unl | andard Operating Conditions: 2.3V to 3.6V<br>hless otherwise stated)<br>berating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |         |      |       |                               |  |

|---------------|--------------------------|-------------------------------------------------------------|-------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|-------------------------------|--|

| Param.<br>No. | Symbol Characteristics 4 |                                                             |                               |      | Min.                                                                                                                                                                                                     | Typical | Max. | Units | Conditions                    |  |

| TA10          | T⊤xH                     | TxCK<br>High Time                                           | Synchronow with presca        |      | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns                                                                                                                                                                        | —       | —    | ns    | Must also meet parameter TA15 |  |

|               |                          |                                                             | Asynchrono<br>with presca     |      | 10                                                                                                                                                                                                       | —       | _    | ns    | —                             |  |

| TA11          | T⊤xL                     | TxCK<br>Low Time                                            | Synchronor<br>with presca     |      | [(12.5 ns or 1 Трв)/N]<br>+ 25 ns                                                                                                                                                                        | —       | _    | ns    | Must also meet parameter TA15 |  |

|               |                          |                                                             | Asynchrono<br>with presca     |      | 10                                                                                                                                                                                                       | _       | _    | ns    | —                             |  |

| TA15          | ΤτχΡ                     | TxCK<br>Input Period                                        | Synchrono<br>with presca      |      | [(Greater of 25 ns or<br>2 Трв)/N] + 30 ns                                                                                                                                                               | -       | _    | ns    | VDD > 2.7V                    |  |

|               |                          |                                                             |                               |      | [(Greater of 25 ns or<br>2 TPB)/N] + 50 ns                                                                                                                                                               | -       | —    | ns    | VDD < 2.7V                    |  |

|               |                          |                                                             | Asynchrono<br>with presca     |      | 20                                                                                                                                                                                                       | -       | —    | ns    | VDD > 2.7V<br>(Note 3)        |  |

|               |                          |                                                             |                               |      | 50                                                                                                                                                                                                       | -       | _    | ns    | VDD < 2.7V<br>(Note 3)        |  |

| OS60          | FT1                      | SOSC1/T1C<br>Input Freque<br>(oscillator en<br>the TCS (T10 | ncy Range<br>abled by setting |      | 32                                                                                                                                                                                                       | —       | 100  | kHz   | -                             |  |

| TA20          | TCKEXTMRL                | Delay from E<br>Clock Edge t<br>Increment                   |                               | К    |                                                                                                                                                                                                          | —       | 1    | Трв   | —                             |  |

**Note 1:** Timer1 is a Type A timer.

**2:** This parameter is characterized, but not tested in manufacturing.

**3:** N = Prescale Value (1, 8, 64, 256).

## TABLE 31-8:SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |          |                                 | (unless o | otherwise | e stated<br>ture -40 | l)<br>°C ≤ TA : | : <b>2.3V to 3.6V</b><br>≤ +85°C for Industrial<br>≤ +105°C for V-temp |

|--------------------|----------|---------------------------------|-----------|-----------|----------------------|-----------------|------------------------------------------------------------------------|

| Param.<br>No.      | Min.     | Тур.                            | Max.      | Units     | Conditions           |                 |                                                                        |

| MSP70              | TscL     | SCKx Input Low Time (Note 1,2)  | Tsck/2    |           | _                    | ns              | _                                                                      |

| MSP71              | TscH     | SCKx Input High Time (Note 1,2) | Tsck/2    | —         |                      | ns              | —                                                                      |

| MSP51              | TssH2doZ | 5                               |           | 25        | ns                   | —               |                                                                        |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns.

## TABLE 31-9: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA                                            | AC CHARACTERISTICS |                                 |        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |       |            |   |  |

|---------------------------------------------------|--------------------|---------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|---|--|

| Param.<br>No.SymbolCharacteristicsMin.TypicalMax. |                    |                                 |        | Max.                                                                                                                                              | Units | Conditions |   |  |

| SP70                                              | TscL               | SCKx Input Low Time (Note 1,2)  | Tsck/2 |                                                                                                                                                   |       | ns         |   |  |

| SP71                                              | TscH               | SCKx Input High Time (Note 1,2) | Tsck/2 | _                                                                                                                                                 | _     | ns         | — |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns.

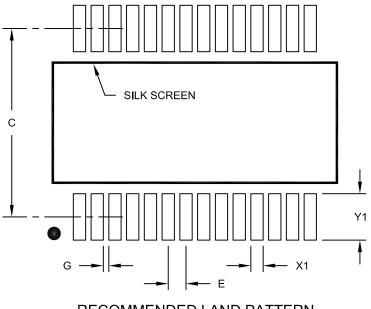

## 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | Ν                | /ILLIMETER | S |      |  |

|--------------------------|------------------|------------|---|------|--|

| Dimension                | Dimension Limits |            |   | MAX  |  |

| Contact Pitch            | E                | 0.65 BSC   |   |      |  |

| Contact Pad Spacing      | С                | 7.20       |   |      |  |

| Contact Pad Width (X28)  | X1               |            |   | 0.45 |  |

| Contact Pad Length (X28) | Y1               |            |   | 1.75 |  |

| Distance Between Pads    | G                | 0.20       |   |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

## **Revision E (October 2012)**

All singular pin diagram occurrences of CVREF were changed to: CVREFOUT. In addition, minor text and formatting changes were incorporated throughout the document.

All major changes are referenced by their respective section in Table A-4.

| TABLE A-4: | MAJOR SECTION UPDATES |

|------------|-----------------------|

|------------|-----------------------|

| Section                                                                                                                                | Update Description                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to<br>128 KB Flash and 32 KB SRAM)<br>with Audio and Graphics<br>Interfaces, USB, and Advanced<br>Analog" | Updated the following feature sections: <ul> <li>"Operating Conditions"</li> <li>"Communication Interfaces"</li> </ul>                                                                                                                                       |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                               | Removed Section 2.8 "Configuration of Analog and Digital Pins During ICSP Operations".                                                                                                                                                                       |

| 3.0 "CPU"                                                                                                                              | Removed references to GPR shadow registers in <b>3.1 "Features"</b> and <b>3.2.1 "Execution Unit"</b> .                                                                                                                                                      |

| 4.0 "Memory Organization"                                                                                                              | Updated the BRG bit range in the SPI1 and SPI2 Register Map (see Table 4-8).<br>Added the PWP<6> bit to the Device Configuration Word Summary<br>(see Table 4-17).                                                                                           |

| 5.0 "Flash Program Memory"                                                                                                             | Added a note with Flash page size and row size information.                                                                                                                                                                                                  |

| 7.0 "Interrupt Controller"                                                                                                             | Updated the TPC<2:0> bit definitions (see Register 7-1).<br>Updated the IPTMR<31:0> bit definition (see Register 7-3).                                                                                                                                       |

| 8.0 "Oscillator Configuration"                                                                                                         | Updated the PIC32MX1XX/2XX Family Clock Diagram (see Figure 8-1).<br>Updated the RODIV<14:0> bit definitions (see Register 8-3).                                                                                                                             |

| 10.0 "USB On-The-Go (OTG)"                                                                                                             | Updated the Notes in the USB Interface Diagram (see Figure 10-1).                                                                                                                                                                                            |

| 18.0 "Universal Asynchronous<br>Receiver Transmitter (UART)"                                                                           | Updated the baud rate range in the list of primary features.                                                                                                                                                                                                 |