Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 16KB (16K × 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx110f016bt-v-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

|                     |      |                                    |                  | Rem             | appab                                  | le Pe | riphe                | erals                              |                    |                     |                  |     | (                                        |      | ls)                          |      |          |      |                                 |

|---------------------|------|------------------------------------|------------------|-----------------|----------------------------------------|-------|----------------------|------------------------------------|--------------------|---------------------|------------------|-----|------------------------------------------|------|------------------------------|------|----------|------|---------------------------------|

| Device              | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/Compare | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | I <sup>2</sup> C | dMq | DMA Channels<br>(Programmable/Dedicated) | CTMU | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | Packages                        |

| PIC32MX210F016B     | 28   | 16+3                               | 4                | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX210F016C     | 36   | 16+3                               | 4                | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 25       | Y    | VTLA                            |

| PIC32MX210F016D     | 44   | 16+3                               | 4                | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX220F032B     | 28   | 32+3                               | 8                | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX220F032C     | 36   | 32+3                               | 8                | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA                            |

| PIC32MX220F032D     | 44   | 32+3                               | 8                | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX230F064B     | 28   | 64+3                               | 16               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F064C     | 36   | 64+3                               | 16               | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA                            |

| PIC32MX230F064D     | 44   | 64+3                               | 16               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX250F128B     | 28   | 128+3                              | 32               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX250F128C     | 36   | 128+3                              | 32               | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA<br>VTLA,                   |

| PIC32MX250F128D     | 44   | 128+3                              | 32               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | TQFP,<br>QFN                    |

| PIC32MX230F256B     | 28   | 256+3                              | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F256D     | 44   | 256+3                              | 16               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256B     | 28   | 256+3                              | 64               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX270F256D     | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256DB(4) | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

## TABLE 2: PIC32MX2XX 28/36/44-PIN USB FAMILY FEATURES

Note 1: This device features 3 KB of boot Flash memory.

**2:** Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

4: This PIC32 device is targeted to specific audio software packages that are tracked for licensing royalty purposes. All peripherals and electrical characteristics are identical to their corresponding base part numbers.

# TABLE 11: PIN NAMES FOR 44-PIN GENERAL PURPOSE DEVICES

# 44-PIN TQFP (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX110F016D PIC32MX120F032D PIC32MX130F064D PIC32MX130F256D PIC32MX150F128D PIC32MX170F256D

44

1

| Pin # | Full Pin Name                                  | Pin # | Full Pin Name                        |

|-------|------------------------------------------------|-------|--------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                       | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 |

| 2     | RPC6/PMA1/RC6                                  | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   |

| 3     | RPC7/PMA0/RC7                                  | 25    | AN6/RPC0/RC0                         |

| 4     | RPC8/PMA5/RC8                                  | 26    | AN7/RPC1/RC1                         |

| 5     | RPC9/CTED7/PMA6/RC9                            | 27    | AN8/RPC2/PMA2/RC2                    |

| 6     | Vss                                            | 28    | VDD                                  |

| 7     | VCAP                                           | 29    | Vss                                  |

| 8     | PGED2/RPB10/CTED11/PMD2/RB10                   | 30    | OSC1/CLKI/RPA2/RA2                   |

| 9     | PGEC2/RPB11/PMD1/RB11                          | 31    | OSC2/CLKO/RPA3/RA3                   |

| 10    | AN12/PMD0/RB12                                 | 32    | TDO/RPA8/PMA8/RA8                    |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                     | 33    | SOSCI/RPB4/RB4                       |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10           | 34    | SOSCO/RPA4/T1CK/CTED9/RA4            |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7       | 35    | TDI/RPA9/PMA9/RA9                    |

| 14    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 | 36    | RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          | 37    | RPC4/PMA4/RC4                        |

| 16    | AVss                                           | 38    | RPC5/PMA3/RC5                        |

| 17    | AVDD                                           | 39    | Vss                                  |

| 18    | MCLR                                           | 40    | VDD                                  |

| 19    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          | 41    | PGED3/RPB5/PMD7/RB5                  |

| 20    | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                | 42    | PGEC3/RPB6/PMD6/RB6                  |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           | 43    | RPB7/CTED3/PMD5/INT0/RB7             |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          | 44    | RPB8/SCL1/CTED10/PMD4/RB8            |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

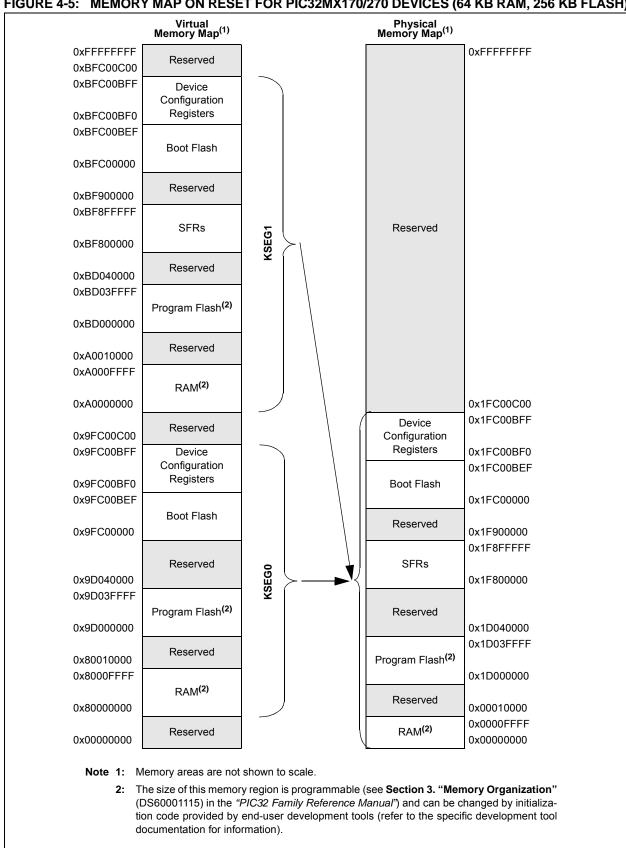

## FIGURE 4-5: MEMORY MAP ON RESET FOR PIC32MX170/270 DEVICES (64 KB RAM, 256 KB FLASH)

## TABLE 4-1: SFR MEMORY MAP

|                           | Virtual A | ddress          |  |  |

|---------------------------|-----------|-----------------|--|--|

| Peripheral                | Base      | Offset<br>Start |  |  |

| Watchdog Timer            |           | 0x0000          |  |  |

| RTCC                      |           | 0x0200          |  |  |

| Timer1-5                  |           | 0x0600          |  |  |

| Input Capture 1-5         |           | 0x2000          |  |  |

| Output Compare 1-5        |           | 0x3000          |  |  |

| IC1 and IC2               |           | 0x5000          |  |  |

| SPI1 and SPI2             |           | 0x5800          |  |  |

| UART1 and UART2           |           | 0x6000          |  |  |

| PMP                       |           | 0x7000          |  |  |

| ADC                       | 0xBF80    | 0x9000          |  |  |

| CVREF                     |           | 0x9800          |  |  |

| Comparator                |           | 0xA000          |  |  |

| CTMU                      |           | 0xA200          |  |  |

| Oscillator                |           | 0xF000          |  |  |

| Device and Revision ID    |           | 0xF220          |  |  |

| Peripheral Module Disable |           | 0xF240          |  |  |

| Flash Controller          |           | 0xF400          |  |  |

| Reset                     |           | 0xF600          |  |  |

| PPS                       |           | 0xFA04          |  |  |

| Interrupts                |           | 0x1000          |  |  |

| Bus Matrix                |           | 0x2000          |  |  |

| DMA                       | 0xBF88    | 0x3000          |  |  |

| USB                       |           | 0x5050          |  |  |

| PORTA-PORTC               |           | 0x6000          |  |  |

| Configuration             | 0xBFC0    | 0x0BF0          |  |  |

| Bit<br>Range |           |           | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |

|--------------|-----------|-----------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|

| 24.04        | U-0       | U-0       | U-0               | U-0               | U-0               | U-0               | U-0                | U-0                |  |

| 31:24        | _         | _         | _                 | _                 | _                 |                   | -                  | —                  |  |

| 22:16        | U-0       | U-0       | U-0               | U-0               | U-0               | U-0               | U-0                | U-0                |  |

| 23:16        | _         | _         | _                 | _                 | _                 |                   | -                  | —                  |  |

| 45.0         | U-0       | U-0       | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |  |

| 15:8         |           | _         | _                 | -                 | _                 | _                 | CMR                | VREGS              |  |

| 7.0          | R/W-0, HS | R/W-0, HS | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |  |

| 7:0          | EXTR      | SWR       | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |  |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Legend:           | HS = Set by hardware |                           |                    |

|-------------------|----------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | x = Bit is unknown |

## bit 31-10 Unimplemented: Read as '0'

| bit 9 | CMR: Configuration Mismatch Reset Flag bit             |

|-------|--------------------------------------------------------|

|       | 1 = Configuration mismatch Reset has occurred          |

|       | 0 = Configuration mismatch Reset has not occurred      |

| bit 8 | VREGS: Voltage Regulator Standby Enable bit            |

|       | 1 = Regulator is enabled and is on during Sleep mode   |

|       | 0 = Regulator is disabled and is off during Sleep mode |

| bit 7 | EXTR: External Reset (MCLR) Pin Flag bit               |

|       | 1 = Master Clear (pin) Reset has occurred              |

|       | 0 = Master Clear (pin) Reset has not occurred          |

| bit 6 | SWR: Software Reset Flag bit                           |

|       | 1 = Software Reset was executed                        |

|       | 0 = Software Reset as not executed                     |

| bit 5 | Unimplemented: Read as '0'                             |

| bit 4 | WDTO: Watchdog Timer Time-out Flag bit                 |

|       | 1 = WDT Time-out has occurred                          |

|       | 0 = WDT Time-out has not occurred                      |

| bit 3 | SLEEP: Wake From Sleep Flag bit                        |

|       | 1 = Device was in Sleep mode                           |

|       | 0 = Device was not in Sleep mode                       |

| bit 2 | IDLE: Wake From Idle Flag bit                          |

|       | 1 = Device was in Idle mode                            |

|       | 0 = Device was not in Idle mode                        |

| bit 1 | BOR: Brown-out Reset Flag bit <sup>(1)</sup>           |

|       | 1 = Brown-out Reset has occurred                       |

|       | 0 = Brown-out Reset has not occurred                   |

| bit 0 | POR: Power-on Reset Flag bit <sup>(1)</sup>            |

|       | 1 = Power-on Reset has occurred                        |

|       | 0 = Power-on Reset has not occurred                    |

|       |                                                        |

**Note 1:** User software must clear this bit to view next detection.

# 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the features<br>of the PIC32MX1XX/2XX 28/36/44-pin<br>Family of devices. It is not intended to be<br>a comprehensive reference source. To<br>complement the information in this data |  |  |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | sheet, refer to Section 6. "Oscillator                                                                                                                                                                          |  |  |  |  |  |  |  |

|       | Configuration" (DS60001112), which is                                                                                                                                                                           |  |  |  |  |  |  |  |

|       | available from the Documentation >                                                                                                                                                                              |  |  |  |  |  |  |  |

|       | Reference Manual section of the                                                                                                                                                                                 |  |  |  |  |  |  |  |

|       | Microchip PIC32 web site                                                                                                                                                                                        |  |  |  |  |  |  |  |

|       | (www.microchip.com/pic32).                                                                                                                                                                                      |  |  |  |  |  |  |  |

The PIC32MX1XX/2XX 28/36/44-pin Family oscillator system has the following modules and features:

- Four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

# REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| bit 3   | CF: Clock Fail Detect bit                                                                                                                                      |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = FSCM has detected a clock failure                                                                                                                          |

|         | 0 = No clock failure has been detected                                                                                                                         |

| bit 2   | UFRCEN: USB FRC Clock Enable bit <sup>(1)</sup>                                                                                                                |

|         | <ul> <li>1 = Enable the FRC as the clock source for the USB clock source</li> <li>0 = Use the Primary Oscillator or USB PLL as the USB clock source</li> </ul> |

| bit 1   | SOSCEN: Secondary Oscillator (Sosc) Enable bit                                                                                                                 |

|         | 1 = Enable the Secondary Oscillator                                                                                                                            |

|         | 0 = Disable the Secondary Oscillator                                                                                                                           |

| bit 0   | OSWEN: Oscillator Switch Enable bit                                                                                                                            |

|         | <ul> <li>1 = Initiate an oscillator switch to selection specified by NOSC&lt;2:0&gt; bits</li> <li>0 = Oscillator switch is complete</li> </ul>                |

| Note 1: | This bit is only available on PIC32MX2XX devices.                                                                                                              |

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

# TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       | - /   |       |      |      | Bit  | s    |      |          |        |        |         |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5200                        |                                 | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |      | _    | —    | —        | —      | _      | —       | —      | 0000       |

| 5390 U1EP9                  | UIEF9                           | 15:0      |       |       | —     | —     | —     | —     | _    | —    |      |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5240                        | 50.00 1145040                   | 31:16     | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | —        | _      | _      | —       | _      | 0000       |

| 53A0 U1EP10                 | UIEPIU                          | 15:0      |       | _     | _     | -     | _     | _     | _    | -    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 53BU                        | UIEPII                          | 15:0      | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEFIZ                          | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEF 13                         | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     |       | _     | _     |       | -     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0 U1EF                   | U1EP14                          | 15:0      | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | —        | _      | _      | _       | _      | 0000       |

| 53F0 U1                     | U1EP15                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | —    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                              | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------------|------------------|--|

| 21.24        | U-0                                           | U-0              |  |

| 31:24        |                   | _                 | —                 | —                 | _                 | —                 | _                                             | _                |  |

| 22:16        | U-0                                           | U-0              |  |

| 23:16        |                   | _                 | _                 | —                 |                   |                   | _                                             |                  |  |

| 15:0         | U-0                                           | U-0              |  |

| 15:8         |                   | —                 | —                 | —                 | —                 | -                 | —                                             | —                |  |

|              | R/W-0                                         | R/W-0            |  |

| 7:0          | BTSEE BMXEE       |                   | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup><br>EOFEE <sup>(2)</sup> | PIDEE            |  |

# REGISTER 10-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

## Legend:

| 0                 |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

## bit 31-8 Unimplemented: Read as '0'

|       | •                                                         |

|-------|-----------------------------------------------------------|

| bit 7 | BTSEE: Bit Stuff Error Interrupt Enable bit               |

|       | 1 = BTSEF interrupt is enabled                            |

|       | 0 = BTSEF interrupt is disabled                           |

| bit 6 | BMXEE: Bus Matrix Error Interrupt Enable bit              |

|       | 1 = BMXEF interrupt is enabled                            |

|       | 0 = BMXEF interrupt is disabled                           |

| bit 5 | DMAEE: DMA Error Interrupt Enable bit                     |

|       | 1 = DMAEF interrupt is enabled                            |

|       | 0 = DMAEF interrupt is disabled                           |

| bit 4 | BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit |

|       | 1 = BTOEF interrupt is enabled                            |

|       | 0 = BTOEF interrupt is disabled                           |

| bit 3 | DFN8EE: Data Field Size Error Interrupt Enable bit        |

|       | 1 = DFN8EF interrupt is enabled                           |

|       | 0 = DFN8EF interrupt is disabled                          |

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- bit 1 CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup>

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 PIDEE: PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

- Note 1: Device mode.

- 2: Host mode.

Note: For an interrupt to propagate the USBIF register, the UERRIE (U1IE<1>) bit must be set.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | -                 | -                 | —                 | -                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | —                 |                   | _                 | _                 |                   | _                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                   |                   |                   | CNT               | <7:0>             |                   |                  |                  |

# REGISTER 10-16: U1SOF: USB SOF THRESHOLD REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-8 Unimplemented: Read as '0'

- bit 7-0 CNT<7:0>: SOF Threshold Value bits Typical values of the threshold are:

- 01001010 = 64-byte packet 00101010 = **32-byte packet**

- 00011010 = **16-byte packet**

- 00010010 = 8-byte packet

## REGISTER 10-17: U1BDTP1: USB BUFFER DESCRIPTOR TABLE PAGE 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | -                 | -                 | -                 | -                 | -                 | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | -                 |                   |                   |                   |                   |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | -                 | -                 | -                 |                   |                   |                  | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |

|              |                   |                   | B                 | DTPTRL<15:9       | )>                |                   |                  | _                |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

## bit 31-8 Unimplemented: Read as '0'

bit 7-1 BDTPTRL<15:9>: Buffer Descriptor Table Base Address bits This 7-bit value provides address bits 15 through 9 of the Buffer Descriptor Table base address, which defines the starting location of the Buffer Descriptor Table in system memory. The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

bit 0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                   | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                   | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | _                 | _                 | _                 | —                 | _                 | —                | _                |

| 7:0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

|              | _                   | SWDTPS<4:0>       |                   |                   |                   |                   | WDTWINEN         | WDTCLR           |

# REGISTER 14-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                        |                    |

|-------------------|-----------------------------------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit                              | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared   | x = Bit is unknown |

## bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration

- 0 = Disable the WDT if it was enabled in software

- bit 14-7 Unimplemented: Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- bit 0 **WDTCLR:** Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- **Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | _                 | —                 | -                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 |                   | —                 | —                 | -                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |

## REGISTER 19-1: UXMODE: UARTX MODE REGISTER

# Legend:

| Logona.           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

## bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by the UEN<1:0> and UTXEN control bits.

- 0 = UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal.

- bit 14 Unimplemented: Read as '0'

## bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- $1 = \overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

- bit 10 Unimplemented: Read as '0'

- bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up enabled

- 0 = Wake-up disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | CH0NB             | _                 | _                 | —                 | CH0SB<3:0>        |                   |                  |                  |  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | CH0NA             | _                 | _                 | —                 | CH0SA<3:0>        |                   |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         |                   | _                 | _                 | —                 | _                 | —                 | —                | —                |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          | —                 |                   |                   | —                 | _                 | _                 | _                | _                |  |

# REGISTER 22-4: AD1CHS: ADC INPUT SELECT REGISTER

CHONB: Negative Input Select bit for Sample B

# Legend:

bit 31

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

|        |                      | <ul> <li>1 = Channel 0 negative input is AN1</li> <li>0 = Channel 0 negative input is VREFL</li> </ul>                                                                                                                                                                                                                                          |

|--------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30 | -28                  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

| bit 27 | -24                  | CH0SB<3:0>: Positive Input Select bits for Sample B                                                                                                                                                                                                                                                                                             |

|        |                      | <pre>1111 = Channel 0 positive input is Open<sup>(1)</sup> 1110 = Channel 0 positive input is IVREF<sup>(2)</sup> 1101 = Channel 0 positive input is CTMU temperature sensor (CTMUT)<sup>(3)</sup> 1100 = Channel 0 positive input is AN12<sup>(4)</sup></pre>                                                                                  |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | 0001 = Channel 0 positive input is AN1<br>0000 = Channel 0 positive input is AN0                                                                                                                                                                                                                                                                |

| bit 23 |                      | CH0NA: Negative Input Select bit for Sample A Multiplexer Setting <sup>(2)</sup>                                                                                                                                                                                                                                                                |

|        |                      | <ul><li>1 = Channel 0 negative input is AN1</li><li>0 = Channel 0 negative input is VREFL</li></ul>                                                                                                                                                                                                                                             |

| bit 22 | -20                  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

| bit 19 | -16                  | CH0SA<3:0>: Positive Input Select bits for Sample A Multiplexer Setting<br>1111 = Channel 0 positive input is Open <sup>(1)</sup><br>1110 = Channel 0 positive input is IVREF <sup>(2)</sup><br>1101 = Channel 0 positive input is CTMU temperature (CTMUT) <sup>(3)</sup><br>1100 = Channel 0 positive input is AN12 <sup>(4)</sup>            |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | •                                                                                                                                                                                                                                                                                                                                               |

|        |                      | 0001 = Channel 0 positive input is AN1<br>0000 = Channel 0 positive input is AN0                                                                                                                                                                                                                                                                |

| bit 15 | -0                   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                      |

| Note   | 1:<br>2:<br>3:<br>4: | This selection is only used with CTMU capacitive and time measurement.<br>See <b>Section 24.0 "Comparator Voltage Reference (CVREF)"</b> for more information.<br>See <b>Section 25.0 "Charge Time Measurement Unit (CTMU)"</b> for more information.<br>AN12 is only available on 44-pin devices. AN6-AN8 are not available on 28-pin devices. |

|        |                      |                                                                                                                                                                                                                                                                                                                                                 |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|--|

| 24.04        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1                   | R/P              | R/P              |  |

| 31:24        | _                 | _                 | _                 | _                 | —                 | —                     | FWDTWI           | NSZ<1:0>         |  |

| 00.40        | R/P               | R/P               | r-1               | R/P               | R/P               | R/P                   | R/P              | R/P              |  |

| 23:16        | FWDTEN            | WINDIS            | _                 | WDTPS<4:0>        |                   |                       |                  |                  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-1               | R/P                   | R/P              | R/P              |  |

| 15:8         | FCKSM             | 1<1:0>            | FPBDI             | V<1:0>            | —                 | OSCIOFNC POSCMOD<1:0> |                  |                  |  |

| 7.0          | R/P               | r-1               | R/P               | r-1               | r-1               | R/P                   | R/P              | R/P              |  |

| 7:0          | IESO              | _                 | FSOSCEN           | _                 | —                 | F                     | NOSC<2:0>        |                  |  |

## REGISTER 27-2: DEVCFG1: DEVICE CONFIGURATION WORD 1

| Legend:           | r = Reserved bit | P = Programmable bit               |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

## bit 31-26 Reserved: Write '1'

bit 25-24 FWDTWINSZ<1:0>: Watchdog Timer Window Size bits

- 11 = Window size is 25%

- 10 = Window size is 37.5%

- 01 = Window size is 50%

- 00 = Window size is 75%

## bit 23 FWDTEN: Watchdog Timer Enable bit

- 1 = Watchdog Timer is enabled and cannot be disabled by software

- 0 = Watchdog Timer is not enabled; it can be enabled in software

## bit 22 WINDIS: Watchdog Timer Window Enable bit

- 1 = Watchdog Timer is in non-Window mode

- 0 = Watchdog Timer is in Window mode

## bit 21 Reserved: Write '1'

## bit 20-16 WDTPS<4:0>: Watchdog Timer Postscale Select bits

| 10100 <b>= 1:1048576</b>                                     |

|--------------------------------------------------------------|

| 10011 <b>= 1:524288</b>                                      |

| 10010 <b>= 1:262144</b>                                      |

| 10001 <b>= 1:131072</b>                                      |

| 10000 <b>= 1:65536</b>                                       |

| 01111 <b>= 1:32768</b>                                       |

| 01110 <b>= 1:16384</b>                                       |

| 01101 = 1:8192                                               |

| 01100 = 1:4096                                               |

| 01011 = <b>1:2048</b>                                        |

| 01010 = 1:1024                                               |

| 01001 = 1:512                                                |

| 01000 <b>= 1:256</b>                                         |

| 00111 <b>= 1:128</b>                                         |

| 00110 <b>= 1:64</b>                                          |

| 00101 <b>= 1:32</b>                                          |

| 00100 <b>= 1:16</b>                                          |

| 00011 <b>= 1:8</b>                                           |

| 00010 = 1:4                                                  |

| 00001 = 1:2                                                  |

| 00000 = 1:1                                                  |

| All other combinations not shown result in operation = 10100 |

| ······································                       |

**Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

# REGISTER 27-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

## bit 15-14 FCKSM<1:0>: Clock Switching and Monitor Selection Configuration bits

- 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

- 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

- 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

- bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output disabled

- 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

## bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary Oscillator is disabled

- 10 = HS Oscillator mode is selected

- 01 = XT Oscillator mode is selected

- 00 = External Clock mode is selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 **Reserved:** Write '1'

- bit 5 **FSOSCEN:** Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 Reserved: Write '1'

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup>

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the POSC (POSCMOD = 11) when using this oscillator source.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-----------------------|------------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                     | —                      | _                 |                   | _                | —                |

| 22:16        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | —                 | -                     | —                      | _                 | -                 | -                | —                |

| 45.0         | U-0               | U-0               | R/W-0                 | R/W-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | —                 | IOLOCK <sup>(1)</sup> | PMDLOCK <sup>(1)</sup> |                   |                   |                  | —                |

| 7.0          | U-0               | U-0               | U-0                   | U-0                    | R/W-1             | U-0               | U-1              | R/W-1            |

| 7:0          | _                 |                   |                       | _                      | JTAGEN            |                   | _                | TDOEN            |

## **REGISTER 27-5: CFGCON: CONFIGURATION CONTROL REGISTER**

# Legend:

| Logona.                           |                  |                                    |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

## bit 31-14 Unimplemented: Read as '0'

- bit 13 IOLOCK: Peripheral Pin Select Lock bit<sup>(1)</sup>

- 1 = Peripheral Pin Select is locked. Writes to PPS registers is not allowed.

- 0 = Peripheral Pin Select is not locked. Writes to PPS registers is allowed.

- bit 12 PMDLOCK: Peripheral Module Disable bit<sup>(1)</sup>

- 1 = Peripheral module is locked. Writes to PMD registers is not allowed.

- 0 = Peripheral module is not locked. Writes to PMD registers is allowed.

## bit 11-4 Unimplemented: Read as '0'

- bit 3 JTAGEN: JTAG Port Enable bit

- 1 = Enable the JTAG port

- 0 = Disable the JTAG port

- bit 2-1 Unimplemented: Read as '1'

- bit 0 **TDOEN:** TDO Enable for 2-Wire JTAG bit

- 1 = 2-wire JTAG protocol uses TDO

- 0 = 2-wire JTAG protocol does not use TDO

- Note 1: To change this bit, the unlock sequence must be performed. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

# 29.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

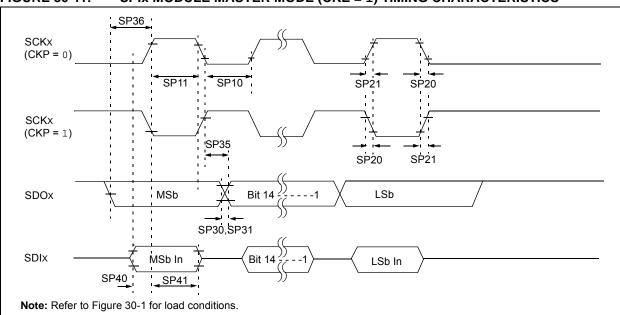

## FIGURE 30-11: SPIX MODULE MASTER MODE (CKE = 1) TIMING CHARACTERISTICS

# TABLE 30-29: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                      |                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                    |  |

|--------------------|----------------------|----------------------------------------------|-------------------------------------------------------|---------------------|------|-------|--------------------|--|

| Param.<br>No.      | Symbol               | Characteristics <sup>(1)</sup>               | Min.                                                  | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |

| SP10               | TscL                 | SCKx Output Low Time (Note 3)                | Tsck/2                                                | —                   | _    | ns    | _                  |  |

| SP11               | TscH                 | SCKx Output High Time (Note 3)               | Tsck/2                                                | —                   | _    | ns    | —                  |  |

| SP20               | TscF                 | SCKx Output Fall Time (Note 4)               | —                                                     | —                   | —    | ns    | See parameter DO32 |  |

| SP21               | TscR                 | SCKx Output Rise Time (Note 4)               | _                                                     | _                   | _    | ns    | See parameter DO31 |  |

| SP30               | TDOF                 | SDOx Data Output Fall Time (Note 4)          | _                                                     | —                   | _    | ns    | See parameter DO32 |  |

| SP31               | TDOR                 | SDOx Data Output Rise Time (Note 4)          | _                                                     | _                   | _    | ns    | See parameter DO31 |  |

| SP35               | TscH2doV,            | , SDOx Data Output Valid after               |                                                       |                     | 15   | ns    | VDD > 2.7V         |  |

|                    | TscL2DoV             | SCKx Edge                                    | _                                                     |                     | 20   | ns    | VDD < 2.7V         |  |

| SP36               | TDOV2SC,<br>TDOV2SCL | SDOx Data Output Setup to<br>First SCKx Edge | 15                                                    | —                   | _    | ns    | —                  |  |

| SP40               | TDIV2scH,            | Setup Time of SDIx Data Input to             | 15                                                    | _                   | _    | ns    | VDD > 2.7V         |  |

|                    | TDIV2scL             | SCKx Edge                                    | 20                                                    | —                   |      | ns    | VDD < 2.7V         |  |

| SP41               | TscH2DIL,            | Hold Time of SDIx Data Input                 | 15                                                    | —                   | _    | ns    | VDD > 2.7V         |  |

|                    | TscL2DIL             | to SCKx Edge                                 | 20                                                    | —                   | _    | ns    | VDD < 2.7V         |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 50 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

# TABLE 31-8:SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                        |                                                        | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |      |       | ≤ +85°C for Industrial |

|--------------------|------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------------|

| Param.<br>No.      | Symbol Characteristics |                                                        | Min.                                                                                                                                                                                                          | Тур. | Max. | Units | Conditions             |

| MSP70              | TscL                   | SCKx Input Low Time (Note 1,2)                         | Tsck/2                                                                                                                                                                                                        |      | _    | ns    | _                      |

| MSP71              | TscH                   | SCKx Input High Time (Note 1,2)                        | Tsck/2                                                                                                                                                                                                        | —    |      | ns    | —                      |

| MSP51              | TssH2doZ               | SSx ↑ to SDOx Output<br>High-Impedance <b>(Note 2)</b> | 5                                                                                                                                                                                                             |      | 25   | ns    | —                      |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns.

# TABLE 31-9: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS                   |      |                                 | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |       |            |   |

|--------------------------------------|------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|---|

| Param.<br>No. Symbol Characteristics |      | Min.                            | Typical                                                                                                                                              | Max. | Units | Conditions |   |

| SP70                                 | TscL | SCKx Input Low Time (Note 1,2)  | Tsck/2                                                                                                                                               |      |       | ns         |   |

| SP71                                 | TscH | SCKx Input High Time (Note 1,2) | Tsck/2                                                                                                                                               | _    | _     | ns         | _ |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY