Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 25                                                                             |

| Program Memory Size        | 16KB (16K × 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 12x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

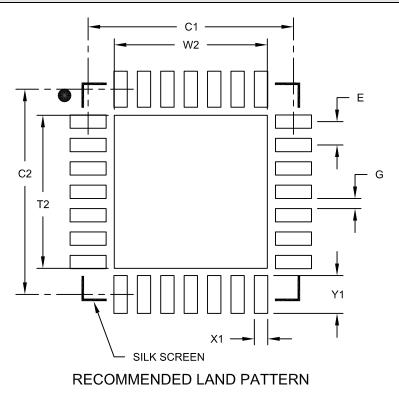

| Package / Case             | 36-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 36-VTLA (5x5)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx110f016c-i-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

| Note: | To access the following documents, refer |

|-------|------------------------------------------|

|       | to the Documentation > Reference         |

|       | Manuals section of the Microchip PIC32   |

|       | website: http://www.microchip.com/pic32  |

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 3. "Memory Organization" (DS60001115)

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer" (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167)

|                 |                             | OUT I/O D<br>Pin Nui                        |                                       |                                 |             | Í                    |                                                                                                 |

|-----------------|-----------------------------|---------------------------------------------|---------------------------------------|---------------------------------|-------------|----------------------|-------------------------------------------------------------------------------------------------|

| Pin Name        | 28-pin<br>QFN               | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC           | 36-pin<br>VTLA                        | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type       | Description                                                                                     |

| PMA0            | 7                           | 10                                          | 8                                     | 3                               | I/O         | TTL/ST               | Parallel Master Port Address bit 0 input<br>(Buffered Slave modes) and output<br>(Master modes) |

| PMA1            | 9                           | 12                                          | 10                                    | 2                               | I/O         | TTL/ST               | Parallel Master Port Address bit 1 input<br>(Buffered Slave modes) and output<br>(Master modes) |

| PMA2            |                             | _                                           |                                       | 27                              | 0           | —                    | Parallel Master Port address                                                                    |

| PMA3            |                             | _                                           | _                                     | 38                              | 0           | _                    | (Demultiplexed Master modes)                                                                    |

| PMA4            |                             | _                                           | _                                     | 37                              | 0           | _                    | 7                                                                                               |

| PMA5            |                             | _                                           | _                                     | 4                               | 0           | _                    |                                                                                                 |

| PMA6            |                             | _                                           | _                                     | 5                               | 0           | _                    | -                                                                                               |

| PMA7            |                             | _                                           | _                                     | 13                              | 0           | _                    | -                                                                                               |

| PMA8            |                             | _                                           | _                                     | 32                              | 0           | _                    | -                                                                                               |

| PMA9            |                             | _                                           | _                                     | 35                              | 0           | _                    | -                                                                                               |

| PMA10           |                             |                                             | _                                     | 12                              | 0           |                      | -                                                                                               |

| PMCS1           | 23                          | 26                                          | 29                                    | 15                              | 0           |                      | Parallel Master Port Chip Select 1 strob                                                        |

|                 | 20 <sup>(2)</sup>           | 23 <sup>(2)</sup>                           | 26 <sup>(2)</sup>                     | 10 <sup>(2)</sup>               | -           |                      | Parallel Master Port data (Demultiplexed                                                        |

| PMD0            | 1 <sup>(3)</sup>            | <br>4 <sup>(3)</sup>                        | 35 <sup>(3)</sup>                     | 21 <sup>(3)</sup>               | I/O         | TTL/ST               | Master mode) or address/data                                                                    |

|                 | 19(2)                       | 22(2)                                       | 25(2)                                 | <u>9</u> (2)                    |             |                      | (Multiplexed Master modes)                                                                      |

| PMD1            | 2(3)                        | 5 <sup>(3)</sup>                            | 36 <sup>(3)</sup>                     | 22 <sup>(3)</sup>               | I/O         | TTL/ST               |                                                                                                 |

|                 | 18(2)                       | 21 <sup>(2)</sup>                           | 24 <sup>(2)</sup>                     | 8 <sup>(2)</sup>                |             |                      | -                                                                                               |

| PMD2            | <u></u>                     | 6 <sup>(3)</sup>                            | 1 <sup>(3)</sup>                      | 23(3)                           | I/O         | TTL/ST               |                                                                                                 |

| PMD3            | 15                          | 18                                          | 19                                    | 1                               | I/O         | TTL/ST               | -                                                                                               |

| PMD4            | 10                          | 10                                          | 18                                    | 44                              | 1/O         | TTL/ST               | -                                                                                               |

| PMD5            | 13                          | 16                                          | 17                                    | 43                              | I/O         | TTL/ST               | -                                                                                               |

| PMD5<br>PMD6    | 12 <sup>(2)</sup>           | 15 <sup>(2)</sup>                           | 16 <sup>(2)</sup>                     | 43<br>42 <sup>(2)</sup>         | 1/0         | 111/31               | -                                                                                               |

| FIVIDO          | 28(3)                       | 3( <b>3</b> )                               | 34 <b>(3)</b>                         | 20(3)                           | I/O         | TTL/ST               |                                                                                                 |

| PMD7            | <u>11(2)</u>                | 14(2)                                       | 15 <sup>(2)</sup>                     | 41 <sup>(2)</sup>               |             |                      | -                                                                                               |

| PINDI           | 27 <sup>(3)</sup>           | 2 <sup>(3)</sup>                            | 33( <b>3</b> )                        | 19 <sup>(3)</sup>               | I/O         | TTL/ST               |                                                                                                 |

| PMRD            | 2/07                        | 24                                          | 27                                    | 19(1)                           | 0           |                      | Derellel Meeter Pert read stroke                                                                |

| PINIRD          | 21<br>22 <sup>(2)</sup>     | 24<br>25 <sup>(2)</sup>                     | 27<br>28 <sup>(2)</sup>               | 14 <sup>(2)</sup>               | 0           |                      | Parallel Master Port read strobe                                                                |

| PMWR            | <u></u><br>4 <sup>(3)</sup> | 25 <sup>(2)</sup><br>7 <sup>(3)</sup>       | 28 <sup>(-)</sup><br>2 <sup>(3)</sup> | 24 <sup>(3)</sup>               | 0           | —                    | Parallel Master Port write strobe                                                               |

| VBUS            | 12(3)                       | 15 <sup>(3)</sup>                           | 16 <sup>(3)</sup>                     | 42(3)                           |             | Analog               | USB bus power monitor                                                                           |

| VBUS<br>VUSB3V3 | 20 <sup>(3)</sup>           | 23 <sup>(3)</sup>                           | 26 <sup>(3)</sup>                     | 10 <sup>(3)</sup>               | P           | Analog               | USB internal transceiver supply. This pin                                                       |

| VUSBSVS         | 20.7                        | 23.7                                        | 20.7                                  | 10.7                            | Г           | _                    | must be connected to VDD.                                                                       |

| VBUSON          | 22 <sup>(3)</sup>           | 25 <sup>(3)</sup>                           | 28 <sup>(3)</sup>                     | 14 <sup>(3)</sup>               | 0           | _                    | USB Host and OTG bus power control output                                                       |

| D+              | 18 <sup>(3)</sup>           | 21 <sup>(3)</sup>                           | 24 <sup>(3)</sup>                     | 8 <sup>(3)</sup>                | I/O         | Analog               | USB D+                                                                                          |

| –<br>D-         | 19(3)                       | 22 <sup>(3)</sup>                           | 25 <sup>(3)</sup>                     | 9 <sup>(3)</sup>                | I/O         | Analog               | USB D-                                                                                          |

| Legend: C       | CMOS = CI<br>ST = Schm      | MOS compa<br>itt Trigger in<br>input buffer | atible input                          | or output                       |             | Analog =<br>O = Outp | Analog input P = Power                                                                          |

####

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

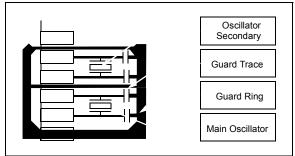

# 2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

# FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

# 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 31:24        |                   | BMXPFMSZ<31:24>   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 23:16        | BMXPFMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 15:8         |                   |                   |                   | BMXPF             | /ISZ<15:8>        |                   |                  |                  |  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 7:0          | 7:0 BMXPFMSZ<7:0> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

# REGISTER 4-7: BMXPFMSZ: PROGRAM FLASH (PFM) SIZE REGISTER

# Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXPFMSZ<31:0>: Program Flash Memory (PFM) Size bits

Static value that indicates the size of the PFM in bytes: 0x00004000 = Device has 16 KB Flash 0x00008000 = Device has 32 KB Flash 0x00010000 = Device has 64 KB Flash 0x00020000 = Device has 128 KB Flash 0x00040000 = Device has 256 KB Flash

# REGISTER 4-8: BMXBOOTSZ: BOOT FLASH (IFM) SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7  | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R                  | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 31:24        | BMXBOOTSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R                  | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 23:16        | BMXBOOTSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R                  | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 15:8         |                    |                   |                   | BMXBOC            | )TSZ<15:8>        |                   |                  |                  |  |  |  |  |

| 7.0          | R                  | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 7:0          | 7:0 BMXBOOTSZ<7:0> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **BMXBOOTSZ<31:0>:** Boot Flash Memory (BFM) Size bits Static value that indicates the size of the Boot PFM in bytes: 0x00000C00 = Device has 3 KB boot Flash

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | _                       | —                 | —                 |                   | _                | —                |  |  |  |

| 23:16        | U-0               | R-0               | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | —                 | —                 | _                       | —                 | —                 | _                 | —                | —                |  |  |  |

| 45.0         | U-0               | R-0               | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | —                 | —                 | _                       | —                 | _                 | _                 | _                | —                |  |  |  |

| 7.0          | U-0               | U-0               | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | —                 | _                 | TUN<5:0> <sup>(1)</sup> |                   |                   |                   |                  |                  |  |  |  |

### REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

# Legend:

| Logona.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized, nor tested.

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

# 9.1 DMA Control Registers

## TABLE 9-1: DMA GLOBAL REGISTER MAP

| ess                         |                                 | 0         |       |       |       |         |         |       |      | Bi       | ts        |      |      |      |      |      |           |      | s         |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|---------|---------|-------|------|----------|-----------|------|------|------|------|------|-----------|------|-----------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8     | 23/7      | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Reset |

| 2000                        | DMACON                          | 31:16     | _     | _     | -     | —       | —       | _     | —    | —        | —         | -    | -    | _    | -    | -    | —         | _    | 0000      |

| 3000                        | DIVIACON                        | 15:0      | ON    | —     | _     | SUSPEND | DMABUSY | —     | _    | —        | _         | —    | —    | —    | —    | —    | —         | _    | 0000      |

| 2010                        | DMASTAT                         | 31:16     | -     | _     | —     | —       | —       | —     | —    | —        | _         | _    | _    | _    | _    | —    | —         | _    | 0000      |

| 3010                        | DIVIASTAT                       | 15:0      | -     | _     | —     | —       | —       | —     | —    | —        | _         | _    | _    | _    | RDWR | DI   | MACH<2:0> | .(2) | 0000      |

| 3020                        | DMAADDR                         | 31:16     |       |       |       |         |         |       |      | DMAADD   | D-31:05   |      |      |      |      |      |           |      | 0000      |

| 3020                        | DIVIAADDR                       | 15:0      |       |       |       |         |         |       |      | DIVIAADL | vix~51.02 |      |      |      |      |      |           |      | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

### TABLE 9-2: DMA CRC REGISTER MAP

| ess                         |                | ge    |       |                | -                         |       |       |           |      | В    | ts        |        | -      |      |      |      |           |      |            |

|-----------------------------|----------------|-------|-------|----------------|---------------------------|-------|-------|-----------|------|------|-----------|--------|--------|------|------|------|-----------|------|------------|

| Virtual Address<br>(BF88_#) | 3030 DCRCCON 3 |       | 31/15 | 30/14          | 29/13                     | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7      | 22/6   | 21/5   | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Resets |

| 2020                        | DODOCON        | 31:16 | —     | _              | - BYTO<1:0> WBO BITO 0000 |       |       |           |      |      |           |        |        | 0000 |      |      |           |      |            |

| 3030                        | DURUUUN        | 15:0  | —     | _              | —                         |       |       | PLEN<4:0> |      |      | CRCEN     | CRCAPP | CRCTYP | —    | —    | C    | CRCCH<2:0 | >    | 0000       |

| 2040                        | DCRCDATA       | 31:16 |       |                |                           |       |       |           |      |      | TA ~21:05 |        |        |      |      |      |           |      | 0000       |

| 3040                        | DURUDAIA       | 15:0  |       | DCRCDATA<31:0> |                           |       |       |           |      |      |           |        |        |      |      |      |           |      |            |

| 3050                        | DCRCXOR        | 31:16 |       | DCPCYOP<21:0>  |                           |       |       |           |      |      |           |        |        |      |      |      |           |      |            |

| 3050                        | DUNUAUR        | 15:0  |       | DCRCXOR<31:0>  |                           |       |       |           |      |      |           |        |        |      |      |      |           |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 31:24        |                     | —                 | —                 | _                 | _                 | _                 |                  | _                     |

| 22.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | —                   | —                 | —                 | _                 | _                 | —                 | —                | —                     |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | —                 | —                 | _                 | _                 | _                 | _                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             |                   | CHEDET            | CHPF             | RI<1:0>               |

## REGISTER 9-7: DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER

#### Legend:

| 0                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 CHBUSY: Channel Busy bit

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14-9 Unimplemented: Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

#### bit 7 CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 = Channel is disabled

### bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

### bit CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- bit 4 CHAEN: Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

0 = Channel is disabled on block transfer complete

### bit 3 Unimplemented: Read as '0'

- bit 2 CHEDET: Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

- bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |  |  |  |  |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|--|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |  |  |  |  |

| 31:24        | —                 | —                 | —                        | _                 | —                     | —                     |                  | _                    |  |  |  |  |  |

| 22:16        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |  |  |  |  |

| 23:16        | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |  |  |  |  |

| 15.0         | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |  |  |  |  |  |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |  |  |  |  |  |

| 7:0          | JSTATE            | SE0               | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |  |  |  |  |  |

|              | JUNATE            | SEU               | TOKBUSY <sup>(1,5)</sup> | USBROI            | TIOSTEIN /            |                       | PPBR51           | SOFEN <sup>(5)</sup> |  |  |  |  |  |

# REGISTER 10-11: U1CON: USB CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE was detected on the USB

- 0 = No JSTATE was detected on the

- bit 6 **SE0:** Live Single-Ended Zero flag bit 1 = Single-Ended Zero was detected on the USB

- 0 = No Single-Ended Zero was detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing is disabled (set upon SETUP token received)

- 0 = Token and packet processing is enabled

- TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token is being executed by the USB module

- 0 = No token is being executed

### bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset generated

- 0 = USB reset terminated

- bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

- bit 2 RESUME: RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | _                 |                   |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | _                 | -                 | —                 | _                 | _                 | -                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | P]R<3:0>         |                  |

#### **REGISTER 11-1:** [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

## Legend:

| Legena.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

# bit 31-4 Unimplemented: Read as '0'

bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 11-1 for input pin selection values.

Note: Register values can only be changed if the Configuration bit, IOLOCK (CFGCON<13>), = 0.

### REGISTER 11-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | —                 |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   |                   |                   | RPnR              | <3:0>            |                  |

# Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 11-2 for output pin selection values.

Note: Register values can only be changed if the Configuration bit, IOLOCK (CFGCON<13>), = 0.

# REGISTER 12-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

- bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit When TCS = 1: 1 = External clock input is synchronized 0 = External clock input is not synchronized When TCS = 0: This bit is ignored.

bit 1 TCS: Timer Clock Source Select bit 1 = External clock from TxCKI pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCmLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### **Input Capture Control Registers** 15.1

|                             | LE 15-1:              | IN            | PUT C | APTURE | E 1-INPU | JT CAP | <b>FURE 5</b> | REGIST | ER MAI | 2      |        |      |      |      |       |      |          |

|-----------------------------|-----------------------|---------------|-------|--------|----------|--------|---------------|--------|--------|--------|--------|------|------|------|-------|------|----------|

| ess                         |                       |               |       |        |          |        |               |        |        | Bi     | ts     |      |      |      |       |      |          |

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15 | 30/14  | 29/13    | 28/12  | 27/11         | 26/10  | 25/9   | 24/8   | 23/7   | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1     |

| 2000                        | IC1CON <sup>(1)</sup> | 31:16         |       | —      | —        | —      | _             | —      | —      | —      | —      | —    | _    | —    | —     | _    | —        |

| 2000                        | 101001                | 15:0          | ON    | —      | SIDL     | —      | —             |        | FEDGE  | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2010                        | IC1BUF                | 31:16<br>15:0 |       |        |          |        |               |        |        | IC1BUF | <31:0> |      |      |      |       |      |          |

| 2200                        | IC2CON <sup>(1)</sup> | 31:16         |       | —      | —        | —      | —             | —      | —      | _      | —      | —    | —    | —    | _     |      | -        |

| 2200                        | 102001                | 15:0          | ON    | —      | SIDL     | —      | —             | —      | FEDGE  | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2210                        | IC2BUF                | 31:16<br>15:0 |       |        |          |        |               |        |        | IC2BUF | <31:0> |      |      |      |       |      |          |

| 2400                        | IC3CON <sup>(1)</sup> | 31:16         | -     | —      | —        | _      | _             | -      | —      | _      | —      | -    | _    | —    | —     |      | —        |

| 2400                        | 103001                | 15.0          | ON    | —      | SIDL     | —      | —             | —      | FEDGE  | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2410                        | IC3BUF                | 31:16<br>15:0 |       |        |          |        |               |        |        | IC3BUF | <31:0> |      |      |      |       |      |          |

| 2600                        | IC4CON <sup>(1)</sup> | 31:16         |       | _      | _        | —      | _             | _      | _      |        | _      | —    | —    | —    | _     |      | —        |

| 2000                        | 104001                | 15:0          | ON    | —      | SIDL     | —      | —             | —      | FEDGE  | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2610                        | IC4BUF                | 31:16<br>15:0 |       |        |          |        |               |        |        | IC4BUF | <31:0> |      |      |      |       |      |          |

| 2800                        | IC5CON <sup>(1)</sup> | 31:16         | -     | —      | —        | _      | _             | _      | —      | —      | —      | _    |      | —    | —     |      | —        |

| 2000                        | 1000014               | 15:0          | ON    | —      | SIDL     | _      | _             | _      | FEDGE  | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |

| 2810                        | IC5BUF                | 31:16<br>15:0 |       |        |          |        |               |        |        | IC5BUF | <31:0> |      |      |      |       |      |          |

#

Legend:

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

All Resets

0000

0000 xxxx xxxx 0000 0000 xxxx xxxx 0000 0000 xxxx xxxx 0000 0000 xxxx xxxx 0000 0000 xxxx xxxx

16/0

—

# REGISTER 18-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |  |

| 31:24        | —                 | —                 | _                 | -                 | —                 |                   | _                | _                |  |  |  |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |  |

| 23:16        | —                 | _                 | _                 | _                 | _                 | —                 | _                | _                |  |  |  |  |  |  |  |  |

| 45.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |  |  |  |  |  |  |  |  |

| 15:8         | ACKSTAT           | TRSTAT            | -                 | -                 | _                 | BCL               | GCSTAT           | ADD10            |  |  |  |  |  |  |  |  |

| 7.0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |  |  |  |  |  |  |  |  |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |  |  |  |  |  |  |  |  |

| Legend:           | HS = Set in hardware | red                      |                    |  |  |

|-------------------|----------------------|--------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, r | d bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared     | C = Clearable bit  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) 1 = Acknowledge was not received from slave 0 = Acknowledge was received from slave Hardware set or clear at end of slave Acknowledge. bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) 1 = Master transmit is in progress (8 bits + ACK) 0 = Master transmit is not in progress Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge. bit 13-11 Unimplemented: Read as '0' bit 10 BCL: Master Bus Collision Detect bit 1 = A bus collision has been detected during a master operation 0 = No collisionHardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module. bit 9 GCSTAT: General Call Status bit 1 = General call address was received 0 = General call address was not received Hardware set when address matches general call address. Hardware clear at Stop detection. bit 8 ADD10: 10-bit Address Status bit 1 = 10-bit address was matched 0 = 10-bit address was not matched Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

bit 7 IWCOL: Write Collision Detect bit

| 1 = An attempt to write the I2CxTRN register failed because the I <sup>2</sup> | C module is busy |

|--------------------------------------------------------------------------------|------------------|

| 0 = No collision                                                               |                  |

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

- bit 6 I2COV: Receive Overflow Flag bit

- 1 = A byte was received while the I2CxRCV register is still holding the previous byte 0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

## bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.24        | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        | CH0NB             | _                 | _                 | —                 | CH0SB<3:0>        |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        | CH0NA             | _                 | _                 | —                 | CH0SA<3:0>        |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 15:8         |                   | _                 | _                 | —                 | _                 | —                 | —                | —                |  |  |  |  |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 7:0          | —                 |                   |                   | —                 | _                 | _                 | _                | _                |  |  |  |  |  |  |

# REGISTER 22-4: AD1CHS: ADC INPUT SELECT REGISTER

CHONB: Negative Input Select bit for Sample B

# Legend:

bit 31

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

|        |                      | <ul> <li>1 = Channel 0 negative input is AN1</li> <li>0 = Channel 0 negative input is VREFL</li> </ul>                                                                                                                                                                                                                                           |

|--------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30 | -28                  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                       |

| bit 27 | -24                  | CH0SB<3:0>: Positive Input Select bits for Sample B                                                                                                                                                                                                                                                                                              |

|        |                      | <pre>1111 = Channel 0 positive input is Open<sup>(1)</sup> 1110 = Channel 0 positive input is IVREF<sup>(2)</sup> 1101 = Channel 0 positive input is CTMU temperature sensor (CTMUT)<sup>(3)</sup> 1100 = Channel 0 positive input is AN12<sup>(4)</sup></pre>                                                                                   |

|        |                      | •                                                                                                                                                                                                                                                                                                                                                |

|        |                      | •                                                                                                                                                                                                                                                                                                                                                |

|        |                      | •                                                                                                                                                                                                                                                                                                                                                |

|        |                      | 0001 = Channel 0 positive input is AN1<br>0000 = Channel 0 positive input is AN0                                                                                                                                                                                                                                                                 |

| bit 23 |                      | CH0NA: Negative Input Select bit for Sample A Multiplexer Setting <sup>(2)</sup>                                                                                                                                                                                                                                                                 |

|        |                      | <ul><li>1 = Channel 0 negative input is AN1</li><li>0 = Channel 0 negative input is VREFL</li></ul>                                                                                                                                                                                                                                              |

| bit 22 | -20                  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                       |

| bit 19 | -16                  | CH0SA<3:0>: Positive Input Select bits for Sample A Multiplexer Setting<br>1111 = Channel 0 positive input is Open <sup>(1)</sup><br>1110 = Channel 0 positive input is IVREF <sup>(2)</sup><br>1101 = Channel 0 positive input is CTMU temperature (CTMUT) <sup>(3)</sup><br>1100 = Channel 0 positive input is AN12 <sup>(4)</sup>             |

|        |                      | •                                                                                                                                                                                                                                                                                                                                                |

|        |                      | •                                                                                                                                                                                                                                                                                                                                                |

|        |                      | •                                                                                                                                                                                                                                                                                                                                                |

|        |                      | 0001 = Channel 0 positive input is AN1<br>0000 = Channel 0 positive input is AN0                                                                                                                                                                                                                                                                 |

| bit 15 | -0                   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                       |

| Note   | 1:<br>2:<br>3:<br>4: | This selection is only used with CTMU capacitive and time measurement.<br>See <b>Section 24.0 "Comparator Voltage Reference (CVREF)"</b> for more information.<br>See <b>Section 25.0 "Charge Time Measurement Unit (CTMU)</b> " for more information.<br>AN12 is only available on 44-pin devices. AN6-AN8 are not available on 28-pin devices. |

|        |                      |                                                                                                                                                                                                                                                                                                                                                  |

# 24.1 Comparator Voltage Reference Control Register

| <b>TABLE 24-1</b> : | COMPARATOR VOLTAGE REFERENCE REGISTER MAP |

|---------------------|-------------------------------------------|

|---------------------|-------------------------------------------|

| ress<br>t)               |                                 | Ð         |       | Bits  |       |       |       |       |      |      |      | ŝ     |      |       |             |      |      |      |            |

|--------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|-------|------|-------|-------------|------|------|------|------------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3        | 18/2 | 17/1 | 16/0 | All Resets |

| 0000                     |                                 | 31:16     | _     | _     | —     | —     | —     | —     | _    | _    | —    | —     | —    | _     | —           | _    | _    | —    | 0000       |

| 9800                     | CVRCON                          | 15:0      | ON    | _     | _     | _     | _     | _     | _    | _    | _    | CVROE | CVRR | CVRSS | SS CVR<3:0> |      |      | 0000 |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

# **30.1 DC Characteristics**

# TABLE 30-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range                 | Temp. Range     | Max. Frequency                     |  |  |  |

|----------------|---------------------------|-----------------|------------------------------------|--|--|--|

| Gharacteristic | (in Volts) <sup>(1)</sup> | (in °C)         | PIC32MX1XX/2XX 28/36/44-pin Family |  |  |  |

| DC5            | 2.3-3.6V                  | -40°C to +85°C  | 40 MHz                             |  |  |  |

| DC5b           | 2.3-3.6V                  | -40°C to +105°C | 40 MHz                             |  |  |  |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 30-11 for BOR values.

# TABLE 30-2: THERMAL OPERATING CONDITIONS

| Rating                                                                               | Symbol | Min. | Typical     | Max. | Unit |

|--------------------------------------------------------------------------------------|--------|------|-------------|------|------|

| Industrial Temperature Devices                                                       |        |      |             |      |      |

| Operating Junction Temperature Range                                                 | TJ     | -40  | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                  | TA     | -40  | —           | +85  | °C   |

| V-temp Temperature Devices                                                           |        |      |             |      |      |

| Operating Junction Temperature Range                                                 | TJ     | -40  | _           | +140 | °C   |

| Operating Ambient Temperature Range                                                  | TA     | -40  | —           | +105 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>PINT = VDD x (IDD – S IOH) |        |      | PINT + PI/c | )    | w    |

| I/O Pin Power Dissipation:<br>I/O = S (({VDD – VOH} x IOH) + S (VOL x IOL))          |        |      |             |      |      |

| Maximum Allowed Power Dissipation                                                    | Pdmax  | (    | Tj — Ta)/θJ | A    | W    |

### TABLE 30-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristics                          | Symbol | Typical | Max. | Unit | Notes |

|------------------------------------------|--------|---------|------|------|-------|

| Package Thermal Resistance, 28-pin SSOP  | θJA    | 71      | _    | °C/W | 1     |

| Package Thermal Resistance, 28-pin SOIC  | θJA    | 50      | —    | °C/W | 1     |

| Package Thermal Resistance, 28-pin SPDIP | θJA    | 42      | _    | °C/W | 1     |

| Package Thermal Resistance, 28-pin QFN   | θJA    | 35      | —    | °C/W | 1     |

| Package Thermal Resistance, 36-pin VTLA  | θJA    | 31      | —    | °C/W | 1     |

| Package Thermal Resistance, 44-pin QFN   | θJA    | 32      | _    | °C/W | 1     |

| Package Thermal Resistance, 44-pin TQFP  | θJA    | 45      |      | °C/W | 1     |

| Package Thermal Resistance, 44-pin VTLA  | θJA    | 30      | _    | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

# TABLE 30-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA        |         | ISTICS                   |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |      |       |                                |  |  |

|---------------|---------|--------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------|--|--|

| Param.<br>No. | Symbol  | Charact                  | eristics                      | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                               | Max. | Units | Conditions                     |  |  |

| IM10          | TLO:SCL | Clock Low Time           | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   | _    | μs    | —                              |  |  |

|               |         |                          | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   |      | μS    | —                              |  |  |

|               |         |                          | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   | —    | μs    | _                              |  |  |

| IM11          | THI:SCL | Clock High Time          | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   |      | μS    | —                              |  |  |

|               |         |                          | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   | _    | μS    | —                              |  |  |

|               |         |                          | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                   |      | μs    | -                              |  |  |

| IM20          | TF:SCL  | SDAx and SCLx            | 100 kHz mode                  | —                                                                                                                                                                                                                                                                                 | 300  | ns    | CB is specified to be          |  |  |

|               |         | Fall Time                | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                                                                                                       | 300  | ns    | from 10 to 400 pF              |  |  |

|               |         |                          | 1 MHz mode<br><b>(Note 2)</b> | _                                                                                                                                                                                                                                                                                 | 100  | ns    |                                |  |  |

| IM21          | TR:SCL  | SDAx and SCLx            | 100 kHz mode                  | —                                                                                                                                                                                                                                                                                 | 1000 | ns    | CB is specified to be          |  |  |

|               |         | Rise Time                | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                                                                                                       | 300  | ns    | from 10 to 400 pF              |  |  |