Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                |

|---------------------------|--------------------------------------------------------------------------------|

| Product Status            | Obsolete                                                                       |

| Core Processor            | MIPS32® M4K™                                                                   |

| Core Size                 | 32-Bit Single-Core                                                             |

| Speed                     | 40MHz                                                                          |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals               | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| lumber of I/O             | 25                                                                             |

| Program Memory Size       | 16KB (16K x 8)                                                                 |

| Program Memory Type       | FLASH                                                                          |

| EPROM Size                | -                                                                              |

| AM Size                   | 4K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| ata Converters            | A/D 12x10b                                                                     |

| Scillator Type            | Internal                                                                       |

| perating Temperature      | -40°C ~ 105°C (TA)                                                             |

| lounting Type             | Surface Mount                                                                  |

| ackage / Case             | 36-VFTLA Exposed Pad                                                           |

| upplier Device Package    | 36-VTLA (5x5)                                                                  |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx110f016c-v-tl |

TABLE 1: PIC32MX1XX 28/36/44-PIN GENERAL PURPOSE FAMILY FEATURES

|                 |      |                                    |                  | Rem             | appab                                  | le Pe | riphe                | rals                               |                    |                     |                  |     | _                                     |      | ls)                          |      |          |      |                                 |

|-----------------|------|------------------------------------|------------------|-----------------|----------------------------------------|-------|----------------------|------------------------------------|--------------------|---------------------|------------------|-----|---------------------------------------|------|------------------------------|------|----------|------|---------------------------------|

| Device          | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/Compare | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | l <sup>2</sup> C | PMP | DMA Channels (Programmable/Dedicated) | СТМО | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | Packages                        |

| PIC32MX110F016B | 28   | 16+3                               | 4                | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2                | Υ   | 4/0                                   | Υ    | 10                           | Υ    | 21       | Υ    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX110F016C | 36   | 16+3                               | 4                | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 12                           | Υ    | 25       | Υ    | VTLA                            |

| PIC32MX110F016D | 44   | 16+3                               | 4                | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 13                           | Y    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX120F032B | 28   | 32+3                               | 8                | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Y    | 10                           | Y    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX120F032C | 36   | 32+3                               | 8                | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 12                           | Υ    | 25       | Υ    | VTLA                            |

| PIC32MX120F032D | 44   | 32+3                               | 8                | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Ν                   | 2                | Υ   | 4/0                                   | Υ    | 13                           | Υ    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX130F064B | 28   | 64+3                               | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 10                           | Υ    | 21       | Υ    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX130F064C | 36   | 64+3                               | 16               | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 12                           | Υ    | 25       | Υ    | VTLA                            |

| PIC32MX130F064D | 44   | 64+3                               | 16               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Y    | 13                           | Y    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX150F128B | 28   | 128+3                              | 32               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 10                           | Υ    | 21       | Υ    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX150F128C | 36   | 128+3                              | 32               | 24              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 12                           | Υ    | 25       | Υ    | VTLA                            |

| PIC32MX150F128D | 44   | 128+3                              | 32               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 13                           | Υ    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX130F256B | 28   | 256+3                              | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Y    | 10                           | Υ    | 21       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX130F256D | 44   | 256+3                              | 16               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 13                           | Υ    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX170F256B | 28   | 256+3                              | 64               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Y    | 10                           | Υ    | 21       | Υ    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX170F256D | 44   | 256+3                              | 64               | 32              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | N                   | 2                | Υ   | 4/0                                   | Υ    | 13                           | Υ    | 35       | Υ    | VTLA,<br>TQFP,<br>QFN           |

Note 1: This device features 3 KB of boot Flash memory.

**3:** Four out of five external interrupts are remappable.

**<sup>2:</sup>** Four out of five timers are remappable.

### **Pin Diagrams**

#### TABLE 3: PIN NAMES FOR 28-PIN GENERAL PURPOSE DEVICES

28-PIN SOIC, SPDIP, SSOP (TOP VIEW)(1,2,3)

1 28 1 28 1 28 SSOP SOIC SPDIP

PIC32MX110F016B PIC32MX120F032B PIC32MX130F064B PIC32MX130F256B PIC32MX150F128B PIC32MX170F256B

| Pin # | Full Pin Name                         |

|-------|---------------------------------------|

| 1     | MCLR                                  |

| 2     | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0 |

| 3     | VREF-/CVREF-/AN1/RPA1/CTED2/RA1       |

| 4     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0  |

| 5     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1 |

| 6     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2  |

| 7     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3    |

| 8     | Vss                                   |

| 9     | OSC1/CLKI/RPA2/RA2                    |

| 10    | OSC2/CLKO/RPA3/PMA0/RA3               |

| 11    | SOSCI/RPB4/RB4                        |

| 12    | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4        |

| 13    | VDD                                   |

| 14    | PGED3/RPR5/PMD7/RR5                   |

| Pin# | Full Pin Name                                  |

|------|------------------------------------------------|

| 15   | PGEC3/RPB6/PMD6/RB6                            |

| 16   | TDI/RPB7/CTED3/PMD5/INT0/RB7                   |

| 17   | TCK/RPB8/SCL1/CTED10/PMD4/RB8                  |

| 18   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 19   | Vss                                            |

| 20   | VCAP                                           |

| 21   | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 22   | PGEC2/TMS/RPB11/PMD1/RB11                      |

| 23   | AN12/PMD0/RB12                                 |

| 24   | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 25   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 26   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 27   | AVss                                           |

| 28   | AVDD                                           |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: Shaded pins are 5V tolerant.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |               | Pin Nu                            | mber <sup>(1)</sup> |                                 |             |                |                                                                                   |

|----------|---------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|-----------------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                                       |

| MCLR     | 26            | 1                                 | 32                  | 18                              | I/P         | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device.        |

| AVDD     | 25            | 28                                | 31                  | 17                              | Р           | _              | Positive supply for analog modules. This pin must be connected at all times.      |

| AVss     | 24            | 27                                | 30                  | 16                              | Р           | _              | Ground reference for analog modules                                               |

| VDD      | 10            | 13                                | 5, 13, 14,<br>23    | 28, 40                          | Р           | _              | Positive supply for peripheral logic and I/O pins                                 |

| VCAP     | 17            | 20                                | 22                  | 7                               | Р           |                | CPU logic filter capacitor connection                                             |

| Vss      | 5, 16         | 8, 19                             | 6, 12, 21           | 6, 29, 39                       | Р           | _              | Ground reference for logic and I/O pins. This pin must be connected at all times. |

| VREF+    | 27            | 2                                 | 33                  | 19                              | I           | Analog         | Analog voltage reference (high) input                                             |

| VREF-    | 28            | 3                                 | 34                  | 20                              | I           | Analog         | Analog voltage reference (low) input                                              |

**Legend:** CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

O = Output PPS = Peripheral Pin Select

Analog = Analog input

P = Power I = Input — = N/A

TTL = TTL input buffer

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

#### REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 24.24        | U-0                | U-0                |

| 31:24        | _                 | _                 | -                 | _                 | _                 |                   | _                  | _                  |

| 22:16        | U-0                | U-0                |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                  | _                  |

| 45.0         | U-0               | U-0 U-0           |                   | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | CMR                | VREGS              |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

**Legend:** HS = Set by hardware

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-10 Unimplemented: Read as '0'

bit 9 **CMR:** Configuration Mismatch Reset Flag bit

1 = Configuration mismatch Reset has occurred

0 = Configuration mismatch Reset has not occurred

bit 8 VREGS: Voltage Regulator Standby Enable bit

1 = Regulator is enabled and is on during Sleep mode

0 = Regulator is disabled and is off during Sleep mode

bit 7 **EXTR:** External Reset (MCLR) Pin Flag bit

1 = Master Clear (pin) Reset has occurred

0 = Master Clear (pin) Reset has not occurred

bit 6 SWR: Software Reset Flag bit

1 = Software Reset was executed

0 = Software Reset as not executed

bit 5 Unimplemented: Read as '0'

bit 4 WDTO: Watchdog Timer Time-out Flag bit

1 = WDT Time-out has occurred

0 = WDT Time-out has not occurred

bit 3 SLEEP: Wake From Sleep Flag bit

1 = Device was in Sleep mode

0 = Device was not in Sleep mode

bit 2 IDLE: Wake From Idle Flag bit

1 = Device was in Idle mode

0 = Device was not in Idle mode

bit 1 **BOR:** Brown-out Reset Flag bit<sup>(1)</sup>

1 = Brown-out Reset has occurred

0 = Brown-out Reset has not occurred

bit 0 **POR:** Power-on Reset Flag bit<sup>(1)</sup>

1 = Power-on Reset has occurred

0 = Power-on Reset has not occurred

**Note 1:** User software must clear this bit to view next detection.

#### 10.0 USB ON-THE-GO (OTG)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 27. "USB On-The-Go (OTG)"** (DS60001126), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 Full-Speed and Low-Speed embedded host, Full-Speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 10-1.

The clock generator provides the 48 MHz clock required for USB Full-Speed and Low-Speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The PIC32 USB module includes the following features:

- · USB Full-Speed support for Host and Device

- · Low-Speed Host support

- · USB OTG support

- · Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- · Integrated USB transceiver

- · Transaction handshaking performed by hardware

- · Endpoint buffering anywhere in system RAM

- Integrated DMA to access system RAM and Flash

Note:

The implementation and use of the USB specifications, as well as other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc., also referred to as USB-IF (www.usb.org). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

#### REGISTER 10-18: U1BDTP2: USB BUFFER DESCRIPTOR TABLE PAGE 2 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                                                                                                                                                                                              | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 31:24        | U-0                                                                                                                                                                                                           | U-0              |

| 31.24        | -                 |                   | 1                 | 1                 | -                 | 1                 | 1                                                                                                                                                                                                             | _                |

| 23:16        | U-0                                                                                                                                                                                                           | U-0              |

| 23.10        | _                 | -                 | -                 | -                 | -                 | 1                 | 0/2         25/17/9/1         24/16/8/0           U-0         U-0           —         —           U-0         U-0           —         —           U-0         U-0           —         —           —         — | _                |

| 15:8         | U-0                                                                                                                                                                                                           | U-0              |

| 15.6         | _                 | _                 |                   | _                 | _                 | -                 | _                                                                                                                                                                                                             | _                |

| 7:0          | R/W-0                                                                                                                                                                                                         | R/W-0            |

| 7:0          |                   |                   |                   | BDTPTRI           | H<23:16>          |                   |                                                                                                                                                                                                               |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 BDTPTRH<23:16>: Buffer Descriptor Table Base Address bits

This 8-bit value provides address bits 23 through 16 of the Buffer Descriptor Table base address, which defines the starting location of the Buffer Descriptor Table in system memory.

The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

#### REGISTER 10-19: U1BDTP3: USB BUFFER DESCRIPTOR TABLE PAGE 3 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   |                   | 1                 | -                 | -                 | -                 | -                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | BDTPTR            | U<31:24>          |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 BDTPTRU<31:24>: Buffer Descriptor Table Base Address bits

This 8-bit value provides address bits 31 through 24 of the Buffer Descriptor Table base address, defines the starting location of the Buffer Descriptor Table in system memory.

The 32-bit Buffer Descriptor Table base address is 512-byte aligned.

#### 12.0 TIMER1

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14.** "Timers" (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features one synchronous/asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the Low-Power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications.

The following modes are supported:

- · Synchronous Internal Timer

- · Synchronous Internal Gated Timer

- Synchronous External Timer

- · Asynchronous External Timer

#### 12.1 Additional Supported Features

- · Selectable clock prescaler

- · Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

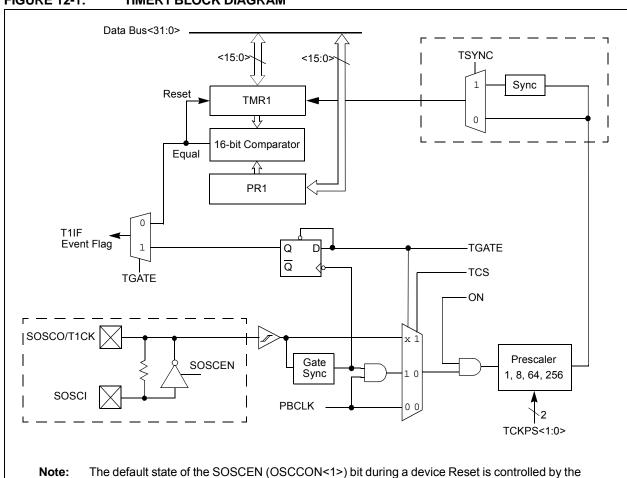

Figure 12-1 illustrates a general block diagram of Timer1.

FIGURE 12-1: TIMER1 BLOCK DIAGRAM

**Note:** The default state of the SOSCEN (OSCCON<1>) bit during a device Reset is controlled by the FSOSCEN bit in Configuration Word, DEVCFG1.

### 17.1 SPI Control Registers

### TABLE 17-1: SPI1 AND SPI2 REGISTER MAP

| .,,,                        | LL 1/-1                         |           | ,, ,, ,,,,,,  | J U     | 0.0.   | LIZ INITAL   |                                   |              |           |        |         |           |        |                                  |             |          |        |         |            |

|-----------------------------|---------------------------------|-----------|---------------|---------|--------|--------------|-----------------------------------|--------------|-----------|--------|---------|-----------|--------|----------------------------------|-------------|----------|--------|---------|------------|

| ess                         |                                 | •         |               |         |        |              |                                   |              |           | Bi     | ts      |           |        |                                  |             |          |        |         | ,,         |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14   | 29/13  | 28/12        | 27/11                             | 26/10        | 25/9      | 24/8   | 23/7    | 22/6      | 21/5   | 20/4                             | 19/3        | 18/2     | 17/1   | 16/0    | All Resets |

| 5800                        | SPI1CON                         | 31:16     | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW                           | FF           | RMCNT<2:0 | 0>     | MCLKSEL | _         | _      | _                                | _           | _        | SPIFE  | ENHBUF  | 0000       |

| 3000                        | 31 11001                        | 15:0      | ON            | _       | SIDL   | DISSDO       | MODE32                            | MODE16       | SMP       | CKE    | SSEN    | CKP       | MSTEN  | DISSDI STXISEL<1:0> SRXISEL<1:0> |             |          | L<1:0> | 0000    |            |

| E010                        | SPI1STAT                        | 31:16     | _             | _       | _      |              | RXBUFELM<4:0> — — — TXBUFELM<4:0> |              |           |        |         |           |        |                                  | :0>         |          | 0000   |         |            |

| 3010                        | 01 110 1711                     | 15:0      | _             | _       | _      | FRMERR       | SPIBUSY                           |              | _         | SPITUR | SRMT    | SPIROV    | SPIRBE | _                                | SPITBE      | _        | SPITBF | SPIRBF  | 8000       |

| 5820                        | SPI1BUF                         | 31:16     |               |         |        |              |                                   |              |           | DATA<  | 31.0>   |           |        |                                  |             |          |        |         | 0000       |

| 3020                        | OI IIDOI                        | 15:0      |               |         |        |              |                                   |              |           |        |         |           |        |                                  |             |          |        |         | 0000       |

| 5830                        | SPI1BRG                         | 31:16     | _             | _       | _      | _            |                                   | _            | _         | _      | _       | _         | _      | _                                | _           | _        | _      | _       | 0000       |

| 0000                        |                                 | 15:0      | _             | _       | _      |              |                                   |              |           |        | E       | 3RG<12:0> |        |                                  |             |          |        |         | 0000       |

|                             |                                 | 31:16     | _             | _       | _      | _            | _                                 | _            | _         | _      | _       | _         | _      | _                                | _           | _        | _      | _       | 0000       |

| 5840                        | SPI1CON2                        | 15:0      | SPI<br>SGNEXT | 1       | 1      | FRM<br>ERREN | SPI<br>ROVEN                      | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | _         | ı      | 1                                | AUD<br>MONO | 1        | AUDMO  | D<1:0>  | 0000       |

| EA00                        | SPI2CON                         | 31:16     | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW                           | FF           | RMCNT<2:0 | 0>     | MCLKSEL | _         | -      | _                                | _           | _        | SPIFE  | ENHBUF  | 0000       |

| SAUU                        | SFIZCON                         | 15:0      | ON            |         | SIDL   | DISSDO       | MODE32                            | MODE16       | SMP       | CKE    | SSEN    | CKP       | MSTEN  | DISSDI                           | STXISE      | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| E A 10                      | SPI2STAT                        | 31:16     | _             |         | _      |              | RXE                               | BUFELM<4:    | 0>        |        | _       | _         | -      |                                  | TXI         | BUFELM<4 | :0>    |         | 0000       |

| SATU                        | SF IZS IAI                      | 15:0      | _             | _       | _      | FRMERR       | SPIBUSY                           | _            | _         | SPITUR | SRMT    | SPIROV    | SPIRBE | _                                | SPITBE      | _        | SPITBF | SPIRBF  | 0008       |

| 5A20                        | SPI2BUF                         | 31:16     |               |         |        |              |                                   |              |           | DATA<  | 21.05   |           |        |                                  |             |          |        |         | 0000       |

| 5A20                        | SFIZEUI                         | 15:0      |               |         |        |              |                                   |              |           | DAIA   | 31.0    |           |        |                                  |             |          |        |         | 0000       |

| E A 20                      | SPI2BRG                         | 31:16     | _             | _       | _      | _            | _                                 | _            | -         | _      | _       | _         | _      | _                                | _           | _        | _      | _       | 0000       |

| 5A30                        | OI IZDINO                       | 15:0      |               | _       | _      |              |                                   |              |           |        | E       | 3RG<12:0> |        |                                  |             |          |        |         | 0000       |

|                             |                                 | 31:16     |               | _       | _      | _            | _                                 |              | _         | _      | _       | _         | _      | _                                | _           | _        | _      | _       | 0000       |

| 5A40                        | SPI2CON2                        | 15:0      | SPI<br>SGNEXT | _       | 1      | FRM<br>ERREN | SPI<br>ROVEN                      | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | _         | _      | 1                                | AUD<br>MONO | 1        | AUDMC  | )D<1:0> | 0000       |

|                             |                                 |           |               |         |        |              |                                   |              |           |        |         |           |        |                                  |             |          |        |         |            |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### REGISTER 17-1: SPIXCON: SPI CONTROL REGISTER (CONTINUED)

- bit 17 SPIFE: Frame Sync Pulse Edge Select bit (Framed SPI mode only)

- 1 = Frame synchronization pulse coincides with the first bit clock

- 0 = Frame synchronization pulse precedes the first bit clock

- bit 16 **ENHBUF**: Enhanced Buffer Enable bit<sup>(2)</sup>

- 1 = Enhanced Buffer mode is enabled

- 0 = Enhanced Buffer mode is disabled

- bit 15 **ON:** SPI Peripheral On bit<sup>(1)</sup>

- 1 = SPI Peripheral is enabled

- 0 = SPI Peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- bit 12 DISSDO: Disable SDOx pin bit

- 1 = SDOx pin is not used by the module. Pin is controlled by associated PORT register

- 0 = SDOx pin is controlled by the module

- bit 11-10 MODE<32.16>: 32/16-Bit Communication Select bits

#### When AUDEN = 1:

| MODE32 | MODE16 | Communication                                         |

|--------|--------|-------------------------------------------------------|

| 1      | 1      | 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame |

| 1      | 0      | 32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame |

| 0      | 1      | 16-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame |

| 0      | 0      | 16-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame |

#### When AUDEN = 0:

| MODE32 | MODE16 | Communication |

|--------|--------|---------------|

| 1      | x      | 32-bit        |

| 0      | 1      | 16-bit        |

| 0      | 0      | 8-bit         |

|        |        |               |

bit 9 SMP: SPI Data Input Sample Phase bit

#### Master mode (MSTEN = 1):

- 1 = Input data sampled at end of data output time

- 0 = Input data sampled at middle of data output time

#### Slave mode (MSTEN = 0):

SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.

To write a '1' to this bit, the MSTEN value = 1 must first be written.

- bit 8 **CKE**: SPI Clock Edge Select bit<sup>(3)</sup>

- 1 = Serial output data changes on transition from active clock state to Idle clock state (see the CKP bit)

- 0 = Serial output data changes on transition from Idle clock state to active clock state (see the CKP bit)

- bit 7 SSEN: Slave Select Enable (Slave mode) bit

- $1 = \overline{SSx}$  pin used for Slave mode

- $0 = \overline{SSx}$  pin not used for Slave mode, pin controlled by port function.

- bit 6 **CKP:** Clock Polarity Select bit<sup>(4)</sup>

- 1 = Idle state for clock is a high level; active state is a low level

- 0 = Idle state for clock is a low level; active state is a high level

- Note 1: When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit can only be written when the ON bit = 0.

- 3: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- **4:** When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

### REGISTER 18-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER (CONTINUED)

- bit 7 **GCEN:** General Call Enable bit (when operating as I<sup>2</sup>C slave)

- 1 = Enable interrupt when a general call address is received in the I2CxRSR (module is enabled for reception)

- 0 = General call address is disabled

- bit 6 **STREN:** SCLx Clock Stretch Enable bit (when operating as I<sup>2</sup>C slave)

Used in conjunction with SCLREL bit.

- 1 = Enable software or receive clock stretching

- 0 = Disable software or receive clock stretching

- bit 5 **ACKDT:** Acknowledge Data bit (when operating as I<sup>2</sup>C master, applicable during master receive)

Value that is transmitted when the software initiates an Acknowledge sequence.

- 1 = Send a NACK during an Acknowledge sequence

- 0 = Send an ACK during an Acknowledge sequence

- bit 4 **ACKEN:** Acknowledge Sequence Enable bit (when operating as I<sup>2</sup>C master, applicable during master receive)

- 1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit. Hardware clear at end of master Acknowledge sequence.

- 0 = Acknowledge sequence not in progress

- bit 3 **RCEN:** Receive Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Enables Receive mode for I<sup>2</sup>C. Hardware clear at end of eighth bit of master receive data byte.

- 0 = Receive sequence not in progress

- bit 2 **PEN:** Stop Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.

- 0 = Stop condition not in progress

- bit 1 **RSEN:** Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence.

- 0 = Repeated Start condition not in progress

- bit 0 **SEN:** Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.

- 0 = Start condition not in progress

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

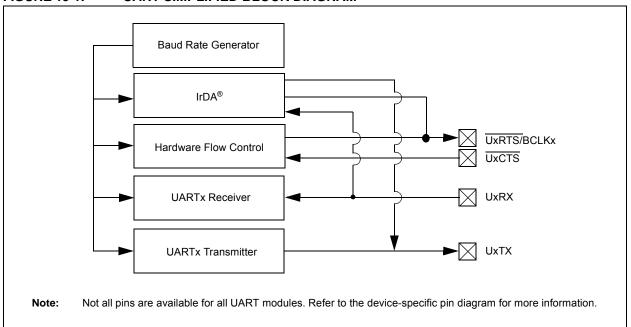

# 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 21.** "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The UART module is one of the serial I/O modules available in PIC32MX1XX/2XX 28/36/44-pin Family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN, and IrDA®. The UART module also supports the hardware flow control option, with UxCTS and UxRTS pins, and also includes an IrDA encoder and decoder.

Key features of the UART module include:

- Full-duplex. 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- · One or two Stop bits

- · Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 38 bps to 12.5 Mbps at 50 MHz

- 8-level deep First In First Out (FIFO) transmit data buffer

- · 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9th bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the UART module.

FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

### 20.1 PMP Control Registers

### TABLE 20-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 | 4         |       |               |       |       |         |        |        | Ві     | ts      |       |           |      |      |       |      |      |            |

|-----------------------------|---------------------------------|-----------|-------|---------------|-------|-------|---------|--------|--------|--------|---------|-------|-----------|------|------|-------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14         | 29/13 | 28/12 | 27/11   | 26/10  | 25/9   | 24/8   | 23/7    | 22/6  | 21/5      | 20/4 | 19/3 | 18/2  | 17/1 | 16/0 | All Resets |

| 7000                        | PMCON                           | 31:16     | _     | _             | -     | _     | _       | _      | _      |        |         | _     | _         | _    | _    | _     | _    | _    | 0000       |

| 7000                        | FIVICOIN                        | 15:0      | ON    | _             | SIDL  | ADRMU | JX<1:0> | PMPTTL | PTWREN | PTRDEN | CSF     | <1:0> | ALP       | _    | CS1P | _     | WRSP | RDSP | 0000       |

| 7010                        | PMMODE                          | 31:16     | -     | _             | ı     | _     | _       | _      | _      | I      | I       | _     | _         | _    | _    | _     | _    |      | 0000       |

| 7010                        | FIVIIVIODE                      | 15:0      | BUSY  | IRQM          | <1:0> | INCM  | <1:0>   |        |        |        |         |       |           |      |      | <1:0> | 0000 |      |            |

|                             | 31:16 — — — — —                 |           |       |               |       | _     | _       | _      |        |        | _       | _     | _         | _    | _    | _     | _    | 0000 |            |

| 7020                        | PMADDR                          | 15:0      | -     | CS1<br>ADDR14 | -     | _     | _       |        |        |        |         | ,     | ADDR<10:0 | >    |      |       |      |      | 0000       |

| 7020                        | PMDOUT                          | 31:16     |       |               |       | •     | •       | •      |        | DATAOL | T-21.05 |       |           |      |      |       |      |      | 0000       |

| 7030                        | PINIDOUT                        | 15:0      |       |               |       |       |         |        |        | DATAOU | 1<31:0> |       |           |      |      |       |      |      | 0000       |

| 7040                        | PMDIN                           | 31:16     |       |               |       |       |         |        |        | DATAIN | 1-21-0> |       |           |      |      |       |      |      | 0000       |

| 7040                        | FINIDIN                         | 15:0      |       |               |       |       |         |        |        | DATAIN | 1.02    |       |           |      |      |       |      |      | 0000       |

| 7050                        | DNAAEN                          | 31:16     | -     | _             | ı     | _     | _       | _      | _      | I      | ı       | _     | _         | _    | _    | _     | _    | -    | 0000       |

| 7050                        | PMAEN                           | 15:0      | 1     | PTEN14        | -     | _     | _       |        |        |        |         | - 1   | PTEN<10:0 | >    |      |       |      |      | 0000       |

| 7060                        | PMSTAT                          | 31:16     | _     | _             | ı     | _     | _       | _      | _      |        |         | _     | _         | _    | _    | _     | _    | _    | 0000       |

| 7000                        | FINIOINI                        | 15:0      | IBF   | IBOV          | I     | _     | IB3F    | IB2F   | IB1F   | IB0F   | OBE     | OBUF  | _         | _    | OB3E | OB2E  | OB1E | OB0E | 008F       |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information

### 25.1 CTMU Control Registers

#### TABLE 25-1: CTMU REGISTER MAP

| ess                      |                                 |           | Bits    |         |          |       |         |          |          |          |         |         |        | <b>(0</b> |          |      |      |       |            |

|--------------------------|---------------------------------|-----------|---------|---------|----------|-------|---------|----------|----------|----------|---------|---------|--------|-----------|----------|------|------|-------|------------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13    | 28/12 | 27/11   | 26/10    | 25/9     | 24/8     | 23/7    | 22/6    | 21/5   | 20/4      | 19/3     | 18/2 | 17/1 | 16/0  | All Resets |

| 4000                     | CTMUCON                         | 31:16     | EDG1MOD | EDG1POL |          | EDG1S | EL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |        | EDG2S     | SEL<3:0> |      | _    | _     | 0000       |

| A200                     | CTMUCON                         | 15:0      | ON      | _       | CTMUSIDL | TGEN  | EDGEN   | EDGSEQEN | IDISSEN  | CTTRIG   |         |         | ITRIM< | <5:0>     |          |      | IRNG | <1:0> | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 27-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 18-10 PWP<8:0>: Program Flash Write-Protect bits(3)

```

Prevents selected program Flash memory pages from being modified during code execution.

111111111 = Disabled

111111110 = Memory below 0x0400 address is write-protected

111111101 = Memory below 0x0800 address is write-protected

111111100 = Memory below 0x0C00 address is write-protected

111111011 = Memory below 0x1000 (4K) address is write-protected

111111010 = Memory below 0x1400 address is write-protected

111111001 = Memory below 0x1800 address is write-protected

111111000 = Memory below 0x1C00 address is write-protected

111110111 = Memory below 0x2000 (8K) address is write-protected

111110110 = Memory below 0x2400 address is write-protected

111110101 = Memory below 0x2800 address is write-protected

111110100 = Memory below 0x2C00 address is write-protected

111110011 = Memory below 0x3000 address is write-protected

111110010 = Memory below 0x3400 address is write-protected

111110001 = Memory below 0x3800 address is write-protected

111110000 = Memory below 0x3C00 address is write-protected

111101111 = Memory below 0x4000 (16K) address is write-protected

110111111 = Memory below 0x10000 (64K) address is write-protected

101111111 = Memory below 0x20000 (128K) address is write-protected

011111111 = Memory below 0x40000 (256K) address is write-protected

000000000 = All possible memory is write-protected

Reserved: Write '1'

ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits(2)

11 = PGEC1/PGED1 pair is used

10 = PGEC2/PGED2 pair is used

01 = PGEC3/PGED3 pair is used

00 = PGEC4/PGED4 pair is used<sup>(2)</sup>

JTAGEN: JTAG Enable bit(1)

1 = JTAG is enabled

0 = JTAG is disabled

DEBUG<1:0>: Background Debugger Enable bits (forced to '11' if code-protect is enabled)

1x = Debugger is disabled

0x = Debugger is enabled

2: The PGEC4/PGED4 pin pair is not available on all devices. Refer to the "Pin Diagrams" section for

```

- Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

- availability.

- 3: The PWP<8:7> bits are only available on devices with 256 KB Flash.

bit 9-5

bit 4-3

bit 2

bit 1-0

#### REGISTER 27-5: CFGCON: CONFIGURATION CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-----------------------|------------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                     | _                      | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | -                 | -                     | _                      | _                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | R/W-0                 | R/W-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 |                   | IOLOCK <sup>(1)</sup> | PMDLOCK <sup>(1)</sup> | _                 | _                 |                  | _                |

| 7.0          | U-0               | U-0               | U-0                   | U-0                    | R/W-1             | U-0               | U-1              | R/W-1            |

| 7:0          | _                 |                   |                       | _                      | JTAGEN            | _                 |                  | TDOEN            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-14 Unimplemented: Read as '0'

bit 13 **IOLOCK:** Peripheral Pin Select Lock bit<sup>(1)</sup>

${\tt 1}$  = Peripheral Pin Select is locked. Writes to PPS registers is not allowed.

0 = Peripheral Pin Select is not locked. Writes to PPS registers is allowed.

bit 12 **PMDLOCK:** Peripheral Module Disable bit<sup>(1)</sup>

1 = Peripheral module is locked. Writes to PMD registers is not allowed.

0 = Peripheral module is not locked. Writes to PMD registers is allowed.

bit 11-4 Unimplemented: Read as '0'

bit 3 JTAGEN: JTAG Port Enable bit

1 = Enable the JTAG port

0 = Disable the JTAG port

bit 2-1 Unimplemented: Read as '1'

bit 0 TDOEN: TDO Enable for 2-Wire JTAG bit

1 = 2-wire JTAG protocol uses TDO

0 = 2-wire JTAG protocol does not use TDO

**Note 1:** To change this bit, the unlock sequence must be performed. Refer to **Section 6. "Oscillator"** (DS60001112) in the "PIC32 Family Reference Manual" for details.

TABLE 30-6: DC CHARACTERISTICS: IDLE CURRENT (IDLE)

| DC CHARACTI                                                        | ERISTICS |     | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                 |      |               |  |  |

|--------------------------------------------------------------------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|---------------|--|--|

| Parameter Typical <sup>(2)</sup> Max.                              |          |     | Units Conditions                                                                                                                                                                                                                               |                 |      |               |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Notes 1, 4) |          |     |                                                                                                                                                                                                                                                |                 |      |               |  |  |

| DC30a                                                              | 1        | 1.5 | mA                                                                                                                                                                                                                                             | 4 MHz (Note 3)  |      |               |  |  |

| DC31a                                                              | 2        | 3   | mA                                                                                                                                                                                                                                             | 10 MHz          |      |               |  |  |

| DC32a                                                              | 4        | 6   | mA                                                                                                                                                                                                                                             | 20 MHz (Note 3) |      |               |  |  |

| DC33a                                                              | 5.5      | 8   | mA                                                                                                                                                                                                                                             | 30 MHz (Note 3) |      |               |  |  |

| DC34a 7.5 11                                                       |          |     | mA                                                                                                                                                                                                                                             | 40 MHz          |      |               |  |  |

| DC37a                                                              | 100      | _   | μA                                                                                                                                                                                                                                             | -40°C           |      | LPRC (31 kHz) |  |  |

| DC37b                                                              | 250      | _   | μA                                                                                                                                                                                                                                             | +25°C           | 3.3V | (Note 3)      |  |  |

| DC37c                                                              | 380      | _   | μA                                                                                                                                                                                                                                             | +85°C           |      |               |  |  |

**Note 1:** The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode (CPU core Halted), and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- · WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- · RTCC and JTAG are disabled

- **2:** Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- 4: IIDLE electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

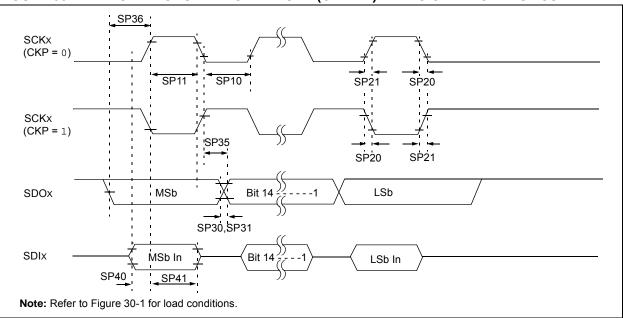

FIGURE 30-11: SPIX MODULE MASTER MODE (CKE = 1) TIMING CHARACTERISTICS

TABLE 30-29: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        | ARACTERIS <sup>*</sup> | rics                                      | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                     |      |       |                    |  |

|---------------|------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|

| Param.<br>No. | Symbol                 | Characteristics <sup>(1)</sup>            | Min.                                                                                                                                                                                                                                            | Typ. <sup>(2)</sup> | Max. | Units | Conditions         |  |

| SP10          | TscL                   | SCKx Output Low Time (Note 3)             | Tsck/2                                                                                                                                                                                                                                          | _                   |      | ns    | _                  |  |

| SP11          | TscH                   | SCKx Output High Time (Note 3)            | Tsck/2                                                                                                                                                                                                                                          | _                   | _    | ns    | _                  |  |

| SP20          | TscF                   | SCKx Output Fall Time (Note 4)            | _                                                                                                                                                                                                                                               | _                   | _    | ns    | See parameter DO32 |  |

| SP21          | TscR                   | SCKx Output Rise Time (Note 4)            | _                                                                                                                                                                                                                                               | _                   | _    | ns    | See parameter DO31 |  |

| SP30          | TDOF                   | SDOx Data Output Fall Time (Note 4)       | _                                                                                                                                                                                                                                               | _                   | _    | ns    | See parameter DO32 |  |

| SP31          | TDOR                   | SDOx Data Output Rise Time (Note 4)       | _                                                                                                                                                                                                                                               | _                   | _    | ns    | See parameter DO31 |  |

| SP35          | TscH2DoV,              | SDOx Data Output Valid after              |                                                                                                                                                                                                                                                 | _                   | 15   | ns    | VDD > 2.7V         |  |

|               | TscL2DoV               | SCKx Edge                                 | _                                                                                                                                                                                                                                               | _                   | 20   | ns    | VDD < 2.7V         |  |

| SP36          | TDOV2SC,<br>TDOV2SCL   | SDOx Data Output Setup to First SCKx Edge | 15                                                                                                                                                                                                                                              | _                   | _    | ns    | _                  |  |

| SP40          | TDIV2scH,              | Setup Time of SDIx Data Input to          | 15                                                                                                                                                                                                                                              | _                   | _    | ns    | VDD > 2.7V         |  |

|               | TDIV2scL               | SCKx Edge                                 | 20                                                                                                                                                                                                                                              | _                   | _    | ns    | VDD < 2.7V         |  |

| SP41          | TscH2DIL,              | Hold Time of SDIx Data Input              | 15                                                                                                                                                                                                                                              | _                   | _    | ns    | VDD > 2.7V         |  |

|               | TscL2DIL               | to SCKx Edge                              | 20                                                                                                                                                                                                                                              |                     | _    | ns    | VDD < 2.7V         |  |

- **Note 1:** These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The minimum clock period for SCKx is 50 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

| PIC32WX1XX/2XX 28/36/44-PIN FAWILY |  |                |                      |                            |                             |  |

|------------------------------------|--|----------------|----------------------|----------------------------|-----------------------------|--|

|                                    |  |                |                      |                            |                             |  |

|                                    |  |                |                      |                            |                             |  |

|                                    |  |                |                      |                            |                             |  |

|                                    |  |                |                      |                            |                             |  |

|                                    |  |                |                      |                            |                             |  |

|                                    |  |                |                      |                            |                             |  |

|                                    |  |                |                      |                            |                             |  |

|                                    |  |                |                      |                            |                             |  |

|                                    |  |                |                      |                            |                             |  |

|                                    |  |                |                      |                            |                             |  |

|                                    |  |                |                      |                            |                             |  |

|                                    |  |                |                      |                            |                             |  |

|                                    |  |                |                      |                            |                             |  |

|                                    |  | 1XX/2XX 28/36/ | 1XX/2XX 28/36/44-PIN | 1XX/2XX 28/36/44-PIN FAMIL | 1XX/2XX 28/36/44-PIN FAMILY |  |

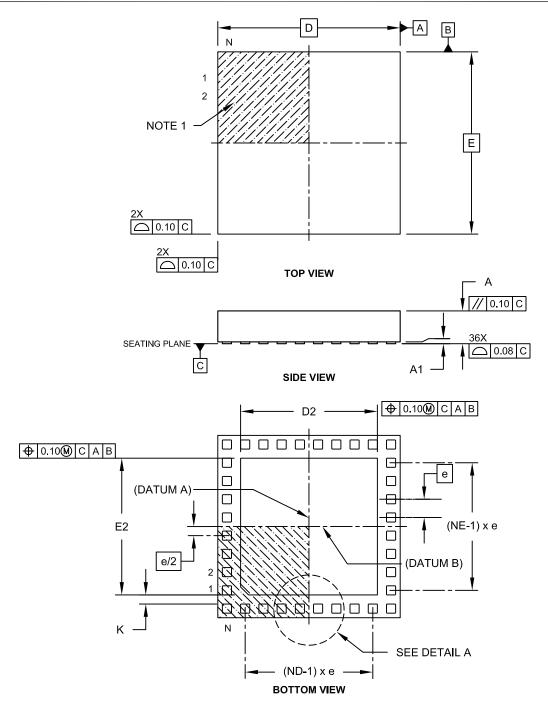

## 36-Terminal Very Thin Thermal Leadless Array Package (TL) – 5x5x0.9 mm Body with Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-187C Sheet 1 of 2

### Revision J (April 2016)

This revision includes the following major changes as described in Table A-8, as well as minor updates to text and formatting, which were incorporated throughout the document.

#### TABLE A-8: MAJOR SECTION UPDATES

| Section                                                                                                                                | Update Description                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to<br>256 KB Flash and 64 KB<br>SRAM) with Audio and<br>Graphics Interfaces, USB, and<br>Advanced Analog" | The PIC32MX270FDB device and Note 4 were added to TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features".                         |

| 2.0 "Guidelines for Getting Started with 32-bit MCUs"                                                                                  | EXAMPLE 2-1: "Crystal Load Capacitor Calculation" was updated.                                                                    |

| 30.0 "Electrical<br>Characteristics"                                                                                                   | Parameter DO50a (Csosc) was removed from the Capacitive Loading Requirements on Output Pins AC Characteristics (see Table 30-16). |

| "Product Identification<br>System"                                                                                                     | The device mapping was updated to include type B for Software Targeting.                                                          |