Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 16KB (16K × 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx110f016d-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 6: PIN NAMES FOR 28-PIN USB DEVICES

## 28-PIN QFN (TOP VIEW)<sup>(1,2,3,4)</sup>

PIC32MX210F016B PIC32MX220F032B PIC32MX230F064B PIC32MX230F256B PIC32MX250F128B PIC32MX250F128B

28

1

| Pin # | Full Pin Name                              | Pin # | Full Pin Name                                    |

|-------|--------------------------------------------|-------|--------------------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0  | 15    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1 | 16    | Vss                                              |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2  | 17    | VCAP                                             |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3    | 18    | PGED2/RPB10/D+/CTED11/RB10                       |

| 5     | Vss                                        | 19    | PGEC2/RPB11/D-/RB11                              |

| 6     | OSC1/CLKI/RPA2/RA2                         | 20    | VUSB3V3                                          |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3                    | 21    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 8     | SOSCI/RPB4/RB4                             | 22    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4             | 23    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 10    | Vdd                                        | 24    | AVss                                             |

| 11    | TMS/RPB5/USBID/RB5                         | 25    | AVDD                                             |

| 12    | VBUS                                       | 26    | MCLR                                             |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7               | 27    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8              | 28    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: Shaded pins are 5V tolerant.

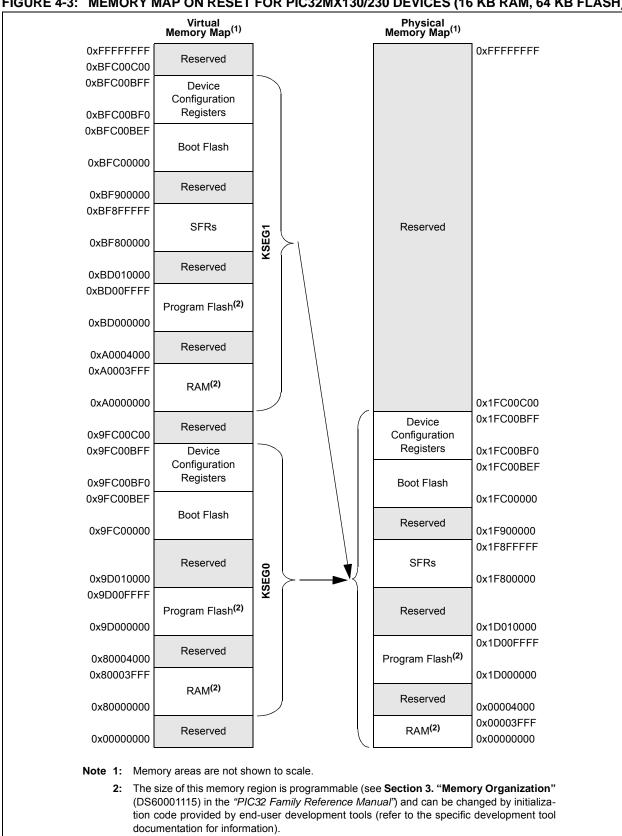

#### FIGURE 4-3: MEMORY MAP ON RESET FOR PIC32MX130/230 DEVICES (16 KB RAM, 64 KB FLASH)

## 8.1 Oscillator Control Regiters

| TABLE 8-1: OSCILLATOR CONTROL REGISTER MAP                      |             |           |                                    |       |          |              |           |       |               |      |         |                      |                |       |              |                       |        |                     |           |

|-----------------------------------------------------------------|-------------|-----------|------------------------------------|-------|----------|--------------|-----------|-------|---------------|------|---------|----------------------|----------------|-------|--------------|-----------------------|--------|---------------------|-----------|

| ess                                                             |             | 0         |                                    |       |          |              |           |       |               |      | Bits    |                      |                |       |              |                       |        |                     | ú         |

| Virtual Address<br>(BF80_#)<br>Register<br>Name <sup>(†</sup> ) |             | Bit Range | 31/15                              | 30/14 | 29/13    | 28/12        | 27/11     | 26/10 | 25/9          | 24/8 | 23/7    | 22/6                 | 21/5           | 20/4  | 19/3         | 18/2                  | 17/1   | 16/0                | All Reset |

| F000                                                            | F000 OSCCON | 31:16     | —                                  | _     | Р        | PLLODIV<2:0> |           |       | FRCDIV<2:0> — |      | SOSCRDY | PBDIVRDY             | RDY PBDIV<1:0> |       | PLLMULT<2:0> |                       |        | x1xx <sup>(2)</sup> |           |

| FUUU                                                            | 030001      | 15:0      | —                                  |       | COSC<2:0 | OSC<2:0> —   |           |       | NOSC<2:0>     |      | CLKLOCK | ULOCK <sup>(3)</sup> | SLOCK          | SLPEN | CF           | UFRCEN <sup>(3)</sup> | SOSCEN | OSWEN               | xxxx(2)   |

| F010                                                            | OSCTUN      | 31:16     | _                                  | _     |          | _            | _         |       |               | _    | _       | _                    | _              | _     |              | _                     | —      | _                   | 0000      |

| 1010                                                            | 030101      | 15:0      | _                                  | _     |          | _            | _         |       |               | _    | _       | _                    |                |       | TUN          | l<5:0>                |        |                     | 0000      |

| 5000                                                            |             | 31:16     | _                                  |       |          |              |           |       |               |      | RODIV<1 | 4:0>                 |                |       |              |                       |        |                     | 0000      |

| F020                                                            | REFOCON     | 15:0      | ON - SIDL OE RSLP - DIVSWEN ACTIVE |       |          |              |           |       |               | ROSE | _<3:0>  |                      | 0000           |       |              |                       |        |                     |           |

| F000                                                            | DEFOTDIM    | 31:16     |                                    |       |          | R            | OTRIM<8:0 | )>    |               |      |         | _                    | _              | _     | _            | _                     | _      | _                   | 0000      |

| F030                                                            | REFOTRIM    | 15:0      | _                                  | _     |          | _            | _         |       |               | -    | _       | _                    | _              | _     |              | _                     | —      | _                   | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on PIC32MX2XX devices.

## 9.1 DMA Control Registers

#### TABLE 9-1: DMA GLOBAL REGISTER MAP

| ess                         |                                 | Ċ,        |               |       |       |         |         |       |      | Bi   | ts      |      |      |      |      |      |           |      | s         |

|-----------------------------|---------------------------------|-----------|---------------|-------|-------|---------|---------|-------|------|------|---------|------|------|------|------|------|-----------|------|-----------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14 | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8 | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Reset |

| 2000                        | DMACON                          | 31:16     | _             | _     | -     | —       | —       | _     | —    | —    | —       | -    | -    | _    | -    | -    | —         | _    | 0000      |

| 3000                        | DIVIACON                        | 15:0      | ON            | —     | _     | SUSPEND | DMABUSY | —     | _    | —    | _       | —    | —    | —    | —    | —    | —         | _    | 0000      |

| 2010                        | DMASTAT                         | 31:16     | -             | _     | —     | —       | —       | —     | —    | —    | _       | _    | _    | _    | _    | —    | —         | _    | 0000      |

| 3010                        | DIVIASTAT                       | 15:0      | -             | _     | —     | —       | —       | —     | —    | —    | _       | _    | _    | _    | RDWR | DI   | MACH<2:0> | .(2) | 0000      |

| 3020                        | DMAADDR                         | 31:16     |               |       |       |         |         |       |      |      | D-31:05 |      |      |      |      |      |           |      | 0000      |

| 3020                        | DIVIAADDR                       | 15:0      | DMAADDR<31:0> |       |       |         |         |       |      |      | 0000    |      |      |      |      |      |           |      |           |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### TABLE 9-2: DMA CRC REGISTER MAP

| ess                         |                                 | â         |       |                | -     |       |       |           |      | В    | ts        |        | -      |      |      |      |           |      |            |

|-----------------------------|---------------------------------|-----------|-------|----------------|-------|-------|-------|-----------|------|------|-----------|--------|--------|------|------|------|-----------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14          | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7      | 22/6   | 21/5   | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Resets |

| 2020                        | DCRCCON                         | 31:16     | —     | _              | BYTO  | <1:0> | WBO   | —         | —    | BITO | _         | —      | —      | _    | _    | _    | —         | _    | 0000       |

| 3030                        | DURUUUN                         | 15:0      | —     | _              | —     |       |       | PLEN<4:0> |      |      | CRCEN     | CRCAPP | CRCTYP | —    | —    | C    | CRCCH<2:0 | >    | 0000       |

| 2040                        | DCRCDATA                        | 31:16     |       |                |       |       |       |           |      |      | TA ~21:05 |        |        |      |      |      |           |      | 0000       |

| 3040                        | DURUDAIA                        | 15:0      |       | DCRCDATA<31:0> |       |       |       |           |      |      |           |        |        |      |      |      |           |      |            |

| 3050                        | DCRCXOR                         | 31:16     |       | DCRCXOR<31:0>  |       |       |       |           |      |      |           |        |        |      |      |      |           |      |            |

| 3050                        | DUNUAUR                         | 15:0      |       | 0000           |       |       |       |           |      |      |           |        |        |      |      |      |           |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6       | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------------|-------------------------|-------------------|----------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 31.24        | —                 | _                       | _                       | _                 | —                    | —                 | -                     | —                       |

| 23:16        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 23.10        | —                 | _                       | _                       | _                 | —                    | —                 | -                     | —                       |

| 15:8         | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 15.6         | —                 | _                       | _                       | _                 | —                    | —                 | —                     | —                       |

|              | R/WC-0, HS        | R/WC-0, HS              | R/WC-0, HS              | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS        | R-0                   | R/WC-0, HS              |

| 7:0          | STALLIF           | ATTACHIF <sup>(1)</sup> | RESUMEIF <sup>(2)</sup> | IDLEIF            | TRNIF <sup>(3)</sup> | SOFIF             | UERRIF <sup>(4)</sup> | URSTIF <sup>(5)</sup>   |

|              | STALLIF           |                         | INE SOMEIFY /           | IDLEIF            |                      | JOFIE             |                       | DETACHIF <sup>(6)</sup> |

## REGISTER 10-6: U1IR: USB INTERRUPT REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settat | ble bit            |

|-------------------|-------------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7       | <b>STALLIF:</b> STALL Handshake Interrupt bit<br>1 = In Host mode a STALL handshake was received during the handshake phase of the transaction<br>In Device mode a STALL handshake was transmitted during the handshake phase of the transaction<br>0 = STALL handshake has not been sent                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6       | ATTACHIF: Peripheral Attach Interrupt bit <sup>(1)</sup><br>1 = Peripheral attachment was detected by the USB module<br>0 = Peripheral attachment was not detected                                                                                                                                                                                                                                                                               |

| bit 5       | <b>RESUMEIF:</b> Resume Interrupt bit <sup>(2)</sup><br>1 = K-State is observed on the D+ or D- pin for 2.5 μs<br>0 = K-State is not observed                                                                                                                                                                                                                                                                                                    |

| bit 4       | IDLEIF: Idle Detect Interrupt bit<br>1 = Idle condition detected (constant Idle state of 3 ms or more)<br>0 = No Idle condition detected                                                                                                                                                                                                                                                                                                         |

| bit 3       | <b>TRNIF:</b> Token Processing Complete Interrupt bit <sup>(3)</sup><br>1 = Processing of current token is complete; a read of the U1STAT register will provide endpoint information<br>0 = Processing of current token not complete                                                                                                                                                                                                             |

| bit 2       | <b>SOFIF:</b> SOF Token Interrupt bit<br>1 = SOF token received by the peripheral or the SOF threshold reached by the host<br>0 = SOF token was not received nor threshold reached                                                                                                                                                                                                                                                               |

| bit 1       | <b>UERRIF</b> : USB Error Condition Interrupt bit <sup>(4)</sup><br>1 = Unmasked error condition has occurred<br>0 = Unmasked error condition has not occurred                                                                                                                                                                                                                                                                                   |

| bit 0       | <pre>URSTIF: USB Reset Interrupt bit (Device mode)<sup>(5)</sup> 1 = Valid USB Reset has occurred 0 = No USB Reset has occurred DETACHIF: USB Detach Interrupt bit (Host mode)<sup>(6)</sup> 1 = Peripheral detachment was detected by the USB module 0 = Peripheral detachment was not detected</pre>                                                                                                                                           |

| 3<br>2<br>5 | <ul> <li>This bit is valid only if the HOSTEN bit is set (see Register 10-11), there is no activity on the USB for 2.5 µs, and the current bus state is not SE0.</li> <li>When not in Suspend mode, this interrupt should be disabled.</li> <li>Clearing this bit will cause the STAT FIFO to advance.</li> <li>Only error conditions enabled through the U1EIE register will set this bit.</li> <li>Device mode.</li> <li>Host mode.</li> </ul> |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        |                   | —                 |                   | —                 |                   |                   |                  | —                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        |                   | —                 |                   | —                 | -                 |                   |                  | —                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | -                 | —                 | -                 | —                 | _                 | -                 | —                | —                |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7.0          | LSPDEN            | DEVADDR<6:0>      |                   |                   |                   |                   |                  |                  |  |  |  |

## REGISTER 10-12: U1ADDR: USB ADDRESS REGISTER

## Legend:

| U                 |                  |                                        |                    |  |  |  |

|-------------------|------------------|----------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | Dit U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                   | x = Bit is unknown |  |  |  |

bit 31-8 Unimplemented: Read as '0'

bit 7 LSPDEN: Low-Speed Enable Indicator bit

1 = Next token command to be executed at Low-Speed

0 = Next token command to be executed at Full-Speed

bit 6-0 **DEVADDR<6:0>:** 7-bit USB Device Address bits

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | —                 | _                 | —                 | _                 | —                |                  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | _                 | —                 | _                 | —                |                  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | —                 | —                 | —                 | -                 | —                 | _                 | —                | -                |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   | FRML<7:0>         |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 10-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FRML<7:0>:** The 11-bit Frame Number Lower bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0        |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|-------------------------|

| 31:24        | U-0 U-0              |                   | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 31.24        |                      |                   | —                 | —                 | —                        | —                 | _                | —                       |

| 23:16        | U-0 U-0              |                   | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 23.10        |                      |                   | —                 | —                 | —                        | —                 | _                | —                       |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                   |

| 10.0         | SPISGNEXT            | —                 | —                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                  |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                   |

| 7:0          | AUDEN <sup>(1)</sup> | _                 | _                 | —                 | AUDMONO <sup>(1,2)</sup> | —                 | AUDMOD           | )<1:0> <sup>(1,2)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-16 Unimplemented: Read as '0'

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extended

- bit 14-13 Unimplemented: Read as '0'

- bit 12 **FRMERREN:** Enable Interrupt Events via FRMERR bit

- 1 = Frame Error overflow generates error events

- 0 = Frame Error does not generate error events

- bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

- 1 = Receive overflow generates error events

- 0 = Receive overflow does not generate error events

- bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit

- 1 = Transmit underrun generates error events

- 0 = Transmit underrun does not generate error events

- bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions)

- 1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data

0 = A ROV is a critical error that stops SPI operation

- bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

- 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

- 0 = A TUR is a critical error that stops SPI operation

- bit 7 AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup>

- 1 = Audio protocol enabled

- 0 = Audio protocol disabled

- bit 6-5 Unimplemented: Read as '0'

- bit 3 AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup>

- 1 = Audio data is mono (Each data word is transmitted on both left and right channels)

- 0 = Audio data is stereo

- bit 2 Unimplemented: Read as '0'

- bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup>

- 11 = PCM/DSP mode

- 10 = Right-Justified mode

- 01 = Left-Justified mode

- $00 = I^2S \mod$

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

| REGISTE | R 18-1:           | I2CxCON: I <sup>2</sup> C CONTROL REGISTER (CONTINUED)                                                                                                                |

|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7   | GCEN: Ge          | eneral Call Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                     |

|         | (module           | interrupt when a general call address is received in the I2CxRSR<br>e is enabled for reception)                                                                       |

|         |                   | al call address is disabled                                                                                                                                           |

| bit 6   | STREN: S          | CLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)                                                                                               |

|         |                   | njunction with SCLREL bit.                                                                                                                                            |

|         |                   | e software or receive clock stretching                                                                                                                                |

| L:1 F   |                   | e software or receive clock stretching                                                                                                                                |

| bit 5   |                   | cknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive) is transmitted when the software initiates an Acknowledge sequence. |

|         |                   | a NACK during an Acknowledge sequence                                                                                                                                 |

|         |                   | an ACK during an Acknowledge sequence                                                                                                                                 |

| bit 4   | ACKEN: A receive) | cknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master                                                                   |

|         | Hardwa            | Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.<br>are clear at end of master Acknowledge sequence.<br>wledge sequence not in progress        |

| bit 3   | RCEN: Re          | ceive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                          |

|         |                   | es Receive mode for I <sup>2</sup> C. Hardware clear at end of eighth bit of master receive data byte.<br>The sequence not in progress                                |

| bit 2   | PEN: Stop         | Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                      |

|         |                   | Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence. ondition not in progress                                                         |

| bit 1   | RSEN: Re          | peated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                         |

|         |                   | Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of Repeated Start sequence.                                                                     |

|         | 0 = Repeat        | ted Start condition not in progress                                                                                                                                   |

| bit 0   |                   | Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                      |

|         |                   | Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence. ondition not in progress                                                       |

|         |                   |                                                                                                                                                                       |

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | -                 | _                 | _                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | -                 | _                 | -                 | _                 | -                | —                |

| 45.0         | R-0               | R/W-0, HSC        | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | _                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HSC        | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              | _                 | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

#### REGISTER 20-5: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Legend:           | HSC = Set by Hardware; Cleared by Software |                                                     |                    |  |  |  |  |  |

|-------------------|--------------------------------------------|-----------------------------------------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit                           | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                           | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 IBF: Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer occurred (must be cleared in software)0 = No overflow occurred

- bit 13-12 Unimplemented: Read as '0'

- bit 11-8 IBxF: Input Buffer 'x' Status Full bits

- 1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input Buffer does not contain any unread data

- bit 7 **OBE:** Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

- bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = No underflow occurred

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

#### REGISTER 22-1: AD1CON1: ADC CONTROL REGISTER 1 (CONTINUED)

bit 4 **CLRASAM:** Stop Conversion Sequence bit (when the first ADC interrupt is generated)

- 1 = Stop conversions when the first ADC interrupt is generated. Hardware clears the ASAM bit when the ADC interrupt is generated.

- 0 = Normal operation, buffer contents will be overwritten by the next conversion sequence

- bit 3 Unimplemented: Read as '0'

- bit 2 **ASAM:** ADC Sample Auto-Start bit

1 = Sampling begins immediately after last conversion completes; SAMP bit is automatically set.

- 0 = Sampling begins when SAMP bit is set

- bit 1 SAMP: ADC Sample Enable bit<sup>(2)</sup>

1 = The ADC sample and hold amplifier is sampling

0 = The ADC sample/hold amplifier is holding

When ASAM = 0, writing '1' to this bit starts sampling.

When SSRC = 000, writing '0' to this bit will end sampling and start conversion.

- bit 0 DONE: Analog-to-Digital Conversion Status bit<sup>(3)</sup>

1 = Analog-to-digital conversion is done

0 = Analog-to-digital conversion is not done or has not started Clearing this bit will not affect any operation in progress.

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ '0', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.04        | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        | CH0NB             | _                 | _                 | _                 |                   | CH0SB             | <3:0>            |                  |  |  |  |  |  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | CH0NA             |                   | _                 | _                 | CH0SA<3:0>        |                   |                  |                  |  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0 U-0           |                   | U-0 U-0           |                   | U-0              | U-0              |  |  |  |  |  |

| 15:8         | _                 | _                 | _                 | _                 | _                 |                   | _                | -                |  |  |  |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 7:0          |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

#### REGISTER 22-4: AD1CHS: ADC INPUT SELECT REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 31 |          | CH0NB: Negative Input Select bit for Sample B                                                                                        |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------|

|        |          | 1 = Channel 0 negative input is AN1                                                                                                  |

|        |          | 0 = Channel 0 negative input is VREFL                                                                                                |

| bit 30 | -28      | Unimplemented: Read as '0'                                                                                                           |

| bit 27 | -24      | CH0SB<3:0>: Positive Input Select bits for Sample B                                                                                  |

|        |          | 1111 = Channel 0 positive input is Open <sup>(1)</sup>                                                                               |

|        |          | 1110 = Channel 0 positive input is IVREF <sup>(2)</sup>                                                                              |

|        |          | 1101 = Channel 0 positive input is CTMU temperature sensor (CTMUT) <sup>(3)</sup>                                                    |

|        |          | 1100 = Channel 0 positive input is AN12 <sup>(4)</sup>                                                                               |

|        |          | •                                                                                                                                    |

|        |          | •                                                                                                                                    |

|        |          | •                                                                                                                                    |

|        |          | 0001 = Channel 0 positive input is AN1                                                                                               |

|        |          | 0000 = Channel 0 positive input is AN0                                                                                               |

| bit 23 |          | <b>CH0NA:</b> Negative Input Select bit for Sample A Multiplexer Setting <sup>(2)</sup>                                              |

|        |          | 1 = Channel 0 negative input is AN1                                                                                                  |

|        | ~ ~      | 0 = Channel 0 negative input is VREFL                                                                                                |

| bit 22 | -20      | Unimplemented: Read as '0'                                                                                                           |

| bit 19 | -16      | CH0SA<3:0>: Positive Input Select bits for Sample A Multiplexer Setting                                                              |

|        |          | 1111 = Channel 0 positive input is Open <sup>(1)</sup>                                                                               |

|        |          | 1110 = Channel 0 positive input is IVREF <sup>(2)</sup>                                                                              |

|        |          | 1101 = Channel 0 positive input is CTMU temperature (CTMUT) <sup>(3)</sup><br>1100 = Channel 0 positive input is AN12 <sup>(4)</sup> |

|        |          |                                                                                                                                      |

|        |          |                                                                                                                                      |

|        |          |                                                                                                                                      |

|        |          | - Channel O positive input in AN1                                                                                                    |

|        |          | 0001 = Channel 0 positive input is AN1<br>0000 = Channel 0 positive input is AN0                                                     |

| bit 15 | 0        | Unimplemented: Read as '0'                                                                                                           |

| bit 15 | -0       | Ommplemented. Nead as 0                                                                                                              |

| Note   | 1:       | This selection is only used with CTMU capacitive and time measurement.                                                               |

|        | 2:       | See Section 24.0 "Comparator Voltage Reference (CVREF)" for more information.                                                        |

|        | 3:       | See Section 25.0 "Charge Time Measurement Unit (CTMU)" for more information.                                                         |

|        | 3.<br>4: | AN12 is only available on 44-pin devices. AN6-AN8 are not available on 28-pin devices.                                               |

|        | т.       |                                                                                                                                      |

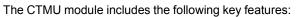

## 25.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that has a configurable current source with a digital configuration circuit built around it. The CTMU can be used for differential time measurement between pulse sources and can be used for generating an asynchronous pulse. By working with other on-chip analog modules, the CTMU can be used for high resolution time measurement, measure capacitance, measure relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

- Up to 13 channels available for capacitive or time measurement input

- · On-chip precision current source

- 16-edge input trigger sources

- · Selection of edge or level-sensitive inputs

- · Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · High precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- · Integrated temperature sensing diode

- · Control of current source during auto-sampling

- · Four current source ranges

- · Time measurement resolution of one nanosecond

A block diagram of the CTMU is shown in Figure 25-1.

© 2011-2016 Microchip Technology Inc.

NOTES:

## 26.0 POWER-SAVING FEATURES

| Note: | This data sheet summarizes the features<br>of the PIC32MX1XX/2XX 28/36/44-pin<br>Family of devices. It is not intended to be<br>a comprehensive reference source. To<br>complement the information in this data<br>sheet, refer to <b>Section 10. "Power-</b><br><b>Saving Features"</b> (DS60001130), which<br>is available from the <i>Documentation</i> ><br><i>Reference Manual</i> section of the<br>Microchip PIC32 web site |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | (www.microchip.com/pic32).                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | (                                                                                                                                                                                                                                                                                                                                                                                                                                  |

This section describes power-saving features for the PIC32MX1XX/2XX 28/36/44-pin Family. The PIC32 devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

## 26.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the PBCLK and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers

- LPRC Run mode: the CPU is clocked from the LPRC clock source

- Sosc Run mode: the CPU is clocked from the Sosc clock source

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

## 26.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as follows:

- Posc Idle mode: the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- Sosc Idle mode: the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

- Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

## 26.3 Power-Saving Operation

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

## 26.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- The CPU is halted

- The system clock source is typically shutdown. See Section 26.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

- The USB module can override the disabling of the Posc or FRC. Refer to the USB section for specific details.

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption

## 27.2 Configuration Registers

## TABLE 27-1: DEVCFG: DEVICE CONFIGURATION WORD SUMMARY

| ess (                       |                  | e         |                       |          |         |          |       |          |           | Bits                |        |        |            |       |        |           |             |        | ú         |

|-----------------------------|------------------|-----------|-----------------------|----------|---------|----------|-------|----------|-----------|---------------------|--------|--------|------------|-------|--------|-----------|-------------|--------|-----------|

| Virtual Address<br>(BFC0_#) | Register<br>Name | Bit Range | 31/15                 | 30/14    | 29/13   | 28/12    | 27/11 | 26/10    | 25/9      | 24/8                | 23/7   | 22/6   | 21/5       | 20/4  | 19/3   | 18/2      | 17/1        | 16/0   | All Reset |

|                             | DEVCFG3          | 31:16     | FVBUSONIO             | FUSBIDIO | IOL1WAY | PMDL1WAY | _     | -        | _         | —                   | —      | -      | -          | _     | -      | —         | —           | -      | xxxx      |

| UDFU                        | DEVCEGS          | 15:0      | USERID<15:0>          |          |         |          |       |          |           |                     |        | xxxx   |            |       |        |           |             |        |           |

|                             | DEVCFG2          | 31:16     | —                     | _        | —       | —        | —     | —        | _         |                     | —      | _      | —          | —     | _      | FP        | LLODIV<2:   | 0>     | xxxx      |

|                             |                  | 15:0      | UPLLEN <sup>(1)</sup> |          | _       | _        | _     | UPL      | LIDIV<2:0 | <sub>&gt;</sub> (1) | _      | FI     | PLLMUL<2:( | )>    | _      | FF        | PLLIDIV<2:0 | )>     | xxxx      |

|                             | DEVCFG1          | 31:16     | _                     |          | _       | _        | _     | _        | FWDTWI    | NSZ<1:0>            | FWDTEN | WINDIS | —          |       | ١      | WDTPS<4:0 | )>          |        | xxxx      |

|                             |                  | 15:0      | FCKSM                 | <1:0>    | FPBD    | IV<1:0>  | _     | OSCIOFNC | POSCM     | OD<1:0>             | IESO   |        | FSOSCEN    | _     | _      | F         | NOSC<2:0>   | >      | xxxx      |

|                             | DEVCFG0          | 31:16     | _                     | _        | —       | CP       | —     | —        | _         | BWP                 | —      | _      | —          | —     | _      | F         | PWP<8:6>(2) | )      | xxxx      |

| UBEC                        |                  | 15:0      |                       |          | PWP<    | :5:0>    |       |          |           |                     | _      | _      | _          | ICESE | L<1:0> | JTAGEN    | DEBUG       | G<1:0> | xxxx      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on PIC32MX2XX devices.

2: PWP<8:7> are only available on devices with 256 KB of Flash.

## TABLE 27-2: DEVICE ID, REVISION, AND CONFIGURATION SUMMARY

| ess                         |                       | 0         | Bits         |                                          |        |         |       |       |      |        |         |                     |      | (1)  |        |      |      |       |                     |

|-----------------------------|-----------------------|-----------|--------------|------------------------------------------|--------|---------|-------|-------|------|--------|---------|---------------------|------|------|--------|------|------|-------|---------------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15        | 30/14                                    | 29/13  | 28/12   | 27/11 | 26/10 | 25/9 | 24/8   | 23/7    | 22/6                | 21/5 | 20/4 | 19/3   | 18/2 | 17/1 | 16/0  | All Resets          |

| F220                        | DEVID                 | 31:16     |              | VER<3:0> DEVID<27:16> xxxx <sup>(1</sup> |        |         |       |       |      |        |         | xxxx <sup>(1)</sup> |      |      |        |      |      |       |                     |

| F220                        | DEVID                 | 15:0      |              |                                          |        |         |       |       |      | DEVID  | <15:0>  |                     |      |      |        |      |      |       | xxxx <sup>(1)</sup> |

| F000                        |                       | 31:16     | -            | _                                        | _      | _       | -     | _     | _    | _      | _       | _                   | _    | _    | _      | -    | _    | _     | 0000                |

|                             | CFGCON                | 15:0      |              | _                                        | IOLOCK | PMDLOCK |       | _     | _    | _      | —       | _                   | _    | _    | JTAGEN | -    | _    | TDOEN | 000B                |

| F000                        | SYSKEY <sup>(3)</sup> | 31:16     |              |                                          |        |         |       |       |      | evere) | /~31.0> |                     |      |      |        |      |      |       | 0000                |

| F230                        | STOKET                | 15:0      | SYSKEY<31:0> |                                          |        |         |       |       |      |        |         | 0000                |      |      |        |      |      |       |                     |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset values are dependent on the device variant.

## 28.0 INSTRUCTION SET

The PIC32MX1XX/2XX family instruction set complies with the MIPS32<sup>®</sup> Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

**Note:** Refer to *"MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set"* at www.imgtec.com for more information.

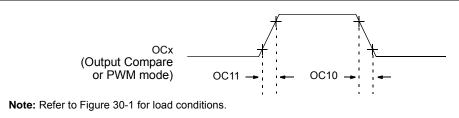

#### FIGURE 30-8: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

#### TABLE 30-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHA        | RACTER | ISTICS                         | (unless | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |                    |  |  |  |

|---------------|--------|--------------------------------|---------|------------------------------------------------------|------|-------|--------------------|--|--|--|

| Param.<br>No. | Symbol | Characteristics <sup>(1)</sup> | Min.    | Typical <sup>(2)</sup>                               | Max. | Units | Conditions         |  |  |  |

| OC10          | TccF   | OCx Output Fall Time           | —       | —                                                    | _    | ns    | See parameter DO32 |  |  |  |

| OC11          | TccR   | OCx Output Rise Time           | —       | See parameter DO31                                   |      |       |                    |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

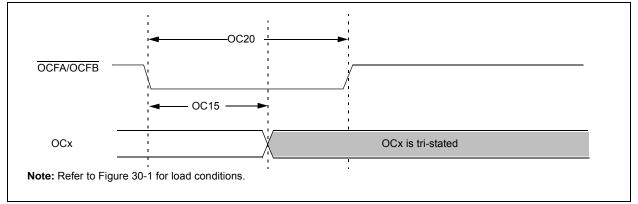

#### FIGURE 30-9: OCx/PWM MODULE TIMING CHARACTERISTICS

#### TABLE 30-27: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                        |     |       |            |  |

|--------------------|--------|--------------------------------|-------------------------------------------------------|------------------------|-----|-------|------------|--|

| Param<br>No.       | Symbol | Characteristics <sup>(1)</sup> | Min                                                   | Typical <sup>(2)</sup> | Max | Units | Conditions |  |

| OC15               | Tfd    | Fault Input to PWM I/O Change  | —                                                     | —                      | 50  | ns    | _          |  |

| OC20               | TFLT   | Fault Input Pulse Width        | 50                                                    | —                      |     | ns    | —          |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 30-41: CTMU CURRENT SOURCE SPECIFICATIONS

| DC CHARACTERISTICS |           |                                                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |      |       |                                  |  |

|--------------------|-----------|----------------------------------------------------|------------------------------------------------------|-------|------|-------|----------------------------------|--|

| Param<br>No.       | Symbol    | Characteristic                                     | Min.                                                 | Тур.  | Max. | Units | Conditions                       |  |

| CTMU CUR           | RENT SOUR | CE                                                 | •                                                    | •     |      |       |                                  |  |

| CTMUI1             | Ιουτ1     | Base Range <sup>(1)</sup>                          | _                                                    | 0.55  | _    | μA    | CTMUCON<9:8> = 01                |  |

| CTMUI2             | Ιουτ2     | 10x Range <sup>(1)</sup>                           | _                                                    | 5.5   |      | μA    | CTMUCON<9:8> = 10                |  |

| CTMUI3             | Ιουτ3     | 100x Range <sup>(1)</sup>                          | _                                                    | 55    |      | μA    | CTMUCON<9:8> = 11                |  |

| CTMUI4             | IOUT4     | 1000x Range <sup>(1)</sup>                         | _                                                    | 550   |      | μA    | CTMUCON<9:8> = 00                |  |

| CTMUFV1            | VF        | Temperature Diode Forward Voltage <sup>(1,2)</sup> | —                                                    | 0.598 | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 01 |  |

|                    |           |                                                    | _                                                    | 0.658 | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 10 |  |

|                    |           |                                                    | —                                                    | 0.721 |      | V     | TA = +25°C,<br>CTMUCON<9:8> = 11 |  |

| CTMUFV2            | VFVR      | Temperature Diode Rate of                          | —                                                    | -1.92 |      | mV/ºC | CTMUCON<9:8> = 01                |  |

|                    |           | Change <sup>(1,2)</sup>                            | _                                                    | -1.74 |      | mV/ºC | CTMUCON<9:8> = 10                |  |

|                    |           |                                                    | _                                                    | -1.56 |      | mV/ºC | CTMUCON<9:8> = 11                |  |

**Note 1:** Nominal value at center point of current trim range (CTMUCON<15:10> = 000000).

**2:** Parameters are characterized but not tested in manufacturing. Measurements taken with the following conditions:

- VREF+ = AVDD = 3.3V

- ADC module configured for conversion speed of 500 ksps

- All PMD bits are cleared (PMDx = 0)

- Executing a while(1) statement

- Device operating from the FRC with no PLL

- **3:** The CTMU module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

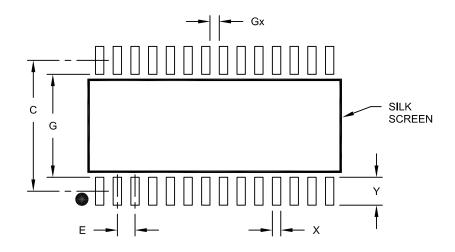

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |      |          |      |

|--------------------------|-------------|------|----------|------|

| Dimension Limits         |             | MIN  | NOM      | MAX  |

| Contact Pitch            | E           |      | 1.27 BSC |      |

| Contact Pad Spacing      | С           |      | 9.40     |      |

| Contact Pad Width (X28)  | X           |      |          | 0.60 |

| Contact Pad Length (X28) | Y           |      |          | 2.00 |

| Distance Between Pads    | Gx          | 0.67 |          |      |

| Distance Between Pads    | G           | 7.40 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

## APPENDIX A: REVISION HISTORY

## Revision A (May 2011)

This is the initial released version of this document.

## **Revision B (October 2011)**

The following two global changes are included in this revision:

- All packaging references to VLAP have been changed to VTLA throughout the document

- All references to VCORE have been removed

- All occurrences of the ASCL1, ASCL2, ASDA1, and ASDA2 pins have been removed

- V-temp temperature range (-40°C to +105°C) was added to all electrical specification tables

This revision includes the addition of the following devices:

- PIC32MX130F064B

- PIC32MX130F064C

- PIC32MX130F064D

- PIC32MX150F128B

- PIC32MX150F128CPIC32MX150F128D

- PIC32MX250F128C

PIC32MX250F128D

PIC32MX230F064B

PIC32MX230F064C

PIC32MX230F064D

PIC32MX250F128B

Text and formatting changes were incorporated throughout the document.

All other major changes are referenced by their respective section in Table A-1.

| Section                                                                    | Update Description                                                                                                                                                        |  |  |  |  |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| "32-bit Microcontrollers (up to 128 KB<br>Flash and 32 KB SRAM) with Audio | Split the existing Features table into two: PIC32MX1XX General Purpose Family Features (Table 1) and PIC32MX2XX USB Family Features (Table 2)                             |  |  |  |  |

| and Graphics Interfaces, USB, and Advanced Analog"                         | Added the SPDIP package reference (see Table 1, Table 2, and " <b>Pin Diagrams</b> ").                                                                                    |  |  |  |  |

|                                                                            | Added the new devices to the applicable pin diagrams.                                                                                                                     |  |  |  |  |

|                                                                            | Changed PGED2 to PGED1 on pin 35 of the 36-pin VTLA diagram for PIC32MX220F032C, PIC32MX220F016C, PIC32MX230F064C, and PIC32MX250F128C devices.                           |  |  |  |  |

| 1.0 "Device Overview"                                                      | Added the SPDIP package reference and updated the pin number for AN12 for 44-pin QFN devices in the Pinout I/O Descriptions (see Table 1-1).                              |  |  |  |  |

|                                                                            | Added the PGEC4/PGED4 pin pair and updated the C1INA-C1IND and C2INA-C2IND pin numbers for 28-pin SSOP/SPDIP/SOIC devices in the Pinout I/O Descriptions (see Table 1-1). |  |  |  |  |

| 2.0 "Guidelines for Getting Started with 32-bit Microcontrollers"          | Updated the Recommended Minimum Connection diagram (see Figure 2-1).                                                                                                      |  |  |  |  |

## TABLE A-1: MAJOR SECTION UPDATES