Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx110f016d-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 10: PIN NAMES FOR 44-PIN USB DEVICES

#### 44-PIN QFN (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

|       |                                                  |       | 44 1                                      |

|-------|--------------------------------------------------|-------|-------------------------------------------|

| Pin # | Full Pin Name                                    | Pin # | Full Pin Name                             |

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2     | RPC6/PMA1/RC6                                    | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3     | RPC7/PMA0/RC7                                    | 25    | AN6/RPC0/RC0                              |

| 4     | RPC8/PMA5/RC8                                    | 26    | AN7/RPC1/RC1                              |

| 5     | RPC9/CTED7/PMA6/RC9                              | 27    | AN8/RPC2/PMA2/RC2                         |

| 6     | Vss                                              | 28    | Vdd                                       |

| 7     | VCAP                                             | 29    | Vss                                       |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       | 30    | OSC1/CLKI/RPA2/RA2                        |

| 9     | PGEC2/RPB11/D-/RB11                              | 31    | OSC2/CLKO/RPA3/RA3                        |

| 10    | VUSB3V3                                          | 32    | TDO/RPA8/PMA8/RA8                         |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       | 33    | SOSCI/RPB4/RB4                            |

| 12    | PGED4/TMS/PMA10/RA10                             | 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 13    | PGEC4/TCK/CTED8/PMA7/RA7                         | 35    | TDI/RPA9/PMA9/RA9                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 | 36    | AN12/RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            | 37    | RPC4/PMA4/RC4                             |

| 16    | AVss                                             | 38    | RPC5/PMA3/RC5                             |

| 17    | AVDD                                             | 39    | Vss                                       |

| 18    | MCLR                                             | 40    | Vdd                                       |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 | 41    | RPB5/USBID/RB5                            |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       | 42    | VBUS                                      |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        | 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       | 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

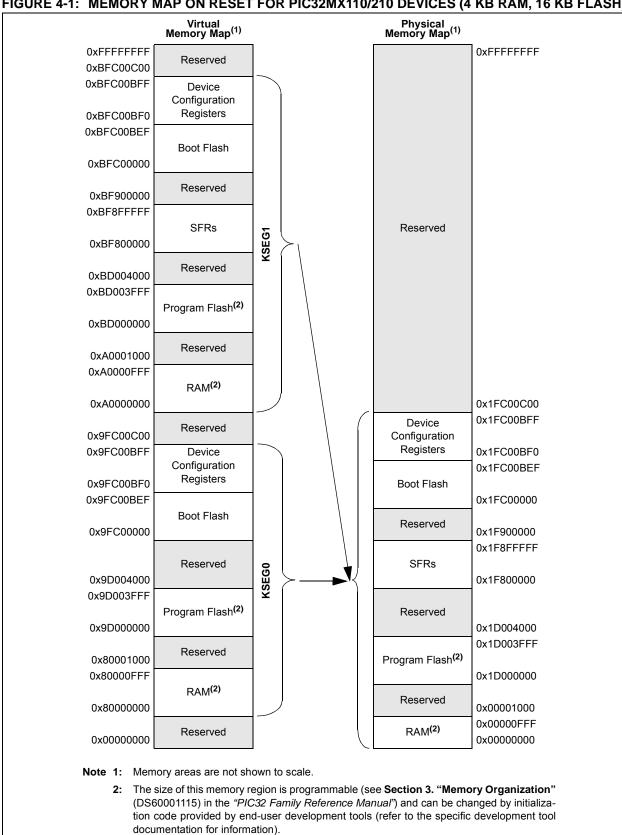

#### FIGURE 4-1: MEMORY MAP ON RESET FOR PIC32MX110/210 DEVICES (4 KB RAM, 16 KB FLASH)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 |                   | —                | —                |  |  |

|              | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |

| 23:16        | _                 | —                 | _                 | BMX<br>ERRIXI     | BMX<br>ERRICD     | BMX<br>ERRDMA     | BMX<br>ERRDS     | BMX<br>ERRIS     |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | —                 | —                 | —                 | -                 | —                 | _                 |                  | —                |  |  |

|              | U-0               | R/W-1             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |  |  |

| 7:0          | _                 | BMX<br>WSDRM      | _                 | _                 | _                 | E                 | BMXARB<2:0>      |                  |  |  |

### REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

#### Legend:

| 5                 |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

# bit 31-21 Unimplemented: Read as '0'

|          | Ommplemented. Read as 0                                                                                                                                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 20   | BMXERRIXI: Enable Bus Error from IXI bit                                                                                                                                                                                              |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> </ul>                 |

| bit 19   | BMXERRICD: Enable Bus Error from ICD Debug Unit bit                                                                                                                                                                                   |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from ICD</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from ICD</li> </ul>                                       |

| bit 18   | BMXERRDMA: Bus Error from DMA bit                                                                                                                                                                                                     |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from DMA</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from DMA</li> </ul>                                       |

| bit 17   | BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)                                                                                                                                                                 |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access</li> </ul>               |

| bit 16   | BMXERRIS: Bus Error from CPU Instruction Access bit (disabled in Debug mode)                                                                                                                                                          |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> </ul> |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 6    | BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit                                                                                                                                                                 |

|          | <ul> <li>1 = Data RAM accesses from CPU have one wait state for address setup</li> <li>0 = Data RAM accesses from CPU have zero wait states for address setup</li> </ul>                                                              |

| bit 5-3  | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 2-0  | BMXARB<2:0>: Bus Matrix Arbitration Mode bits                                                                                                                                                                                         |

|          | 111 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          | •                                                                                                                                                                                                                                     |

|          | •                                                                                                                                                                                                                                     |

|          | <ul><li>011 = Reserved (using these Configuration modes will produce undefined behavior)</li><li>010 = Arbitration Mode 2</li></ul>                                                                                                   |

|          | 001 = Arbitration Mode 1 (default)<br>000 = Arbitration Mode 0                                                                                                                                                                        |

|          |                                                                                                                                                                                                                                       |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | -                 | _                 | _                 | _                 | _                 |                   | _                | _                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | —                 | —                 | _                 | _                 | —                 | —                | —                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 15:8         |                   |                   |                   | BMXDK             | PBA<15:8>         |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          | BMXDKPBA<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 4-2: BMXDKPBA: DATA RAM KERNEL PROGRAM BASE ADDRESS REGISTER

# Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 **BMXDKPBA<15:10>:** DRM Kernel Program Base Address bits When non-zero, this value selects the relative base address for kernel program space in RAM

bit 9-0 BMXDKPBA<9:0>: Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

# 6.1 Reset Control Registers

# TABLE 6-1: RESET CONTROL REGISTER MAP

| ess                         |                                 | 0         | Bits  |       |       |       |       |       |      |       |      |      |      | s    |       |      |      |       |           |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|------|-------|------|------|-------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1 | 16/0  | All Reset |

| F600                        | RCON                            | 31:16     | _     | _     | _     |       | —     | _     |      | —     | _    | _    |      | _    |       | -    | -    | _     | 0000      |

| 1 000                       | ROOM                            | 15:0      | _     |       | -     |       | _     | -     | CMR  | VREGS | EXTR | SWR  |      | WDTO | SLEEP | IDLE | BOR  | POR   | xxxx(2)   |

| E610                        | RSWRST                          | 31:16     |       | —     | -     | —     | —     | —     | —    | —     |      | —    | —    | _    | —     | _    | —    | —     | 0000      |

| 1010                        | N31/K31                         | 15:0      | _     | _     | _     | -     | _     | _     |      | —     | _    | _    | -    | _    | _     | _    | -    | SWRST | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

### 7.1 Interrupt Control Registers

#### TABLE 7-2: INTERRUPT REGISTER MAP

| ess                         |                                 | â             |             |        |        |             |             |            |                        | Bits    |        |           |          |            |                      |                |            |        |               |      |

|-----------------------------|---------------------------------|---------------|-------------|--------|--------|-------------|-------------|------------|------------------------|---------|--------|-----------|----------|------------|----------------------|----------------|------------|--------|---------------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15       | 30/14  | 29/13  | 28/12       | 27/11       | 26/10      | 25/9                   | 24/8    | 23/7   | 22/6      | 21/5     | 20/4       | 19/3                 | 18/2           | 17/1       | 16/0   | All<br>Resets |      |

| 1000                        | INTCON                          | 31:16         | _           | _      | —      | _           |             |            | _                      | -       |        |           | _        | _          |                      | —              |            |        | 0000          |      |

| 1000                        | INTCOM                          | 15:0          | —           | _      | —      | MVEC        | -           |            | TPC<2:0>               |         | -      | —         | _        | INT4EP     | INT3EP               | INT2EP         | INT1EP     | INT0EP | 0000          |      |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         | —           |        | —      | _           | _           | _          | —                      | —       |        | _         | _        | _          |                      |                | —          | —      | 0000          |      |

| 1010                        | INTOTAL                         | 15:0          | —           | _      | —      | —           | _           |            | SRIPL<2:0>             |         | _      | _         |          |            | VEC<5:0              | )>             |            |        | 0000          |      |

| 1020                        | IPTMR                           | 31:16<br>15:0 | IPTMR<31:0> |        |        |             |             |            |                        |         |        |           |          | 0000       |                      |                |            |        |               |      |

| 4000                        | 1500                            | 31:16         | FCEIF       | RTCCIF | FSCMIF | AD1IF       | OC5IF       | IC5IF      | IC5EIF                 | T5IF    | INT4IF | OC4IF     | IC4IF    | IC4EIF     | T4IF                 | INT3IF         | OC3IF      | IC3IF  | 0000          |      |

| 1030                        | IFS0                            | 15:0          | IC3EIF      | T3IF   | INT2IF | OC2IF       | IC2IF       | IC2EIF     | T2IF                   | INT1IF  | OC1IF  | IC1IF     | IC1EIF   | T1IF       | INT0IF               | CS1IF          | CS0IF      | CTIF   | 0000          |      |

| 1010                        | 1504                            | 31:16         | DMA3IF      | DMA2IF | DMA1IF | DMA0IF      | CTMUIF      | I2C2MIF    | I2C2SIF                | I2C2BIF | U2TXIF | U2RXIF    | U2EIF    | SPI2TXIF   | SPI2RXIF             | SPI2EIF        | PMPEIF     | PMPIF  | 0000          |      |

| 1040                        | IFS1                            | 15:0          | CNCIF       | CNBIF  | CNAIF  | I2C1MIF     | I2C1SIF     | I2C1BIF    | U1TXIF                 | U1RXIF  | U1EIF  | SPI1TXIF  | SPI1RXIF | SPI1EIF    | USBIF <sup>(2)</sup> | CMP3IF         | CMP2IF     | CMP1IF | 0000          |      |

| 1060                        | IEC0                            | 31:16         | FCEIE       | RTCCIE | FSCMIE | AD1IE       | OC5IE       | IC5IE      | IC5EIE                 | T5IE    | INT4IE | OC4IE     | IC4IE    | IC4EIE     | T4IE                 | INT3IE         | OC3IE      | IC3IE  | 0000          |      |

| 1060                        | IECU                            | 15:0          | IC3EIE      | T3IE   | INT2IE | OC2IE       | IC2IE       | IC2EIE     | T2IE                   | INT1IE  | OC1IE  | IC1IE     | IC1EIE   | T1IE       | INT0IE               | CS1IE          | CS0IE      | CTIE   | 0000          |      |

| 1070                        | IEC1                            | 31:16         | DMA3IE      | DMA2IE | DMA1IE | DMA0IE      | CTMUIE      | I2C2MIE    | I2C2SIE                | I2C2BIE | U2TXIE | U2RXIE    | U2EIE    | SPI2TXIE   | SPI2RXIE             | SPI2EIE        | PMPEIE     | PMPIE  | 0000          |      |

| 1070                        | ILUT                            | 15:0          | CNCIE       | CNBIE  | CNAIE  | I2C1MIE     | I2C1SIE     | I2C1BIE    | U1TXIE                 | U1RXIE  | U1EIE  | SPI1TXIE  | SPI1RXIE | SPI1EIE    | USBIE <sup>(2)</sup> | CMP3IE         | CMP2IE     | CMP1IE | 0000          |      |

| 1090                        | IPC0                            | 31:16         | —           | _      | —      |             | INT0IP<2:0> |            | INT0IS<1:0>            |         | -      | —         | _        | CS1IP<2:0> |                      |                | CS1IS<1:0> |        | 0000          |      |

| 1030                        | 11 00                           | 15:0          | —           | —      | —      |             | CS0IP<2:0>  |            | CS0IS<1:0>             |         | _      | —         | —        | CTIP<2:0>  |                      | CTIP<2:0> CTIS |            | <1:0>  | 0000          |      |

| 10A0                        | IPC1                            | 31:16         | —           |        | —      |             | INT1IP<2:0> |            | INT1IS                 | <1:0>   | _      | —         | _        | OC1IP<2:0> |                      |                | OC1IS      | S<1:0> | 0000          |      |

| 10,10                       |                                 | 15:0          | —           | —      | —      |             | IC1IP<2:0>  |            | IC1IS•                 | <1:0>   | —      | —         | —        | T1IP<2:0>  |                      |                | T1IS       | <1:0>  | 0000          |      |

| 10B0                        | IPC2                            | 31:16         | _           | —      | —      |             | INT2IP<2:0> |            | INT2IS                 | <1:0>   | _      | —         | _        | OC2IP<2:0> |                      |                | OC2IS      | 6<1:0> | 0000          |      |

| 1000                        | 11 02                           | 15:0          | —           |        | —      |             | IC2IP<2:0>  |            | IC2IS<                 | <1:0>   | _      | —         | _        | 1          | [21P<2:0>            |                | T2IS       | <1:0>  | 0000          |      |

| 10C0                        | IPC3                            | 31:16         | —           | —      | —      |             | INT3IP<2:0> |            | INT3IS                 | <1:0>   | —      |           | —        | 0          | C3IP<2:0>            |                | OC3IS      | 6<1:0> | 0000          |      |

| 1000                        | 1 00                            | 15:0          | —           | —      | —      |             | IC3IP<2:0>  |            | IC3IS<                 | <1:0>   | —      |           | —        |            | [3IP<2:0>            |                | T3IS-      |        | 0000          |      |

| 10D0                        | IPC4                            | 31:16         | —           |        | —      | INT4IP<2:0> |             | INT4IS     | <1:0>                  | _       | —      | _         | 0        | C4IP<2:0>  |                      | OC4IS          | S<1:0>     | 0000   |               |      |

| 1020                        |                                 | 15:0          | —           | —      | —      | IC4IP<2:0>  |             | IC4IS<     | <1:0>                  |         | —      | _         | 1        | [4IP<2:0>  |                      | T4IS           | <1:0>      | 0000   |               |      |

| 10E0                        | IPC5                            | 31:16         | —           | —      | —      | AD1IP<2:0>  |             | AD1IP<2:0> |                        | <1:0>   | _      | —         | _        | OC5IP<2:0> |                      | OC5IS          | S<1:0>     | 0000   |               |      |

| 1020                        |                                 | 15:0          | —           | _      | —      | IC5IP<2:0>  |             |            | G<1:0> — — — T5IP<2:0> |         |        | T5IS<1:0> |          | 0000       |                      |                |            |        |               |      |

| 10F0                        | IPC6                            | 31:16         | —           | —      | —      | CMP1IP<2:0> |             | -          |                        | S<1:0>  |        | _         | —        | FCEIP<2:0> |                      | FCEIP<2:0>     |            | FCEIS  | 6<1:0>        | 0000 |

| 101 0                       | " 00                            | 15:0          | —           | —      | —      | F           | RTCCIP<2:0> |            |                        | 6<1:0>  | —      | —         | _        | FS         | CMIP<2:0>            | >              | FSCMI      | S<1:0> | 0000          |      |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX1XX devices.

3: This register does not have associated CLR, SET, INV registers.

# TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP (CONTINUED)

| ess                         |                                 | ē                 |           |       |       |       | -      |       |      | Bi     | ts      |        |        |        |              |        |        |        | s          |

|-----------------------------|---------------------------------|-------------------|-----------|-------|-------|-------|--------|-------|------|--------|---------|--------|--------|--------|--------------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range         | 31/15     | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3         | 18/2   | 17/1   | 16/0   | All Resets |

| 3280                        | DCH2CPTR                        | 31:16             | —         | _     | _     | _     |        | _     |      | —      |         | _      | _      |        |              | _      | _      |        | 0000       |

| 5200                        | DONZOFIK                        | 15:0 CHCPTR<15:0> |           |       |       |       |        |       |      |        | 0000    |        |        |        |              |        |        |        |            |

| 3290                        | DCH2DAT                         | 31:16             | _         | _     | —     | —     |        | _     |      | _      | _       | _      | —      | _      | —            | _      | _      |        | 0000       |

| 3290                        | DCHZDAI                         | 15:0              | _         |       | _     | _     |        | -     |      | -      |         |        |        | CHPDA  | AT<7:0>      |        |        |        | 0000       |

| 2240                        | DCH3CON                         | 31:16             | _         | _     | _     | _     | _      | _     | _    | _      | _       | _      | _      | _      | _            | _      | _      | _      | 0000       |

| 32A0                        | DCH3CON                         | 15:0              | CHBUSY    | _     | _     | _     |        |       |      | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  | —            | CHEDET | CHPR   | l<1:0> | 0000       |

| 3280                        | DCH3ECON                        | 31:16             |           |       |       |       |        |       |      |        |         |        |        | OOFF   |              |        |        |        |            |

| 5200                        |                                 | 15:0              |           |       |       | CHSIR | Q<7:0> |       |      |        | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN       | _      | _      | _      | FF00       |

| 32C0                        | DCH3INT                         | 31:16             | —         | —     | —     | —     | -      | _     | -    | —      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE       | CHCCIE | CHTAIE | CHERIE | 0000       |

| 0200                        |                                 | 15:0              | —         |       |       | _     | —      | _     | _    | —      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF       | CHCCIF | CHTAIF | CHERIF | 0000       |

| 32D0                        | DCH3SSA                         | 31:16<br>15:0     | (HSSA<31) |       |       |       |        |       |      |        |         |        |        | 0000   |              |        |        |        |            |

|                             |                                 | 31:16             |           | 000   |       |       |        |       |      |        |         |        |        | 0000   |              |        |        |        |            |

| 32E0                        | DCH3DSA                         | 15:0              |           |       |       |       |        |       |      | CHDSA  | <31:0>  |        |        |        |              |        |        |        | 0000       |

| 0050                        | 00100017                        | 31:16             |           | _     |       |       | _      | _     | _    |        |         |        |        |        |              | _      |        | _      | 0000       |

| 32FU                        | DCH3SSIZ                        | 15:0              |           |       |       |       |        |       |      | CHSSIZ | 2<15:0> |        |        |        |              |        |        |        | 0000       |

| 2200                        | DCH3DSIZ                        | 31:16             | —         | —     | —     | —     | _      | —     | _    | —      | _       | —      | —      | —      | —            | _      | —      | _      | 0000       |

| 3300                        | DCH3D3IZ                        | 15:0              |           |       |       |       |        |       |      | CHDSIZ | 2<15:0> |        |        |        |              |        |        |        | 0000       |

| 3310                        | DCH3SPTR                        | 31:16             | —         | _     | _     | _     |        |       |      | _      | —       |        | _      |        | _            |        |        |        | 0000       |

| 3310                        | DOI IJOF I K                    | 15:0              |           |       |       |       |        |       |      | CHSPTF | ۲<15:0> |        |        |        |              |        |        |        | 0000       |

| 3320                        | DCH3DPTR                        | 31:16             | —         | —     | —     | —     | _      | _     | _    | —      | _       | _      | —      | —      | —            | _      | —      | _      | 0000       |

| 0020                        |                                 | 15:0              |           |       |       |       |        |       |      |        | 0000    |        |        |        |              |        |        |        |            |

| 3330                        | <b>DCH3CSIZ</b>                 | 31:16             | —         | _     | —     | —     | —      | —     | —    | —      | —       | —      | —      | —      | —            | —      | —      | —      | 0000       |

|                             |                                 | 15:0              |           |       |       |       |        |       |      | CHCSIZ | 2<15:0> |        |        |        |              |        |        |        | 0000       |

| 3340                        | DCH3CPTR                        | 31:16             | _         | —     | —     | —     | _      | —     | _    | —      | _       | —      | —      | —      | —            | —      | —      | _      | 0000       |

|                             |                                 | 15:0              |           |       |       |       |        |       |      | CHCPT  | ≺<15:0> |        |        |        |              |        |        |        | 0000       |

| 3350                        | DCH3DAT                         | 31:16             | —         | _     | —     | _     | _      | _     | —    | _      | _       | —      | —      | -      | —<br>T :7 0: | —      | —      | —      | 0000       |

| <u> </u>                    |                                 | 15:0              | —         | —     | —     | —     | —      | —     | —    | _      |         |        |        | CHPDA  | AT<7:0>      |        |        |        | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |  |  |

| 31:24        | _                 | —                 | _                 | -                 | _                 | _                 | _                | —                |  |  |  |  |  |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |  |  |

| 23.10        | —                 | —                 | _                 | -                 | _                 | _                 | -                | —                |  |  |  |  |  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |  |  |

| 15:8         |                   | —                 |                   | _                 | _                 |                   | _                | —                |  |  |  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | CHPDAT            | [<7:0>            |                   | CHPDAT<7:0>      |                  |  |  |  |  |  |  |  |  |  |

### REGISTER 9-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

### Legend:

| =0901141          |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 CHPDAT<7:0>: Channel Data Register bits

Pattern Terminate mode: Data to be matched must be stored in this register to allow a "terminate on match".

All other modes: Unused.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

|              |                   | _                 |                   |                   |                   |                   | FRMH<2:0>        |                  |

#### REGISTER 10-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

#### Legend:

| 0                 |                           |                      |                    |

|-------------------|---------------------------|----------------------|--------------------|

| R = Readable bit  | able bit W = Writable bit |                      | ead as '0'         |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared | x = Bit is unknown |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** The Upper 3 bits of the Frame Numbers bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### Bit Bit Bit Bit Bit Bit Bit Bit Bit 30/22/14/6 27/19/11/3 26/18/10/2 25/17/9/1 24/16/8/0 Range 31/23/15/7 29/21/13/5 28/20/12/4 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 31:24 \_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 23:16 \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 15:8 \_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 7:0 PID < 3:0 > (1)EP<3:0>

#### **REGISTER 10-15: U1TOK: USB TOKEN REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-4 **PID<3:0>:** Token Type Indicator bits<sup>(1)</sup>

1101 = SETUP (TX) token type transaction

- 1001 = IN (RX) token type transaction

- 0001 = OUT (TX) token type transaction

Note: All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

Note 1: All other values are reserved and must not be used.

# 11.1 Parallel I/O (PIO) Ports

All port pins have 10 registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

#### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx, and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Pin Diagrams"** section for the available pins and their functionality.

# 11.1.2 CONFIGURING ANALOG AND DIGITAL PORT PINS

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSEL and TRIS bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

If the TRIS bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 11.1.3 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP.

# 11.1.4 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports allows the PIC32MX1XX/2XX 28/36/44-pin Family devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a change-of-state.

Five control registers are associated with the CN functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

**Note:** Pull-ups and pull-downs on change notification pins should always be disabled when the port pin is configured as a digital output.

An additional control register (CNCONx) is shown in Register 11-3.

# 11.2 CLR, SET and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR, or INV register, the base register must be read.

### TABLE 11-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection       |

|--------------|----------|-------------|---------------------------------------------|

| RPA0         | RPA0R    | RPA0R<3:0>  | 0000 = No Connect                           |

| RPB3         | RPB3R    | RPB3R<3:0>  | 0001 = <u>U1TX</u><br>0010 = <u>U2RTS</u>   |

| RPB4         | RPB4R    | RPB4R<3:0>  | 0011 = SS1                                  |

| RPB15        | RPB15R   | RPB15R<3:0> |                                             |

| RPB7         | RPB7R    | RPB7R<3:0>  | 0110 = Reserved<br>0111 = C2OUT             |

| RPC7         | RPC7R    | RPC7R<3:0>  | 1000 = Reserved                             |

| RPC0         | RPC0R    | RPC0R<3:0>  | •                                           |

| RPC5         | RPC5R    | RPC5R<3:0>  | •<br>1111 = Reserved                        |

| RPA1         | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                           |

| RPB5         | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPB1         | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                 |

| RPB11        | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                   |

| RPB8         | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                             |

| RPA8         | RPA8R    | RPA8R<3:0>  |                                             |

| RPC8         | RPC8R    | RPC8R<3:0>  | •                                           |

| RPA9         | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                             |

| RPA2         | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                           |

| RPB6         | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPA4         | RPA4R    | RPA4R<3:0>  | 0011 = SDO1<br>0100 = SDO2                  |

| RPB13        | RPB13R   | RPB13R<3:0> | 0101 <b>= OC4</b>                           |

| RPB2         | RPB2R    | RPB2R<3:0>  |                                             |

| RPC6         | RPC6R    | RPC6R<3:0>  | 1000 = Reserved                             |

| RPC1         | RPC1R    | RPC1R<3:0>  |                                             |

| RPC3         | RPC3R    | RPC3R<3:0>  | 1111 = Reserved                             |

| RPA3         | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                           |

| RPB14        | RPB14R   | RPB14R<3:0> |                                             |

| RPB0         | RPB0R    | RPB0R<3:0>  | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |

| RPB10        | RPB10R   | RPB10R<3:0> | 0101 <b>= OC3</b>                           |

| RPB9         | RPB9R    | RPB9R<3:0>  |                                             |

| RPC9         | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                             |

| RPC2         | RPC2R    | RPC2R<3:0>  |                                             |

| RPC4         | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                             |

NOTES:

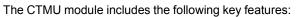

# 25.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that has a configurable current source with a digital configuration circuit built around it. The CTMU can be used for differential time measurement between pulse sources and can be used for generating an asynchronous pulse. By working with other on-chip analog modules, the CTMU can be used for high resolution time measurement, measure capacitance, measure relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

- Up to 13 channels available for capacitive or time measurement input

- · On-chip precision current source

- 16-edge input trigger sources

- · Selection of edge or level-sensitive inputs

- · Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · High precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- · Integrated temperature sensing diode

- · Control of current source during auto-sampling

- · Four current source ranges

- · Time measurement resolution of one nanosecond

A block diagram of the CTMU is shown in Figure 25-1.

© 2011-2016 Microchip Technology Inc.

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |

|--------------|-----------------------------|-------------------|---------------------|-------------------|-------------------|-------------------|-----------------------|------------------|--|

| 04.04        | R                           | R                 | R                   | R                 | R                 | R                 | R                     | R                |  |

| 31:24        |                             | VER<              | 3:0> <sup>(1)</sup> |                   |                   | DEVID<            | 27:24> <sup>(1)</sup> |                  |  |

| 00.40        | R                           | R                 | R                   | R                 | R                 | R                 | R                     | R                |  |

| 23:16        | DEVID<23:16> <sup>(1)</sup> |                   |                     |                   |                   |                   |                       |                  |  |

| 45.0         | R                           | R                 | R                   | R                 | R                 | R                 | R                     | R                |  |

| 15:8         | DEVID<15:8> <sup>(1)</sup>  |                   |                     |                   |                   |                   |                       |                  |  |

| 7:0          | R                           | R                 | R                   | R                 | R                 | R                 | R                     | R                |  |

|              |                             |                   |                     | DEVID-            | <7:0>(1)          |                   |                       |                  |  |

#### REGISTER 27-6: DEVID: DEVICE AND REVISION ID REGISTER

#### Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID bits<sup>(1)</sup>

**Note 1:** See the "*PIC32 Flash Programming Specification*" (DS60001145) for a list of Revision and Device ID values.

| DC CHA        | RACTERIS               | TICS         | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                                                     |                                        |  |  |  |

|---------------|------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------|--|--|--|

| Param.<br>No. | Typical <sup>(2)</sup> | Max.         | Units                                                                                                                                                                                                                                                                      | Conditions                                          |                                        |  |  |  |

| Power-D       | own Curre              | nt (IPD) (No | otes 1, 5)                                                                                                                                                                                                                                                                 |                                                     |                                        |  |  |  |

| DC40k         | 44                     | 70           | μA                                                                                                                                                                                                                                                                         | -40°C                                               |                                        |  |  |  |

| DC40I         | 44                     | 70           | μA                                                                                                                                                                                                                                                                         | +25°C                                               | Base Power-Down Current                |  |  |  |

| DC40n         | 168                    | 259          | μA                                                                                                                                                                                                                                                                         | +85°C                                               |                                        |  |  |  |

| DC40m         | 335                    | 536          | μA                                                                                                                                                                                                                                                                         | +105°C                                              |                                        |  |  |  |

| Module        | Differential           | Current      |                                                                                                                                                                                                                                                                            |                                                     |                                        |  |  |  |

| DC41e         | 5                      | 20           | μA                                                                                                                                                                                                                                                                         | 3.6V                                                | Watchdog Timer Current: AIWDT (Note 3) |  |  |  |

| DC42e         | 23                     | 50           | μA                                                                                                                                                                                                                                                                         | 3.6V RTCC + Timer1 w/32 kHz Crystal: △IRTCC (Note 3 |                                        |  |  |  |

| DC43d         | 1000                   | 1100         | μA                                                                                                                                                                                                                                                                         | 3.6V ADC: △IADC (Notes 3,4)                         |                                        |  |  |  |

### TABLE 30-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** The test conditions for IPD current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

OSC2/CLKO is configured as an I/O input pin

• USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

• CPU is in Sleep mode, and SRAM data memory Wait states = 1

• No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

• WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

• All I/O pins are configured as inputs and pulled to Vss

• MCLR = VDD

• RTCC and JTAG are disabled

2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

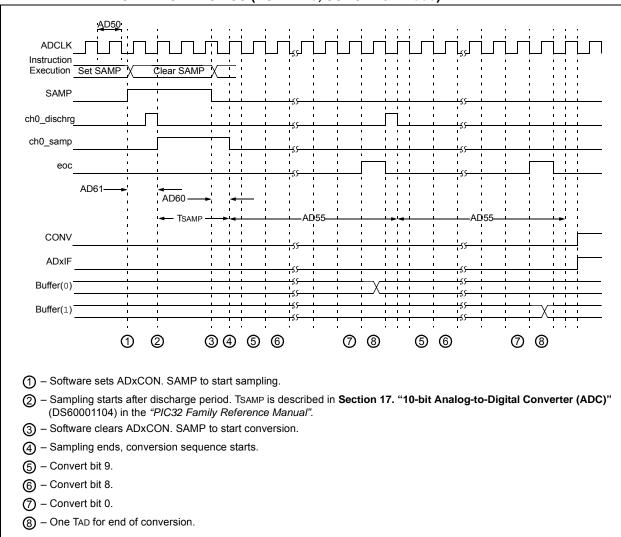

#### FIGURE 30-18: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

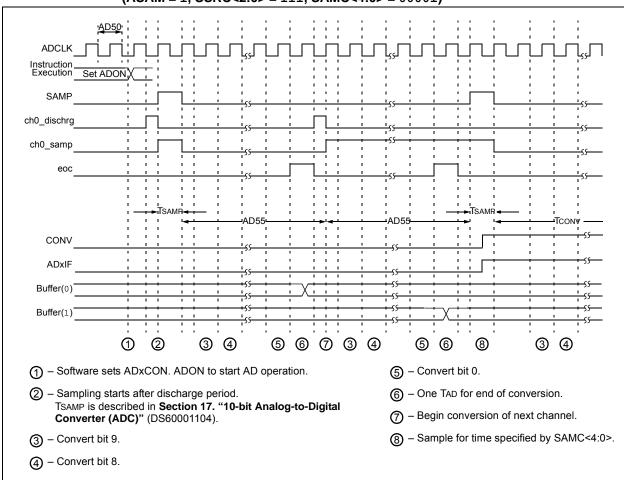

#### FIGURE 30-19: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

#### TABLE 31-5: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                                    | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |         |          |       |                               |

|--------------------|--------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|-------|-------------------------------|

| Param.<br>No.      | Symbol | Characteristics                                                                    | Min.                                                                                                                                                | Typical | Max.     | Units | Conditions                    |

| MOS10              |        | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC<br>4                                                                                                                                             |         | 50<br>50 |       | EC (Note 2)<br>ECPLL (Note 1) |

Note 1: PLL input requirements: 4 MHz  $\leq$  FPLLIN  $\leq$  5 MHz (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

**2:** This parameter is characterized, but not tested in manufacturing.

### TABLE 31-6:SPIX MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \end{array}$ |         |      |       |            |

|--------------------|--------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|

| Param.<br>No.      | Symbol | Characteristics                    | Min.                                                                                                                                                                                                                  | Typical | Max. | Units | Conditions |

| MSP10              | TscL   | SCKx Output Low Time<br>(Note 1,2) | Тѕск/2                                                                                                                                                                                                                |         | —    | ns    | _          |

| MSP11              | TscH   | SCKx Output High Time (Note 1,2)   | Тѕск/2                                                                                                                                                                                                                | _       | _    | ns    | _          |

Note 1: These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

#### TABLE 31-7: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                     | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |      |       |            |

|--------------------|--------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup>      | Min.                                                                                                                                            | Тур. | Max. | Units | Conditions |

| MSP10              | TscL   | SCKx Output Low Time<br>(Note 1,2)  | Тѕск/2                                                                                                                                          | _    |      | ns    | _          |

| MSP11              | TSCH   | SCKx Output High Time<br>(Note 1,2) | Тѕск/2                                                                                                                                          | _    | _    | ns    | —          |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

**2:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Program Memory Size<br>Pin Count<br>Software Targeting<br>Tape and Reel Flag (if<br>Speed (if applicable)<br>Temperature Range<br>Package | 32-bit RISC MCU with M4K <sup>®</sup> core,<br>32 KB program memory, 44-pin,                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                           | Flash Memory Family                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Architecture                                                                                                                              | $MX = M4K^{\odot} MCU \text{ core}$                                                                                                                                                                                                                                                                                                                                                                                                    |

| Product Groups                                                                                                                            | 1XX = General purpose microcontroller family<br>2XX = General purpose microcontroller family                                                                                                                                                                                                                                                                                                                                           |

| Flash Memory Family                                                                                                                       | F = Flash program memory                                                                                                                                                                                                                                                                                                                                                                                                               |

| Program Memory Size                                                                                                                       | 016 = 16K<br>032 = 32K<br>064 = 64K<br>128 = 128K<br>256 = 256K                                                                                                                                                                                                                                                                                                                                                                        |

| Pin Count                                                                                                                                 | B = 28-pin<br>C = 36-pin<br>D = 44-pin                                                                                                                                                                                                                                                                                                                                                                                                 |

| Software Targeting                                                                                                                        | B = Targeted for Bluetooth <sup>®</sup> Audio Break-in devices                                                                                                                                                                                                                                                                                                                                                                         |

| Speed                                                                                                                                     | <ul> <li>= 40 MHz - () indicates a blank field; package markings for 40 MHz devices do not include the Speed</li> <li>= 50 MHz</li> </ul>                                                                                                                                                                                                                                                                                              |

| Temperature Range                                                                                                                         | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>V = $-40^{\circ}$ C to $+105^{\circ}$ C (V-temp)                                                                                                                                                                                                                                                                                                                                |

| Package                                                                                                                                   | ML= 28-Lead (6x6 mm) QFN (Plastic Quad Flatpack)ML= 44-Lead (8x8 mm) QFN (Plastic Quad Flatpack)PT= 44-Lead (10x10x1 mm) TQFP (Plastic Thin Quad Flatpack)SO= 28-Lead (7.50 mm) SOIC (Plastic Small Outline)SP= 28-Lead (300 mil) SPDIP (Skinny Plastic Dual In-line)SS= 28-Lead (5.30 mm) SSOP (Plastic Shrink Small Outline)TL= 36-Lead (5x5 mm) VTLA (Very Thin Leadless Array)TL= 44-Lead (6x6 mm) VTLA (Very Thin Leadless Array) |

| Pattern                                                                                                                                   | Three-digit QTP, SQTP, Code or Special Requirements (blank otherwise)<br>ES = Engineering Sample                                                                                                                                                                                                                                                                                                                                       |