Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                  |                                                                                |

|-------------------------|--------------------------------------------------------------------------------|

| roduct Status           | Obsolete                                                                       |

| ore Processor           | MIPS32® M4K™                                                                   |

| ore Size                | 32-Bit Single-Core                                                             |

| peed                    | 40MHz                                                                          |

| onnectivity             | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| eripherals              | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                |

| umber of I/O            | 35                                                                             |

| ogram Memory Size       | 16KB (16K x 8)                                                                 |

| ogram Memory Type       | FLASH                                                                          |

| PROM Size               | -                                                                              |

| M Size                  | 4K x 8                                                                         |

| tage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| ta Converters           | A/D 13x10b                                                                     |

| scillator Type          | Internal                                                                       |

| erating Temperature     | -40°C ~ 105°C (TA)                                                             |

| unting Type             | Surface Mount                                                                  |

| ckage / Case            | 44-VFTLA Exposed Pad                                                           |

| pplier Device Package   | 44-VTLA (6x6)                                                                  |

| rchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx110f016d-v-tl |

#### TABLE 7: PIN NAMES FOR 36-PIN GENERAL PURPOSE DEVICES

**36-PIN VTLA (TOP VIEW)**(1,2,3,5)

PIC32MX110F016C PIC32MX120F032C PIC32MX130F064C PIC32MX150F128C

36

1

|       | T                                    |

|-------|--------------------------------------|

| Pin # | Full Pin Name                        |

| 1     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 |

| 2     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   |

| 3     | PGED4 <sup>(4)</sup> /AN6/RPC0/RC0   |

| 4     | PGEC4 <sup>(4)</sup> /AN7/RPC1/RC1   |

| 5     | VDD                                  |

| 6     | Vss                                  |

| 7     | OSC1/CLKI/RPA2/RA2                   |

| 8     | OSC2/CLKO/RPA3/PMA0/RA3              |

| 9     | SOSCI/RPB4/RB4                       |

| 10    | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4       |

| 11    | RPC3/RC3                             |

| 12    | Vss                                  |

| 13    | VDD                                  |

| 14    | VDD                                  |

| 15    | PGED3/RPB5/PMD7/RB5                  |

| 16    | PGEC3/RPB6/PMD6/RB6                  |

| 17    | TDI/RPB7/CTED3/PMD5/INT0/RB7         |

| 18    | TCK/RPB8/SCL1/CTED10/PMD4/RB8        |

| Pin# | Full Pin Name                                  |

|------|------------------------------------------------|

| 19   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 20   | RPC9/CTED7/RC9                                 |

| 21   | Vss                                            |

| 22   | VCAP                                           |

| 23   | VDD                                            |

| 24   | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 25   | PGEC2/TMS/RPB11/PMD1/RB11                      |

| 26   | AN12/PMD0/RB12                                 |

| 27   | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 28   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 29   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 30   | AVss                                           |

| 31   | AVDD                                           |

| 32   | MCLR                                           |

| 33   | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 34   | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

| 35   | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           |

| 36   | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: This pin function is not available on PIC32MX110F016C and PIC32MX120F032C devices.

- 5: Shaded pins are 5V tolerant.

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000D).

#### **Frrata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

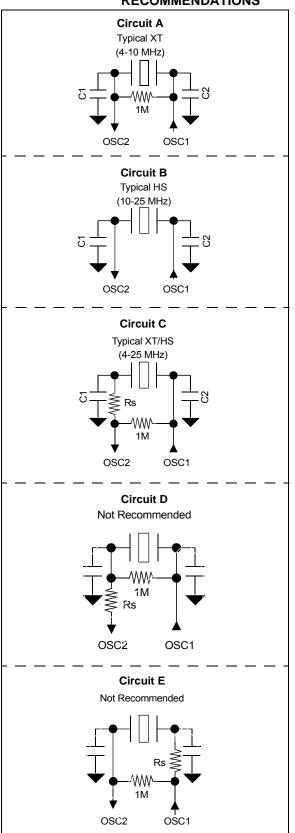

## 2.8.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32 OSC2 Pin Capacitance = ~4-5 pF

- COUT = PIC32 OSC1 Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

## EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

```

Crystal manufacturer recommended: CI = C2 = 15 pF

Therefore:

CLOAD = \{([CIN + CI]^*[COUT + C2]) / [CIN + CI + C2 + COUT]\} + estimated oscillator PCB stray capacitance

= \{([5 + 15][5 + 15]) / [5 + 15 + 15 + 5]\} + 2.5 pF

= \{([20][20]) / [40]\} + 2.5

= 10 + 2.5 = 12.5 pF

Rounded to the nearest standard value or 12 pF in this example for Primary Oscillator crystals "C1" and "C2".

```

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator.

The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to ~VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with ≤ 1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

### 2.8.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro® Devices"

- AN849 "Basic PICmicro® Oscillator Design"

# FIGURE 2-4: PRIMARY CRYSTAL OSCILLATOR CIRCUIT RECOMMENDATIONS

NOTES:

### 5.1 Flash Controller Control Registers

### TABLE 5-1: FLASH CONTROLLER REGISTER MAP

|                             | TEXAL CONTROLLER REGIONER MAN    |           |       |                    |       |        |         |       |      |            |          |      |      |      |      |      |        |      |            |

|-----------------------------|----------------------------------|-----------|-------|--------------------|-------|--------|---------|-------|------|------------|----------|------|------|------|------|------|--------|------|------------|

| ess                         |                                  | 3         |       |                    |       |        |         |       |      | Bit        | s        |      |      |      |      |      |        |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name                 | Bit Range | 31/15 | 30/14              | 29/13 | 28/12  | 27/11   | 26/10 | 25/9 | 24/8       | 23/7     | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| F400                        | NVMCON <sup>(1)</sup>            | 31:16     | _     | _                  | _     | _      | _       | _     | _    | _          | _        | _    | _    | _    | _    | _    | _      | _    | 0000       |

| F400                        | INVIVICOIN                       | 15:0      | WR    | WREN               | WRERR | LVDERR | LVDSTAT | _     | _    | _          | _        | _    | _    | _    |      | NVMO | P<3:0> |      | 0000       |

| F410                        | NVMKEY                           | 31:16     |       | NVMKEY<31:0>       |       |        |         |       |      |            |          |      |      |      |      | 0000 |        |      |            |

| 1 4 10                      | IN VIVINE I                      | 15:0      |       | INVINICE 1 < 31:U> |       |        |         |       |      |            |          |      |      |      |      | 0000 |        |      |            |

| F420                        | NVMADDR <sup>(1)</sup>           | 31:16     |       |                    |       |        |         |       |      | NVMADD     | 2<31.0>  |      |      |      |      |      |        |      | 0000       |

| 1 720                       | INVIVIADDIC: .                   | 15:0      |       |                    |       |        |         |       |      | INVIVIADO  | ( 1.0    |      |      |      |      |      |        |      | 0000       |

| F430                        | F430 NVMDATA 31:16 NVMDATA<31:0> |           |       |                    |       |        |         |       |      | 0000       |          |      |      |      |      |      |        |      |            |

| 1 +30                       | NVIVIDAIA                        | 15:0      |       |                    |       |        |         |       |      | INVIVIDAL  | 1.07     |      |      |      |      |      |        |      | 0000       |

| E440                        | NVMSRCADDR                       | 31:16     |       |                    |       |        |         |       | N    | VMSDCAL    | DR<31:0> |      |      |      |      |      |        |      | 0000       |

| 1 +40                       | INVINIONCADDIN                   | 15:0      |       |                    |       |        |         |       | i N  | VIVIOINOAL | אטוי.טר  |      |      |      |      |      |        |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### **REGISTER 5-1:** NVMCON: PROGRAMMING CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|----------------------|-------------------|------------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0                  | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |

| 31.24        | _                 | _                 | _                    | _                 | _                      |                   | _                | _                |  |  |

| 23:16        | U-0               | U-0               | U-0                  | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |

| 23.10        | _                 | _                 | _                    | _                 | _                      |                   | _                | _                |  |  |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0               | R-0                    | U-0               | U-0              | U-0              |  |  |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR(1)         | LVDSTAT <sup>(1)</sup> | _                 | _                | _                |  |  |

| 7.0          | U-0               | U-0               | U-0                  | U-0               | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | _                 | _                 | _                    | _                 | NVMOP<3:0>             |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 WR: Write Control bit

This bit is writable when WREN = 1 and the unlock sequence is followed.

1 = Initiate a Flash operation. Hardware clears this bit when the operation completes

0 = Flash operation is complete or inactive

bit 14 WREN: Write Enable bit

This is the only bit in this register reset by a device Reset.

1 = Enable writes to WR bit and enables LVD circuit

0 = Disable writes to WR bit and disables LVD circuit

bit 13 WRERR: Write Error bit<sup>(1)</sup>

This bit is read-only and is automatically set by hardware.

1 = Program or erase sequence did not complete successfully

0 = Program or erase sequence completed normally

LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled)<sup>(1)</sup> bit 12

This bit is read-only and is automatically set by hardware.

1 = Low-voltage detected (possible data corruption, if WRERR is set)

0 = Voltage level is acceptable for programming

bit 11 **LVDSTAT:** Low-Voltage Detect Status bit (LVD circuit must be enabled)<sup>(1)</sup>

This bit is read-only and is automatically set and cleared by the hardware.

1 = Low-voltage event is active

0 = Low-voltage event is not active

bit 10-4 Unimplemented: Read as '0'

bit 3-0 NVMOP<3:0>: NVM Operation bits

These bits are writable when WREN = 0.

1111 = Reserved

0111 = Reserved

0110 = No operation

0101 = Program Flash Memory (PFM) erase operation: erases PFM, if all pages are not write-protected

0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected

0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected

0010 = No operation

0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected

0000 = No operation

Note 1: This bit is cleared by setting NVMOP == `b0000, and initiating a Flash operation (i.e., WR).

| PIC32MX1XX | PIC32MX1XX/2XX 28/36/44-PIN FAMILY |  |  |  |  |  |  |  |  |

|------------|------------------------------------|--|--|--|--|--|--|--|--|

| NOTES:     |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

|            |                                    |  |  |  |  |  |  |  |  |

### 9.1 DMA Control Registers

### TABLE 9-1: DMA GLOBAL REGISTER MAP

| ess                         | -          | Bit Range                                      |               |       |       |         |         |       |      | Bi     | ts      |      |      |      |      |      |      |      | ω,         |

|-----------------------------|------------|------------------------------------------------|---------------|-------|-------|---------|---------|-------|------|--------|---------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF88_#) |            |                                                | 31/15         | 30/14 | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8   | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 2000                        | DMACON     | 31:16                                          | _             | _     | _     | _       | _       | _     | _    | _      | _       | _    | _    | _    | _    | _    | _    | _    | 0000       |

| 3000                        | DIVIACON   | 15:0                                           | ON            | -     | _     | SUSPEND | DMABUSY |       | _    | _      | _       | _    | _    | -    | -    | _    | _    | _    | 0000       |

| 3010                        | DMASTAT    | 31:16                                          | _             |       | _     | _       | _       | _     | I    | I      | I       | _    | _    |      |      | I    | _    |      | 0000       |

| 3010                        | DIVIASTAT  | AT 15:0 — — — — — — — — — — RDWR DMACH<2:0>(2) |               |       |       |         |         |       |      |        |         | (2)  | 0000 |      |      |      |      |      |            |

| 3020                        | DMAADDR    | 31:16                                          |               |       |       |         |         |       |      | DMAADD | D<31·0> |      |      |      |      |      |      |      | 0000       |

| 3020                        | DIVIDADDIX | 15:0                                           | DMAADDR<31:0> |       |       |         |         |       |      |        |         |      |      | 0000 |      |      |      |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information

### TABLE 9-2: DMA CRC REGISTER MAP

| ess                         |                                 | e ·       |       |       |       |                                     |       |       |      | Ві     | ts       |      |          |      |      |      |      |      |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------------------------------------|-------|-------|------|--------|----------|------|----------|------|------|------|------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12                               | 27/11 | 26/10 | 25/9 | 24/8   | 23/7     | 22/6 | 21/5     | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 2020                        | DCRCCON                         | 31:16     | _     | _     | BYTO  | <1:0>                               | WBO   | _     | _    | BITO   | _        | _    | _        | _    | _    | _    | _    | _    | 0000       |

| 3030                        | DCRCCON                         | 15:0      | _     | _     | _     | - PLEN<4:0> CRCEN CRCAPP CRCTYP CRC |       |       |      |        |          |      | RCCH<2:0 | >    | 0000 |      |      |      |            |

| 2040                        | DCRCDATA                        | 31:16     |       |       |       |                                     |       |       |      |        |          |      |          |      |      |      |      | 0000 |            |

| 3040                        | DCKCDAIA                        | 15:0      |       |       |       |                                     |       |       |      | DCRCDA | IA\31.0> |      |          |      |      |      |      |      | 0000       |

| 3050                        | DCRCXOR                         | 31:16     |       |       |       |                                     |       |       |      | DCRCXC | D-31:0>  |      |          |      |      |      |      |      | 0000       |

| 3030                        | DCKCXOK                         | 15:0      |       |       |       |                                     |       |       |      | DURUXU | /K\31.U> |      |          |      |      |      |      |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

### REGISTER 9-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)

- bit 4 **CHDHIF:** Channel Destination Half Full Interrupt Flag bit

- 1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)

- 0 = No interrupt is pending

- bit 3 CHBCIF: Channel Block Transfer Complete Interrupt Flag bit

- 1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs

- 0 = No interrupt is pending

- bit 2 CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit

- 1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)

- 0 = No interrupt is pending

- bit 1 CHTAIF: Channel Transfer Abort Interrupt Flag bit

- 1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted

- 0 = No interrupt is pending

- bit 0 CHERIF: Channel Address Error Interrupt Flag bit

- 1 = A channel address error has been detected (either the source or the destination address is invalid)

- 0 = No interrupt is pending

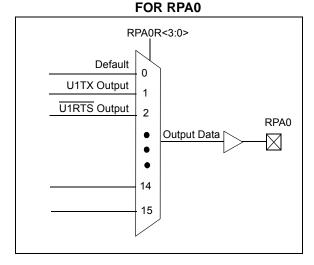

#### 11.3.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the PPS options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 11-2) are used to control output mapping. Like the [pin name]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

FIGURE 11-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT

## 11.3.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to the peripheral map:

- · Control register lock sequence

- · Configuration bit select lock

### 11.3.6.1 Control Register Lock Sequence

Under normal operation, writes to the RPnR and [pin name]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, IOLOCK (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 6.** "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

### 11.3.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [pin name]R registers. The Configuration bit, IOL1WAY (DEVCFG3<29>), blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the PPS control registers cannot be written to. The only way to clear the bit and reenable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

## 18.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 24.** "InterIntegrated Circuit (I<sup>2</sup>C)" (DS60001116), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard. Figure 18-1 illustrates the I<sup>2</sup>C module block diagram.

Each I<sup>2</sup>C module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

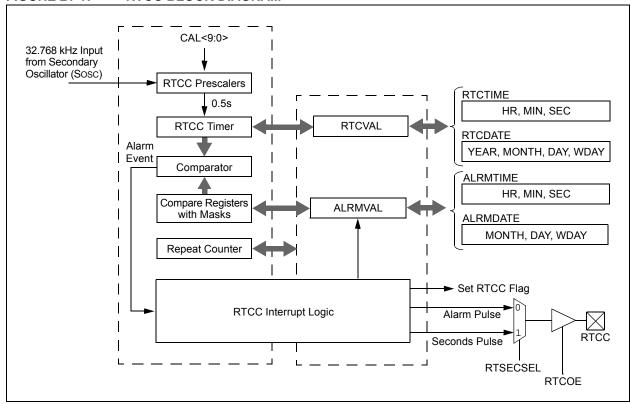

## 21.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time.

Following are some of the key features of this module:

- · Time: hours, minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- · Provides calendar: day, date, month and year

- Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month and one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat: Chime

- · Year range: 2000 to 2099

- Leap year correction

- · BCD format for smaller firmware overhead

- · Optimized for long-term battery operation

- · Fractional second synchronization

- User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- Calibrates up to 260 ppm of crystal error

- · Requirements: External 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

#### REGISTER 23-1: CMXCON: COMPARATOR CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                   | _                 | _                 |                   | _                | _                |

| 22.46        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                   | _                 | _                 | -                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | _                 | _                 | _                 | _                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            | _                   | CREF              | _                 | _                 | CCH              | <1:0>            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

1 = Module is enabled. Setting this bit does not affect the other bits in this register

0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

bit 14 COE: Comparator Output Enable bit

1 = Comparator output is driven on the output CxOUT pin

0 = Comparator output is not driven on the output CxOUT pin

bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

1 = Output is inverted

0 = Output is not inverted

bit 12-9 Unimplemented: Read as '0'

bit 8 **COUT:** Comparator Output bit

1 = Output of the Comparator is a '1'

0 = Output of the Comparator is a '0'

bit 7-6 **EVPOL<1:0>:** Interrupt Event Polarity Select bits

11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

00 = Comparator interrupt generation is disabled

bit 5 **Unimplemented:** Read as '0'

bit 4 **CREF:** Comparator Positive Input Configure bit

1 = Comparator non-inverting input is connected to the internal CVREF

0 = Comparator non-inverting input is connected to the CxINA pin

bit 3-2 Unimplemented: Read as '0'

bit 1-0 **CCH<1:0>:** Comparator Negative Input Select bits for Comparator

11 = Comparator inverting input is connected to the IVREF

10 = Comparator inverting input is connected to the CxIND pin

01 = Comparator inverting input is connected to the CxINC pin

00 = Comparator inverting input is connected to the CxINB pin

**Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

### REGISTER 27-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

- bit 15-14 FCKSM<1:0>: Clock Switching and Monitor Selection Configuration bits

- 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

- 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

- 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

- bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output disabled

- 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

- bit 9-8 POSCMOD<1:0>: Primary Oscillator Configuration bits

- 11 = Primary Oscillator is disabled

- 10 = HS Oscillator mode is selected

- 01 = XT Oscillator mode is selected

- 00 = External Clock mode is selected

- bit 7 **IESO:** Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 Reserved: Write '1'

- bit 5 FSOSCEN: Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 **Reserved:** Write '1'

- bit 2-0 FNOSC<2:0>: Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT. HS. EC)(1)

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

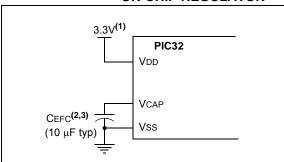

### 27.3 On-Chip Voltage Regulator

All PIC32MX1XX/2XX 28/36/44-pin Family devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX1XX/2XX 28/36/44-pin Family family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 30.1** "**DC Characteristics**".

**Note:** It is important that the low-ESR capacitor is placed as close as possible to the VCAP pin.

### 27.3.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

#### 27.3.2 ON-CHIP REGULATOR AND BOR

PIC32MX1XX/2XX 28/36/44-pin Family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 30.1** "DC Characteristics".

FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

- Note 1: These are typical operating voltages. Refer to Section 30.1 "DC Characteristics" for the full operating ranges of VDD.

- **2:** It is important that the low-ESR capacitor is placed as close as possible to the VCAP pin.

- **3:** The typical voltage on the VCAP pin is 1.8V.

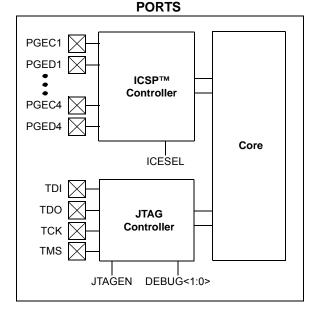

### 27.4 Programming and Diagnostics

PIC32MX1XX/2XX 28/36/44-pin Family devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming™ (ICSP™) interfaces

- · Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

Figure 27-2 illustrates a block diagram of the programming, debugging, and trace ports.

FIGURE 27-2: BLOCK DIAGRAM OF PROGRAMMING, DEBUGGING AND TRACE

TABLE 30-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARA      | CTERISTICS             | 3               | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                                    |             |  |  |  |  |  |

|---------------|------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------|--|--|--|--|--|

| Parameter No. | Typical <sup>(3)</sup> | Max.            | Units                                                                                                                                                                                                                                          | Conditions                         |             |  |  |  |  |  |

| Operating (   | Current (IDD)          | (Notes 1, 2, 5) | )                                                                                                                                                                                                                                              |                                    |             |  |  |  |  |  |

| DC20          | 2                      | 3               | mA                                                                                                                                                                                                                                             | 4 MF                               | łz (Note 4) |  |  |  |  |  |

| DC21          | 7                      | 10.5            | mA                                                                                                                                                                                                                                             | 1                                  | 0 MHz       |  |  |  |  |  |

| DC22          | 10                     | 15              | mA                                                                                                                                                                                                                                             | 20 MI                              | Hz (Note 4) |  |  |  |  |  |

| DC23          | 15                     | 23              | mA                                                                                                                                                                                                                                             | 30 MHz (Note 4)                    |             |  |  |  |  |  |

| DC24          | 20                     | 30              | mA                                                                                                                                                                                                                                             | 40 MHz                             |             |  |  |  |  |  |

| DC25          | 100                    | 150             | μA                                                                                                                                                                                                                                             | +25°C, 3.3V LPRC (31 kHz) (Note 4) |             |  |  |  |  |  |

- **Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- · OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, Program Flash, and SRAM data memory are operational, SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- · WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- $\bullet \ \ CPU \ executing \ while (1) \ \ statement \ from \ Flash$

- · RTCC and JTAG are disabled

- **3:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- **4:** This parameter is characterized, but not tested in manufacturing.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

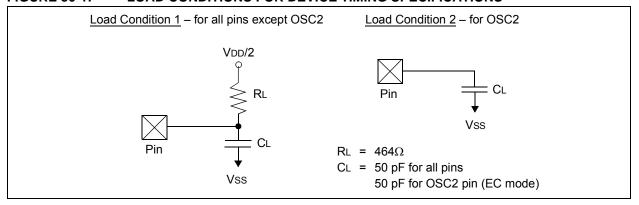

## 30.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC32MX1XX/2XX 28/36/44-pin Family AC characteristics and timing parameters.

### FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| .,            |         |                       |                                                                                                                                                                                                                                                    |                        |      |       |                          |  |  |  |  |

|---------------|---------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------------|--|--|--|--|

| AC CHA        | RACTERI | STICS                 | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \leq \text{Ta} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{Ta} \leq +105^{\circ}\text{C}$ for V-temp |                        |      |       |                          |  |  |  |  |

| Param.<br>No. | Symbol  | Characteristics       | Min.                                                                                                                                                                                                                                               | Typical <sup>(1)</sup> | Max. | Units | Conditions               |  |  |  |  |

| DO56          | Сю      | All I/O pins and OSC2 | _                                                                                                                                                                                                                                                  | _                      | 50   | pF    | EC mode                  |  |  |  |  |

| DO58          | Св      | SCLx, SDAx            | _                                                                                                                                                                                                                                                  | _                      | 400  | pF    | In I <sup>2</sup> C mode |  |  |  |  |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

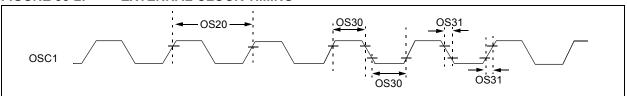

### FIGURE 30-2: EXTERNAL CLOCK TIMING

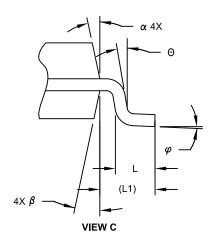

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units  | MILLIMETERS |           |      |  |  |  |  |

|--------------------------|--------|-------------|-----------|------|--|--|--|--|

| Dimension                | Limits | MIN         | NOM       | MAX  |  |  |  |  |

| Number of Pins           | N      |             | 28        |      |  |  |  |  |

| Pitch                    | е      |             | 1.27 BSC  |      |  |  |  |  |

| Overall Height           | Α      | İ           | ı         | 2.65 |  |  |  |  |

| Molded Package Thickness | A2     | 2.05        | ı         | -    |  |  |  |  |

| Standoff §               | A1     | 0.10        | -         | 0.30 |  |  |  |  |

| Overall Width            | Е      |             | 10.30 BSC |      |  |  |  |  |

| Molded Package Width     | E1     |             | 7.50 BSC  |      |  |  |  |  |

| Overall Length           | D      |             | 17.90 BSC |      |  |  |  |  |

| Chamfer (Optional)       | h      | 0.25        | -         | 0.75 |  |  |  |  |

| Foot Length              | ∟      | 0.40        | ı         | 1.27 |  |  |  |  |

| Footprint                | L1     |             | 1.40 REF  |      |  |  |  |  |

| Lead Angle               | Θ      | 0°          | ı         | 1    |  |  |  |  |

| Foot Angle               | φ      | 0°          | ı         | 8°   |  |  |  |  |

| Lead Thickness           | С      | 0.18        | =         | 0.33 |  |  |  |  |

| Lead Width               | b      | 0.31        | -         | 0.51 |  |  |  |  |

| Mold Draft Angle Top     | α      | 5°          | -         | 15°  |  |  |  |  |

| Mold Draft Angle Bottom  | β      | 5°          | -         | 15°  |  |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

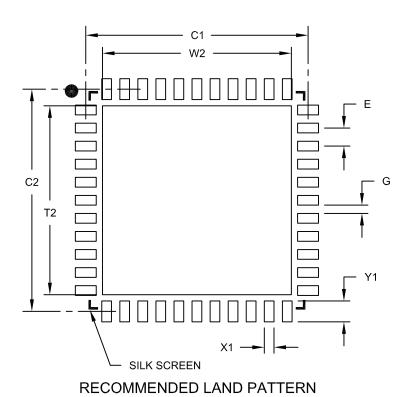

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**>te:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**MILLIMETERS** Units **Dimension Limits** MIN MOM MAX Contact Pitch Ε 0.65 BSC Optional Center Pad Width W2 6.80 Optional Center Pad Length T2 6.80 Contact Pad Spacing C1 8.00 Contact Pad Spacing C2 8.00 Contact Pad Width (X44) X1 0.35 Contact Pad Length (X44) <u>Y1</u> 0.80 0.25 Distance Between Pads G

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103A

TABLE A-1: MAJOR SECTION UPDATES (CONTINUED)

| Section                                            | Update Description                                                                                                                                                                                                                   |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.0 "Memory Organization"                          | Added Memory Maps for the new devices (see Figure 4-3 and Figure 4-4).                                                                                                                                                               |

|                                                    | Removed the BMXCHEDMA bit from the Bus Matrix Register map (see Table 4-1).                                                                                                                                                          |

|                                                    | Added the REFOTRIM register, added the DIVSWEN bit to the REFOCON registers, added Note 4 to the ULOCK and SOSCEN bits and added the PBDIVRDY bit in the OSCCON register in the in the System Control Register map (see Table 4-16). |

|                                                    | Removed the ALTI2C1 and ALTI2C2 bits from the DEVCFG3 register and added Note 1 to the UPLLEN and UPLLIDIV<2:0> bits of the DEVCFG2 register in the Device Configuration Word Summary (see Table 4-17).                              |

|                                                    | Updated Note 1 in the Device and Revision ID Summary (see Table 4-18).                                                                                                                                                               |

|                                                    | Added Note 2 to the PORTA Register map (see Table 4-19).                                                                                                                                                                             |

|                                                    | Added the ANSB6 and ANSB12 bits to the ANSELB register in the PORTB Register map (see Table 4-20).                                                                                                                                   |

|                                                    | Added Notes 2 and 3 to the PORTC Register map (see Table 4-21).                                                                                                                                                                      |

|                                                    | Updated all register names in the Peripheral Pin Select Register map (see Table 4-23).                                                                                                                                               |

|                                                    | Added values in support of new devices (16 KB RAM and 32 KB RAM) in the Data RAM Size register (see Register 4-5).                                                                                                                   |

|                                                    | Added values in support of new devices (64 KB Flash and 128 KB Flash) in the Data RAM Size register (see Register 4-5).                                                                                                              |

| 8.0 "Oscillator Configuration"                     | Added Note 5 to the PIC32MX1XX/2XX Family Clock Diagram (see Figure 8-1).                                                                                                                                                            |

|                                                    | Added the PBDIVRDY bit and Note 2 to the Oscillator Control register (see Register 8-1).                                                                                                                                             |

|                                                    | Added the DIVSWEN bit and Note 3 to the Reference Oscillator Control register (see Register 8-3).                                                                                                                                    |

|                                                    | Added the REFOTRIM register (see Register 8-4).                                                                                                                                                                                      |

| 21.0 "10-bit Analog-to-Digital<br>Converter (ADC)" | Updated the ADC1 Module Block Diagram (see Figure 21-1).                                                                                                                                                                             |

|                                                    | Updated the Notes in the ADC Input Select register (see Register 21-4).                                                                                                                                                              |

| 24.0 "Charge Time Measurement Unit (CTMU)"         | Updated the CTMU Block Diagram (see Figure 24-1).                                                                                                                                                                                    |

|                                                    | Added Note 3 to the CTMU Control register (see Register 24-1)                                                                                                                                                                        |

| 26.0 "Special Features"                            | Added Note 1 and the PGEC4/PGED4 pin pair to the ICESEL<1:0> bits in DEVCFG0: Device Configuration Word 0 (see Register 26-1).                                                                                                       |

|                                                    | Removed the ALTI2C1 and ALTI2C2 bits from the Device Configuration Word 3 register (see Register 26-4).                                                                                                                              |

|                                                    | Removed 26.3.3 "Power-up Requirements".                                                                                                                                                                                              |

|                                                    | Added Note 3 to the Connections for the On-Chip Regulator diagram (see Figure 26-2).                                                                                                                                                 |

|                                                    | Updated the Block Diagram of Programming, Debugging and Trace Ports diagram (see Figure 26-3).                                                                                                                                       |