Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx110f016dt-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4:PIN NAMES FOR 28-PIN USB DEVICES

| 28                                              | PIN SOIC, SPDIP, SSOP (TOP VIEW) <sup>(1,2,3)</sup>                                                                                                                                                                                                                                                                                                                                                                   |                                                                |                                                                                                                                                                                                                    |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                 | 1<br>SSOP                                                                                                                                                                                                                                                                                                                                                                                                             | 28                                                             | 1 28 1 28<br>SOIC SPDIP                                                                                                                                                                                            |

|                                                 | PIC32MX210F016B<br>PIC32MX220F032B<br>PIC32MX230F064B<br>PIC32MX230F256B<br>PIC32MX250F128B<br>PIC32MX270F256B                                                                                                                                                                                                                                                                                                        |                                                                |                                                                                                                                                                                                                    |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                |                                                                                                                                                                                                                    |

| Pin #                                           | Full Pin Name                                                                                                                                                                                                                                                                                                                                                                                                         | Pin #                                                          | Full Pin Name                                                                                                                                                                                                      |

| <b>Pin #</b>                                    | Full Pin Name                                                                                                                                                                                                                                                                                                                                                                                                         | <b>Pin #</b>                                                   | Full Pin Name                                                                                                                                                                                                      |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                |                                                                                                                                                                                                                    |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                             | VBUS                                                                                                                                                                                                               |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                             | VBUS                                                                                                                                                                                                               |

|                                                 | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0                                                                                                                                                                                                                                                                                                                                                                      | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0                                                                                                                                                                                                                                                                                                                                                                      | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1                                                                                                                                                                                                                                                                                                                                                                            | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0                                                                                                                                                                                                                                                                                                                                                                      | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1                                                                                                                                                                                                                                                                                                                                                                            | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0                                                                                                                                                                                                                                                                                                                                                                             | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1                                                                                                                                                                                                 | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2                                                                                                                                               | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                             | Vcap                                                                                                                                                                                                               |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2         AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3                                                                                               | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                             | Vcap                                                                                                                                                                                                               |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2         AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3         Vss                                                                                   | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                             | Vcap                                                                                                                                                                                                               |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |

| 8                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                                             | PGEC2/RPB11/D-/RB11                                                                                                                                                                                                |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2         AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3         Vss         OSC1/CLKI/RPA2/RA2                                                        | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                             | VCAP                                                                                                                                                                                                               |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |

| 8                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                                             | PGEC2/RPB11/D-/RB11                                                                                                                                                                                                |

| 9                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 23                                                             | VUSB3V3                                                                                                                                                                                                            |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10 | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2         AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3         Vss         OSC1/CLKI/RPA2/RA2         OSC2/CLKO/RPA3/PMA0/RA3                        | 15<br>16<br>17<br>18<br>19<br>20<br>21<br>21<br>22<br>23<br>24 | VBUS<br>TDI/RPB7/CTED3/PMD5/INT0/RB7<br>TCK/RPB8/SCL1/CTED10/PMD4/RB8<br>TDO/RPB9/SDA1/CTED4/PMD3/RB9<br>VSS<br>VCAP<br>PGED2/RPB10/D+/CTED11/RB10<br>PGEC2/RPB11/D-/RB11<br>VUSB3V3<br>AN11/RPB13/CTPLS/PMRD/RB13 |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2         AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3         Vss         OSC1/CLKI/RPA2/RA2         OSC2/CLKO/RPA3/PMA0/RA3         SOSCI/RPB4/RB4 | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                             | VcAP                                                                                                                                                                                                               |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |

| 8                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                                             | PGEC2/RPB11/D-/RB11                                                                                                                                                                                                |

| 9                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 23                                                             | VUSB3V3                                                                                                                                                                                                            |

| 10                                              |                                                                                                                                                                                                                                                                                                                                                                                                                       | 24                                                             | AN11/RPB13/CTPLS/PMRD/RB13                                                                                                                                                                                         |

| 11                                              |                                                                                                                                                                                                                                                                                                                                                                                                                       | 25                                                             | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB                                                                                                                                                                     |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

#### TABLE 10: PIN NAMES FOR 44-PIN USB DEVICES

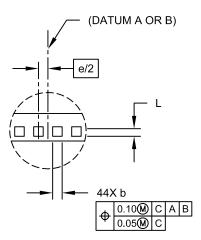

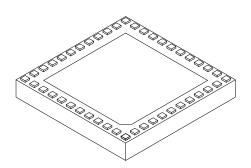

#### 44-PIN QFN (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

|       |                                                  | 44 1  |                                           |

|-------|--------------------------------------------------|-------|-------------------------------------------|

| Pin # | Full Pin Name                                    | Pin # | Full Pin Name                             |

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2     | RPC6/PMA1/RC6                                    | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3     | RPC7/PMA0/RC7                                    | 25    | AN6/RPC0/RC0                              |

| 4     | RPC8/PMA5/RC8                                    | 26    | AN7/RPC1/RC1                              |

| 5     | RPC9/CTED7/PMA6/RC9                              | 27    | AN8/RPC2/PMA2/RC2                         |

| 6     | Vss                                              | 28    | Vdd                                       |

| 7     | VCAP                                             | 29    | Vss                                       |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       | 30    | OSC1/CLKI/RPA2/RA2                        |

| 9     | PGEC2/RPB11/D-/RB11                              | 31    | OSC2/CLKO/RPA3/RA3                        |

| 10    | VUSB3V3                                          | 32    | TDO/RPA8/PMA8/RA8                         |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       | 33    | SOSCI/RPB4/RB4                            |

| 12    | PGED4/TMS/PMA10/RA10                             | 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 13    | PGEC4/TCK/CTED8/PMA7/RA7                         | 35    | TDI/RPA9/PMA9/RA9                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 | 36    | AN12/RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            | 37    | RPC4/PMA4/RC4                             |

| 16    | AVss                                             | 38    | RPC5/PMA3/RC5                             |

| 17    | AVDD                                             | 39    | Vss                                       |

| 18    | MCLR                                             | 40    | Vdd                                       |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 | 41    | RPB5/USBID/RB5                            |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       | 42    | VBUS                                      |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        | 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       | 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

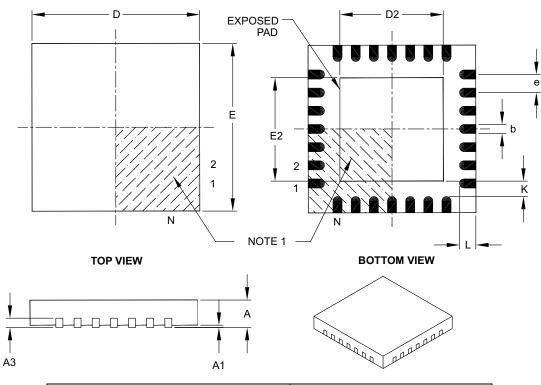

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

#### TABLE 11: PIN NAMES FOR 44-PIN GENERAL PURPOSE DEVICES

### 44-PIN TQFP (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX110F016D PIC32MX120F032D PIC32MX130F064D PIC32MX130F256D PIC32MX150F128D PIC32MX170F256D

44

1

| Pin # | Pin # Full Pin Name                            |    | Full Pin Name                        |

|-------|------------------------------------------------|----|--------------------------------------|

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                       | 23 | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2 |

| 2     | RPC6/PMA1/RC6                                  | 24 | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3   |

| 3     | RPC7/PMA0/RC7                                  | 25 | AN6/RPC0/RC0                         |

| 4     | RPC8/PMA5/RC8                                  | 26 | AN7/RPC1/RC1                         |

| 5     | RPC9/CTED7/PMA6/RC9                            | 27 | AN8/RPC2/PMA2/RC2                    |

| 6     | Vss                                            | 28 | VDD                                  |

| 7     | VCAP                                           | 29 | Vss                                  |

| 8     | PGED2/RPB10/CTED11/PMD2/RB10                   | 30 | OSC1/CLKI/RPA2/RA2                   |

| 9     | PGEC2/RPB11/PMD1/RB11                          | 31 | OSC2/CLKO/RPA3/RA3                   |

| 10    | AN12/PMD0/RB12                                 | 32 | TDO/RPA8/PMA8/RA8                    |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                     | 33 | SOSCI/RPB4/RB4                       |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10           | 34 | SOSCO/RPA4/T1CK/CTED9/RA4            |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7       | 35 | TDI/RPA9/PMA9/RA9                    |

| 14    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 | 36 | RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          | 37 | RPC4/PMA4/RC4                        |

| 16    | AVss                                           | 38 | RPC5/PMA3/RC5                        |

| 17    | AVDD                                           | 39 | Vss                                  |

| 18    | MCLR                                           | 40 | VDD                                  |

| 19    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          | 41 | PGED3/RPB5/PMD7/RB5                  |

| 20    | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                | 42 | PGEC3/RPB6/PMD6/RB6                  |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0           | 43 | RPB7/CTED3/PMD5/INT0/RB7             |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1          | 44 | RPB8/SCL1/CTED10/PMD4/RB8            |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | —                       | _                 |                   | _                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                 | —                 | —                 | —                       | —                 | —                 | —                | -                |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0                     | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                   | _                 |                   | _                       | _                 | S                 | RIPL<2:0>(1)     |                  |  |  |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | _                 | _                 |                   | VEC<5:0> <sup>(1)</sup> |                   |                   |                  |                  |  |  |

#### REGISTER 7-2: INTSTAT: INTERRUPT STATUS REGISTER

#### Legend:

| Legena.           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-11 Unimplemented: Read as '0'

- bit 10-8 SRIPL<2:0>: Requested Priority Level bits<sup>(1)</sup>

- 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

| D:/          | Dit               | Dit               | D:                | Dit               | D'i               | D''               | Dir              | Dit              |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        |                   | IPTMR<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23.10        | IPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 10.0         | IPTMR<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | IPTM              | R<7:0>            |                   | IPTMR<7:0>       |                  |  |  |  |  |  |  |

#### REGISTER 7-3: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Legend:           |                  |                                                     |                    |  |  |

|-------------------|------------------|-----------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                                | x = Bit is unknown |  |  |

bit 31-0 **IPTMR<31:0>:** Interrupt Proximity Timer Reload bits Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

### 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the features<br>of the PIC32MX1XX/2XX 28/36/44-pin<br>Family of devices. It is not intended to be<br>a comprehensive reference source. To<br>complement the information in this data |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | sheet, refer to Section 6. "Oscillator                                                                                                                                                                          |  |  |  |  |  |

|       | Configuration" (DS60001112), which is                                                                                                                                                                           |  |  |  |  |  |

|       | available from the Documentation >                                                                                                                                                                              |  |  |  |  |  |

|       | Reference Manual section of the                                                                                                                                                                                 |  |  |  |  |  |

|       | Microchip PIC32 web site                                                                                                                                                                                        |  |  |  |  |  |

|       | (www.microchip.com/pic32).                                                                                                                                                                                      |  |  |  |  |  |

The PIC32MX1XX/2XX 28/36/44-pin Family oscillator system has the following modules and features:

- Four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        |                   | ROTRIM<8:1>       |                   |                   |                   |                   |                  |                  |  |

| 00.40        | R/W-0             | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | ROTRIM<0>         | _                 | _                 | _                 | —                 | _                 | —                | —                |  |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | —                 | _                 | _                 | _                 | _                 | _                 | —                | _                |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          | _                 | _                 | _                 | _                 | —                 | _                 | _                | —                |  |

#### REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

#### Legend:

| Logona.           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

Note: While the ON (REFOCON<15>) bit is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        |                   |                   |                   | DCRCDAT           | 4<31:24>          |                   |                  |                  |  |

| 00.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | DCRCDATA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | DCRCDA            | TA<7:0>           |                   |                  |                  |  |

#### REGISTER 9-5: DCRCDATA: DMA CRC DATA REGISTER

### Legend:

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

#### REGISTER 9-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 |        |                | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|--------|----------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0  | R/W-0          | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        | DCRCXOR<31:24>    |                   |                   |        |                |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0  | R/W-0          | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |        |                |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0  | R/W-0 R/W-0 R/ |                   | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         | DCRCXOR<15:8>     |                   |                   |        |                |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0 R/W-0       |        | R/W-0          | R/W-0 R/W-0       |                  | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCXO | R<7:0>         |                   |                  |                  |  |  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31.24        |                   | —                 | —                 | _                 | _                 | _                 | _                | —                |  |  |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | —                 | —                 | _                 | -                 | _                 |                   |                  | —                |  |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 15:8         | CHSPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 7:0          |                   |                   |                   | CHSPTF            | R<7:0>            |                   |                  |                  |  |  |  |  |  |

#### REGISTER 9-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

#### Legend: