Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 010                      |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx110f016dt-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 4:PIN NAMES FOR 28-PIN USB DEVICES

| 28                                              | PIN SOIC, SPDIP, SSOP (TOP VIEW) <sup>(1,2,3)</sup>                                                                                                                                                                                                                                                                                                                                                                   |                                                                |                                                                                                                                                                                                                    |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                 | 1<br>SSOP                                                                                                                                                                                                                                                                                                                                                                                                             | 28                                                             | 1 28 1 28<br>SOIC SPDIP                                                                                                                                                                                            |

|                                                 | PIC32MX210F016B<br>PIC32MX220F032B<br>PIC32MX230F064B<br>PIC32MX230F256B<br>PIC32MX250F128B<br>PIC32MX270F256B                                                                                                                                                                                                                                                                                                        |                                                                |                                                                                                                                                                                                                    |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                |                                                                                                                                                                                                                    |

| Pin #                                           | Full Pin Name                                                                                                                                                                                                                                                                                                                                                                                                         | Pin #                                                          | Full Pin Name                                                                                                                                                                                                      |

| <b>Pin #</b>                                    | Full Pin Name                                                                                                                                                                                                                                                                                                                                                                                                         | <b>Pin #</b>                                                   | Full Pin Name                                                                                                                                                                                                      |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                |                                                                                                                                                                                                                    |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                             | VBUS                                                                                                                                                                                                               |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                             | VBUS                                                                                                                                                                                                               |

|                                                 | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0                                                                                                                                                                                                                                                                                                                                                                      | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0                                                                                                                                                                                                                                                                                                                                                                      | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1                                                                                                                                                                                                                                                                                                                                                                            | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 1                                               | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0                                                                                                                                                                                                                                                                                                                                                                      | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1                                                                                                                                                                                                                                                                                                                                                                            | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0                                                                                                                                                                                                                                                                                                                                                                             | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1                                                                                                                                                                                                 | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2                                                                                                                                               | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                             | Vcap                                                                                                                                                                                                               |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2         AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3                                                                                               | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                             | Vcap                                                                                                                                                                                                               |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2         AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3         Vss                                                                                   | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                             | Vcap                                                                                                                                                                                                               |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |

| 8                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                                             | PGEC2/RPB11/D-/RB11                                                                                                                                                                                                |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2         AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3         Vss         OSC1/CLKI/RPA2/RA2                                                        | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                             | VCAP                                                                                                                                                                                                               |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |

| 8                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                                             | PGEC2/RPB11/D-/RB11                                                                                                                                                                                                |

| 9                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 23                                                             | VUSB3V3                                                                                                                                                                                                            |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10 | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2         AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3         Vss         OSC1/CLKI/RPA2/RA2         OSC2/CLKO/RPA3/PMA0/RA3                        | 15<br>16<br>17<br>18<br>19<br>20<br>21<br>21<br>22<br>23<br>24 | VBUS<br>TDI/RPB7/CTED3/PMD5/INT0/RB7<br>TCK/RPB8/SCL1/CTED10/PMD4/RB8<br>TDO/RPB9/SDA1/CTED4/PMD3/RB9<br>VSS<br>VCAP<br>PGED2/RPB10/D+/CTED11/RB10<br>PGEC2/RPB11/D-/RB11<br>VUSB3V3<br>AN11/RPB13/CTPLS/PMRD/RB13 |

| 1                                               | MCLR         PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0         PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1         PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0         PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1         AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2         AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3         Vss         OSC1/CLKI/RPA2/RA2         OSC2/CLKO/RPA3/PMA0/RA3         SOSCI/RPB4/RB4 | 15                                                             | VBUS                                                                                                                                                                                                               |

| 2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 16                                                             | TDI/RPB7/CTED3/PMD5/INT0/RB7                                                                                                                                                                                       |

| 3                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                             | TCK/RPB8/SCL1/CTED10/PMD4/RB8                                                                                                                                                                                      |

| 4                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                             | TDO/RPB9/SDA1/CTED4/PMD3/RB9                                                                                                                                                                                       |

| 5                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                             | Vss                                                                                                                                                                                                                |

| 6                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 20                                                             | VcAP                                                                                                                                                                                                               |

| 7                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                             | PGED2/RPB10/D+/CTED11/RB10                                                                                                                                                                                         |

| 8                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                                             | PGEC2/RPB11/D-/RB11                                                                                                                                                                                                |

| 9                                               |                                                                                                                                                                                                                                                                                                                                                                                                                       | 23                                                             | VUSB3V3                                                                                                                                                                                                            |

| 10                                              |                                                                                                                                                                                                                                                                                                                                                                                                                       | 24                                                             | AN11/RPB13/CTPLS/PMRD/RB13                                                                                                                                                                                         |

| 11                                              |                                                                                                                                                                                                                                                                                                                                                                                                                       | 25                                                             | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB                                                                                                                                                                     |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

| Note: | To access the following documents, refer |

|-------|------------------------------------------|

|       | to the Documentation > Reference         |

|       | Manuals section of the Microchip PIC32   |

|       | website: http://www.microchip.com/pic32  |

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 3. "Memory Organization" (DS60001115)

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer" (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

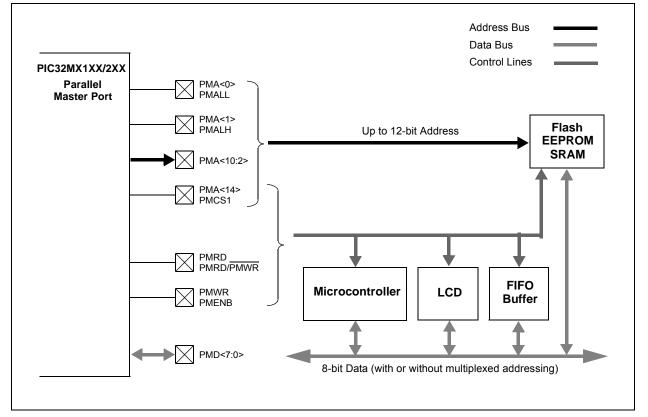

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

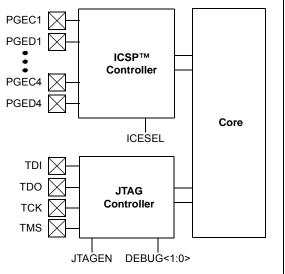

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167)

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

### 2.8.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

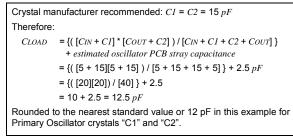

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32\_OSC2\_Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

### EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

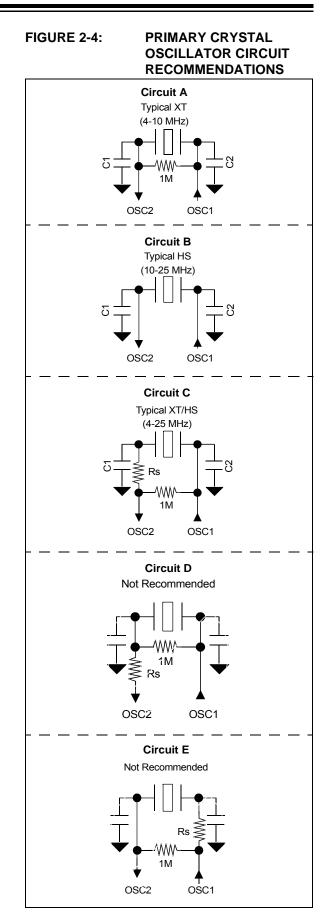

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator. The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

- Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to ~VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with ≤ 1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

#### 2.8.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849 "Basic PICmicro<sup>®</sup> Oscillator Design"

### 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the features<br>of the PIC32MX1XX/2XX 28/36/44-pin<br>Family of devices. It is not intended to be<br>a comprehensive reference source. To<br>complement the information in this data |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|       | sheet, refer to Section 6. "Oscillator                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|       | Configuration" (DS60001112), which is                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|       | available from the Documentation >                                                                                                                                                                              |  |  |  |  |  |  |  |  |

|       | Reference Manual section of the                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|       | Microchip PIC32 web site                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|       | (www.microchip.com/pic32).                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

The PIC32MX1XX/2XX 28/36/44-pin Family oscillator system has the following modules and features:

- Four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24     |                   |                   |                   | CHSSA<            | 31:24>            |                   |                  |                  |  |  |  |

| 00:40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8      | CHSSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0       | CHSSA<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

### **REGISTER 9-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0

CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

Note: This must be the physical address of the source.

#### **REGISTER 9-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        |                   | CHDSA<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | CHDSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   | CHDSA<7:0>        |                   |                   |                   |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **CHDSA<31:0>:** Channel Destination Start Address bits Channel destination start address.

$\ensuremath{\textbf{Note:}}$  This must be the physical address of the destination.

### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 | 0         |       |       |       |       |       |       |      |      | Bi    | ts       |       |          |        |        |           |          | (0         |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _     | —        | _     | —        | _      | _      | —         | —        | 0000       |

| 5200                        |                                 | 15:0      | _     | —     | _     | _     | —     | _     | _    | _    |       |          |       | FRML<    | 7:0>   |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | _     | —     | —     | —     |       | —     | —    | _    |       | —        |       | —        | —      | —      | _         | —        | 0000       |

| 52.50                       | OTTRAIT                         | 15:0      | _     | —     | —     | —     | —     | —     | —    |      |       | —        |       | _        | —      |        | FRMH<2:0> | >        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | _     | —     | —     | —     |       | —     | —    | _    |       | —        | _     | _        | —      | —      | _         | —        | 0000       |

| 5270                        | UTTOR                           | 15:0      | _     | —     | —     | —     | —     | —     | —    |      |       | PID      | <3:0> |          |        | EP     | <3:0>     | -        | 0000       |

| 52B0                        | U1SOF                           | 31:16     | —     | —     |       |       | —     |       |      | _    | _     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 5260                        | 0130F                           | 15:0      | —     |       |       | _     | _     |       | _    |      |       |          |       | CNT<7    | /:0>   |        | -         | •        | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | _     | —     |       | _     |       |       | _    | _    | _     | —        | _     | —        | —      | _      | _         | —        | 0000       |

| 5200                        | OIBDIF2                         | 15:0      | _     | —     |       | _     |       |       | _    | _    |       |          |       | BDTPTR   | H<7:0> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5200                        | 01BD1F3                         | 15:0      | _     | —     |       | _     |       |       | _    | _    |       |          |       | BDTPTRI  | J<7:0> |        |           |          | 0000       |

| 52E0                        | 0 U1CNFG1                       | 31:16     | _     | —     | —     | —     | —     | —     | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5210                        |                                 | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    | UTEYE | UOEMON   |       | USBSIDL  | —      | —      | _         | UASUSPND | 0001       |

| 5300                        | U1EP0                           | 31:16     | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | _        | —      | —      | _         | —        | 0000       |

| 5500                        | UIEI U                          | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    | LSPD  | RETRYDIS |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | _        | —      | —      | _         | —        | 0000       |

| 5510                        | UIEI I                          | 15:0      | _     | _     | —     | —     | —     | —     | —    | _    |       | —        |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | —     | —     | _     | _     | _     | _     | —    | _    | —     | —        | —     | _        | —      | _      | —         | —        | 0000       |

| 0020                        | OTET 2                          | 15:0      | _     | —     |       | —     | —     |       | —    | —    |       | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | _     | —     |       | —     | —     | —     | —    |      |       | —        | _     |          | —      | —      |           | —        | 0000       |

| 0000                        | UTER 0                          | 15:0      | _     | —     |       | —     | —     |       | —    | —    |       | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      |           | —        | 0000       |

| 0010                        | 01EFT                           | 15:0      | —     | —     | —     | —     | —     |       | —    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0000                        | 01EI 0                          | 15:0      | —     | —     | —     | —     | —     |       | —    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5360                        | U1EP6                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0000                        | 0.2.0                           | 15:0      | _     | _     | _     | —     |       |       |      |      | _     | —        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5370                        | U1EP7                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | —     | —        | —      | —      |           | —        | 0000       |

| 3070                        | 01217                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5380                        | U1EP8                           | 31:16     | _     | —     | —     | —     |       |       | —    | _    | _     | —        | _     | _        | —      | —      | —         | —        | 0000       |

| 5500                        | UTEP8                           | 15:0      | —     | -     | _     | _     | —     | _     | _    | _    | _     | —        | —     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | _                 |                   |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | _                 | -                 | —                 | _                 | _                 | -                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | P]R<3:0>         |                  |

#### **REGISTER 11-1:** [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

#### Legend:

| Legena.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

### bit 31-4 Unimplemented: Read as '0'

bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 11-1 for input pin selection values.

Note: Register values can only be changed if the Configuration bit, IOLOCK (CFGCON<13>), = 0.

#### REGISTER 11-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | —                 |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   |                   |                   | RPnR              | <3:0>            |                  |

### Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 11-2 for output pin selection values.

Note: Register values can only be changed if the Configuration bit, IOLOCK (CFGCON<13>), = 0.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | —                 |                   |                   | _                 | _                 | -                | _                |

| 15:8         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 10.0         | ON <sup>(1)</sup> | —                 | SIDL              | TWDIS             | TWIP              | —                 | -                | _                |

| 7:0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |