Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                 |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

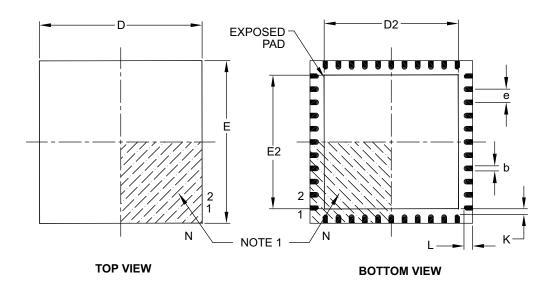

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx110f016dt-v-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-1: PINOUT I/O DESCRIPTIONS

|          |               | Pin Nu                            | mber <sup>(1)</sup> |                                 |             |                |                                                                                                                                                                                    |

|----------|---------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                        |

| AN0      | 27            | 2                                 | 33                  | 19                              | I           | Analog         | Analog input channels.                                                                                                                                                             |

| AN1      | 28            | 3                                 | 34                  | 20                              | I           | Analog         |                                                                                                                                                                                    |

| AN2      | 1             | 4                                 | 35                  | 21                              | I           | Analog         |                                                                                                                                                                                    |

| AN3      | 2             | 5                                 | 36                  | 22                              | I           | Analog         |                                                                                                                                                                                    |

| AN4      | 3             | 6                                 | 1                   | 23                              | I           | Analog         |                                                                                                                                                                                    |

| AN5      | 4             | 7                                 | 2                   | 24                              | I           | Analog         |                                                                                                                                                                                    |

| AN6      | _             | _                                 | 3                   | 25                              | I           | Analog         |                                                                                                                                                                                    |

| AN7      | _             | _                                 | 4                   | 26                              | ı           | Analog         |                                                                                                                                                                                    |

| AN8      | _             | _                                 | _                   | 27                              | ı           | Analog         |                                                                                                                                                                                    |

| AN9      | 23            | 26                                | 29                  | 15                              | ı           | Analog         |                                                                                                                                                                                    |

| AN10     | 22            | 25                                | 28                  | 14                              | ı           | Analog         |                                                                                                                                                                                    |

| AN11     | 21            | 24                                | 27                  | 11                              | ı           | Analog         |                                                                                                                                                                                    |

| A N 14 O | 20(2)         | 23 <sup>(2)</sup>                 | 26 <sup>(2)</sup>   | 10 <sup>(2)</sup>               |             | A 1            |                                                                                                                                                                                    |

| AN12     | 20(2)         | 23(2)                             | 11 <sup>(3)</sup>   | 36 <sup>(3)</sup>               |             | Analog         |                                                                                                                                                                                    |

| CLKI     | 6             | 9                                 | 7                   | 30                              | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                             |

| CLKO     | 7             | 10                                | 8                   | 31                              | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1     | 6             | 9                                 | 7                   | 30                              | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                    |

| OSC2     | 7             | 10                                | 8                   | 31                              | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                           |

| SOSCI    | 8             | 11                                | 9                   | 33                              | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                     |

| SOSCO    | 9             | 12                                | 10                  | 34                              | 0           | _              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                    |

| REFCLKI  | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | Reference Input Clock                                                                                                                                                              |

| REFCLKO  | PPS           | PPS                               | PPS                 | PPS                             | 0           | _              | Reference Output Clock                                                                                                                                                             |

| IC1      | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | Capture Inputs 1-5                                                                                                                                                                 |

| IC2      | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             |                                                                                                                                                                                    |

| IC3      | PPS           | PPS                               | PPS                 | PPS                             | ı           | ST             |                                                                                                                                                                                    |

| IC4      | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             |                                                                                                                                                                                    |

| IC5      | PPS           | PPS                               | PPS                 | PPS                             | ı           | ST             |                                                                                                                                                                                    |

**Legend:** CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

P = Power

TTL = TTL input buffer

O = Output PPS = Peripheral Pin Select I = Input

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

— = N/A

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                   | Pin Nu                            | mber <sup>(1)</sup> | •                               |             |                |                                                                         |  |  |

|----------|-------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|-------------------------------------------------------------------------|--|--|

| Pin Name | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                             |  |  |

| USBID    | 11 <sup>(3)</sup> | 14 <sup>(3)</sup>                 | 15 <sup>(3)</sup>   | 41(3)                           | ı           | ST             | USB OTG ID detect                                                       |  |  |

| CTED1    | 27                | 2                                 | 33                  | 19                              | I           | ST             | CTMU External Edge Input                                                |  |  |

| CTED2    | 28                | 3                                 | 34                  | 20                              | I           | ST             | 1                                                                       |  |  |

| CTED3    | 13                | 16                                | 17                  | 43                              | I           | ST             | 1                                                                       |  |  |

| CTED4    | 15                | 18                                | 19                  | 1                               | I           | ST             | 1                                                                       |  |  |

| CTED5    | 22                | 25                                | 28                  | 14                              | I           | ST             | 1                                                                       |  |  |

| CTED6    | 23                | 26                                | 29                  | 15                              | I           | ST             | 1                                                                       |  |  |

| CTED7    | _                 | _                                 | 20                  | 5                               | I           | ST             | 1                                                                       |  |  |

| CTED8    | _                 | _                                 | -                   | 13                              | I           | ST             | 1                                                                       |  |  |

| CTED9    | 9                 | 12                                | 10                  | 34                              | I           | ST             | 1                                                                       |  |  |

| CTED10   | 14                | 17                                | 18                  | 44                              | I           | ST             | 1                                                                       |  |  |

| CTED11   | 18                | 21                                | 24                  | 8                               | I           | ST             | 1                                                                       |  |  |

| CTED12   | 2                 | 5                                 | 36                  | 22                              | I           | ST             | 1                                                                       |  |  |

| CTED13   | 3                 | 6                                 | 1                   | 23                              | I           | ST             | 1                                                                       |  |  |

| CTPLS    | 21                | 24                                | 27                  | 11                              | 0           | _              | CTMU Pulse Output                                                       |  |  |

| PGED1    | 1                 | 4                                 | 35                  | 21                              | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 1          |  |  |

| PGEC1    | 2                 | 5                                 | 36                  | 22                              | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 1 |  |  |

| PGED2    | 18                | 21                                | 24                  | 8                               | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 2          |  |  |

| PGEC2    | 19                | 22                                | 25                  | 9                               | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 2 |  |  |

| PGED3    | 11 <sup>(2)</sup> | 14 <sup>(2)</sup>                 | 15 <sup>(2)</sup>   | 41 <sup>(2)</sup>               | I/O         | ST             | Data I/O pin for Programming/Debugging                                  |  |  |

| PGED3    | 27 <sup>(3)</sup> | 2 <sup>(3)</sup>                  | 33(3)               | 19 <sup>(3)</sup>               | 1/0         | 31             | Communication Channel 3                                                 |  |  |

| DCEC2    | 12 <sup>(2)</sup> | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup>   | 42 <sup>(2)</sup>               |             | ST             | Clock input pin for Programming/                                        |  |  |

| PGEC3    | 28 <sup>(3)</sup> | 3(3)                              | 34 <sup>(3)</sup>   | 20 <sup>(3)</sup>               | 1 '         | 31             | Debugging Communication Channel 3                                       |  |  |

| PGED4    | _                 | _                                 | 3                   | 12                              | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 4          |  |  |

| PGEC4    | _                 | _                                 | 4                   | 13                              | I           | ST             | Clock input pin for Programming/<br>Debugging Communication Channel 4   |  |  |

**Legend:** CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input O = Output P = Power I = Input

TTL = TTL input buffer

PPS = Peripheral Pin Select

--=N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

**3:** Pin number for PIC32MX2XX devices only.

TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| Interrupt Source <sup>(1)</sup>     | IRQ | Vector |              | Interru       | pt Bit Location |              | Persistent |

|-------------------------------------|-----|--------|--------------|---------------|-----------------|--------------|------------|

| interrupt Source(*)                 | #   | #      | Flag         | Enable        | Priority        | Sub-priority | Interrupt  |

|                                     |     | Highes | st Natural O | rder Priority | 1               | •            | •          |

| CT – Core Timer Interrupt           | 0   | 0      | IFS0<0>      | IEC0<0>       | IPC0<4:2>       | IPC0<1:0>    | No         |

| CS0 – Core Software Interrupt 0     | 1   | 1      | IFS0<1>      | IEC0<1>       | IPC0<12:10>     | IPC0<9:8>    | No         |

| CS1 – Core Software Interrupt 1     | 2   | 2      | IFS0<2>      | IEC0<2>       | IPC0<20:18>     | IPC0<17:16>  | No         |

| INT0 – External Interrupt           | 3   | 3      | IFS0<3>      | IEC0<3>       | IPC0<28:26>     | IPC0<25:24>  | No         |

| T1 – Timer1                         | 4   | 4      | IFS0<4>      | IEC0<4>       | IPC1<4:2>       | IPC1<1:0>    | No         |

| IC1E - Input Capture 1 Error        | 5   | 5      | IFS0<5>      | IEC0<5>       | IPC1<12:10>     | IPC1<9:8>    | Yes        |

| IC1 – Input Capture 1               | 6   | 5      | IFS0<6>      | IEC0<6>       | IPC1<12:10>     | IPC1<9:8>    | Yes        |

| OC1 – Output Compare 1              | 7   | 6      | IFS0<7>      | IEC0<7>       | IPC1<20:18>     | IPC1<17:16>  | No         |

| INT1 – External Interrupt 1         | 8   | 7      | IFS0<8>      | IEC0<8>       | IPC1<28:26>     | IPC1<25:24>  | No         |

| T2 – Timer2                         | 9   | 8      | IFS0<9>      | IEC0<9>       | IPC2<4:2>       | IPC2<1:0>    | No         |

| IC2E – Input Capture 2              | 10  | 9      | IFS0<10>     | IEC0<10>      | IPC2<12:10>     | IPC2<9:8>    | Yes        |

| IC2 – Input Capture 2               | 11  | 9      | IFS0<11>     | IEC0<11>      | IPC2<12:10>     | IPC2<9:8>    | Yes        |

| OC2 – Output Compare 2              | 12  | 10     | IFS0<12>     | IEC0<12>      | IPC2<20:18>     | IPC2<17:16>  | No         |

| INT2 – External Interrupt 2         | 13  | 11     | IFS0<13>     | IEC0<13>      | IPC2<28:26>     | IPC2<25:24>  | No         |

| T3 – Timer3                         | 14  | 12     | IFS0<14>     | IEC0<14>      | IPC3<4:2>       | IPC3<1:0>    | No         |

| IC3E - Input Capture 3              | 15  | 13     | IFS0<15>     | IEC0<15>      | IPC3<12:10>     | IPC3<9:8>    | Yes        |

| IC3 – Input Capture 3               | 16  | 13     | IFS0<16>     | IEC0<16>      | IPC3<12:10>     | IPC3<9:8>    | Yes        |

| OC3 – Output Compare 3              | 17  | 14     | IFS0<17>     | IEC0<17>      | IPC3<20:18>     | IPC3<17:16>  | No         |

| INT3 – External Interrupt 3         | 18  | 15     | IFS0<18>     | IEC0<18>      | IPC3<28:26>     | IPC3<25:24>  | No         |

| T4 – Timer4                         | 19  | 16     | IFS0<19>     | IEC0<19>      | IPC4<4:2>       | IPC4<1:0>    | No         |

| IC4E – Input Capture 4 Error        | 20  | 17     | IFS0<20>     | IEC0<20>      | IPC4<12:10>     | IPC4<9:8>    | Yes        |

| IC4 – Input Capture 4               | 21  | 17     | IFS0<21>     | IEC0<21>      | IPC4<12:10>     | IPC4<9:8>    | Yes        |

| OC4 – Output Compare 4              | 22  | 18     | IFS0<22>     | IEC0<22>      | IPC4<20:18>     | IPC4<17:16>  | No         |

| INT4 – External Interrupt 4         | 23  | 19     | IFS0<23>     | IEC0<23>      | IPC4<28:26>     | IPC4<25:24>  | No         |

| T5 – Timer5                         | 24  | 20     | IFS0<24>     | IEC0<24>      | IPC5<4:2>       | IPC5<1:0>    | No         |

| IC5E – Input Capture 5 Error        | 25  | 21     | IFS0<25>     | IEC0<25>      | IPC5<12:10>     | IPC5<9:8>    | Yes        |

| IC5 – Input Capture 5               | 26  | 21     | IFS0<26>     | IEC0<26>      | IPC5<12:10>     | IPC5<9:8>    | Yes        |

| OC5 – Output Compare 5              | 27  | 22     | IFS0<27>     | IEC0<27>      | IPC5<20:18>     | IPC5<17:16>  | No         |

| AD1 – ADC1 Convert done             | 28  | 23     | IFS0<28>     | IEC0<28>      | IPC5<28:26>     | IPC5<25:24>  | Yes        |

| FSCM – Fail-Safe Clock Monitor      | 29  | 24     | IFS0<29>     | IEC0<29>      | IPC6<4:2>       | IPC6<1:0>    | No         |

| RTCC – Real-Time Clock and Calendar | 30  | 25     | IFS0<30>     | IEC0<30>      | IPC6<12:10>     | IPC6<9:8>    | No         |

| FCE – Flash Control Event           | 31  | 26     | IFS0<31>     | IEC0<31>      | IPC6<20:18>     | IPC6<17:16>  | No         |

| CMP1 – Comparator Interrupt         | 32  | 27     | IFS1<0>      | IEC1<0>       | IPC6<28:26>     | IPC6<25:24>  | No         |

| CMP2 – Comparator Interrupt         | 33  | 28     | IFS1<1>      | IEC1<1>       | IPC7<4:2>       | IPC7<1:0>    | No         |

| CMP3 – Comparator Interrupt         | 34  | 29     | IFS1<2>      | IEC1<2>       | IPC7<12:10>     | IPC7<9:8>    | No         |

| USB – USB Interrupts                | 35  | 30     | IFS1<3>      | IEC1<3>       | IPC7<20:18>     | IPC7<17:16>  | Yes        |

| SPI1E – SPI1 Fault                  | 36  | 31     | IFS1<4>      | IEC1<4>       | IPC7<28:26>     | IPC7<25:24>  | Yes        |

| SPI1RX – SPI1 Receive Done          | 37  | 31     | IFS1<5>      | IEC1<5>       | IPC7<28:26>     | IPC7<25:24>  | Yes        |

| SPI1TX – SPI1 Transfer Done         | 38  | 31     | IFS1<6>      | IEC1<6>       | IPC7<28:26>     | IPC7<25:24>  | Yes        |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/36/44-Pin General Purpose Family Features" and TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features" for the lists of available peripherals.

#### REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS09            | IFS08            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | IFS07             | IFS06             | IFS05             | IFS04             | IFS03             | IFS02             | IFS01            | IFS00            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 IFS31-IFS00: Interrupt Flag Status bits

1 = Interrupt request has occurred

0 = No interrupt request has occurred

Note: This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit

definitions.

#### REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.6         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC09            | IEC08            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | IEC07             | IEC06             | IEC05             | IEC04             | IEC03             | IEC02             | IEC01            | IEC00            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 IEC31-IEC00: Interrupt Enable bits

1 = Interrupt is enabled0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

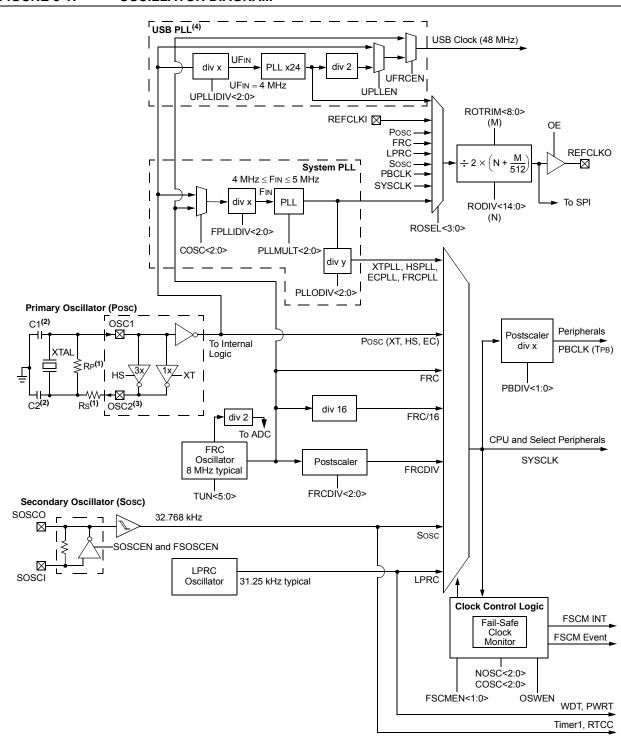

FIGURE 8-1: OSCILLATOR DIAGRAM

- Notes: 1. A series resistor, Rs, may be required for AT strip cut crystals or eliminate clipping. Alternately, to increase oscillator circuit gain, add a parallel resistor, RP, with a value of 1 MΩ.

- Refer to Section 6. "Oscillator Configuration" (DS60001112) in the "PIC32 Family Reference Manual" for help in determining the best oscillator components.

- 3. The PBCLK out is only available on the OSC2 pin in certain clock modes.

- 4. The USB PLL is only available on PIC32MX2XX devices.

TABLE 11-1: INPUT PIN SELECTION

| Peripheral Pin | [pin name]R SFR | [pin name]R bits | [pin name]R Value to<br>RPn Pin Selection                                              |  |  |  |  |  |

|----------------|-----------------|------------------|----------------------------------------------------------------------------------------|--|--|--|--|--|

| INT4           | INT4R           | INT4R<3:0>       | 0000 = RPA0<br>0001 = RPB3                                                             |  |  |  |  |  |

| T2CK           | T2CKR           | T2CKR<3:0>       | 0010 = RPB4<br>0011 = RPB15<br>0100 = RPB7                                             |  |  |  |  |  |

| IC4            | IC4R            | IC4R<3:0>        | 0101 = RPC7 <sup>(2)</sup><br>0110 = RPC0 <sup>(1)</sup><br>0111 = RPC5 <sup>(2)</sup> |  |  |  |  |  |

| SS1            | SS1R            | SS1R<3:0>        | 1000 = Reserved                                                                        |  |  |  |  |  |

| REFCLKI        | REFCLKIR        | REFCLKIR<3:0>    | 1111 = Reserved                                                                        |  |  |  |  |  |

| INT3           | INT3R           | INT3R<3:0>       | 0000 = RPA1<br>0001 = RPB5                                                             |  |  |  |  |  |

| T3CK           | T3CKR           | T3CKR<3:0>       | 0010 = RPB1<br>0011 = RPB11                                                            |  |  |  |  |  |

| IC3            | IC3R            | IC3R<3:0>        | 0100 = RPB8<br>0101 = RPA8 <sup>(2)</sup>                                              |  |  |  |  |  |

| U1CTS          | U1CTSR          | U1CTSR<3:0>      | 0110 = RPC8 <sup>(2)</sup><br>0111 = RPA9 <sup>(2)</sup>                               |  |  |  |  |  |

| U2RX           | U2RXR           | U2RXR<3:0>       | 1000 = Reserved                                                                        |  |  |  |  |  |

| SDI1           | SDI1R           | SDI1R<3:0>       | 1111 = Reserved                                                                        |  |  |  |  |  |

| INT2           | INT2R           | INT2R<3:0>       | 0000 = RPA2                                                                            |  |  |  |  |  |

| T4CK           | T4CKR           | T4CKR<3:0>       | 0001 = RPB6<br>0010 = RPA4                                                             |  |  |  |  |  |

| IC1            | IC1R            | IC1R<3:0>        | 0011 = RPB13<br>0100 = RPB2                                                            |  |  |  |  |  |

| IC5            | IC5R            | IC5R<3:0>        | 0101 = RPC6 <sup>(2)</sup>                                                             |  |  |  |  |  |

| U1RX           | U1RXR           | U1RXR<3:0>       | 0110 = RPC1 <sup>(1)</sup><br>0111 = RPC3 <sup>(1)</sup>                               |  |  |  |  |  |

| U2CTS          | U2CTSR          | U2CTSR<3:0>      | 1000 = Reserved                                                                        |  |  |  |  |  |

| SDI2           | SDI2R           | SDI2R<3:0>       | <b></b>                                                                                |  |  |  |  |  |

| OCFB           | OCFBR           | OCFBR<3:0>       | • 1111 = Reserved                                                                      |  |  |  |  |  |

| INT1           | INT1R           | INT1R<3:0>       | 0000 = RPA3<br>0001 = RPB14                                                            |  |  |  |  |  |

| T5CK           | T5CKR           | T5CKR<3:0>       | 0010 = RPB0<br>0011 = RPB10<br>0100 = RPB9                                             |  |  |  |  |  |

| IC2            | IC2R            | IC2R<3:0>        | 0101 = RPC9 <sup>(1)</sup><br>0110 = RPC2 <sup>(2)</sup><br>0111 = RPC4 <sup>(2)</sup> |  |  |  |  |  |

| SS2            | SS2R            | SS2R<3:0>        | 1000 = Reserved                                                                        |  |  |  |  |  |

| OCFA           | OCFAR           | OCFAR<3:0>       | •<br>•<br>1111 = Reserved                                                              |  |  |  |  |  |

Note 1: This pin is not available on 28-pin devices.

<sup>2:</sup> This pin is only available on 44-pin devices.

TABLE 11-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits   | RPnR Value to Peripheral Selection          |

|--------------|----------|-------------|---------------------------------------------|

| RPA0         | RPA0R    | RPA0R<3:0>  | 0000 = No Connect                           |

| RPB3         | RPB3R    | RPB3R<3:0>  | 0001 = <u>U1TX</u><br>0010 = <u>U2RTS</u>   |

| RPB4         | RPB4R    | RPB4R<3:0>  | 0011 = SS1                                  |

| RPB15        | RPB15R   | RPB15R<3:0> | 0100 = Reserved<br>0101 = OC1               |

| RPB7         | RPB7R    | RPB7R<3:0>  | 0110 = Reserved<br>0111 = C2OUT             |

| RPC7         | RPC7R    | RPC7R<3:0>  | 1000 = Reserved                             |

| RPC0         | RPC0R    | RPC0R<3:0>  | :                                           |

| RPC5         | RPC5R    | RPC5R<3:0>  | •<br>1111 = Reserved                        |

| RPA1         | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                           |

| RPB5         | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPB1         | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                 |

| RPB11        | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                   |

| RPB8         | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                             |

| RPA8         | RPA8R    | RPA8R<3:0>  | 0111 = C3OUT                                |

| RPC8         | RPC8R    | RPC8R<3:0>  | <b></b> :                                   |

| RPA9         | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                             |

| RPA2         | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                           |

| RPB6         | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPA4         | RPA4R    | RPA4R<3:0>  | 0011 = SDO1<br>0100 = SDO2                  |

| RPB13        | RPB13R   | RPB13R<3:0> | 0101 = OC4                                  |

| RPB2         | RPB2R    | RPB2R<3:0>  | 0110 = OC5<br>0111 = REFCLKO                |

| RPC6         | RPC6R    | RPC6R<3:0>  | 1000 = Reserved                             |

| RPC1         | RPC1R    | RPC1R<3:0>  | :                                           |

| RPC3         | RPC3R    | RPC3R<3:0>  | 1111 = Reserved                             |

| RPA3         | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                           |

| RPB14        | RPB14R   | RPB14R<3:0> | 0001 = U1RTS<br>0010 = U2TX                 |

| RPB0         | RPB0R    | RPB0R<3:0>  | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |

| RPB10        | RPB10R   | RPB10R<3:0> | 0101 = OC3                                  |

| RPB9         | RPB9R    | RPB9R<3:0>  | 0110 = Reserved<br>0111 = C1OUT             |

| RPC9         | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                             |

| RPC2         | RPC2R    | RPC2R<3:0>  | <b></b> :                                   |

| RPC4         | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                             |

TABLE 11-6: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| SS                          |                  |           |       |       |       |       |       |       | (00  |      | its  |      |      |      |      |       |          |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1     | 16/0 | All Resets |

| FA54                        | U1CTSR           | 31:16     | ı     | _     | _     | _     | _     | _     | _    | _    | 1    | _    | _    | _    |      | _     | _        | ı    | 0000       |

| FA54                        | UICISK           | 15:0      | -     | _     | _     |       | -     | _     | _    |      | -    | _    | _    | _    |      | U1CTS | R<3:0>   |      | 0000       |

| FA58                        | U2RXR            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | _    | 0000       |

| FASO                        | UZKAK            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U2RX  | R<3:0>   |      | 0000       |

| FA5C                        | U2CTSR           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | -    | 0000       |

| FASC                        | UZCISK           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U2CTS | R<3:0>   |      | 0000       |

| FA84                        | SDI1R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | -    | 0000       |

| FA04                        | SUIIK            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | SDI1F | R<3:0>   |      | 0000       |

| FA88                        | SS1R             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | -    | 0000       |

| FAOO                        | 33 IK            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | SS1R  | <3:0>    |      | 0000       |

| FA90                        | SDI2R            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | -    | 0000       |

| FA90                        | SDIZK            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | SDI2F | R<3:0>   |      | 0000       |

| FA94                        | SS2R             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | -    | 0000       |

| FA94                        | 332K             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | SS2R  | <3:0>    |      | 0000       |

| EVDo                        | REFCLKIR         | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _        | _    | 0000       |

| I ADO                       | NLI OLNIK        | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | REFCL | (IR<3:0> |      | 0000       |

## 13.2 Timer Control Registers

### TABLE 13-1: TIMER2-TIMER5 REGISTER MAP

| SS                          |                                 |           |       |       |       |       |       |       |      | Ві   | its    |      |          |      |      |      |      |      |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|--------|------|----------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5     | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0800                        | T2CON                           | 31:16     | _     | -     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    |      | 0000       |

| 0000                        | 12001                           | 15:0      | ON    | _     | SIDL  | _     | _     | _     | _    | _    | TGATE  | 7    | CKPS<2:0 | >    | T32  | _    | TCS  |      | 0000       |

| 0810                        | TMR2                            | 31:16     | _     | _     | _     | _     | _     | _     | _    |      | _      |      | _        | _    | _    | _    | _    | _    | 0000       |

| 0010                        | TIVITYZ                         | 15:0      |       |       |       |       |       |       |      |      |        |      |          |      |      |      | 0000 |      |            |

| 0820                        | PR2                             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    | _    | 0000       |

| 0020                        |                                 | 15:0      |       |       |       |       |       |       |      |      |        |      |          |      | FFFF |      |      |      |            |

| 0400                        | T3CON                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    |      | 0000       |

| 0,00                        | 13001                           | 15:0      | ON    |       | SIDL  |       | _     | _     | _    |      | TGATE  | 7    | CKPS<2:0 | >    | _    | _    | TCS  | _    | 0000       |

| 0410                        | TMR3                            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    | _    | 0000       |

| 0/110                       | TIVITO                          | 15:0      |       |       |       |       |       |       |      | TMR3 | <15:0> |      |          |      |      |      |      |      | 0000       |

| 0A20                        | PR3                             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    | _    | 0000       |

| 07120                       |                                 | 15:0      |       |       |       |       |       |       |      | PR3< | :15:0> |      |          |      |      |      |      |      | FFFF       |

| 0000                        | T4CON                           | 31:16     | _     | _     | _     | _     | _     |       | _    | _    | _      | _    | _        | _    | _    | _    | _    | _    | 0000       |

| 0000                        |                                 | 15:0      | ON    | _     | SIDL  | _     | _     |       | _    | _    | TGATE  | 7    | CKPS<2:0 | >    | T32  | _    | TCS  | _    | 0000       |

| 0C10                        | TMR4                            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    | _    | 0000       |

| 00.0                        |                                 | 15:0      |       |       |       |       |       |       |      | TMR4 | <15:0> |      |          |      |      | I    | 1    |      | 0000       |

| 0C20                        | PR4                             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    | _    | 0000       |

| 0020                        |                                 | 15:0      |       |       | ı     |       | 1     |       |      | PR4< | :15:0> |      | 1        |      | ı    |      | ı    |      | FFFF       |

| 0F00                        | T5CON                           | 31:16     | _     | -     | _     | _     | _     | -     | _    | _    | _      | _    | _        | _    | _    | _    | _    | -    | 0000       |

| 3200                        |                                 | 15:0      | ON    | _     | SIDL  | _     | _     | _     | _    |      | TGATE  |      | CKPS<2:0 | >    | _    | _    | TCS  | _    | 0000       |

| 0E10                        | TMR5                            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    | _    | 0000       |

| 02.10                       |                                 | 15:0      |       |       |       |       |       |       |      | TMR5 | <15:0> |      |          |      |      | I    | 1    |      | 0000       |

| 0E20                        | PR5                             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | _        | _    | _    | _    | _    | _    | 0000       |

| 3220                        |                                 | 15:0      |       |       |       |       |       |       |      |      |        |      |          |      | FFFF |      |      |      |            |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| PIC32IVIA | (1XX/2X | X 28/36 | )/44-PIN | Y FAIVIII | _ Y |  |

|-----------|---------|---------|----------|-----------|-----|--|

| NOTES:    |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

|           |         |         |          |           |     |  |

## 15.1 Input Capture Control Registers

#### TABLE 15-1: INPUT CAPTURE 1-INPUT CAPTURE 5 REGISTER MAP

|                             | LE 13-1.              |               | FOI CAFTORE 1-INFOT CAFTORE 3 REGISTER MAF |                                                           |       |       |       |       |       |        |        |      |      |      |       |      |          |      |            |

|-----------------------------|-----------------------|---------------|--------------------------------------------|-----------------------------------------------------------|-------|-------|-------|-------|-------|--------|--------|------|------|------|-------|------|----------|------|------------|

| ess                         |                       | •             |                                            |                                                           |       |       |       |       |       | Bi     | ts     |      |      |      |       |      |          |      | ,,         |

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15                                      | 30/14                                                     | 29/13 | 28/12 | 27/11 | 26/10 | 25/9  | 24/8   | 23/7   | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1     | 16/0 | All Resets |

| 2000                        | IC1CON <sup>(1)</sup> | 31:16         | _                                          | _                                                         | _     | _     | _     | _     | _     | _      | _      | _    | _    | _    | _     | _    | _        | _    | 0000       |

| 2000                        | IC ICON.              | 15:0          | ON                                         | _                                                         | SIDL  | _     | _     | _     | FEDGE | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2010                        | IC1BUF                | 31:16<br>15:0 |                                            |                                                           |       |       |       |       |       | IC1BUF | <31:0> |      |      |      |       |      |          |      | xxxx       |

|                             |                       | 31:16         | _                                          | _                                                         | _     | _     | _     | _     | _     | _      | _      | _    | _    | _    | _     | _    | _        | _    | 0000       |

| 2200                        | IC2CON <sup>(1)</sup> | 15:0          | ON                                         | ON - SIDL FEDGE C32 ICTMR ICI<1:0> ICOV ICBNE ICM<2:0> 00 |       |       |       |       |       |        |        |      |      | 0000 |       |      |          |      |            |

| 2210                        | IC2BUF                | 31:16<br>15:0 | IC2BUF<31:0>                               |                                                           |       |       |       |       |       |        |        |      | xxxx |      |       |      |          |      |            |

| 0.400                       | 100001(1)             | 31:16         | _                                          | _                                                         | _     | _     | _     | _     | _     | _      | _      | _    | _    | _    | _     | _    | _        | _    | 0000       |

| 2400                        | IC3CON <sup>(1)</sup> | 15:0          | ON                                         | _                                                         | SIDL  | _     | _     | -     | FEDGE | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2410                        | IC3BUF                | 31:16<br>15:0 |                                            |                                                           |       |       |       |       |       | IC3BUF | <31:0> |      |      |      |       |      |          |      | xxxx       |

| 0000                        | IC4CON <sup>(1)</sup> | 31:16         | _                                          | _                                                         | _     | _     | _     | _     | _     | _      | _      | _    | _    | _    | _     | _    | _        | _    | 0000       |

| 2600                        | IC4CON**              | 15:0          | ON                                         | _                                                         | SIDL  | _     | _     | _     | FEDGE | C32    | ICTMR  | ICI< | 1:0> | ICOV | ICBNE |      | ICM<2:0> |      | 0000       |

| 2610                        | IC4BUF                | 31:16<br>15:0 |                                            |                                                           |       |       |       |       |       | IC4BUF | <31:0> |      |      |      |       |      |          |      | xxxx       |

| 2000                        | 10500N(1)             | 31:16         | _                                          | _                                                         | _     | _     | _     | _     | _     | _      | _      | _    | _    | _    | _     | _    | _        | _    | 0000       |

| 2000                        | IC5CON <sup>(1)</sup> | 15:0          |                                            |                                                           |       |       |       |       |       |        |        |      | 0000 |      |       |      |          |      |            |

| 2810                        | IC5BUF                | 31:16<br>15:0 | 1 IC5BUF<31:0>                             |                                                           |       |       |       |       |       |        |        |      | xxxx |      |       |      |          |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### REGISTER 18-2: I2CXSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | -                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |

|              | ACKSTAT           | TRSTAT            | _                 | _                 | _                 | BCL               | GCSTAT           | ADD10            |

| 7:0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |

|              | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |

Legend:HS = Set in hardwareHSC = Hardware set/clearedR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedC = Clearable bit

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ACKSTAT:** Acknowledge Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Acknowledge was not received from slave

- 0 = Acknowledge was received from slave

Hardware set or clear at end of slave Acknowledge.

- bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

- 1 = A bus collision has been detected during a master operation

- 0 = No collision

Hardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module.

- bit 9 GCSTAT: General Call Status bit

- 1 = General call address was received

- 0 = General call address was not received

Hardware set when address matches general call address. Hardware clear at Stop detection.

- bit 8 ADD10: 10-bit Address Status bit

- 1 = 10-bit address was matched

- 0 = 10-bit address was not matched

Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

- bit 7 IWCOL: Write Collision Detect bit

- 1 = An attempt to write the I2CxTRN register failed because the I2C module is busy

- 0 = No collision

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

- bit 6 I2COV: Receive Overflow Flag bit

- 1 = A byte was received while the I2CxRCV register is still holding the previous byte

- 0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

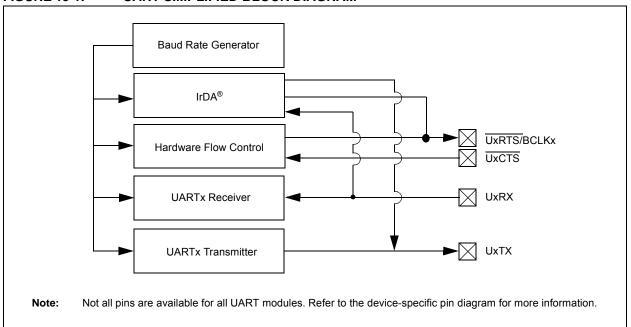

# 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 21.** "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The UART module is one of the serial I/O modules available in PIC32MX1XX/2XX 28/36/44-pin Family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN, and IrDA®. The UART module also supports the hardware flow control option, with UxCTS and UxRTS pins, and also includes an IrDA encoder and decoder.

Key features of the UART module include:

- Full-duplex. 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- · One or two Stop bits

- · Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 38 bps to 12.5 Mbps at 50 MHz

- 8-level deep First In First Out (FIFO) transmit data buffer

- · 8-level deep FIFO receive data buffer

- · Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9th bit = 1)

- · Separate transmit and receive interrupts

- · Loopback mode for diagnostic support

- · LIN protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the UART module.

FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

#### REGISTER 22-1: AD1CON1: ADC CONTROL REGISTER 1 (CONTINUED)

- bit 4 **CLRASAM:** Stop Conversion Sequence bit (when the first ADC interrupt is generated)

- 1 = Stop conversions when the first ADC interrupt is generated. Hardware clears the ASAM bit when the ADC interrupt is generated.

- 0 = Normal operation, buffer contents will be overwritten by the next conversion sequence

- bit 3 Unimplemented: Read as '0'

- bit 2 **ASAM:** ADC Sample Auto-Start bit

- 1 = Sampling begins immediately after last conversion completes; SAMP bit is automatically set.

- 0 = Sampling begins when SAMP bit is set

- bit 1 SAMP: ADC Sample Enable bit<sup>(2)</sup>

- 1 = The ADC sample and hold amplifier is sampling

- 0 = The ADC sample/hold amplifier is holding

- When ASAM = 0, writing '1' to this bit starts sampling.

When SSRC = 000, writing '0' to this bit will end sampling and start conversion.

- bit 0 **DONE**: Analog-to-Digital Conversion Status bit<sup>(3)</sup>

- 1 = Analog-to-digital conversion is done

- 0 = Analog-to-digital conversion is not done or has not started

Clearing this bit will not affect any operation in progress.

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ '0', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

| I I C J Z I WI X I Z | 20/30/ | 7-7-1 II <b>V</b> |  |  |

|----------------------|--------|-------------------|--|--|

| NOTES:               |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

|                      |        |                   |  |  |

#### REGISTER 27-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 18-10 PWP<8:0>: Program Flash Write-Protect bits(3)

```

Prevents selected program Flash memory pages from being modified during code execution.

111111111 = Disabled

111111110 = Memory below 0x0400 address is write-protected

111111101 = Memory below 0x0800 address is write-protected

111111100 = Memory below 0x0C00 address is write-protected

111111011 = Memory below 0x1000 (4K) address is write-protected

111111010 = Memory below 0x1400 address is write-protected

111111001 = Memory below 0x1800 address is write-protected

111111000 = Memory below 0x1C00 address is write-protected

111110111 = Memory below 0x2000 (8K) address is write-protected

111110110 = Memory below 0x2400 address is write-protected

111110101 = Memory below 0x2800 address is write-protected

111110100 = Memory below 0x2C00 address is write-protected

111110011 = Memory below 0x3000 address is write-protected

111110010 = Memory below 0x3400 address is write-protected

111110001 = Memory below 0x3800 address is write-protected

111110000 = Memory below 0x3C00 address is write-protected

111101111 = Memory below 0x4000 (16K) address is write-protected

110111111 = Memory below 0x10000 (64K) address is write-protected

101111111 = Memory below 0x20000 (128K) address is write-protected

011111111 = Memory below 0x40000 (256K) address is write-protected

000000000 = All possible memory is write-protected

Reserved: Write '1'

ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits(2)

11 = PGEC1/PGED1 pair is used

10 = PGEC2/PGED2 pair is used

01 = PGEC3/PGED3 pair is used

00 = PGEC4/PGED4 pair is used<sup>(2)</sup>

JTAGEN: JTAG Enable bit(1)

1 = JTAG is enabled

0 = JTAG is disabled

DEBUG<1:0>: Background Debugger Enable bits (forced to '11' if code-protect is enabled)

1x = Debugger is disabled

0x = Debugger is enabled

2: The PGEC4/PGED4 pin pair is not available on all devices. Refer to the "Pin Diagrams" section for

```

- Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

- availability.

- 3: The PWP<8:7> bits are only available on devices with 256 KB Flash.

bit 9-5

bit 4-3

bit 2

bit 1-0

#### 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

#### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- MPLAB X IDE compatibility

#### 31.0 50 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX1XX/2XX 28/36/44-pin Family electrical characteristics for devices operating at 50 MHz.

The specifications for 50 MHz are identical to those shown in **Section 30.0** "**Electrical Characteristics**", with the exception of the parameters listed in this chapter.

Parameters in this chapter begin with the letter "M", which denotes 50 MHz operation. For example, parameter DC29a in **Section 30.0** "**Electrical Characteristics**", is the up to 40 MHz operation equivalent for MDC29a.

Absolute maximum ratings for the PIC32MX1XX/2XX 28/36/44-pin Family 50 MHz devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

# **Absolute Maximum Ratings**

#### (See Note 1)

| Ambient temperature under bias                                              | 40°C to +85°C            |

|-----------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                         | 65°C to +150°C           |

| Voltage on VDD with respect to Vss                                          | 0.3V to +4.0V            |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)    | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when VDD ≥ 2.3V (Note 3) | 0.3V to +5.5V            |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3) | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to Vusb3v3                             | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                         | 0.3V to +5.5V            |

| Maximum current out of Vss pin(s)                                           | 300 mA                   |

| Maximum current into VDD pin(s) (Note 2)                                    | 300 mA                   |

| Maximum output current sunk by any I/O pin                                  | 15 mA                    |

| Maximum output current sourced by any I/O pin                               | 15 mA                    |

| Maximum current sunk by all ports                                           | 200 mA                   |

| Maximum current sourced by all ports (Note 2)                               | 200 mA                   |

- **Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

#### TABLE 31-5: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS                |  |                                                                                    | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature -40°C ≤ TA ≤ +85°C for Industrial |      |          |            |                               |

|-----------------------------------|--|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|----------|------------|-------------------------------|

| Param. No. Symbol Characteristics |  | Min.                                                                               | Typical                                                                                                                       | Max. | Units    | Conditions |                               |

| MOS10                             |  | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC<br>4                                                                                                                       |      | 50<br>50 |            | EC (Note 2)<br>ECPLL (Note 1) |

**Note 1:** PLL input requirements: 4 MHz ≤ FPLLIN ≤ 5 MHz (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

#### TABLE 31-6: SPIX MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS         |      |                                  | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature -40°C ≤ TA ≤ +85°C for Industrial |         |      |       |            |

|----------------------------|------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|

| Param. No. Characteristics |      | Characteristics                  | Min.                                                                                                                          | Typical | Max. | Units | Conditions |