#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ХF

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Through Hole                                                                     |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                          |

| Supplier Device Package    | 28-SPDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f032b-50i-sp |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 10: PIN NAMES FOR 44-PIN USB DEVICES

## 44-PIN QFN (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

|       |                                                  |       | 44 1                                      |

|-------|--------------------------------------------------|-------|-------------------------------------------|

| Pin # | Full Pin Name                                    | Pin # | Full Pin Name                             |

| 1     | RPB9/SDA1/CTED4/PMD3/RB9                         | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2     | RPC6/PMA1/RC6                                    | 24    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3     | RPC7/PMA0/RC7                                    | 25    | AN6/RPC0/RC0                              |

| 4     | RPC8/PMA5/RC8                                    | 26    | AN7/RPC1/RC1                              |

| 5     | RPC9/CTED7/PMA6/RC9                              | 27    | AN8/RPC2/PMA2/RC2                         |

| 6     | Vss                                              | 28    | Vdd                                       |

| 7     | VCAP                                             | 29    | Vss                                       |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       | 30    | OSC1/CLKI/RPA2/RA2                        |

| 9     | PGEC2/RPB11/D-/RB11                              | 31    | OSC2/CLKO/RPA3/RA3                        |

| 10    | VUSB3V3                                          | 32    | TDO/RPA8/PMA8/RA8                         |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       | 33    | SOSCI/RPB4/RB4                            |

| 12    | PGED4/TMS/PMA10/RA10                             | 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 13    | PGEC4/TCK/CTED8/PMA7/RA7                         | 35    | TDI/RPA9/PMA9/RA9                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 | 36    | AN12/RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            | 37    | RPC4/PMA4/RC4                             |

| 16    | AVss                                             | 38    | RPC5/PMA3/RC5                             |

| 17    | AVDD                                             | 39    | Vss                                       |

| 18    | MCLR                                             | 40    | Vdd                                       |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 | 41    | RPB5/USBID/RB5                            |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       | 42    | VBUS                                      |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        | 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       | 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX110F016D and PIC32MX120F032D devices.

5: Shaded pins are 5V tolerant.

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUs

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

## 2.1 Basic Connection Requirements

Getting started with the PIC32MX1XX/2XX 28/36/44pin Family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pins may be required:

• VREF+/VREF- pins – used when external voltage reference for the ADC module is implemented

Note: The AVDD and AVss pins must be connected, regardless of ADC use and the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu F$  to 0.001  $\mu F$ . Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu F$  in parallel with 0.001  $\mu F$ .

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

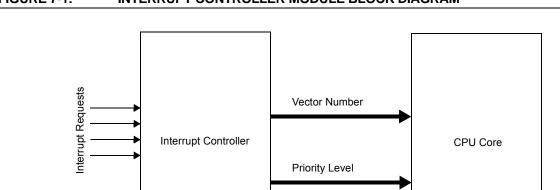

## 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX1XX/2XX 28/36/44-pin Family interrupt module includes the following features:

- Up to 64 interrupt sources

- · Up to 44 interrupt vectors

- · Single and multi-vector mode operations

- Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- · Software can generate any interrupt

- User-configurable Interrupt Vector Table (IVT) location

- User-configurable interrupt vector spacing

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

## FIGURE 7-1: INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

Note: The dedicated shadow register set is not present on PIC32MX1XX/2XX 28/36/44-pin Family devices.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | —                 | —                 |                   | _                | —                |

| 23:16        | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | —                 | —                 | _                 | —                | —                |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | —                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | —                 | _                 |                   |                   | TUN<              | 5:0> <b>(1)</b>   |                  |                  |

## REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

## Legend:

| Logona.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized, nor tested.

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                          | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|--------------------------------------------|-------------------|------------------|------------------|--|--|

|              | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                                      | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | _                 |                   |                   | R                 | )<2017/2017/2017/2017/2017/2017/2017/2017/ | 1,3)              |                  |                  |  |  |

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                                      | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        |                   |                   |                   | RODIV<            | :7:0> <b>(1,3)</b>                         |                   |                  |                  |  |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0                                      | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |

| 15:8         | ON                | _                 | SIDL              | OE                | RSLP <sup>(2)</sup>                        | _                 | DIVSWEN          | ACTIVE           |  |  |

|              | U-0               | U-0               | U-0               | U-0               | R/W-0                                      | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   |                   |                                            | ROSEL             | .<3:0>(1)        |                  |  |  |

## REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Legend:           | HC = Hardware Clearable | HS = Hardware Settable             |                    |

|-------------------|-------------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared               | x = Bit is unknown |

bit 31 Unimplemented: Read as '0'

| bit 30-16 | RODIV<14:0> Reference Clock Divider bits <sup>(1,3)</sup>                           |

|-----------|-------------------------------------------------------------------------------------|

|           | The value selects the reference clock divider bits. See Figure 8-1 for information. |

| bit 15    | ON: Output Enable bit                                                               |

|           | 1 = Reference Oscillator module is enabled                                          |

|           | 0 = Reference Oscillator module is disabled                                         |

| bit 14    | Unimplemented: Read as '0'                                                          |

| bit 13    | SIDL: Peripheral Stop in Idle Mode bit                                              |

- 1 = Discontinue module operation when the device enters Idle mode

- 0 =Continue module operation when the device enters lide mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator module output continues to run in Sleep

- 0 = Reference Oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 |                   |                   |                   | —                 |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | —                 |                   |                   | -                 | —                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -                 | —                 | —                 | -                 | -                 | —                 | —                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7:0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          |                  | VBUSVDIE         |

## REGISTER 10-2: U1OTGIE: USB OTG INTERRUPT ENABLE REGISTER

### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIE:** ID Interrupt Enable bit

- 1 = ID interrupt is enabled

- 0 = ID interrupt is disabled

## bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt is enabled

- 0 = 1 millisecond timer interrupt is disabled

#### bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt is enabled

- 0 = Line state interrupt is disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = Activity interrupt is enabled

- 0 = Activity interrupt is disabled

- bit 3 SESVDIE: Session Valid Interrupt Enable bit

- 1 = Session valid interrupt is enabled

- 0 = Session valid interrupt is disabled

- bit 2 SESENDIE: B-Device Session End Interrupt Enable bit

- 1 = B-Device session end interrupt is enabled

- 0 = B-Device session end interrupt is disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-Device VBUS Valid Interrupt Enable bit

- 1 = A-Device VBUS valid interrupt is enabled

- 0 = A-Device VBUS valid interrupt is disabled

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | _                 |                   |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | _                 | -                 | —                 | _                 | _                 | -                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | P]R<3:0>         |                  |

#### **REGISTER 11-1:** [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

## Legend:

| Legena.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

## bit 31-4 Unimplemented: Read as '0'

bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 11-1 for input pin selection values.

Note: Register values can only be changed if the Configuration bit, IOLOCK (CFGCON<13>), = 0.

## REGISTER 11-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | —                 |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   |                   |                   | RPnR              | <3:0>            |                  |

## Legend:

| 0                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 11-2 for output pin selection values.

Note: Register values can only be changed if the Configuration bit, IOLOCK (CFGCON<13>), = 0.

## 19.1 UART Control Registers

## TABLE 19-1: UART1 AND UART2 REGISTER MAP

| np for point | ess                         |                  | 6         |                               |        |        |       |        |       |       | Bi          | ts          |         |       |             |        |       |        |       | 6          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|-----------|-------------------------------|--------|--------|-------|--------|-------|-------|-------------|-------------|---------|-------|-------------|--------|-------|--------|-------|------------|

| 6000         01MODe <sup>1</sup> 15.0         ON         -         SIDL         IREN         RTSMD         -         UEN<1.0>         WAKE         LPBACK         ABAUD         RXINV         BRGH         PDEL<1.0>         STSL         0.00           610         U1STA(1)         31.16         -         -         -         -         ADM_EN         VERSE         ADM         ADM_EN         RIDE         PERR         PERR         OERR         VERSO         0000           0107         116         -         -         -         -         -         -         -         -         0000         0000           01080         116         -         -         -         -         -         -         -         -         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15                         | 30/14  | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7        | 22/6    | 21/5  | 20/4        | 19/3   | 18/2  | 17/1   | 16/0  | All Resets |

| 610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610 <td>6000</td> <td></td> <td>31:16</td> <td></td> <td></td> <td>_</td> <td>_</td> <td>—</td> <td></td> <td></td> <td>_</td> <td></td> <td>—</td> <td></td> <td></td> <td>_</td> <td>_</td> <td>_</td> <td>_</td> <td>0000</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6000                        |                  | 31:16     |                               |        | _      | _     | —      |       |       | _           |             | —       |       |             | _      | _     | _      | _     | 0000       |

| 600         UTXINT         UTXINV         UTXINV         UTXEN         UTXEN <t< td=""><td>0000</td><td>OTWODE</td><td>15:0</td><td>ON</td><td></td><td>SIDL</td><td>IREN</td><td>RTSMD</td><td>—</td><td>UEN</td><td>-</td><td>WAKE</td><td>LPBACK</td><td>ABAUD</td><td>RXINV</td><td>BRGH</td><td>PDSEI</td><td>L&lt;1:0&gt;</td><td>STSEL</td><td>0000</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0000                        | OTWODE           | 15:0      | ON                            |        | SIDL   | IREN  | RTSMD  | —     | UEN   | -           | WAKE        | LPBACK  | ABAUD | RXINV       | BRGH   | PDSEI | L<1:0> | STSEL | 0000       |

| 15:0         15:0         01XSE<10.5         01XBR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6010                        | 111STA(1)        | 31:16     | _                             | _      | _      | —     | —      | _     | _     | ADM_EN      |             |         |       | ADDR        | 2<7:0> |       |        |       | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0010                        | UIUIA            | 15:0      | UTXISE                        | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE      | EL<1:0> | ADDEN | RIDLE       | PERR   | FERR  | OERR   | URXDA | 0110       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6020                        |                  | 31:16     | —                             | -      | —      | _     | —      | —     | -     | —           | _           | —       | —     | _           | _      | _     | —      | _     | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0020                        | UTTAKLG          | 15:0      | _                             |        | _      |       | _      | _     |       |             |             |         | Tra   | nsmit Regis | ster   |       |        |       | 0000       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6030                        | U1RXREG          | 31:16     | _                             |        | _      |       | _      | _     |       | _           | _           | _       | _     |             | -      |       | _      |       | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0030                        |                  | 15:0      | _                             |        | _      |       | _      | _     |       |             |             |         | Re    | ceive Regis | ster   |       |        |       | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6040                        |                  | 31:16     | -                             |        | -      |       | _      | -     |       | —           | —           | _       | -     |             | -      |       | -      |       | 0000       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00+0                        | 0 IDIXO          | 15:0      | Baud Rate Generator Prescaler |        |        |       |        |       |       |             | 0000        |         |       |             |        |       |        |       |            |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6200                        | 112MODE(1)       | 31:16     | _                             | _      | _      | —     | —      | _     | _     | —           | —           | —       | _     | -           | —      | _     | —      | _     | 0000       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0200                        | OZINODL          | 15:0      | ON                            |        | SIDL   | IREN  | RTSMD  | —     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV       | BRGH   | PDSE  | L<1:0> | STSEL | 0000       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6210                        | 112974(1)        | 31:16     | _                             |        | _      |       | _      | _     |       | ADM_EN      |             |         |       | ADDR        | <7:0>  |       |        |       | 0000       |

| 620     U2TXREG     15:0     -     -     -     -     -     -     -     -     000       6230     U2RXREG     31:16     -     -     -     -     -     -     -     -     000       6230     U2RXREG     31:16     -     -     -     -     -     -     -     -     000       6240     U2BRG(1)     31:16     -     -     -     -     -     -     -     000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0210                        | 0231A. /         | 15:0      | UTXISE                        | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE      | EL<1:0> | ADDEN | RIDLE       | PERR   | FERR  | OERR   | URXDA | 0110       |

| 150     -     -     -     -     -     -     -     -     -     000       623     U2RXEG     31:6     -     -     -     -     -     -     -     -     -     000       623     U2RXEG     31:16     -     -     -     -     -     -     -     -     -     -     000       6240     U2BRG(1)     31:16     -     -     -     -     -     -     -     -     000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6220                        |                  | 31:16     | _                             |        | _      |       | _      | _     |       | _           | _           | _       | _     |             | -      |       | _      |       | 0000       |

| 6230     U2RXREG     -     -     -     -     -     -     -     0000       6240     U2BRG <sup>(1)</sup> 31:16     -     -     -     -     -     -     -     -     0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0220                        | UZTARLO          | 15:0      | _                             |        | _      |       | _      | _     |       |             |             |         | Tra   | nsmit Regis | ster   |       |        |       | 0000       |

| 150       -       -       -       -       -       -       -       0000         6240       U2BRG(1)       31:16       -       -       -       -       -       -       -       -       0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6230                        |                  | 31:16     | _                             | _      | _      | _     | _      | _     | _     | _           | _           | _       | _     | _           | _      | _     | _      | _     | 0000       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0230                        | UZNAREG          | 15:0      | _                             | _      | _      | _     | _      | _     | _     |             |             |         | Re    | ceive Regis | ster   |       |        |       | 0000       |

| 02140     02140     02140     15:0     Baud Rate Generator Prescaler     0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6240                        |                  | 31:16     | _                             | _      | _      | _     | _      | _     | _     | _           | _           | _       | _     | _           | _      | _     | _      | _     | 0000       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0240                        | UZDRG."          | 15:0      |                               |        |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |             |        |       |        |       | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

## REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Wait of 4 Трв

- 10 = Wait of 3 Трв

- 01 = Wait of 2 TPB

- 00 = Wait of 1 TPB (default)

For Read operations:

- 11 = Wait of 3 Трв

- 10 = Wait of 2 TPB

- 01 = Wait of 1 Трв

- 00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

## REGISTER 21-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 5-4 **Unimplemented:** Read as '0'

- bit 3 RTCWREN: RTC Value Registers Write Enable bit<sup>(4)</sup>

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read