Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                   |                                                                                |

|--------------------------|--------------------------------------------------------------------------------|

| roduct Status            | Active                                                                         |

| ore Processor            | MIPS32® M4K™                                                                   |

| ore Size                 | 32-Bit Single-Core                                                             |

| peed                     | 40MHz                                                                          |

| onnectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| eripherals               | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| umber of I/O             | 21                                                                             |

| ogram Memory Size        | 32KB (32K x 8)                                                                 |

| ogram Memory Type        | FLASH                                                                          |

| PROM Size                | -                                                                              |

| M Size                   | 8K x 8                                                                         |

| ltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| ta Converters            | A/D 10x10b                                                                     |

| cillator Type            | Internal                                                                       |

| erating Temperature      | -40°C ~ 85°C (TA)                                                              |

| ounting Type             | Surface Mount                                                                  |

| ckage / Case             | 28-VQFN Exposed Pad                                                            |

| pplier Device Package    | 28-QFN (6x6)                                                                   |

| ırchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f032b-i-ml |

#### TABLE 6: PIN NAMES FOR 28-PIN USB DEVICES

28-PIN QFN (TOP VIEW)(1,2,3,4)

PIC32MX210F016B PIC32MX220F032B PIC32MX230F064B PIC32MX230F256B PIC32MX250F128B PIC32MX270F256B

28

| Pin # | Full Pin Name                              |

|-------|--------------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0  |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1 |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2  |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3    |

| 5     | Vss                                        |

| 6     | OSC1/CLKI/RPA2/RA2                         |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3                    |

| 8     | SOSCI/RPB4/RB4                             |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4             |

| 10    | VDD                                        |

| 11    | TMS/RPB5/USBID/RB5                         |

| 12    | VBUS                                       |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7               |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8              |

| Pin# | Full Pin Name                                    |

|------|--------------------------------------------------|

| 15   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 16   | Vss                                              |

| 17   | VCAP                                             |

| 18   | PGED2/RPB10/D+/CTED11/RB10                       |

| 19   | PGEC2/RPB11/D-/RB11                              |

| 20   | Vusb3v3                                          |

| 21   | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 22   | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 23   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 24   | AVss                                             |

| 25   | AVDD                                             |

| 26   | MCLR                                             |

| 27   | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 28   | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

1

Note 1:

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: Shaded pins are 5V tolerant.

TABLE 1-1: PINOUT I/O DESCRIPTIONS

|          |               | Pin Nu                            | mber <sup>(1)</sup> |                                 |             |                |                                                                                                                                                                                    |

|----------|---------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                        |

| AN0      | 27            | 2                                 | 33                  | 19                              | I           | Analog         | Analog input channels.                                                                                                                                                             |

| AN1      | 28            | 3                                 | 34                  | 20                              | I           | Analog         |                                                                                                                                                                                    |

| AN2      | 1             | 4                                 | 35                  | 21                              | I           | Analog         |                                                                                                                                                                                    |

| AN3      | 2             | 5                                 | 36                  | 22                              | I           | Analog         |                                                                                                                                                                                    |

| AN4      | 3             | 6                                 | 1                   | 23                              | I           | Analog         |                                                                                                                                                                                    |

| AN5      | 4             | 7                                 | 2                   | 24                              | I           | Analog         |                                                                                                                                                                                    |

| AN6      | _             | _                                 | 3                   | 25                              | I           | Analog         |                                                                                                                                                                                    |

| AN7      | _             | _                                 | 4                   | 26                              | ı           | Analog         |                                                                                                                                                                                    |

| AN8      | _             | _                                 | _                   | 27                              | ı           | Analog         |                                                                                                                                                                                    |

| AN9      | 23            | 26                                | 29                  | 15                              | ı           | Analog         |                                                                                                                                                                                    |

| AN10     | 22            | 25                                | 28                  | 14                              | ı           | Analog         |                                                                                                                                                                                    |

| AN11     | 21            | 24                                | 27                  | 11                              | ı           | Analog         |                                                                                                                                                                                    |

| A N 14 O | 20(2)         | 23 <sup>(2)</sup>                 | 26 <sup>(2)</sup>   | 10 <sup>(2)</sup>               |             | A I            |                                                                                                                                                                                    |

| AN12     | 20(2)         | 23(2)                             | 11 <sup>(3)</sup>   | 36 <sup>(3)</sup>               |             | Analog         |                                                                                                                                                                                    |

| CLKI     | 6             | 9                                 | 7                   | 30                              | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                             |

| CLKO     | 7             | 10                                | 8                   | 31                              | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1     | 6             | 9                                 | 7                   | 30                              | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                    |

| OSC2     | 7             | 10                                | 8                   | 31                              | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                           |

| SOSCI    | 8             | 11                                | 9                   | 33                              | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                     |

| SOSCO    | 9             | 12                                | 10                  | 34                              | 0           | _              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                    |

| REFCLKI  | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | Reference Input Clock                                                                                                                                                              |

| REFCLKO  | PPS           | PPS                               | PPS                 | PPS                             | 0           | _              | Reference Output Clock                                                                                                                                                             |

| IC1      | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | Capture Inputs 1-5                                                                                                                                                                 |

| IC2      | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             |                                                                                                                                                                                    |

| IC3      | PPS           | PPS                               | PPS                 | PPS                             | ı           | ST             |                                                                                                                                                                                    |

| IC4      | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             |                                                                                                                                                                                    |

| IC5      | PPS           | PPS                               | PPS                 | PPS                             | ı           | ST             |                                                                                                                                                                                    |

**Legend:** CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

P = Power

TTL = TTL input buffer

O = Output PPS = Peripheral Pin Select I = Input

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

— = N/A

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

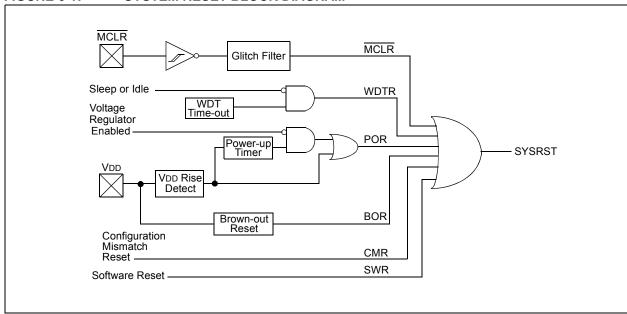

#### 6.0 RESETS

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- Power-on Reset (POR)

- Master Clear Reset pin (MCLR)

- · Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- · Brown-out Reset (BOR)

- · Configuration Mismatch Reset (CMR)

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

| 1XX/2X | X 28/36 | 5/44-PIN      | HAMII                | _ Y                        |                             |

|--------|---------|---------------|----------------------|----------------------------|-----------------------------|

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        |         |               |                      |                            |                             |

|        | 1XX/2X  | 1XX/2XX 28/36 | 1XX/2XX 28/36/44-PIN | 1XX/2XX 28/36/44-PIN FAMIL | 1XX/2XX 28/36/44-PIN FAMILY |

#### REGISTER 10-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the EVEN Buffer Descriptor banks

- 0 = Even/Odd buffer pointers are not Reset

- bit 0 USBEN: USB Module Enable bit (4)

- 1 = USB module and supporting circuitry is enabled0 = USB module and supporting circuitry is disabled

- **SOFEN:** SOF Enable bit<sup>(5)</sup>

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- **2:** All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

#### REGISTER 10-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | 1                 | _                 | _                 | _                 | _                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | -                 | 1                 |                   |                   | -                 |                  | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 7.0          | _                 | _                 | _                 | _                 | _                 |                   | FRMH<2:0>        |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-3 Unimplemented: Read as '0'

bit 2-0 FRMH<2:0>: The Upper 3 bits of the Frame Numbers bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### **REGISTER 10-15: U1TOK: USB TOKEN REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | -                 | -                 | -                   | -                 | 1                 | -                 | -                | _                |  |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | -                 | -                 | -                   | -                 | 1                 | -                 | -                | _                |  |

| 15:8         | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.6         | _                 | _                 | _                   | _                 | _                 | _                 | _                | _                |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   | PID<3             | 3:0> <sup>(1)</sup> |                   | EP<3:0>           |                   |                  |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR  $(1)^2$  = Bit is set  $(0)^2$  = Bit is cleared  $(0)^2$  = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-4 PID<3:0>: Token Type Indicator bits<sup>(1)</sup>

1101 = SETUP (TX) token type transaction 1001 = IN (RX) token type transaction

0001 = OUT (TX) token type transaction

Note: All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits

The four bit value must specify a valid endpoint.

Note 1: All other values are reserved and must not be used.

#### REGISTER 11-3: CNCONx: CHANGE NOTICE CONTROL FOR PORTX REGISTER (x = A, B, C)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | -                 | _                 |                   | _                 |                  | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 | _                 | _                | -                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ON: Change Notice (CN) Control ON bit

1 = CN is enabled0 = CN is disabled

bit 14 **Unimplemented:** Read as '0' bit 13 **SIDL:** Stop in Idle Control bit

1 = Idle mode halts CN operation0 = Idle does not affect CN operation

bit 12-0 Unimplemented: Read as '0'

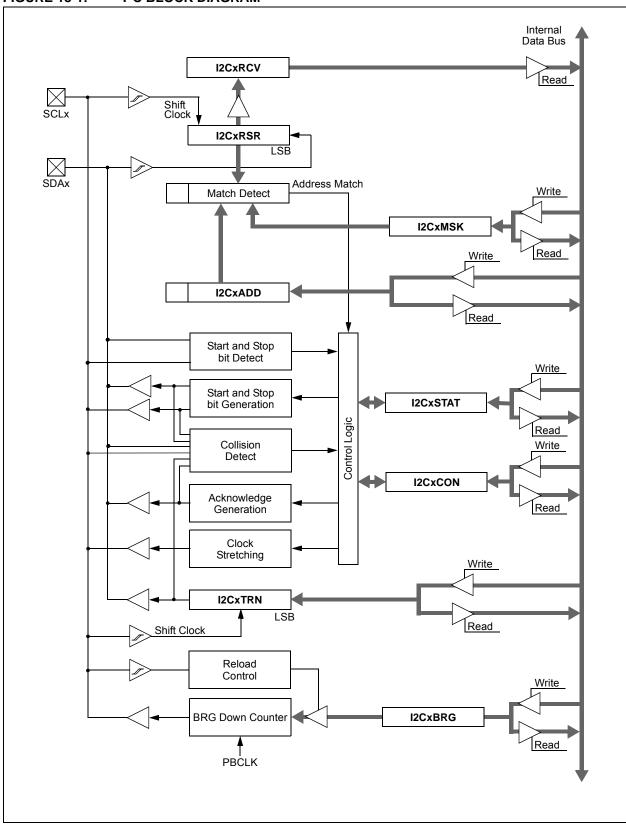

FIGURE 18-1: I<sup>2</sup>C BLOCK DIAGRAM

#### REGISTER 18-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER (CONTINUED)

- bit 7 **GCEN:** General Call Enable bit (when operating as I<sup>2</sup>C slave)

- 1 = Enable interrupt when a general call address is received in the I2CxRSR (module is enabled for reception)

- 0 = General call address is disabled

- bit 6 **STREN:** SCLx Clock Stretch Enable bit (when operating as I<sup>2</sup>C slave)

Used in conjunction with SCLREL bit.

- 1 = Enable software or receive clock stretching

- 0 = Disable software or receive clock stretching

- bit 5 **ACKDT:** Acknowledge Data bit (when operating as I<sup>2</sup>C master, applicable during master receive)

Value that is transmitted when the software initiates an Acknowledge sequence.

- 1 = Send a NACK during an Acknowledge sequence

- 0 = Send an ACK during an Acknowledge sequence

- bit 4 **ACKEN:** Acknowledge Sequence Enable bit (when operating as I<sup>2</sup>C master, applicable during master receive)

- 1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit. Hardware clear at end of master Acknowledge sequence.

- 0 = Acknowledge sequence not in progress

- bit 3 **RCEN:** Receive Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Enables Receive mode for I<sup>2</sup>C. Hardware clear at end of eighth bit of master receive data byte.

- 0 = Receive sequence not in progress

- bit 2 **PEN:** Stop Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.

- 0 = Stop condition not in progress

- bit 1 **RSEN:** Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence.

- 0 = Repeated Start condition not in progress

- bit 0 **SEN:** Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.

- 0 = Start condition not in progress

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## REGISTER 18-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED)

- bit 4 **P:** Stop bit

- 1 = Indicates that a Stop bit has been detected last

- 0 = Stop bit was not detected last

Hardware set or clear when Start, Repeated Start or Stop detected.

- bit 3 S: Start bit

- 1 = Indicates that a Start (or Repeated Start) bit has been detected last

- 0 = Start bit was not detected last

Hardware set or clear when Start, Repeated Start or Stop detected.

- bit 2  $R_W$ : Read/Write Information bit (when operating as  $I^2C$  slave)

- 1 = Read indicates data transfer is output from slave

- 0 = Write indicates data transfer is input to slave

Hardware set or clear after reception of I<sup>2</sup>C device address byte.

- bit 1 RBF: Receive Buffer Full Status bit

- 1 = Receive complete, I2CxRCV is full

- 0 = Receive not complete, I2CxRCV is empty

Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.

- bit 0 TBF: Transmit Buffer Full Status bit

- 1 = Transmit in progress, I2CxTRN is full

- 0 = Transmit complete, I2CxTRN is empty

Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.

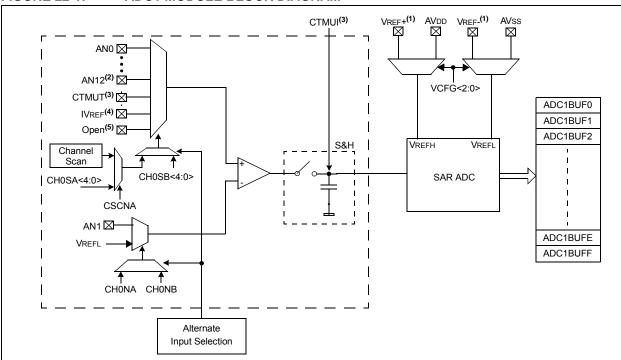

# 22.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- · Up to 1 Msps conversion speed

- · Up to 13 analog input pins

- · External voltage reference input pins

- One unipolar, differential Sample and Hold Amplifier (SHA)

- · Automatic Channel Scan mode

- Selectable conversion trigger source

- · 16-word conversion result buffer

- · Selectable buffer fill modes

- · Eight conversion result format options

- · Operation during Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. Figure 22-2 illustrates a block diagram of the ADC conversion clock period. The 10-bit ADC has up to 13 analog input pins, designated AN0-AN12. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

#### FIGURE 22-1: ADC1 MODULE BLOCK DIAGRAM

- Note 1: VREF+ and VREF- inputs can be multiplexed with other analog inputs.

- 2: AN8 is only available on 44-pin devices. AN6, AN7, and AN12 are not available on 28-pin devices.

- 3: Connected to the CTMU module. See Section 25.0 "Charge Time Measurement Unit (CTMU)" for more information.

- 4: Internal precision voltage reference (1.2V).

- 5: This selection is only used with CTMU capacitive and time measurement.

# DS60001168J-page 211

## **ADC Control Registers**

#### TABLE 22-1: ADC REGISTER MAP

| ess                         |                        | 4             |                                    |                                    |        |        |               |           |          | В                   | its       |                 |       |         |        |       |        |       |            |

|-----------------------------|------------------------|---------------|------------------------------------|------------------------------------|--------|--------|---------------|-----------|----------|---------------------|-----------|-----------------|-------|---------|--------|-------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range     | 31/15                              | 30/14                              | 29/13  | 28/12  | 27/11         | 26/10     | 25/9     | 24/8                | 23/7      | 22/6            | 21/5  | 20/4    | 19/3   | 18/2  | 17/1   | 16/0  | All Resets |

|                             | AD1CON1 <sup>(1)</sup> | 31:16         | _                                  | _                                  | _      | _      | _             | _         | _        | _                   | _         | _               | _     | _       | _      | _     | _      | _     | 0000       |

| 9000                        | ADTCONTO,              | 15:0          | ON                                 | _                                  | SIDL   | _      | _             |           | FORM<2:0 | >                   | ;         | SSRC<2:0>       | >     | CLRASAM | _      | ASAM  | SAMP   | DONE  | 0000       |

| 9010                        | AD1CON2 <sup>(1)</sup> | 31:16         | _                                  | _                                  | _      | _      | _             | _         | _        | _                   | _         | -               | _     | _       | _      | _     | _      | _     | 0000       |

| 3010                        | ADTOONZ                | 15:0          | ,                                  | VCFG<2:0>                          | '      | OFFCAL | CSCNA         |           |          | BUFS                | _         |                 | SMPI  | <3:0>   |        | BUFM  | ALTS   | 0000  |            |

| 9020                        | AD1CON3 <sup>(1)</sup> | 31:16         | _                                  | _                                  | _      | _      | -   -   -   - |           |          | _                   | _         | _               | _     | _       | _      | _     | _      | _     | 0000       |

| 0020                        | , 15 100110            | 15:0          | ADRC                               | _                                  | _      |        |               | SAMC<4:0> |          |                     |           |                 |       | ADCS    | S<7:0> |       |        |       | 0000       |

| 9040                        | AD1CHS <sup>(1)</sup>  | 31:16         | CH0NB                              | _                                  |        | _      |               | CH0SI     | 3<3:0>   | ı                   | CH0NA     | _               | _     | _       |        | CH0S/ | A<3:0> |       | 0000       |

|                             |                        | 15:0          |                                    | _                                  | _      | _      |               |           |          | _                   | _         |                 | _     | _       | _      |       |        | _     | 0000       |

| 9050                        | AD1CSSL <sup>(1)</sup> | 31:16         |                                    | _                                  | _      |        |               |           |          |                     | _         | 0000            |       |         |        |       |        |       |            |

|                             |                        | 15:0          | CSSL15                             | CSSL14                             | CSSL13 | CSSL12 | CSSL11        | CSSL10    | CSSL9    | CSSL8               | CSSL7     | CSSL6           | CSSL5 | CSSL4   | CSSL3  | CSSL2 | CSSL1  | CSSL0 | 0000       |

| 9070                        | ADC1BUF0               | 31:16         |                                    | ADC Result Word 0 (ADC1BUF0<31:0>) |        |        |               |           |          |                     |           |                 |       |         | 0000   |       |        |       |            |

|                             |                        | 15:0          |                                    |                                    |        |        |               |           |          |                     |           |                 |       | 0000    |        |       |        |       |            |

| 9080                        | ADC1BUF1               | 31:16<br>15:0 | ADC Result Word 1 (ADC1BUF1<31:0>) |                                    |        |        |               |           |          |                     |           |                 | 0000  |         |        |       |        |       |            |

|                             |                        | 31:16         |                                    |                                    |        |        |               |           |          |                     |           |                 |       |         |        |       |        |       | 0000       |

| 9090                        | ADC1BUF2               | 15:0          |                                    |                                    |        |        |               |           | ADC Res  | sult Word 2         | (ADC1BUF  | 2<31:0>)        |       |         |        |       |        |       | 0000       |

|                             |                        | 31:16         |                                    |                                    |        |        |               |           |          |                     |           |                 |       |         |        |       |        |       | 0000       |

| 90A0                        | ADC1BUF3               | 15:0          |                                    |                                    |        |        |               |           | ADC Res  | sult Word 3         | (ADC1BUF  | 3<31:0>)        |       |         |        |       |        |       | 0000       |

|                             |                        | 31:16         |                                    |                                    |        |        |               |           |          |                     |           |                 |       |         |        |       |        |       | 0000       |

| 90B0                        | ADC1BUF4               | 15:0          |                                    |                                    |        |        |               |           | ADC Res  | sult Word 4         | (ADC1BUF  | 4<31:0>)        |       |         |        |       |        |       | 0000       |

|                             |                        | 31:16         |                                    |                                    |        |        |               |           |          |                     |           |                 |       |         |        |       |        |       | 0000       |

| 90C0                        | ADC1BUF5               | 15:0          |                                    |                                    |        |        |               |           | ADC Res  | sult Word 5         | (ADC1BUF  | 5<31:0>)        |       |         |        |       |        |       | 0000       |

| 0000                        | ADO4DUEC               | 31:16         |                                    |                                    |        |        |               |           | 4 D.C. D |                     | (ADC4DUE  | 0 -104 -05 \    |       |         |        |       |        |       | 0000       |

| 9000                        | ADC1BUF6               | 15:0          |                                    |                                    |        |        |               |           | ADC Res  | sult Word 6         | (ADC1BUF  | 6<31:0>)        |       |         |        |       |        |       | 0000       |

| 00E0                        | ADC1BUF7               | 31:16         |                                    |                                    |        |        |               |           | ADC Box  | sult Word 7         | (ADC1DLIE | 7/21:0>\        |       |         |        |       |        |       | 0000       |

| 9000                        | ADC IBUF1              | 15:0          |                                    |                                    |        |        |               |           | ADC RE   | suit vvoiu <i>i</i> | (ADC IBUF | /<31.02)        |       |         |        |       |        |       | 0000       |

| 90E0                        | ADC1BUF8               | 31:16         |                                    |                                    |        |        |               |           | ADC Per  | sult Word 8         | (ADC1BLIE | 8<31:0>1        |       |         |        |       |        |       | 0000       |

| 901.0                       | ADC IDOF0              | 15:0          |                                    |                                    |        |        |               |           | ADC RE   | Suit VVOIU O        |           | 0 - 0 1 . 0 ~ ) |       |         |        |       |        |       | 0000       |

| 9100                        | ADC1BUF9               | 31:16         |                                    |                                    |        |        | ·             |           | ADC Res  | sult Word 9         | (ADC1BLIE | 9<31:0>1        |       |         |        |       |        |       | 0000       |

| 3100                        | , .50 1501 9           | 15:0          |                                    | ADC Result Word 9 (ADC1BUF9<31:0>) |        |        |               |           |          |                     |           |                 |       | 0000    |        |       |        |       |            |

| 9110                        | ADC1BUFA               | 31:16         |                                    | ADC Result Word A (ADC1BUFA<31:0>) |        |        |               |           |          |                     |           |                 |       |         |        |       |        |       |            |

|                             |                        | 15:0          |                                    |                                    |        |        |               |           | 0        |                     | ,         | ,               |       |         |        |       |        |       | 0000       |

**PIC32MX1XX/2XX 28/36/44-PIN FAMILY**

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

This register has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for details. Note 1:

#### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 31.24        | EDG1MOD           | EDG1POL           |                   | EDG1S               |                   | EDG2STAT          | EDG1STAT               |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | U-0                    | U-0              |

| 23.10        | EDG2MOD           | EDG2POL           |                   | EDG2S               | _                 | _                 |                        |                  |

| 15:8         | R/W-0             | U-0               | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 15.6         | ON                | _                 | CTMUSIDL          | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN          | IDISSEN <sup>(2)</sup> | CTTRIG           |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 7.0          |                   |                   | IRNG<1:0>         |                     |                   |                   |                        |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 EDG1MOD: Edge1 Edge Sampling Select bit

1 = Input is edge-sensitive

0 = Input is level-sensitive

bit 30 EDG1POL: Edge 1 Polarity Select bit

1 = Edge1 programmed for a positive edge response

0 = Edge1 programmed for a negative edge response

bit 29-26 EDG1SEL<3:0>: Edge 1 Source Select bits

1111 = C3OUT pin is selected

1110 = C2OUT pin is selected

1101 = C1OUT pin is selected

1100 = IC3 Capture Event is selected

1011 = IC2 Capture Event is selected

1010 = IC1 Capture Event is selected

1001 = CTED8 pin is selected

1000 = CTED7 pin is selected

0111 = CTED6 pin is selected

0110 = CTED5 pin is selected

0101 = CTED4 pin is selected

0100 = CTED3 pin is selected

0011 = CTED1 pin is selected

0010 = CTED2 pin is selected

0001 = OC1 Compare Event is selected 0000 = Timer1 Event is selected

bit 25 EDG2STAT: Edge2 Status bit

Indicates the status of Edge2 and can be written to control edge source

1 = Edge2 has occurred

0 = Edge2 has not occurred

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 30-41) in **Section 30.0 "Electrical Characteristics"** for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

#### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

bit 24 EDG1STAT: Edge1 Status bit

Indicates the status of Edge1 and can be written to control edge source

- 1 = Edge1 has occurred

- 0 = Edge1 has not occurred

- bit 23 EDG2MOD: Edge2 Edge Sampling Select bit

- 1 = Input is edge-sensitive

- 0 = Input is level-sensitive

- bit 22 EDG2POL: Edge 2 Polarity Select bit

- 1 = Edge2 programmed for a positive edge response

- 0 = Edge2 programmed for a negative edge response

- bit 21-18 EDG2SEL<3:0>: Edge 2 Source Select bits

- 1111 = C3OUT pin is selected

- 1110 = C2OUT pin is selected

- 1101 = C1OUT pin is selected

- 1100 = PBCLK clock is selected

- 1011 = IC3 Capture Event is selected

- 1010 = IC2 Capture Event is selected

- 1001 = IC1 Capture Event is selected

- 1000 = CTED13 pin is selected

- 0111 = CTED12 pin is selected

- 0110 = CTED11 pin is selected

- 0101 = CTED10 pin is selected

- 0100 = CTED9 pin is selected

- 0011 = CTED1 pin is selected

- 0010 = CTED2 pin is selected

- 0001 = OC1 Compare Event is selected

- 0000 = Timer1 Event is selected

- bit 17-16 Unimplemented: Read as '0'

- bit 15 ON: ON Enable bit

- 1 = Module is enabled

- 0 = Module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **CTMUSIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- bit 12 **TGEN:** Time Generation Enable bit<sup>(1)</sup>

- 1 = Enables edge delay generation

- 0 = Disables edge delay generation

- bit 11 EDGEN: Edge Enable bit

- 1 = Edges are not blocked

- 0 = Edges are blocked

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 30-41) in **Section 30.0 "Electrical Characteristics"** for current values.

- **4:** This bit setting is not available for the CTMU temperature diode.

#### REGISTER 27-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 18-10 PWP<8:0>: Program Flash Write-Protect bits(3)

```

Prevents selected program Flash memory pages from being modified during code execution.

111111111 = Disabled

111111110 = Memory below 0x0400 address is write-protected

111111101 = Memory below 0x0800 address is write-protected

111111100 = Memory below 0x0C00 address is write-protected

111111011 = Memory below 0x1000 (4K) address is write-protected

111111010 = Memory below 0x1400 address is write-protected

111111001 = Memory below 0x1800 address is write-protected

111111000 = Memory below 0x1C00 address is write-protected

111110111 = Memory below 0x2000 (8K) address is write-protected

111110110 = Memory below 0x2400 address is write-protected

111110101 = Memory below 0x2800 address is write-protected

111110100 = Memory below 0x2C00 address is write-protected

111110011 = Memory below 0x3000 address is write-protected

111110010 = Memory below 0x3400 address is write-protected

111110001 = Memory below 0x3800 address is write-protected

111110000 = Memory below 0x3C00 address is write-protected

111101111 = Memory below 0x4000 (16K) address is write-protected

110111111 = Memory below 0x10000 (64K) address is write-protected

101111111 = Memory below 0x20000 (128K) address is write-protected

011111111 = Memory below 0x40000 (256K) address is write-protected

000000000 = All possible memory is write-protected

Reserved: Write '1'

ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits(2)

11 = PGEC1/PGED1 pair is used

10 = PGEC2/PGED2 pair is used

01 = PGEC3/PGED3 pair is used

00 = PGEC4/PGED4 pair is used<sup>(2)</sup>

JTAGEN: JTAG Enable bit(1)

1 = JTAG is enabled

0 = JTAG is disabled

DEBUG<1:0>: Background Debugger Enable bits (forced to '11' if code-protect is enabled)

1x = Debugger is disabled

0x = Debugger is enabled

2: The PGEC4/PGED4 pin pair is not available on all devices. Refer to the "Pin Diagrams" section for

```

- Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

- availability.

- 3: The PWP<8:7> bits are only available on devices with 256 KB Flash.

bit 9-5

bit 4-3

bit 2

bit 1-0

#### TABLE 30-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHA                                | RACTERIS               | TICS    |       | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                                        |  |  |  |  |  |  |  |

|---------------------------------------|------------------------|---------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|--|--|--|--|

| Param.<br>No.                         | Typical <sup>(2)</sup> | Max.    | Units | Units Conditions                                                                                                                                                                                                                                  |                                        |  |  |  |  |  |  |  |

| Power-Down Current (IPD) (Notes 1, 5) |                        |         |       |                                                                                                                                                                                                                                                   |                                        |  |  |  |  |  |  |  |

| DC40k                                 | 44                     | 70      | μА    | -40°C                                                                                                                                                                                                                                             |                                        |  |  |  |  |  |  |  |

| DC40I                                 | 44                     | 70      | μА    | +25°C                                                                                                                                                                                                                                             | Base Power-Down Current                |  |  |  |  |  |  |  |

| DC40n                                 | 168                    | 259     | μА    | +85°C                                                                                                                                                                                                                                             | Base Power-Down Current                |  |  |  |  |  |  |  |

| DC40m                                 | 335                    | 536     | μA    | +105°C                                                                                                                                                                                                                                            |                                        |  |  |  |  |  |  |  |

| Module                                | Differential           | Current |       |                                                                                                                                                                                                                                                   | •                                      |  |  |  |  |  |  |  |

| DC41e                                 | 5                      | 20      | μА    | 3.6V                                                                                                                                                                                                                                              | Watchdog Timer Current: ΔIWDT (Note 3) |  |  |  |  |  |  |  |

| DC42e                                 | 23                     | 50      | μА    | 3.6V RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3                                                                                                                                                                                               |                                        |  |  |  |  |  |  |  |

| DC43d                                 | 1000                   | 1100    | μА    | 3.6V                                                                                                                                                                                                                                              | ADC: ∆IADC (Notes 3,4)                 |  |  |  |  |  |  |  |

**Note 1:** The test conditions for IPD current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

- · WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- · RTCC and JTAG are disabled

- **2:** Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- **4:** Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

TABLE 30-14: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHA        | RACTERIS | STICS                                                       | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |      |                    |       |                                                                 |  |  |  |

|---------------|----------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-------|-----------------------------------------------------------------|--|--|--|

| Param.<br>No. | Symbol   | Characteristics                                             | Min.                                                                                                                                                                                                                                           | Тур. | Max.               | Units | Comments                                                        |  |  |  |

| D312          | TSET     | Internal 4-bit DAC<br>Comparator Reference<br>Settling time | _                                                                                                                                                                                                                                              | _    | 10                 | μs    | See Note 1                                                      |  |  |  |

| D313          | DACREFH  |                                                             | AVss                                                                                                                                                                                                                                           | _    | AVDD               | V     | CVRSRC with CVRSS = 0                                           |  |  |  |

|               |          | Reference Range                                             | VREF-                                                                                                                                                                                                                                          | _    | VREF+              | V     | CVRSRC with CVRSS = 1                                           |  |  |  |

| D314          | DVREF    | CVREF Programmable Output Range                             | 0                                                                                                                                                                                                                                              | -    | 0.625 x<br>DACREFH | V     | 0 to 0.625 DACREFH with DACREFH/24 step size                    |  |  |  |

|               |          |                                                             | 0.25 x<br>DACREFH                                                                                                                                                                                                                              | _    | 0.719 x<br>DACREFH | V     | 0.25 x DACREFH to 0.719<br>DACREFH with<br>DACREFH/32 step size |  |  |  |

| D315          | DACRES   | Resolution                                                  | _                                                                                                                                                                                                                                              | _    | DACREFH/24         | _     | CVRCON <cvrr> = 1</cvrr>                                        |  |  |  |

|               |          |                                                             | _                                                                                                                                                                                                                                              | _    | DACREFH/32         | _     | CVRCON <cvrr> = 0</cvrr>                                        |  |  |  |

| D316          | DACACC   | Absolute Accuracy <sup>(2)</sup>                            | _                                                                                                                                                                                                                                              | _    | 1/4                | LSB   | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                         |  |  |  |

|               |          |                                                             | _                                                                                                                                                                                                                                              | _    | 1/2                | LSB   | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                         |  |  |  |

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

#### **TABLE 30-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS**

| DC CHARACTERISTICS |        |                                 | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |         |      |       |                                                                                           |

|--------------------|--------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|-------------------------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                 | Min.                                                                                                                                                                                                                                           | Typical | Max. | Units | Comments                                                                                  |

| D321               | CEFC   | External Filter Capacitor Value | 8                                                                                                                                                                                                                                              | 10      |      | μF    | Capacitor must be low series resistance (1 ohm). Typical voltage on the VCAP pin is 1.8V. |

<sup>2:</sup> These parameters are characterized but not tested.

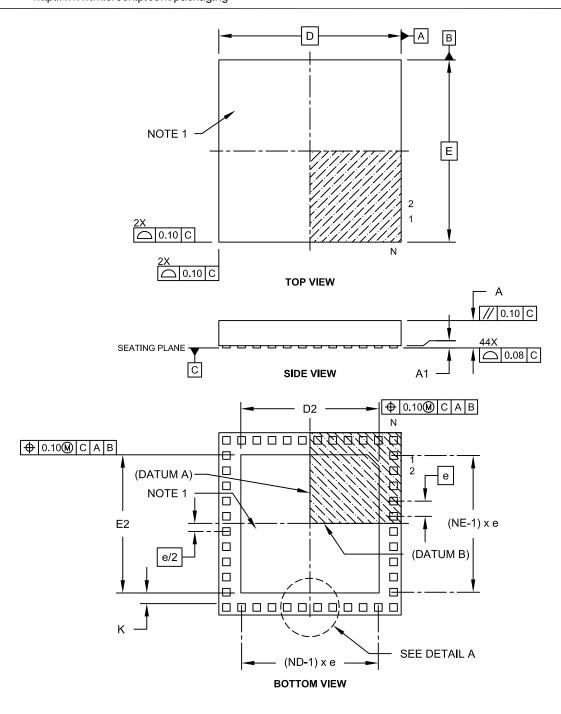

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-157C Sheet 1 of 2

#### **Revision G (April 2015)**

This revision includes the addition of the following devices:

- PIC32MX130F256B

- PIC32MX230F256B

- PIC32MX130F256D

- PIC32MX230F256D

The title of the document was updated to avoid confusion with the PIC32MX1XX/2XX/5XX 64/100-pin Family data sheet.

All peripheral SFR maps have been relocated from the Memory chapter to their respective peripheral chapters.

In addition, this revision includes the following major changes as described in Table A-6, as well as minor updates to text and formatting, which were incorporated throughout the document.

#### TABLE A-6: MAJOR SECTION UPDATES

| Section                                                                                                                  | Update Description                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32-bit Microcontrollers (up to 256 KB Flash and 64 KB SRAM) with Audio and Graphics Interfaces, USB, and Advanced Analog | Added new devices to the family features (see Table 1 and Table 2).  Updated pin diagrams to include new devices (see Pin Diagrams).                                                      |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                 | Updated these sections: 2.2 "Decoupling Capacitors", 2.3 "Capacitor on Internal Voltage Regulator (VCAP)", 2.4 "Master Clear (MCLR) Pin", 2.8.1 "Crystal Oscillator Design Consideration" |

| 4.0 "Memory Organization"                                                                                                | Added Memory Map for new devices (see Figure 4-6).                                                                                                                                        |

| 14.0 "Watchdog Timer (WDT)"                                                                                              | New chapter created from content previously located in the Special Features chapter.                                                                                                      |

| 30.0 "Electrical Characteristics"                                                                                        | Removed parameter D312 (TSET) from the Comparator Specifications (see Table 30-12).                                                                                                       |

|                                                                                                                          | Added the Comparator Voltage Reference Specifications (see Table 30-13).                                                                                                                  |

|                                                                                                                          | Updated Table 30-12.                                                                                                                                                                      |

#### **Revision H (July 2015)**

This revision includes the following major changes as described in Table A-7, as well as minor updates to text and formatting, which were incorporated throughout the document.

#### TABLE A-7: MAJOR SECTION UPDATES

| Section                                                  | Update Description                                                                            |  |  |  |  |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs" | Section 2.9 "Sosc Design Recommendation" was removed.                                         |  |  |  |  |

| 8.0 "Oscillator Configuration"                           | The Primary Oscillator (Posc) logic in the Oscillator diagram was updated (see Figure 8-1).   |  |  |  |  |

| 30.0 "Electrical Characteristics"                        | The Power-Down Current (IPD) DC Characteristics parameter DC40k was updated (see Table 30-7). |  |  |  |  |

|                                                          | Table 30-9: "DC Characteristics: I/O Pin Input Injection current Specifications" was added.   |  |  |  |  |