### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Decalis                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 50MHz                                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 32KB (32K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                    |

| Supplier Device Package    | 28-SOIC                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f032bt-50i-so |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

|                     |      |                                    |                  | Rem             | appab                                  | le Pe | riphe                | erals                              |                    |                     |                  |     | (                                        |      | ls)                          |      |          |      |                                 |

|---------------------|------|------------------------------------|------------------|-----------------|----------------------------------------|-------|----------------------|------------------------------------|--------------------|---------------------|------------------|-----|------------------------------------------|------|------------------------------|------|----------|------|---------------------------------|

| Device              | Pins | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers <sup>(2)</sup> /Capture/Compare | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | Analog Comparators | USB On-The-Go (OTG) | I <sup>2</sup> C | dMq | DMA Channels<br>(Programmable/Dedicated) | CTMU | 10-bit 1 Msps ADC (Channels) | RTCC | I/O Pins | JTAG | Packages                        |

| PIC32MX210F016B     | 28   | 16+3                               | 4                | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX210F016C     | 36   | 16+3                               | 4                | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 25       | Y    | VTLA                            |

| PIC32MX210F016D     | 44   | 16+3                               | 4                | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX220F032B     | 28   | 32+3                               | 8                | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX220F032C     | 36   | 32+3                               | 8                | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA                            |

| PIC32MX220F032D     | 44   | 32+3                               | 8                | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX230F064B     | 28   | 64+3                               | 16               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F064C     | 36   | 64+3                               | 16               | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA                            |

| PIC32MX230F064D     | 44   | 64+3                               | 16               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX250F128B     | 28   | 128+3                              | 32               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX250F128C     | 36   | 128+3                              | 32               | 23              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 12                           | Y    | 23       | Y    | VTLA<br>VTLA,                   |

| PIC32MX250F128D     | 44   | 128+3                              | 32               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | TQFP,<br>QFN                    |

| PIC32MX230F256B     | 28   | 256+3                              | 16               | 20              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX230F256D     | 44   | 256+3                              | 16               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256B     | 28   | 256+3                              | 64               | 19              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 9                            | Y    | 19       | Y    | SOIC,<br>SSOP,<br>SPDIP,<br>QFN |

| PIC32MX270F256D     | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

| PIC32MX270F256DB(4) | 44   | 256+3                              | 64               | 31              | 5/5/5                                  | 2     | 2                    | 5                                  | 3                  | Y                   | 2                | Y   | 4/2                                      | Y    | 13                           | Y    | 33       | Y    | VTLA,<br>TQFP,<br>QFN           |

### TABLE 2: PIC32MX2XX 28/36/44-PIN USB FAMILY FEATURES

Note 1: This device features 3 KB of boot Flash memory.

**2:** Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

4: This PIC32 device is targeted to specific audio software packages that are tracked for licensing royalty purposes. All peripherals and electrical characteristics are identical to their corresponding base part numbers.

### TABLE 5: PIN NAMES FOR 28-PIN GENERAL PURPOSE DEVICES

### 28-PIN QFN (TOP VIEW)<sup>(1,2,3.4)</sup>

PIC32MX110F016B PIC32MX120F032B PIC32MX130F064B PIC32MX130F256B PIC32MX150F128B PIC32MX170F256B

28

1

| Pin # | Full Pin Name                         | Pin # | Full Pin Name                                  |

|-------|---------------------------------------|-------|------------------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0  | 15    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1 | 16    | Vss                                            |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2  | 17    | VCAP                                           |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3    | 18    | PGED2/RPB10/CTED11/PMD2/RB10                   |

| 5     | Vss                                   | 19    | PGEC2/TMS/RPB11/PMD1/RB11                      |

| 6     | OSC1/CLKI/RPA2/RA2                    | 20    | AN12/PMD0/RB12                                 |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3               | 21    | AN11/RPB13/CTPLS/PMRD/RB13                     |

| 8     | SOSCI/RPB4/RB4                        | 22    | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4        | 23    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

| 10    | Vdd                                   | 24    | AVss                                           |

| 11    | PGED3/RPB5/PMD7/RB5                   | 25    | AVDD                                           |

| 12    | PGEC3/RPB6/PMD6/RB6                   | 26    | MCLR                                           |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7          | 27    | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0          |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8         | 28    | VREF-/CVREF-/AN1/RPA1/CTED2/RA1                |

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: Shaded pins are 5V tolerant.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|-----------------------|------------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                    | —                     | —                      |                   | _                |                  |

| 00.40        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                    | —                     | —                      | —                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0                   | R-0                    | U-0               | U-0              | U-0              |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | LVDSTAT <sup>(1)</sup> |                   | _                |                  |

| 7.0          | U-0               | U-0               | U-0                  | U-0                   | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 |                      | —                     |                        | NVMOF             | P<3:0>           |                  |

|              |                   |                   |                      |                       |                        |                   |                  |                  |

### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re- | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

| 011 31-10           | Unimplemented. Read as 0                                                                                              |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|

| bit 15              | WR: Write Control bit                                                                                                 |

|                     | This bit is writable when WREN = 1 and the unlock sequence is followed.                                               |

|                     | 1 = Initiate a Flash operation. Hardware clears this bit when the operation completes                                 |

|                     | 0 = Flash operation is complete or inactive                                                                           |

| bit 14              | WREN: Write Enable bit                                                                                                |

|                     | This is the only bit in this register reset by a device Reset.                                                        |

|                     | 1 = Enable writes to WR bit and enables LVD circuit                                                                   |

|                     | 0 = Disable writes to WR bit and disables LVD circuit                                                                 |

| bit 13              | WRERR: Write Error bit <sup>(1)</sup>                                                                                 |

|                     | This bit is read-only and is automatically set by hardware.                                                           |

|                     | 1 = Program or erase sequence did not complete successfully                                                           |

|                     | 0 = Program or erase sequence completed normally                                                                      |

| bit 12              | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(1)</sup>                                     |

|                     | This bit is read-only and is automatically set by hardware.                                                           |

|                     | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                                                  |

|                     | 0 = Voltage level is acceptable for programming                                                                       |

| bit 11              | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(1)</sup>                                   |

|                     | This bit is read-only and is automatically set and cleared by the hardware.                                           |

|                     | 1 = Low-voltage event is active                                                                                       |

| hit 10 1            | 0 = Low-voltage event is not active                                                                                   |

| bit 10-4<br>bit 3-0 | Unimplemented: Read as '0'                                                                                            |

| 0-6 110             | <b>NVMOP&lt;3:0&gt;:</b> NVM Operation bits<br>These bits are writable when WREN = 0.                                 |

|                     |                                                                                                                       |

|                     | 1111 = Reserved                                                                                                       |

|                     | •                                                                                                                     |

|                     | •                                                                                                                     |

|                     | 0111 = Reserved<br>0110 = No operation                                                                                |

|                     | 0101 = Program Flash Memory (PFM) erase operation: erases PFM, if all pages are not write-protected                   |

|                     | 0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected                            |

|                     | 0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected                          |

|                     | 0010 = No operation                                                                                                   |

|                     | 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected<br>0000 = No operation |

|                     |                                                                                                                       |

**Note 1:** This bit is cleared by setting NVMOP == `b0000, and initiating a Flash operation (i.e., WR).

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 |                   | _                 | _                 | —                 | —                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | _                 | _                 |                   | _                 | _                 | _                 | —                | —                |  |  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | —                 | _                 | —                 | MVEC              | _                 |                   | TPC<2:0>         |                  |  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | _                 | _                 | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |  |  |

### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

### Legend:

| Logona.                           |                  |                                    |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

### bit 15-13 Unimplemented: Read as '0'

- bit 12 MVEC: Multi Vector Configuration bit

- 1 = Interrupt controller configured for Multi-vectored mode

- 0 = Interrupt controller configured for Single-vectored mode

- bit 11 Unimplemented: Read as '0'

- bit 10-8 **TPC<2:0>:** Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer

- 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

- 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

- 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

- 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

### bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------------|-------------------|-------------------|-------------------|---------------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0                       | U-0              |  |  |

| 31:24        | _                 | _                 | _                       | —                 | _                 |                   | _                         | —                |  |  |

| 23:16        | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0                       | U-0              |  |  |

| 23.10        | —                 | —                 | —                       | —                 | —                 | —                 | —                         | -                |  |  |

| 45.0         | U-0               | U-0               | U-0                     | U-0               | U-0               | R/W-0             | R/W-0                     | R/W-0            |  |  |

| 15:8         | —                 | _                 |                         | _                 | _                 | S                 | SRIPL<2:0> <sup>(1)</sup> |                  |  |  |

| 7.0          | U-0               | U-0               | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0            |  |  |

| 7:0          | _                 | _                 | VEC<5:0> <sup>(1)</sup> |                   |                   |                   |                           |                  |  |  |

### REGISTER 7-2: INTSTAT: INTERRUPT STATUS REGISTER

### Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-11 Unimplemented: Read as '0'

- bit 10-8 SRIPL<2:0>: Requested Priority Level bits<sup>(1)</sup>

- 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

| D:/          | Dit               | Dit               | D:                | Dit               | D'i               | D:                | Dir              | Dit              |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        |                   | IPTMR<31:24>      |                   |                   |                   |                   |                  |                  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | IPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         | IPTMR<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          | IPTMR<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

### REGISTER 7-3: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 31-0 **IPTMR<31:0>:** Interrupt Proximity Timer Reload bits Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|----------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0                  | R/W-y             | R/W-y             | R/W-y             | R/W-0                 | R/W-0            | R/W-1            |  |  |

| 31:24        | —                 | —                    | Р                 | LLODIV<2:0        | <b>`</b>          | FRCDIV<2:0>           |                  |                  |  |  |

| 00.40        | U-0               | R-0                  | R-1               | R/W-y             | R/W-y             | R/W-y                 | R/W-y            | R/W-y            |  |  |

| 23:16        | —                 | SOSCRDY              | PBDIVRDY          | PBDI              | /<1:0>            | PLLMULT<2:0>          |                  |                  |  |  |

| 45.0         | U-0               | R-0                  | R-0               | R-0               | U-0               | R/W-y                 | R/W-y            | R/W-y            |  |  |

| 15:8         | —                 |                      | COSC<2:0>         |                   | —                 | NOSC<2:0>             |                  |                  |  |  |

| 7:0          | R/W-0             | R-0                  | R-0               | R/W-0             | R/W-0             | R/W-0                 | R/W-y            | R/W-0            |  |  |

| 7:0          | CLKLOCK           | ULOCK <sup>(1)</sup> | SLOCK             | SLPEN             | CF                | UFRCEN <sup>(1)</sup> | SOSCEN           | OSWEN            |  |  |

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| Legend:         y = Value set from Configuration bits on POR |                  |                      |                    |  |  |  |

|--------------------------------------------------------------|------------------|----------------------|--------------------|--|--|--|

| R = Readable bit                                             | W = Writable bit | U = Unimplemented bi | t, read as '0'     |  |  |  |

| -n = Value at POR                                            | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

### bit 31-30 **Unimplemented:** Read as '0'

### bit 29-27 **PLLODIV<2:0>:** Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

- 1 = The Secondary Oscillator is running and is stable

- 0 = The Secondary Oscillator is still warming up or is turned off

- bit 21 **PBDIVRDY:** Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

Note 1: This bit is only available on PIC32MX2XX devices.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

- bit 18-16 **PLLMULT<2:0>:** Phase-Locked Loop (PLL) Multiplier bits

- 111 = Clock is multiplied by 24

- 110 = Clock is multiplied by 21

- 101 = Clock is multiplied by 20

- 100 = Clock is multiplied by 19

- 011 = Clock is multiplied by 18

- 010 = Clock is multiplied by 17

- 001 = Clock is multiplied by 16

- 000 =Clock is multiplied by 15

- bit 15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (OSCCON<26:24>)

- 110 = Internal Fast RC (FRC) Oscillator divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (Posc) (XT, HS or EC)

- 001 = Internal Fast RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast RC (FRC) Oscillator

- bit 11 Unimplemented: Read as '0'

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits

- 111 = Internal Fast RC Oscillator (FRC) divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC Oscillator (FRC) divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (XT, HS or EC)

- 001 = Internal Fast Internal RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast Internal RC Oscillator (FRC)

On Reset, these bits are set to the value of the FNOSC Configuration bits (DEVCFG1<2:0>).

bit 7 CLKLOCK: Clock Selection Lock Enable bit

If clock switching and monitoring is disabled (FCKSM<1:0> = 1x):

- 1 = Clock and PLL selections are locked

- 0 = Clock and PLL selections are not locked and may be modified

If clock switching and monitoring is enabled (FCKSM<1:0> = 0x):

Clock and PLL selections are never locked and may be modified.

- bit 6 ULOCK: USB PLL Lock Status bit<sup>(1)</sup>

- 1 = The USB PLL module is in lock or USB PLL module start-up timer is satisfied

- 0 =The USB PLL module is out of lock or USB PLL module start-up timer is in progress or the USB PLL is disabled

- bit 5 SLOCK: PLL Lock Status bit

- 1 = The PLL module is in lock or PLL module start-up timer is satisfied

- 0 = The PLL module is out of lock, the PLL start-up timer is running, or the PLL is disabled

- bit 4 SLPEN: Sleep Mode Enable bit

- 1 = The device will enter Sleep mode when a WAIT instruction is executed

- 0 = The device will enter Idle mode when a WAIT instruction is executed

- **Note 1:** This bit is only available on PIC32MX2XX devices.

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | —                 | _                 | —                 | —                 | _                 | _                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | _                 | —                 | —                 | —                 | _                | —                |  |  |  |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | ON <sup>(1)</sup> | —                 | _                 | SUSPEND           | DMABUSY           | _                 | _                | —                |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

### REGISTER 9-1: DMACON: DMA CONTROLLER CONTROL REGISTER

### Legend:

| 0                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: DMA On bit<sup>(1)</sup>

- 1 = DMA module is enabled

- 0 = DMA module is disabled

- bit 14-13 **Unimplemented:** Read as '0'

- bit 12 SUSPEND: DMA Suspend bit

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

### bit 11 DMABUSY: DMA Module Busy bit

- 1 = DMA module is active

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

### TABLE 11-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection       |

|--------------|----------|-------------|---------------------------------------------|

| RPA0         | RPA0R    | RPA0R<3:0>  | 0000 = No Connect                           |

| RPB3         | RPB3R    | RPB3R<3:0>  | 0001 = <u>U1TX</u><br>0010 = <u>U2RTS</u>   |

| RPB4         | RPB4R    | RPB4R<3:0>  | 0011 = SS1                                  |

| RPB15        | RPB15R   | RPB15R<3:0> |                                             |

| RPB7         | RPB7R    | RPB7R<3:0>  | 0110 = Reserved<br>0111 = C2OUT             |

| RPC7         | RPC7R    | RPC7R<3:0>  | 1000 = Reserved                             |

| RPC0         | RPC0R    | RPC0R<3:0>  | •                                           |

| RPC5         | RPC5R    | RPC5R<3:0>  | •<br>1111 = Reserved                        |

| RPA1         | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                           |

| RPB5         | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPB1         | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                 |

| RPB11        | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                   |

| RPB8         | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                             |

| RPA8         | RPA8R    | RPA8R<3:0>  |                                             |

| RPC8         | RPC8R    | RPC8R<3:0>  | •                                           |

| RPA9         | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                             |

| RPA2         | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                           |

| RPB6         | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPA4         | RPA4R    | RPA4R<3:0>  | 0011 = SDO1<br>0100 = SDO2                  |

| RPB13        | RPB13R   | RPB13R<3:0> | 0101 <b>= OC4</b>                           |

| RPB2         | RPB2R    | RPB2R<3:0>  |                                             |

| RPC6         | RPC6R    | RPC6R<3:0>  | 1000 = Reserved                             |

| RPC1         | RPC1R    | RPC1R<3:0>  |                                             |

| RPC3         | RPC3R    | RPC3R<3:0>  | 1111 = Reserved                             |

| RPA3         | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                           |

| RPB14        | RPB14R   | RPB14R<3:0> |                                             |

| RPB0         | RPB0R    | RPB0R<3:0>  | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |

| RPB10        | RPB10R   | RPB10R<3:0> | 0101 <b>= OC3</b>                           |

| RPB9         | RPB9R    | RPB9R<3:0>  |                                             |

| RPC9         | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                             |

| RPC2         | RPC2R    | RPC2R<3:0>  |                                             |

| RPC4         | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                             |

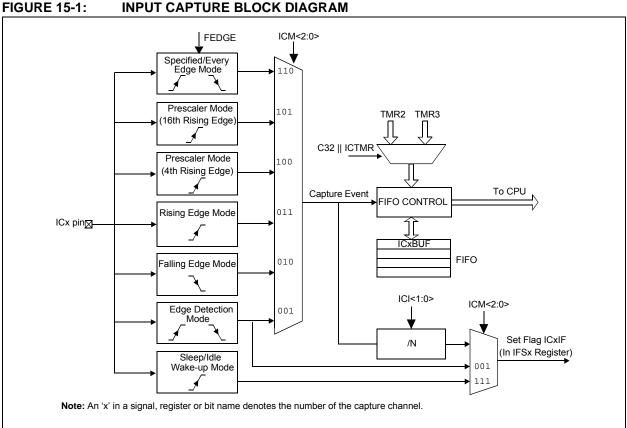

### **INPUT CAPTURE** 15.0

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- · Simple capture event modes:

- Capture timer value on every rising and falling edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- · Device wake-up from capture pin during Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values (interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled)

- · Input capture can also be used to provide additional sources of external interrupts

Figure 15-1 illustrates a general block diagram of the Input Capture module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |  |  |  |

| 31:24        |                   | _                 | _                 | _                 | —                 | _                 | _                | ADM_EN           |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | ADDR<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-1              |  |  |  |

| 15:8         | UTXISE            | L<1:0>            | UTXINV            | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R-1               | R-0               | R-0               | R/W-0            | R-0              |  |  |  |

| 7:0          | URXISE            | L<1:0>            | ADDEN             | RIDLE             | PERR              | FERR              | OERR             | URXDA            |  |  |  |

### REGISTER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

### Legend:

| 0                                 |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-25 Unimplemented: Read as '0'

- bit 24 ADM\_EN: Automatic Address Detect Mode Enable bit

- 1 = Automatic Address Detect mode is enabled

- 0 = Automatic Address Detect mode is disabled

- bit 23-16 ADDR<7:0>: Automatic Address Mask bits

When the ADM\_EN bit is '1', this value defines the address character to use for automatic address detection.

- bit 15-14 UTXISEL<1:0>: TX Interrupt Mode Selection bits

- 11 = Reserved, do not use

- 10 = Interrupt is generated and asserted while the transmit buffer is empty

- 01 = Interrupt is generated and asserted when all characters have been transmitted

- 00 = Interrupt is generated and asserted while the transmit buffer contains at least one empty space

### bit 13 **UTXINV:** Transmit Polarity Inversion bit

If IrDA mode is disabled (i.e., IREN (UxMODE<12>) is '0'):

- 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

If IrDA mode is enabled (i.e., IREN (UxMODE<12>) is '1'):

- 1 = IrDA encoded UxTX Idle state is '1'

- 0 = IrDA encoded UxTX Idle state is '0'

- bit 12 URXEN: Receiver Enable bit

- 1 = UARTx receiver is enabled. UxRX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx receiver is disabled. UxRX pin is ignored by the UARTx module. UxRX pin is controlled by port.

### bit 11 UTXBRK: Transmit Break bit

- 1 = Send Break on next transmission. Start bit followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Break transmission is disabled or completed

- bit 10 UTXEN: Transmit Enable bit

- 1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1).

- 0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset. UxTX pin is controlled by port.

- bit 9 **UTXBF:** Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

- bit 8 TRMT: Transmit Shift Register is Empty bit (read-only)

- 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |

| 45.0         | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | _                 | PTEN14            | _                 | _                 | —                 | PTEN<10:8>        |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | PTEN              | <7:0>             |                   |                  |                  |  |  |  |

## REGISTER 20-4: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-15 Unimplemented: Read as '0'

- bit 15-14 **PTEN14:** PMCS1 Address Port Enable bits

- 1 = PMA14 functions as either PMA14 or PMCS1<sup>(1)</sup>

- 0 = PMA14 functions as port I/O

- bit 13-11 Unimplemented: Read as '0'

- bit 10-2 PTEN<10:2>: PMP Address Port Enable bits

- 1 = PMA<10:2> function as PMP address lines

- 0 = PMA<10:2> function as port I/O

### bit 1-0 PTEN<1:0>: PMALH/PMALL Address Port Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads functions as port I/O

- Note 1: The use of this pin as PMA14 or CS1 is selected by the CSF<1:0> bits in the PMCON register.

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by bits ADRMUX<1:0> in the PMCON register.

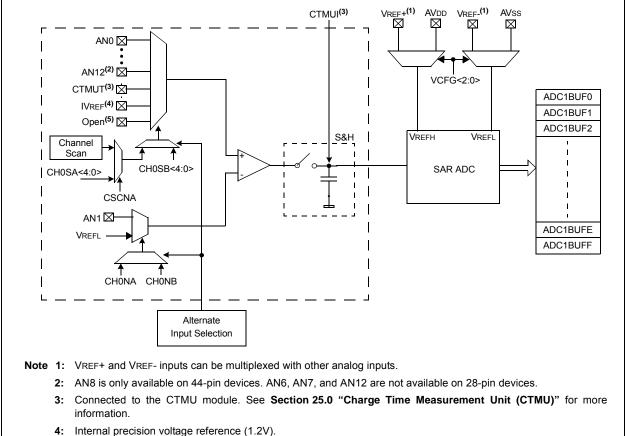

### 22.0 **10-BIT ANALOG-TO-DIGITAL** CONVERTER (ADC)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- · Up to 1 Msps conversion speed

**FIGURE 22-1:**

- Up to 13 analog input pins

- External voltage reference input pins

- · One unipolar, differential Sample and Hold Amplifier (SHA)

- Automatic Channel Scan mode

- Selectable conversion trigger source

- · 16-word conversion result buffer

- Selectable buffer fill modes

- Eight conversion result format options

- · Operation during Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. Figure 22-2 illustrates a block diagram of the ADC conversion clock period. The 10-bit ADC has up to 13 analog input pins, designated AN0-AN12. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

### 5: This selection is only used with CTMU capacitive and time measurement.

ADC1 MODULE BLOCK DIAGRAM

### 25.1 CTMU Control Registers

### TABLE 25-1: CTMU REGISTER MAP

| ess                        |                                 | 6         |                                  | Bits  |          |       |          |                                                |         |        |      |      |        |       | ú    |      |      |       |            |

|----------------------------|---------------------------------|-----------|----------------------------------|-------|----------|-------|----------|------------------------------------------------|---------|--------|------|------|--------|-------|------|------|------|-------|------------|

| Virtual Addres<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15                            | 30/14 | 29/13    | 28/12 | 27/11    | 26/10                                          | 25/9    | 24/8   | 23/7 | 22/6 | 21/5   | 20/4  | 19/3 | 18/2 | 17/1 | 16/0  | All Reset: |

| 4000                       | A200 CTMUCON                    |           | 6 EDG1MOD EDG1POL EDG1SEL<3:0> E |       |          |       | EDG2STAT | EDG2STAT EDG1STAT EDG2MOD EDG2POL EDG2SEL<3:0> |         |        |      | —    | _      | 0000  |      |      |      |       |            |

| A200                       | CIMUCON                         | 15:0      | ON                               | _     | CTMUSIDL | TGEN  | EDGEN    | EDGSEQEN                                       | IDISSEN | CTTRIG |      |      | ITRIM< | <5:0> |      |      | IRNG | <1:0> | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

## 26.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- · Configuration bit select lock

### 26.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, PMDLOCK (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6.** "**Oscillator**" (DS60001112) in the "*PIC32 Family Reference Manual*" for details.

### 26.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The Configuration bit, PMDL1WAY (DEVCFG3<28>), blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

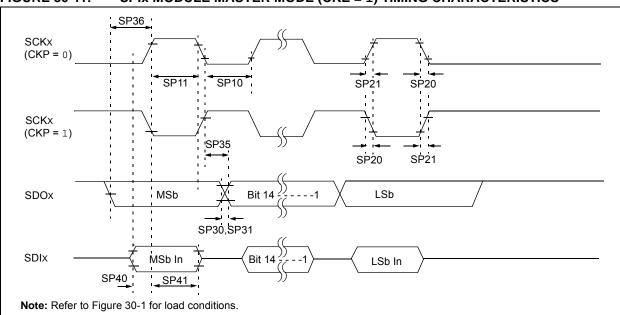

### FIGURE 30-11: SPIX MODULE MASTER MODE (CKE = 1) TIMING CHARACTERISTICS

### TABLE 30-29: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        |                      | rics                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                     |      |       |                    |  |

|---------------|----------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|

| Param.<br>No. | Symbol               | Characteristics <sup>(1)</sup>               | Min.                                                                                                                                                                                                                                                                                | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |

| SP10          | TscL                 | SCKx Output Low Time (Note 3)                | Tsck/2                                                                                                                                                                                                                                                                              | —                   | _    | ns    | _                  |  |

| SP11          | TscH                 | SCKx Output High Time (Note 3)               | Tsck/2                                                                                                                                                                                                                                                                              | —                   | _    | ns    | —                  |  |

| SP20          | TscF                 | SCKx Output Fall Time (Note 4)               | —                                                                                                                                                                                                                                                                                   | —                   | —    | ns    | See parameter DO32 |  |

| SP21          | TscR                 | SCKx Output Rise Time (Note 4)               | _                                                                                                                                                                                                                                                                                   | —                   | _    | ns    | See parameter DO31 |  |

| SP30          | TDOF                 | SDOx Data Output Fall Time (Note 4)          | _                                                                                                                                                                                                                                                                                   | —                   | _    | ns    | See parameter DO32 |  |

| SP31          | TDOR                 | SDOx Data Output Rise Time (Note 4)          | _                                                                                                                                                                                                                                                                                   | _                   | _    | ns    | See parameter DO31 |  |

| SP35          | TscH2doV,            | SDOx Data Output Valid after                 |                                                                                                                                                                                                                                                                                     |                     | 15   | ns    | VDD > 2.7V         |  |

|               | TscL2doV             | SCKx Edge                                    | _                                                                                                                                                                                                                                                                                   |                     | 20   | ns    | VDD < 2.7V         |  |

| SP36          | TDOV2SC,<br>TDOV2SCL | SDOx Data Output Setup to<br>First SCKx Edge | 15                                                                                                                                                                                                                                                                                  | —                   |      | ns    | _                  |  |

| SP40          | TDIV2scH,            | Setup Time of SDIx Data Input to             | 15                                                                                                                                                                                                                                                                                  | —                   | _    | ns    | VDD > 2.7V         |  |

| TDIV2SCL SCK  |                      | SCKx Edge                                    | 20                                                                                                                                                                                                                                                                                  | _                   |      | ns    | VDD < 2.7V         |  |

| SP41          | TscH2DIL,            | Hold Time of SDIx Data Input                 | 15                                                                                                                                                                                                                                                                                  | —                   | _    | ns    | VDD > 2.7V         |  |

|               | TscL2DIL             | to SCKx Edge                                 | 20                                                                                                                                                                                                                                                                                  | _                   |      | ns    | VDD < 2.7V         |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 50 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

| TABLE 30-32: | <b>I2Cx BUS DATA</b> | TIMING REQUIREMENTS | (MASTER MODE) | (CONTINUED) |

|--------------|----------------------|---------------------|---------------|-------------|

|              |                      |                     |               |             |

| AC CHARACTERISTICS |         |                            |                        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |                                                            |  |

|--------------------|---------|----------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------------------------------------------------------|--|

| Param.<br>No.      | Symbol  | Charac                     | teristics              | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                                 | Max. | Units | Conditions                                                 |  |

| IM40               | TAA:SCL | Output Valid<br>from Clock | 100 kHz mode           | —                                                                                                                                                                                                                                                                                   | 3500 | ns    | —                                                          |  |

|                    |         |                            | 400 kHz mode           | —                                                                                                                                                                                                                                                                                   | 1000 | ns    | —                                                          |  |

|                    |         |                            | 1 MHz mode<br>(Note 2) | —                                                                                                                                                                                                                                                                                   | 350  | ns    | —                                                          |  |

| IM45               | TBF:SDA | Bus Free Time              | 100 kHz mode           | 4.7                                                                                                                                                                                                                                                                                 | _    | μS    | The amount of time the                                     |  |

|                    |         |                            | 400 kHz mode           | 1.3                                                                                                                                                                                                                                                                                 | —    | μS    | bus must be free<br>before a new<br>transmission can start |  |

|                    |         |                            | 1 MHz mode<br>(Note 2) | 0.5                                                                                                                                                                                                                                                                                 | —    | μS    |                                                            |  |

| IM50               | Св      | Bus Capacitive Loading     |                        | —                                                                                                                                                                                                                                                                                   | 400  | pF    | —                                                          |  |

| IM51               | Tpgd    | Pulse Gobbler D            | elay                   | 52                                                                                                                                                                                                                                                                                  | 312  | ns    | See Note 3                                                 |  |

**Note 1:** BRG is the value of the  $I^2C$  Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

## 31.0 50 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX1XX/2XX 28/36/44-pin Family electrical characteristics for devices operating at 50 MHz.

The specifications for 50 MHz are identical to those shown in **Section 30.0** "Electrical Characteristics", with the exception of the parameters listed in this chapter.

Parameters in this chapter begin with the letter "M", which denotes 50 MHz operation. For example, parameter DC29a in **Section 30.0** "**Electrical Characteristics**", is the up to 40 MHz operation equivalent for MDC29a.

Absolute maximum ratings for the PIC32MX1XX/2XX 28/36/44-pin Family 50 MHz devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

### Absolute Maximum Ratings

### (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +85°C            |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             | 65°C to +150°C           |

| Voltage on VDD with respect to Vss                                              | -0.3V to +4.0V           |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 2.3V$ (Note 3) | -0.3V to +5.5V           |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | -0.3V to +5.5V           |

| Maximum current out of Vss pin(s)                                               |                          |

| Maximum current into VDD pin(s) (Note 2)                                        |                          |

| Maximum output current sunk by any I/O pin                                      |                          |

| Maximum output current sourced by any I/O pin                                   | 15 mA                    |

| Maximum current sunk by all ports                                               |                          |

| Maximum current sourced by all ports (Note 2)                                   | 200 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

NOTES:

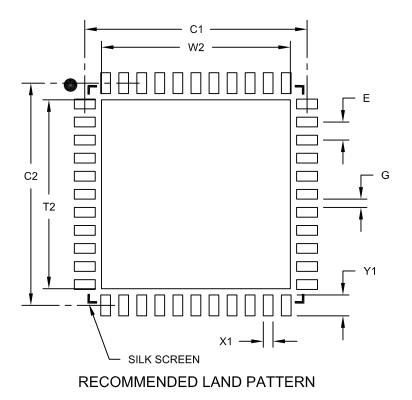

### 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |      |          |      |  |  |

|----------------------------|-------------|------|----------|------|--|--|

| Dimensior                  | MIN         | NOM  | MAX      |      |  |  |

| Contact Pitch              | E           |      | 0.65 BSC |      |  |  |

| Optional Center Pad Width  | W2          |      |          | 6.80 |  |  |

| Optional Center Pad Length | T2          |      |          | 6.80 |  |  |

| Contact Pad Spacing        | C1          |      | 8.00     |      |  |  |

| Contact Pad Spacing        | C2          |      | 8.00     |      |  |  |

| Contact Pad Width (X44)    | X1          |      |          | 0.35 |  |  |

| Contact Pad Length (X44)   | Y1          |      |          | 0.80 |  |  |

| Distance Between Pads      | G           | 0.25 |          |      |  |  |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103A