#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f032bt-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

## 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

## 2.7 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

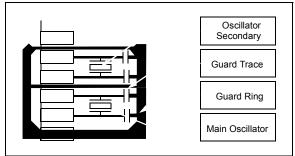

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

## FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

## 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

## 2.9 Typical Application Connection Examples

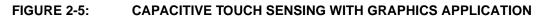

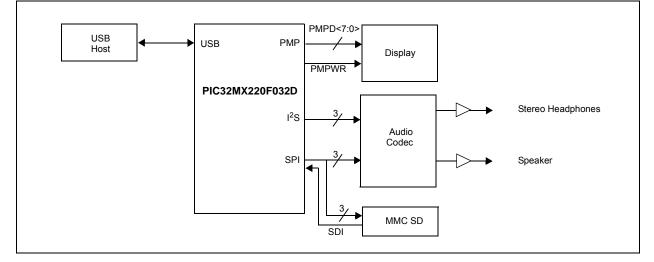

Examples of typical application connections are shown in Figure 2-5 and Figure 2-6.

FIGURE 2-6: AUDIO PLAYBACK APPLICATION

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32<sup>®</sup> architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then

adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

## 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control.                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | EBASE                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration Register 1.                                                |

| 16                 | Config2                 | Configuration Register 2.                                                |

| 16                 | Config3                 | Configuration Register 3.                                                |

| 17-22              | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved in the PIC32MX1XX/2XX family core.                              |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

## TABLE 3-2: COPROCESSOR 0 REGISTERS

**Note 1:** Registers used in exception processing.

**2:** Registers used during debug.

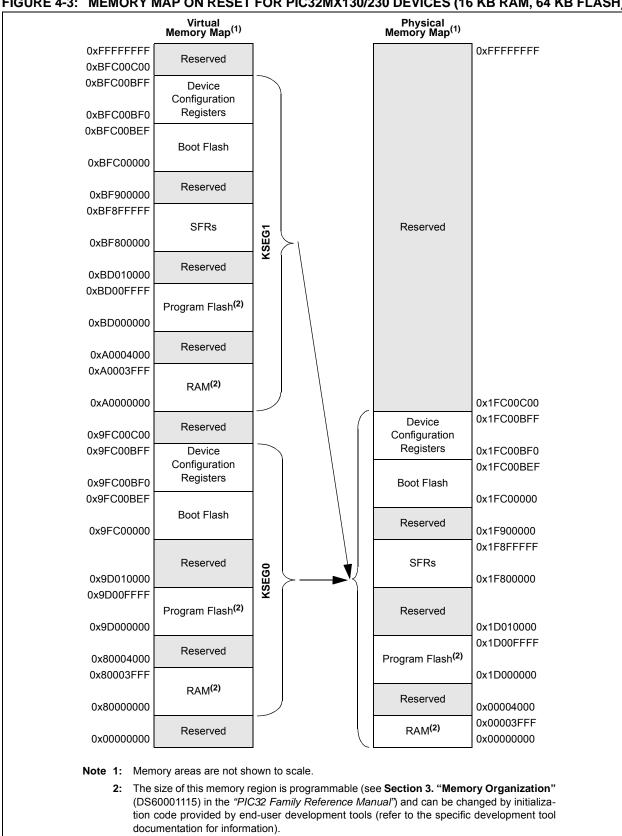

## FIGURE 4-3: MEMORY MAP ON RESET FOR PIC32MX130/230 DEVICES (16 KB RAM, 64 KB FLASH)

NOTES:

## 8.1 Oscillator Control Regiters

| TABLE 8-1: OSCILLATOR CONTROL REGISTER MAP |                                 |           |       |       |          |            |           |       |           |        |         |                      |          |       |        |                       |           |       |                     |

|--------------------------------------------|---------------------------------|-----------|-------|-------|----------|------------|-----------|-------|-----------|--------|---------|----------------------|----------|-------|--------|-----------------------|-----------|-------|---------------------|

| ess                                        |                                 | Bits      |       |       |          |            |           |       |           | ú      |         |                      |          |       |        |                       |           |       |                     |

| Virtual Address<br>(BF80_#)                | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13    | 28/12      | 27/11     | 26/10 | 25/9      | 24/8   | 23/7    | 22/6                 | 21/5     | 20/4  | 19/3   | 18/2                  | 17/1      | 16/0  | All Reset           |

| F000                                       | OSCCON                          | 31:16     | —     | _     | Р        | LLODIV<2:0 | )>        | F     | RCDIV<2:0 | )>     | —       | SOSCRDY              | PBDIVRDY | PBDI\ | /<1:0> | PL                    | LMULT<2:0 | >     | x1xx <sup>(2)</sup> |

| FUUU                                       | 030001                          | 15:0      | —     |       | COSC<2:0 | V          | Ι         |       | NOSC<2:0  | >      | CLKLOCK | ULOCK <sup>(3)</sup> | SLOCK    | SLPEN | CF     | UFRCEN <sup>(3)</sup> | SOSCEN    | OSWEN | xxxx(2)             |

| F010                                       | OSCTUN                          | 31:16     | _     | _     |          | _          | _         |       |           | _      | _       | _                    | _        | _     |        | _                     | —         | _     | 0000                |

| 1010                                       | 030101                          | 15:0      | _     | _     |          | _          | _         |       |           | _      | _       | _                    |          |       | TUN    | l<5:0>                |           |       | 0000                |

| 5000                                       |                                 | 31:16     | _     |       |          |            |           |       |           |        | RODIV<1 | 4:0>                 |          |       |        |                       |           |       | 0000                |

| F020                                       | REFOCON                         | 15:0      | ON    |       | SIDL     | OE         | RSLP      | -     | DIVSWEN   | ACTIVE | —       | —                    |          |       |        | ROSE                  | _<3:0>    |       | 0000                |

| F000                                       | DEEOTDIM                        | 31:16     |       |       |          | R          | OTRIM<8:0 | )>    |           |        |         | _                    | _        | _     | _      | _                     | _         | _     | 0000                |

| F030                                       | REFOTRIM                        | 15:0      | _     | _     |          | _          | _         |       |           | -      | _       | _                    | _        | _     |        | _                     | —         | _     | 0000                |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on PIC32MX2XX devices.

| Bit<br>Range | Bit<br>31/23/15/7              | Bit<br>30/22/14/6           | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|--------------------------------|-----------------------------|-------------------|-------------------|---------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0                            | R/W-0                       | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | — RODIV<14:8> <sup>(1,3)</sup> |                             |                   |                   |                     |                   |                  |                  |  |  |  |

|              | R/W-0                          | R/W-0                       | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        |                                | RODIV<7:0> <sup>(1,3)</sup> |                   |                   |                     |                   |                  |                  |  |  |  |

| 45.0         | R/W-0                          | U-0                         | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |  |

| 15:8         | ON                             | _                           | SIDL              | OE                | RSLP <sup>(2)</sup> | _                 | DIVSWEN          | ACTIVE           |  |  |  |

|              | U-0                            | U-0                         | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                                |                             |                   |                   |                     | ROSEL             | .<3:0>(1)        |                  |  |  |  |

## REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| Legend:           | HC = Hardware Clearable HS = Hardware Settable |                          |                    |  |

|-------------------|------------------------------------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                               | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set                               | '0' = Bit is cleared     | x = Bit is unknown |  |

bit 31 Unimplemented: Read as '0'

| bit 30-16 | RODIV<14:0> Reference Clock Divider bits <sup>(1,3)</sup>                           |

|-----------|-------------------------------------------------------------------------------------|

|           | The value selects the reference clock divider bits. See Figure 8-1 for information. |

| bit 15    | ON: Output Enable bit                                                               |

|           | 1 = Reference Oscillator module is enabled                                          |

|           | 0 = Reference Oscillator module is disabled                                         |

| bit 14    | Unimplemented: Read as '0'                                                          |

| bit 13    | SIDL: Peripheral Stop in Idle Mode bit                                              |

- 1 = Discontinue module operation when the device enters Idle mode

- 0 =Continue module operation when the device enters lide mode

- bit 12 **OE:** Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator module output continues to run in Sleep

- 0 = Reference Oscillator module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0            |  |

| 31:24        | —                 | _                     | BYTC              | <1:0>             | WBO <sup>(1)</sup> | —                 | _                | BITO             |  |

| 22:16        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | _                     | —                 | _                 | —                  | —                 | _                | _                |  |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         |                   | _                     | _                 |                   |                    | PLEN<4:0>         |                  |                  |  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | _                 | _                  | (                 | CRCCH<2:0>       |                  |  |

## Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-30 Unimplemented: Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

#### <u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

#### bit 23-13 Unimplemented: Read as '0'

bit 12-8 **PLEN<4:0>:** Polynomial Length bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        |                   | —                 |                   | —                 |                   |                   |                  | —                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        |                   | —                 |                   | —                 | -                 |                   |                  | —                |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15.0         | -                 | —                 | -                 | —                 | _                 | -                 | —                | —                |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7.0          | LSPDEN            |                   | DEVADDR<6:0>      |                   |                   |                   |                  |                  |  |  |  |  |

## REGISTER 10-12: U1ADDR: USB ADDRESS REGISTER

## Legend:

| U                                 |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-8 Unimplemented: Read as '0'

bit 7 LSPDEN: Low-Speed Enable Indicator bit

1 = Next token command to be executed at Low-Speed

0 = Next token command to be executed at Full-Speed

bit 6-0 **DEVADDR<6:0>:** 7-bit USB Device Address bits

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | _                 | —                 | _                 | —                |                  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | -                 | —                 | _                 | —                |                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 | —                 |                   | —                 | _                 | —                | -                |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | FRML              | <7:0>             |                   |                  |                  |

### REGISTER 10-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FRML<7:0>:** The 11-bit Frame Number Lower bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | _                 |                   |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | -                 | _                 | -                 | —                 | _                 | _                 | -                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | P]R<3:0>         |                  |

#### **REGISTER 11-1:** [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

## Legend:

|                    | Legena.           |                  |                           |                    |  |

|--------------------|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit W |                   | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

|                    | -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

## bit 31-4 Unimplemented: Read as '0'

bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 11-1 for input pin selection values.

Note: Register values can only be changed if the Configuration bit, IOLOCK (CFGCON<13>), = 0.

### REGISTER 11-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | _                 | _                 | —                 | _                 | —                 |                  | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | -                | —                |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | _                 | —                 | _                 | —                 | _                 | —                 | _                | —                |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   | _                 |                   |                   | RPnR<3:0>         |                   |                  |                  |  |

## Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 11-2 for output pin selection values.

Note: Register values can only be changed if the Configuration bit, IOLOCK (CFGCON<13>), = 0.

NOTES:

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

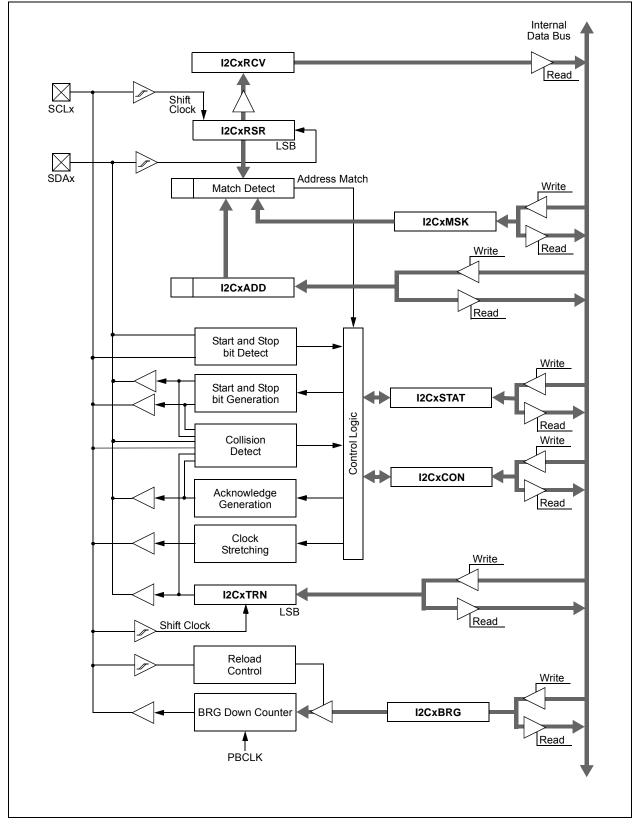

## FIGURE 18-1: I<sup>2</sup>C BLOCK DIAGRAM

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

## REGISTER 18-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |  |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |  |

| Legend:           | HC = Cleared in Hardware                            |                      |                    |  |  |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

bit 12

- 1 = Enables the  $l^2C$  module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the  $I^2$ C module; all  $I^2$ C pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

- 0 = Hold SCLx clock low (clock stretch)

#### If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

#### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule not enabled

#### bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control disabled

- 0 = Slew rate control enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| REGISTE | R 18-1:           | I2CxCON: I <sup>2</sup> C CONTROL REGISTER (CONTINUED)                                                                                                                |

|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7   | GCEN: Ge          | eneral Call Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                     |

|         | (module           | interrupt when a general call address is received in the I2CxRSR<br>e is enabled for reception)                                                                       |

|         |                   | al call address is disabled                                                                                                                                           |

| bit 6   | STREN: S          | CLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)                                                                                               |

|         |                   | njunction with SCLREL bit.                                                                                                                                            |

|         |                   | e software or receive clock stretching                                                                                                                                |

| L:1 F   |                   | e software or receive clock stretching                                                                                                                                |

| bit 5   |                   | cknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive) is transmitted when the software initiates an Acknowledge sequence. |

|         |                   | a NACK during an Acknowledge sequence                                                                                                                                 |

|         |                   | an ACK during an Acknowledge sequence                                                                                                                                 |

| bit 4   | ACKEN: A receive) | cknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master                                                                   |

|         | Hardwa            | Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.<br>are clear at end of master Acknowledge sequence.<br>wledge sequence not in progress        |

| bit 3   | RCEN: Re          | ceive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                          |

|         |                   | es Receive mode for I <sup>2</sup> C. Hardware clear at end of eighth bit of master receive data byte.<br>The sequence not in progress                                |

| bit 2   | PEN: Stop         | Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                      |

|         |                   | Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence. ondition not in progress                                                         |

| bit 1   | RSEN: Re          | peated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                         |

|         |                   | Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of Repeated Start sequence.                                                                     |

|         | 0 = Repeat        | ted Start condition not in progress                                                                                                                                   |

| bit 0   |                   | Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                      |

|         |                   | Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence. ondition not in progress                                                       |

|         |                   |                                                                                                                                                                       |

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## 19.1 UART Control Registers

## TABLE 19-1: UART1 AND UART2 REGISTER MAP

| np for point | ess                         |                  | 6         |                                   |        |        |       |        |       |       | Bi          | ts          |         |       |             |        |       |        |       | 6          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|-----------|-----------------------------------|--------|--------|-------|--------|-------|-------|-------------|-------------|---------|-------|-------------|--------|-------|--------|-------|------------|

| 6000     0 MODE     15.0     ON     -     SIDL     IREN     RTSMD     -     UEN<1:0>     WAKE     LPBACK     ABAUD     RXINV     BRGH     PDEL<1:0>     STSL     0.00       610     U1STA(1)     31:16     -     -     -     -     ADM_EN     VERSE     LPBACK     ABAUD     RXINV     BRGH     PDEL<1:0>     STSL     0.00       600     U1STA(1)     15.0     UTXINV     URXEN     UTXENK     UTXEN     TRM     URXEN     TRMT     URXEN     ADDEN     RIDE     PERR     PERR     OER     URXDA     0100       600     U1TXREG     31:16     -     -     -     -     -     -     -     -     0000       6100     U1RXREG     31:16     -     -     -     -     -     -     -     -     -     0000       6100     U1RXREG     31:16     -     -     -     -     -     -     -     -     0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15                             | 30/14  | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7        | 22/6    | 21/5  | 20/4        | 19/3   | 18/2  | 17/1   | 16/0  | All Resets |

| 610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610     610 <td>6000</td> <td></td> <td>31:16</td> <td></td> <td></td> <td>_</td> <td>_</td> <td>—</td> <td>_</td> <td></td> <td>_</td> <td>_</td> <td>—</td> <td></td> <td></td> <td>_</td> <td>_</td> <td>_</td> <td>_</td> <td>0000</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6000                        |                  | 31:16     |                                   |        | _      | _     | —      | _     |       | _           | _           | —       |       |             | _      | _     | _      | _     | 0000       |

| 600     UTXIST     15.0     UTXIST     UTXINV     UTXRNV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0000                        | OTWODE           | 15:0      | ON                                |        | SIDL   | IREN  | RTSMD  | —     | UEN   | -           | WAKE        | LPBACK  | ABAUD | RXINV       | BRGH   | PDSEI | L<1:0> | STSEL | 0000       |

| 15:0     15:0     01XBE     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6010                        | 111STA(1)        | 31:16     | _                                 | _      | _      | —     | —      | _     | _     | ADM_EN      |             |         |       | ADDR        | 2<7:0> |       |        |       | 0000       |

| 600     UTXRE     1     -     -     -     -     -     -     -     -     -     -     000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000     0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0010                        | UIUIA            | 15:0      | UTXISE                            | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXIS       | EL<1:0> | ADDEN | RIDLE       | PERR   | FERR  | OERR   | URXDA | 0110       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6020                        |                  | 31:16     | —                                 | -      | —      | _     | —      | —     | -     | —           | _           | —       | —     | _           | _      | _     | —      | _     | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0020                        | UTTAKLG          | 15:0      | _                                 |        | _      |       | _      | -     |       |             |             |         | Tra   | nsmit Regis | ster   |       |        |       | 0000       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6030                        |                  | 31:16     | _                                 |        | _      |       | _      | -     |       | _           |             | _       | _     |             | -      |       | _      |       | 0000       |

| 600   11   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   1.50   <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0030                        | 0030 UIRAREG     |           | _                                 |        | _      |       | _      | -     |       |             |             |         | Re    | ceive Regis | ster   |       |        |       | 0000       |

| 15:0     Bale Rate Generator Present     1000       6200     16:0 $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6040                        |                  | 31:16     | -                                 |        | -      |       | _      | -     |       | —           |             | _       | -     |             | -      |       | -      |       | 0000       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00+0                        | 0 IDIXO          | 15:0      | Baud Rate Generator Prescaler 000 |        |        |       |        |       |       |             |             |         |       |             | 0000   |       |        |       |            |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6200                        | 112MODE(1)       | 31:16     | _                                 | _      | _      | —     | —      | _     | _     | —           | -           | —       | _     | -           | —      | _     | —      | _     | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0200                        | OZINODL          | 15:0      | ON                                |        | SIDL   | IREN  | RTSMD  | —     | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV       | BRGH   | PDSE  | L<1:0> | STSEL | 0000       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6210                        | 112974(1)        | 31:16     | _                                 |        | _      |       | _      | -     |       | ADM_EN      |             |         |       | ADDR        | <7:0>  |       |        |       | 0000       |