#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f032bt-i-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                         | Pin Nu                            | mber <sup>(1)</sup> |                                 |             |                      |                                                                                      |  |  |

|----------|-------------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------------|--------------------------------------------------------------------------------------|--|--|

| Pin Name | 28-pin<br>QFN           | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type       | Description                                                                          |  |  |

| MCLR     | 26                      | 1                                 | 32                  | 18                              | I/P         | ST                   | Master Clear (Reset) input. This pin is an active-low Reset to the device.           |  |  |

| AVDD     | 25                      | 28                                | 31                  | 17                              | Р           | _                    | Positive supply for analog modules. This pin must be connected at all times.         |  |  |

| AVss     | 24                      | 27                                | 30                  | 16                              | Р           | —                    | Ground reference for analog modules                                                  |  |  |

| Vdd      | 10                      | 13                                | 5, 13, 14,<br>23    | 28, 40                          | Р           | _                    | Positive supply for peripheral logic and<br>I/O pins                                 |  |  |

| VCAP     | 17                      | 20                                | 22                  | 7                               | Р           | —                    | CPU logic filter capacitor connection                                                |  |  |

| Vss      | 5, 16                   | 8, 19                             | 6, 12, 21           | 6, 29, 39                       | Р           | _                    | Ground reference for logic and I/O pins.<br>This pin must be connected at all times. |  |  |

| VREF+    | 27                      | 2                                 | 33                  | 19                              | I           | Analog               | Analog voltage reference (high) input                                                |  |  |

| VREF-    | 28                      | 3                                 | 34                  | 20                              | I           | Analog               | Analog voltage reference (low) input                                                 |  |  |

| Legend:  | CMOS = CM<br>ST = Schmi |                                   | •                   |                                 |             | Analog =<br>O = Outp | Analog input P = Power<br>ut I = Input                                               |  |  |

#### TADI E 4 4. DINOUT I/O DESCRIPTIONS (CONTINUED)

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer

| . , .     |

|-----------|

| P = Powe  |

| l = Input |

| — = N/A   |

|           |

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site:

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

#### 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

### 2.7 External Oscillator Pins

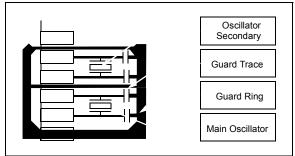

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

### 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

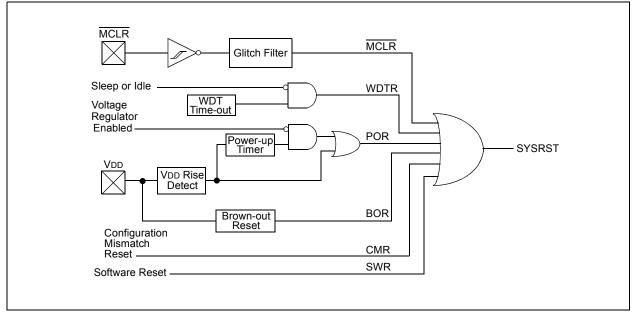

#### 6.0 RESETS

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- Power-on Reset (POR)

- Master Clear Reset pin (MCLR)

- · Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- Brown-out Reset (BOR)

- Configuration Mismatch Reset (CMR)

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

#### FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

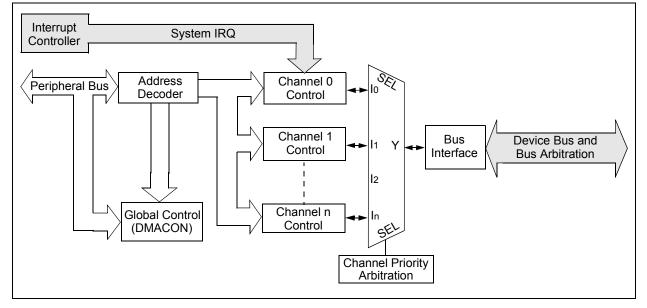

### 9.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32, such as Peripheral Bus devices: SPI, UART, PMP, etc., or memory itself. Figure 9-1 show a block diagram of the DMA Controller module.

The DMA Controller module has the following key features:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

#### FIGURE 9-1: DMA BLOCK DIAGRAM

- Fixed priority channel arbitration

- · Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- · Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

|              | SIGTER 5-10. DOTINGUE. DINA GHANNEE & GELE-GIZE REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|--------------|----------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                        | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 21.24        | U-0                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                                                        | —                 | _                 | —                 | _                 | —                 | _                | _                |  |  |  |

| 22:16        | U-0                                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        |                                                          | _                 |                   | _                 | _                 |                   | _                |                  |  |  |  |

| 45.0         | R/W-0                                                    | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | CHCSIZ<15:8>                                             |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0                                                    | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                                                          |                   |                   | CHCSIZ            | <7:0>             |                   |                  |                  |  |  |  |

#### REGISTER 9-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell Size bits

1111111111111111 = 65,535 bytes transferred on an event

#### REGISTER 9-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | —                 | —                 | —                 | _                 | —                 | —                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | CHCPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | CHCPTF            | R<7:0>            |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

Note: When in Pattern Detect mode, this register is reset on a pattern detect.

#### REGISTER 10-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the EVEN Buffer Descriptor banks

- 0 = Even/Odd buffer pointers are not Reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit<sup>(5)</sup>

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          | —                 | —                 | _                 | —                 | —                 |                   | FRMH<2:0>        |                  |  |  |

#### REGISTER 10-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

#### Legend:

| 0                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** The Upper 3 bits of the Frame Numbers bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### Bit Bit Bit Bit Bit Bit Bit Bit Bit 30/22/14/6 27/19/11/3 26/18/10/2 25/17/9/1 24/16/8/0 Range 31/23/15/7 29/21/13/5 28/20/12/4 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 31:24 \_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 23:16 \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 15:8 \_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 7:0 PID < 3:0 > (1)EP<3:0>

#### **REGISTER 10-15: U1TOK: USB TOKEN REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-4 **PID<3:0>:** Token Type Indicator bits<sup>(1)</sup>

1101 = SETUP (TX) token type transaction

- 1001 = IN (RX) token type transaction

- 0001 = OUT (TX) token type transaction

Note: All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

Note 1: All other values are reserved and must not be used.

#### TABLE 11-6: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| ssa                         |                  |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FA04                        | INT1R            | 31:16     |       | _     |       |       | _     | _     |      | ]    |      | _    |      |      |      | _     | _      |      | 0000       |

| FA04                        |                  | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | INT1F | R<3:0> |      | 0000       |

| FA08                        | INT2R            | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | _     | —      | —    | 0000       |

| FAUO                        | INTZR            | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | INT2F | R<3:0> |      | 0000       |

| FA0C                        | INT3R            | 31:16     | _     | _     | _     | _     | —     | —     | _    | _    | —    | _    |      | —    | _    |       | —      | —    | 0000       |

| FAUC                        | IN I 3R          | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | INT3F | R<3:0> |      | 0000       |

| 5440                        |                  | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | -    | 0000       |

| FA10                        | INT4R            | 15:0      | -     | _     | _     | _     | -     | -     | _    | _    | _    | _    | _    | _    |      | INT4F | R<3:0> |      | 0000       |

| 5440                        | TAOKA            | 31:16     | _     | _     | _     | _     | —     | —     | _    | _    | _    | _    | _    | _    | _    | _     | _      | —    | 0000       |

| FA18                        | T2CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T2CK  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    | _    |       | _      | _    | 0000       |

| FA1C                        | T3CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    |      | T3CK  | R<3:0> | •    | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    | _    |       | _      | _    | 0000       |

| FA20                        | T4CKR            | 15:0      | _     |       | _     |       | _     | _     | _    | _    | _    |      |      | _    |      | T4CK  | R<3:0> | •    | 0000       |

|                             |                  | 31:16     | _     |       | _     |       | _     | _     | _    | _    | _    |      |      | _    | _    |       | _      | _    | 0000       |

| FA24                        | T5CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T5CK  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |       | —      | _    | 0000       |

| FA28                        | IC1R             | 15:0      | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | IC1R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _     | _      | _    | 0000       |

| FA2C                        | IC2R             | 15:0      | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      |      | IC2R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | _     | _      | _    | 0000       |

| FA30                        | IC3R             | 15:0      | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | IC3R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _     | _      | _    | 0000       |

| FA34                        | IC4R             | 15:0      | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      |      | IC4R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _     | _      | _    | 0000       |

| FA38                        | IC5R             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | IC5R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     | _     |       |       | _     | _     |      | _    | _    | _    | _    | _    |      | _     |        | _    | 0000       |

| FA48                        | OCFAR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFA  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA4C                        | OCFBR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFB  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA50                        | U1RXR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U1RX  | R<3:0> |      | 0000       |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 17-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)

- bit 5 **MSTEN:** Master Mode Enable bit

- 1 = Master mode

- 0 = Slave mode

- bit 4 DISSDI: Disable SDI bit

- 1 = SDI pin is not used by the SPI module (pin is controlled by PORT function)

- 0 = SDI pin is controlled by the SPI module

- bit 3-2 STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)

- 10 = Interrupt is generated when the buffer is empty by one-half or more

- 01 = Interrupt is generated when the buffer is completely empty

- 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are complete

- bit 1-0 SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is full

- 10 = Interrupt is generated when the buffer is full by one-half or more

- 01 = Interrupt is generated when the buffer is not empty

- 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit can only be written when the ON bit = 0.

- 3: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

### REGISTER 18-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

|              |                                  |       |                   | 0                 |                   |                   |                  |                  |  |

|--------------|----------------------------------|-------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 21.24        | U-0                              | U-0   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                                | —     | _                 | —                 | —                 | —                 | _                | _                |  |

| 00.40        | U-0                              | U-0   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                                  | —     | _                 | _                 | _                 | _                 | _                | _                |  |

| 45.0         | R/W-0                            | U-0   | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | 0N <sup>(1)</sup>                | —     | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |  |

| 7:0          | R/W-0                            | R/W-0 | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |  |

| 7:0          | GCEN                             | STREN | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |  |

| Legend:           | HC = Cleared in Hardware |                                                     |                    |  |  |  |

|-------------------|--------------------------|-----------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit         | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

bit 12

- 1 = Enables the  $I^2C$  module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the  $I^2$ C module; all  $I^2$ C pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

- 0 = Hold SCLx clock low (clock stretch)

#### If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

#### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule not enabled

#### bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control disabled

- 0 = Slew rate control enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

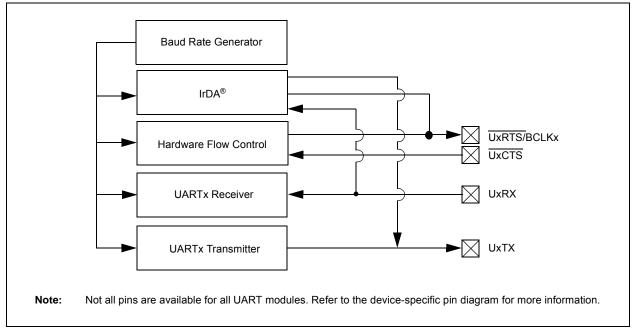

### 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The UART module is one of the serial I/O modules available in PIC32MX1XX/2XX 28/36/44-pin Family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN, and IrDA<sup>®</sup>. The UART module also supports the hardware flow control option, with UXCTS and UXRTS pins, and also includes an IrDA encoder and decoder.

Key features of the UART module include:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- · One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 38 bps to 12.5 Mbps at 50 MHz

- 8-level deep First In First Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9th bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the UART module.

#### FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

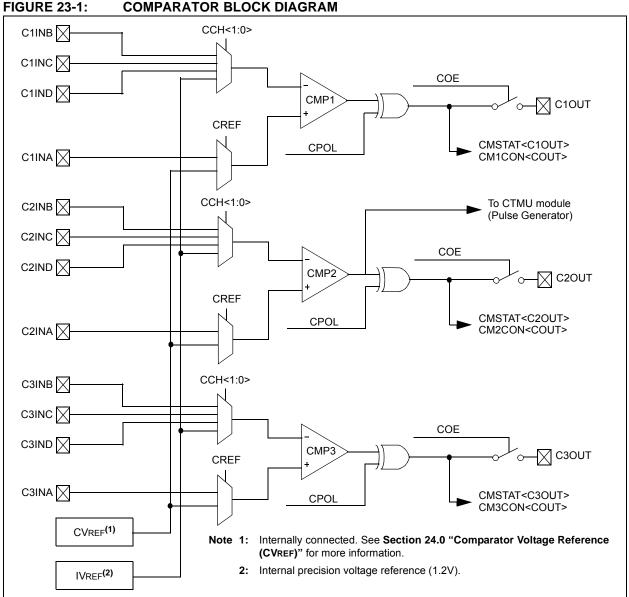

#### 23.0 COMPARATOR

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer Section 19. to "Comparator" (DS60001110), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Analog Comparator module contains three comparators that can be configured in a variety of ways.

Following are some of the key features of this module:

- Selectable inputs available include:

- Analog inputs multiplexed with I/O pins

- On-chip internal absolute voltage reference (IVREF)

- Comparator voltage reference (CVREF)

- · Outputs can be Inverted

- Selectable interrupt generation

A block diagram of the comparator module is provided in Figure 23-1.

#### REGISTER 27-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 18-10 **PWP<8:0>:** Program Flash Write-Protect bits<sup>(3)</sup>

| DIT 18-10 | PWP<8:0>: Program Flash Write-Protect bits <sup>(9)</sup>                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------|

|           | Prevents selected program Flash memory pages from being modified during code execution.<br>111111111 = Disabled |

|           | 111111110 = Memory below 0x0400 address is write-protected                                                      |

|           | 111111101 = Memory below 0x0400 address is write-protected                                                      |

|           | 111111100 = Memory below 0x0000 address is write-protected                                                      |

|           | 111111001 = Memory below 0x0000 address is write-protected                                                      |

|           | 111111010 = Memory below 0x1000 (44) address is write-protected                                                 |

|           | 111111001 = Memory below 0x1400 address is write-protected                                                      |

|           | 111111000 = Memory below 0x1000 address is write-protected                                                      |

|           | 111110111 = Memory below 0x2000 (8K) address is write-protected                                                 |

|           | 111110110 = Memory below 0x2400 address is write-protected                                                      |

|           | 111110101 = Memory below 0x2800 address is write-protected                                                      |

|           | 111110100 = Memory below 0x2C00 address is write-protected                                                      |

|           | 111110011 = Memory below 0x3000 address is write-protected                                                      |

|           | 111110010 = Memory below 0x3400 address is write-protected                                                      |

|           | 111110001 = Memory below 0x3800 address is write-protected                                                      |

|           | 111110000 = Memory below 0x3C00 address is write-protected                                                      |

|           | 111101111 = Memory below 0x4000 (16K) address is write-protected                                                |

|           | •                                                                                                               |

|           | •                                                                                                               |

|           | 110111111 = Memory below 0x10000 (64K) address is write-protected                                               |

|           | •                                                                                                               |

|           |                                                                                                                 |

|           | 101111111 = Memory below 0x20000 (128K) address is write-protected                                              |

|           | •                                                                                                               |

|           | •                                                                                                               |

|           | •                                                                                                               |

|           | 011111111 = Memory below 0x40000 (256K) address is write-protected                                              |

|           | •                                                                                                               |

|           |                                                                                                                 |

|           | 00000000 = All possible memory is write-protected                                                               |

| bit 9-5   | Reserved: Write '1'                                                                                             |

| bit 4-3   | ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits <sup>(2)</sup>                      |

|           | 11 = PGEC1/PGED1 pair is used                                                                                   |

|           | 10 = PGEC2/PGED2 pair is used                                                                                   |

|           | 01 = PGEC3/PGED3 pair is used                                                                                   |

|           | 00 = PGEC4/PGED4 pair is used(2)                                                                                |

| bit 2     | JTAGEN: JTAG Enable bit <sup>(1)</sup>                                                                          |

| DIL Z     | 1 = JTAG is enabled                                                                                             |

|           |                                                                                                                 |

|           | 0 = JTAG is disabled                                                                                            |

| bit 1-0   | <b>DEBUG&lt;1:0&gt;:</b> Background Debugger Enable bits (forced to '11' if code-protect is enabled)            |

|           | 1x = Debugger is disabled                                                                                       |

|           | 0x = Debugger is enabled                                                                                        |

| Note 1:   | This bit sets the value for the JTAGEN bit in the CFGCON register.                                              |

|           |                                                                                                                 |

| 2:        | The PGEC4/PGED4 pin pair is not available on all devices. Refer to the " <b>Pin Diagrams</b> " section for      |

|           | availability.                                                                                                   |

3: The PWP<8:7> bits are only available on devices with 256 KB Flash.

#### 29.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

| DC CHARACTERISTICS |        |                                      |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |        |                                               |  |  |

|--------------------|--------|--------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|-----------------------------------------------|--|--|

| Param.<br>No.      | Symbol | Characteristics                      | Min.   | Typical <sup>(1)</sup>                                                                                                                                                                                                                                                                | Max. | Units  | Conditions                                    |  |  |

|                    |        | Program Flash Memory <sup>(3)</sup>  |        |                                                                                                                                                                                                                                                                                       |      |        |                                               |  |  |

| D130               | Eр     | Cell Endurance                       | 20,000 | —                                                                                                                                                                                                                                                                                     | _    | E/W    | —                                             |  |  |

| D131               | Vpr    | VDD for Read                         | 2.3    | —                                                                                                                                                                                                                                                                                     | 3.6  | V      | —                                             |  |  |

| D132               | VPEW   | VDD for Erase or Write               | 2.3    | —                                                                                                                                                                                                                                                                                     | 3.6  | V      | —                                             |  |  |

| D134               | Tretd  | Characteristic Retention             | 20     | —                                                                                                                                                                                                                                                                                     | _    | Year   | Provided no other specifications are violated |  |  |

| D135               | IDDP   | Supply Current during<br>Programming | _      | 10                                                                                                                                                                                                                                                                                    | _    | mA     | —                                             |  |  |

|                    | Tww    | Word Write Cycle Time                | —      | 411                                                                                                                                                                                                                                                                                   | _    | es     | See Note 4                                    |  |  |

| D136               | Trw    | Row Write Cycle Time                 | —      | 6675                                                                                                                                                                                                                                                                                  | _    | Cycles | See Note 2,4                                  |  |  |

| D137               | TPE    | Page Erase Cycle Time                | —      | 20011                                                                                                                                                                                                                                                                                 | _    |        | See Note 4                                    |  |  |

|                    | TCE    | Chip Erase Cycle Time                | —      | 80180                                                                                                                                                                                                                                                                                 | _    | FRC    | See Note 4                                    |  |  |

#### TABLE 30-12: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: The minimum SYSCLK for row programming is 4 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

**3:** Refer to the *"PIC32 Flash Programming Specification"* (DS60001145) for operating conditions during programming and erase cycles.

4: This parameter depends on FRC accuracy (See Table 30-19) and FRC tuning values (See Register 8-2).

| DC CHARACTERISTICS |                        |                                                           |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |                                                                                         |  |  |

|--------------------|------------------------|-----------------------------------------------------------|------|------------------------------------------------------|------|-------|-----------------------------------------------------------------------------------------|--|--|

| Param.<br>No.      | Symbol Characteristics |                                                           |      | Typical                                              | Max. | Units | Comments                                                                                |  |  |

| D300               | VIOFF                  | Input Offset Voltage                                      | -    | ±7.5                                                 | ±25  | mV    | AVDD = VDD,<br>AVSS = VSS                                                               |  |  |

| D301               | VICM                   | Input Common Mode Voltage                                 | 0    | —                                                    | Vdd  | V     | AVDD = VDD,<br>AVss = Vss<br>(Note 2)                                                   |  |  |

| D302               | CMRR                   | Common Mode Rejection Ratio                               | 55   | —                                                    | _    | dB    | Max VICM = (VDD - 1)V<br>(Note 2)                                                       |  |  |

| D303A              | TRESP                  | Large Signal Response Time                                | _    | 150                                                  | 400  | ns    | AVDD = VDD, AVSS = VSS<br>(Note 1,2)                                                    |  |  |

| D303B              | TSRESP                 | Small Signal Response Time                                | -    | 1                                                    | _    | μS    | This is defined as an input<br>step of 50 mV with 15 mV<br>of overdrive <b>(Note 2)</b> |  |  |

| D304               | ON2ov                  | Comparator Enabled to Output<br>Valid                     | —    | _                                                    | 10   | μs    | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2)  |  |  |

| D305               | IVREF                  | Internal Voltage Reference                                | 1.14 | 1.2                                                  | 1.26 | V     | —                                                                                       |  |  |

| D312               | TSET                   | Internal Comparator Voltage<br>DRC Reference Setting time | —    | —                                                    | 10   | μs    | (Note 3)                                                                                |  |  |

#### TABLE 30-13: COMPARATOR SPECIFICATIONS

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

**4:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

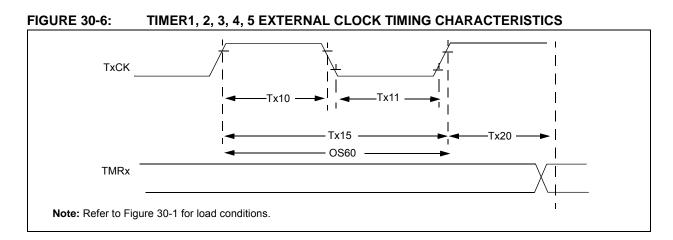

#### TABLE 30-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS

|               |           |                                                                                                           |                                                                   |      | tandard Operating Conditions: 2.3V to 3.6V<br>Inless otherwise stated)<br>perating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |         |                                   |          |                               |    |                               |

|---------------|-----------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------|----------|-------------------------------|----|-------------------------------|

| Param.<br>No. | Symbol    | Characteristics <sup>(2)</sup>                                                                            |                                                                   | Min. |                                                                                                                                                                                                            | Typical | Max.                              | Units    | Conditions                    |    |                               |

| TA10          | T⊤xH      | TxCK<br>High Time                                                                                         | Synchronous, with prescaler                                       |      | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns                                                                                                                                                                          | —       | —                                 | ns       | Must also meet parameter TA15 |    |                               |

|               |           |                                                                                                           | Asynchronous, with prescaler                                      |      | 10                                                                                                                                                                                                         | —       | _                                 | ns       | —                             |    |                               |

| TA11          | T⊤xL      | TxCK<br>Low Time                                                                                          | Synchronous,<br>with prescaler<br>Asynchronous,<br>with prescaler |      |                                                                                                                                                                                                            |         | [(12.5 ns or 1 Трв)/N]<br>+ 25 ns | рв)/N] — |                               | ns | Must also meet parameter TA15 |

|               |           |                                                                                                           |                                                                   |      | 10                                                                                                                                                                                                         | _       | _                                 | ns       | —                             |    |                               |

| TA15          | ΤτχΡ      | TxCK<br>Input Period                                                                                      | Synchronous,<br>with prescaler<br>Asynchronous,<br>with prescaler |      | [(Greater of 25 ns or<br>2 Трв)/N] + 30 ns                                                                                                                                                                 | -       | _                                 | ns       | VDD > 2.7V                    |    |                               |

|               |           |                                                                                                           |                                                                   |      | [(Greater of 25 ns or<br>2 Трв)/N] + 50 ns                                                                                                                                                                 | -       | —                                 | ns       | VDD < 2.7V                    |    |                               |

|               |           |                                                                                                           |                                                                   |      |                                                                                                                                                                                                            |         | 20                                | -        | _                             | ns | VDD > 2.7V<br>(Note 3)        |

|               |           |                                                                                                           |                                                                   |      | 50                                                                                                                                                                                                         | -       | _                                 | ns       | VDD < 2.7V<br>(Note 3)        |    |                               |

| OS60          | FT1       | SOSC1/T1CK Oscillator<br>Input Frequency Range<br>(oscillator enabled by setti<br>the TCS (T1CON<1>) bit) |                                                                   |      | 32                                                                                                                                                                                                         | —       | 100                               | kHz      | -                             |    |                               |

| TA20          | TCKEXTMRL | Delay from External TxCk<br>Clock Edge to Timer<br>Increment                                              |                                                                   | К    |                                                                                                                                                                                                            | —       | 1                                 | Трв      | —                             |    |                               |

**Note 1:** Timer1 is a Type A timer.

**2:** This parameter is characterized, but not tested in manufacturing.

**3:** N = Prescale Value (1, 8, 64, 256).

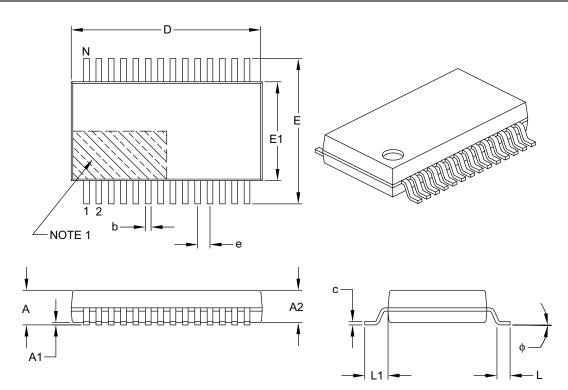

#### 33.2 Package Details

This section provides the technical details of the packages.

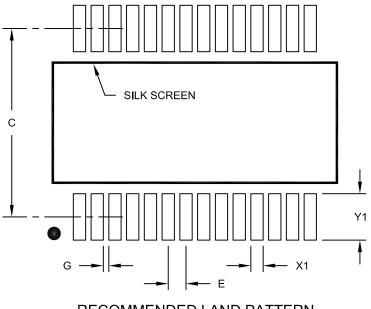

#### 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |      |          | MILLIMETERS |  |  |  |

|--------------------------|------------------|------|----------|-------------|--|--|--|

|                          | Dimension Limits | MIN  | NOM      | MAX         |  |  |  |

| Number of Pins           | N                |      | 28       | 28          |  |  |  |

| Pitch                    | e                |      | 0.65 BSC |             |  |  |  |

| Overall Height           | A                | -    | -        | 2.00        |  |  |  |

| Molded Package Thickness | A2               | 1.65 | 1.75     | 1.85        |  |  |  |

| Standoff                 | A1               | 0.05 | -        | -           |  |  |  |

| Overall Width            | E                | 7.40 | 7.80     | 8.20        |  |  |  |

| Molded Package Width     | E1               | 5.00 | 5.30     | 5.60        |  |  |  |

| Overall Length           | D                | 9.90 | 10.20    | 10.50       |  |  |  |

| Foot Length              | L                | 0.55 | 0.75     | 0.95        |  |  |  |

| Footprint                | ootprint L1      |      |          | 1.25 REF    |  |  |  |

| Lead Thickness           | С                | 0.09 | -        | 0.25        |  |  |  |

| Foot Angle               | φ                | 0°   | 4°       | 8°          |  |  |  |

| Lead Width               | b                | 0.22 | -        | 0.38        |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

#### 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |      |      |

|--------------------------|-------------|----------|------|------|

| Dimension                | MIN         | NOM      | MAX  |      |

| Contact Pitch            | E           | 0.65 BSC |      |      |

| Contact Pad Spacing      | С           |          | 7.20 |      |

| Contact Pad Width (X28)  | X1          |          |      | 0.45 |

| Contact Pad Length (X28) | Y1          |          |      | 1.75 |

| Distance Between Pads    | G           | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A