Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f032bt-v-ml |

## **Pin Diagrams**

### TABLE 3: PIN NAMES FOR 28-PIN GENERAL PURPOSE DEVICES

28-PIN SOIC, SPDIP, SSOP (TOP VIEW)(1,2,3)

1 28 1 28 1 28 SSOP SOIC SPDIP

PIC32MX110F016B PIC32MX120F032B PIC32MX130F064B PIC32MX130F256B PIC32MX150F128B PIC32MX170F256B

| Pin # | Full Pin Name                         |

|-------|---------------------------------------|

| 1     | MCLR                                  |

| 2     | VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/RA0 |

| 3     | VREF-/CVREF-/AN1/RPA1/CTED2/RA1       |

| 4     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/RB0  |

| 5     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/RB1 |

| 6     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/RB2  |

| 7     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/RB3    |

| 8     | Vss                                   |

| 9     | OSC1/CLKI/RPA2/RA2                    |

| 10    | OSC2/CLKO/RPA3/PMA0/RA3               |

| 11    | SOSCI/RPB4/RB4                        |

| 12    | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4        |

| 13    | VDD                                   |

| 14    | PGED3/RPR5/PMD7/RR5                   |

| _ |      |                                                |

|---|------|------------------------------------------------|

|   | Pin# | Full Pin Name                                  |

|   | 15   | PGEC3/RPB6/PMD6/RB6                            |

|   | 16   | TDI/RPB7/CTED3/PMD5/INT0/RB7                   |

|   | 17   | TCK/RPB8/SCL1/CTED10/PMD4/RB8                  |

|   | 18   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                   |

|   | 19   | Vss                                            |

|   | 20   | VCAP                                           |

|   | 21   | PGED2/RPB10/CTED11/PMD2/RB10                   |

|   | 22   | PGEC2/TMS/RPB11/PMD1/RB11                      |

|   | 23   | AN12/PMD0/RB12                                 |

|   | 24   | AN11/RPB13/CTPLS/PMRD/RB13                     |

|   | 25   | CVREFOUT/AN10/C3INB/RPB14/SCK1/CTED5/PMWR/RB14 |

|   | 26   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15          |

|   | 27   | AVss                                           |

|   | 28   | AVnn                                           |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3 "Peripheral Pin Select"** for restrictions.

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: Shaded pins are 5V tolerant.

TABLE 1-1: PINOUT I/O DESCRIPTIONS

|          |               | Pin Nu                            | mber <sup>(1)</sup> |                                 |             |                |                                                                                                                                                                                    |

|----------|---------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                        |

| AN0      | 27            | 2                                 | 33                  | 19                              | I           | Analog         | Analog input channels.                                                                                                                                                             |

| AN1      | 28            | 3                                 | 34                  | 20                              | I           | Analog         |                                                                                                                                                                                    |

| AN2      | 1             | 4                                 | 35                  | 21                              | I           | Analog         |                                                                                                                                                                                    |

| AN3      | 2             | 5                                 | 36                  | 22                              | I           | Analog         |                                                                                                                                                                                    |

| AN4      | 3             | 6                                 | 1                   | 23                              | I           | Analog         |                                                                                                                                                                                    |

| AN5      | 4             | 7                                 | 2                   | 24                              | I           | Analog         |                                                                                                                                                                                    |

| AN6      | _             | _                                 | 3                   | 25                              | I           | Analog         |                                                                                                                                                                                    |

| AN7      | _             | _                                 | 4                   | 26                              | ı           | Analog         |                                                                                                                                                                                    |

| AN8      | _             | _                                 | _                   | 27                              | ı           | Analog         |                                                                                                                                                                                    |

| AN9      | 23            | 26                                | 29                  | 15                              | ı           | Analog         |                                                                                                                                                                                    |

| AN10     | 22            | 25                                | 28                  | 14                              | ı           | Analog         |                                                                                                                                                                                    |

| AN11     | 21            | 24                                | 27                  | 11                              | ı           | Analog         |                                                                                                                                                                                    |

| A N 14 O | 20(2)         | 23 <sup>(2)</sup>                 | 26 <sup>(2)</sup>   | 10 <sup>(2)</sup>               |             | A 1            |                                                                                                                                                                                    |

| AN12     | 20(2)         | 23(2)                             | 11 <sup>(3)</sup>   | 36 <sup>(3)</sup>               |             | Analog         |                                                                                                                                                                                    |

| CLKI     | 6             | 9                                 | 7                   | 30                              | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                             |

| CLKO     | 7             | 10                                | 8                   | 31                              | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1     | 6             | 9                                 | 7                   | 30                              | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                    |

| OSC2     | 7             | 10                                | 8                   | 31                              | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                           |

| SOSCI    | 8             | 11                                | 9                   | 33                              | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                     |

| SOSCO    | 9             | 12                                | 10                  | 34                              | 0           | _              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                    |

| REFCLKI  | PPS           | PPS                               | PPS                 | PPS                             | ı           | ST             | Reference Input Clock                                                                                                                                                              |

| REFCLKO  | PPS           | PPS                               | PPS                 | PPS                             | 0           | _              | Reference Output Clock                                                                                                                                                             |

| IC1      | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             | Capture Inputs 1-5                                                                                                                                                                 |

| IC2      | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             |                                                                                                                                                                                    |

| IC3      | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             |                                                                                                                                                                                    |

| IC4      | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             |                                                                                                                                                                                    |

| IC5      | PPS           | PPS                               | PPS                 | PPS                             | I           | ST             |                                                                                                                                                                                    |

**Legend:** CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

P = Power

TTL = TTL input buffer

O = Output PPS = Peripheral Pin Select I = Input

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

— = N/A

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                   | Pin Nu                            | mber <sup>(1)</sup> | •                               |             |                |                                                                         |

|----------|-------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|-------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                             |

| USBID    | 11 <sup>(3)</sup> | 14 <sup>(3)</sup>                 | 15 <sup>(3)</sup>   | 41(3)                           | ı           | ST             | USB OTG ID detect                                                       |

| CTED1    | 27                | 2                                 | 33                  | 19                              | I           | ST             | CTMU External Edge Input                                                |

| CTED2    | 28                | 3                                 | 34                  | 20                              | I           | ST             | 1                                                                       |

| CTED3    | 13                | 16                                | 17                  | 43                              | I           | ST             | 1                                                                       |

| CTED4    | 15                | 18                                | 19                  | 1                               | I           | ST             | 1                                                                       |

| CTED5    | 22                | 25                                | 28                  | 14                              | I           | ST             | 1                                                                       |

| CTED6    | 23                | 26                                | 29                  | 15                              | I           | ST             | 1                                                                       |

| CTED7    | _                 | _                                 | 20                  | 5                               | I           | ST             | 1                                                                       |

| CTED8    | _                 | _                                 | -                   | 13                              | I           | ST             | 1                                                                       |

| CTED9    | 9                 | 12                                | 10                  | 34                              | I           | ST             | 1                                                                       |

| CTED10   | 14                | 17                                | 18                  | 44                              | I           | ST             | 1                                                                       |

| CTED11   | 18                | 21                                | 24                  | 8                               | I           | ST             | 1                                                                       |

| CTED12   | 2                 | 5                                 | 36                  | 22                              | I           | ST             | 1                                                                       |

| CTED13   | 3                 | 6                                 | 1                   | 23                              | I           | ST             | 1                                                                       |

| CTPLS    | 21                | 24                                | 27                  | 11                              | 0           | _              | CTMU Pulse Output                                                       |

| PGED1    | 1                 | 4                                 | 35                  | 21                              | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 1          |

| PGEC1    | 2                 | 5                                 | 36                  | 22                              | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 1 |

| PGED2    | 18                | 21                                | 24                  | 8                               | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 2          |

| PGEC2    | 19                | 22                                | 25                  | 9                               | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 2 |

| PGED3    | 11 <sup>(2)</sup> | 14 <sup>(2)</sup>                 | 15 <sup>(2)</sup>   | 41 <sup>(2)</sup>               | I/O         | ST             | Data I/O pin for Programming/Debugging                                  |

| PGED3    | 27 <sup>(3)</sup> | 2 <sup>(3)</sup>                  | 33(3)               | 19 <sup>(3)</sup>               | 1/0         | 31             | Communication Channel 3                                                 |

| DCEC2    | 12 <sup>(2)</sup> | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup>   | 42 <sup>(2)</sup>               |             | ST             | Clock input pin for Programming/                                        |

| PGEC3    | 28 <sup>(3)</sup> | 3(3)                              | 34 <sup>(3)</sup>   | 20 <sup>(3)</sup>               | 1 '         | 31             | Debugging Communication Channel 3                                       |

| PGED4    | _                 | _                                 | 3                   | 12                              | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 4          |

| PGEC4    | _                 | _                                 | 4                   | 13                              | I           | ST             | Clock input pin for Programming/<br>Debugging Communication Channel 4   |

**Legend:** CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input P = Power O = Output I = Input PPS = Peripheral Pin Select <math>-= N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

TTL = TTL input buffer

3: Pin number for PIC32MX2XX devices only.

## 4.2 Bus Matrix Control Registers

## TABLE 4-2: BUS MATRIX REGISTER MAP

|                             | 22 4 2. Boo in ATTIMA (A 2010) 2. K in A |           |                    |       |       |       |       |       |      |      |      |              |      |           |           |           |            |          |               |

|-----------------------------|------------------------------------------|-----------|--------------------|-------|-------|-------|-------|-------|------|------|------|--------------|------|-----------|-----------|-----------|------------|----------|---------------|

| ress                        | _                                        | <u>o</u>  |                    |       |       |       |       |       |      |      |      | Bits         |      |           |           |           |            |          |               |

| Virtual Address<br>(BF88_#) | Register<br>Name                         | Bit Range | 31/15              | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6         | 21/5 | 20/4      | 19/3      | 18/2      | 17/1       | 16/0     | All<br>Resets |

| 2000                        | BMXCON <sup>(1)</sup>                    | 31:16     | _                  |       | _     | _     | _     | _     |      | _    |      | _            |      | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS   | BMXERRIS | 001F          |

| 2000                        | PINIYCOM, ,                              | 15:0      | _                  | _     | _     | _     | _     | _     | _    | _    | _    | BMXWSDRM     | _    | _         | _         | В         | MXARB<2:0> |          | 0041          |

| 2010                        | BMXDKPBA <sup>(1)</sup>                  | 31:16     | _                  | _     | _     | _     | _     | _     |      | _    | -    | _            | _    | _         | _         | _         | _          | _        | 0000          |

| 2010                        | BMXDKPBA                                 | 15:0      |                    |       |       |       |       |       |      |      | BM   | XDKPBA<15:0  | >    |           |           |           |            |          | 0000          |

| 2020                        | BMXDUDBA <sup>(1)</sup>                  | 31:16     | _                  | _     | _     | _     | _     | _     | _    | _    | -    | _            | _    | _         | _         | _         | _          | _        | 0000          |

| 2020                        | DIVINDUDBA: 7                            | 15:0      | BMXDUDBA<15:0>     |       |       |       |       |       |      |      |      | 0000         |      |           |           |           |            |          |               |

| 2030                        | BMXDUPBA <sup>(1)</sup>                  | 31:16     | _                  | _     | _     | _     | _     | _     | _    | _    | _    | _            | _    | _         | _         | _         | _          | _        | 0000          |

|                             | 5.1 1.5 6. 5. 1.                         | 15:0      | BMXDUPBA<15:0> 000 |       |       |       |       |       |      |      |      |              | 0000 |           |           |           |            |          |               |

| 2040                        | BMXDRMSZ                                 | 31:16     | BMXDRMSZ<31:0>     |       |       |       |       |       |      |      |      |              | xxxx |           |           |           |            |          |               |

|                             |                                          | 15:0      |                    |       |       |       | ı     |       |      | ı    |      |              |      |           | T         |           |            |          | XXXX          |

| 2050                        | BMXPUPBA <sup>(1)</sup>                  | 31:16     | _                  | _     | _     | _     | _     | _     | _    | _    | _    | _            | _    | _         |           | BMXPUPB/  | A<19:16>   |          | 0000          |

|                             |                                          | 15:0      |                    |       |       |       |       |       |      |      | BM   | XPUPBA<15:0  | >    |           |           |           |            |          | 0000          |

| 2060                        | BMXPFMSZ                                 | 31:16     |                    |       |       |       |       |       |      |      | BM   | XPFMSZ<31:0  | >    |           |           |           |            |          | XXXX          |

|                             |                                          | 15:0      |                    |       |       |       |       |       |      |      |      |              |      |           |           |           |            |          | XXXX          |

| 2070                        | BMXBOOTSZ                                | 31:16     |                    |       |       |       |       |       |      |      | BMX  | (BOOTSZ<31:0 | )>   |           |           |           |            |          | 0000          |

|                             |                                          | 15:0      |                    |       |       |       |       |       |      |      |      |              |      |           |           |           |            |          | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|              | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |

| 23:16        | _                 | _                 | _                 | BMX<br>ERRIXI     | BMX<br>ERRICD     | BMX<br>ERRDMA     | BMX<br>ERRDS     | BMX<br>ERRIS     |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|              | U-0               | R/W-1             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |

| 7:0          | _                 | BMX<br>WSDRM      | _                 | _                 | _                 | E                 | BMXARB<2:0       | >                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared

bit 31-21 Unimplemented: Read as '0'

bit 20 BMXERRIXI: Enable Bus Error from IXI bit

1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus

0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus

bit 19 BMXERRICD: Enable Bus Error from ICD Debug Unit bit

1 = Enable bus error exceptions for unmapped address accesses initiated from ICD

0 = Disable bus error exceptions for unmapped address accesses initiated from ICD

bit 18 BMXERRDMA: Bus Error from DMA bit

1 = Enable bus error exceptions for unmapped address accesses initiated from DMA

0 = Disable bus error exceptions for unmapped address accesses initiated from DMA

bit 17 BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)

1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access

0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access

bit 16 BMXERRIS: Bus Error from CPU Instruction Access bit (disabled in Debug mode)

1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access

0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access

bit 15-7 Unimplemented: Read as '0'

bit 6 BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit

1 = Data RAM accesses from CPU have one wait state for address setup

0 = Data RAM accesses from CPU have zero wait states for address setup

bit 5-3 Unimplemented: Read as '0'

bit 2-0 BMXARB<2:0>: Bus Matrix Arbitration Mode bits

111 = Reserved (using these Configuration modes will produce undefined behavior)

•

011 = Reserved (using these Configuration modes will produce undefined behavior)

010 = Arbitration Mode 2

001 = Arbitration Mode 1 (default)

000 = Arbitration Mode 0

#### REGISTER 10-4: U10TGCON: USB OTG CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | -                 |                   | 1                 | -                 | -                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 |                   |                   | _                 | _                | -                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG          | VBUSDIS          |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 **DPPULUP:** D+ Pull-Up Enable bit

1 = D+ data line pull-up resistor is enabled

0 = D+ data line pull-up resistor is disabled

bit 6 **DMPULUP:** D- Pull-Up Enable bit

1 = D- data line pull-up resistor is enabled

0 = D- data line pull-up resistor is disabled

bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

1 = D+ data line pull-down resistor is enabled

0 = D+ data line pull-down resistor is disabled

bit 4 DMPULDWN: D- Pull-Down Enable bit

1 = D- data line pull-down resistor is enabled

0 = D- data line pull-down resistor is disabled

bit 3 VBUSON: VBUS Power-on bit

1 = VBUS line is powered

0 = VBUS line is not powered

bit 2 OTGEN: OTG Functionality Enable bit

1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

bit 1 VBUSCHG: VBUS Charge Enable bit

1 = VBUS line is charged through a pull-up resistor

0 = VBUS line is not charged through a resistor

bit 0 VBUSDIS: VBUS Discharge Enable bit

1 = VBUS line is discharged through a pull-down resistor

0 = VBUS line is not discharged through a resistor

## 11.1 Parallel I/O (PIO) Ports

All port pins have 10 registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

#### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx, and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the "Pin Diagrams" section for the available pins and their functionality.

# 11.1.2 CONFIGURING ANALOG AND DIGITAL PORT PINS

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSEL and TRIS bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

If the TRIS bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 11.1.3 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP.

#### 11.1.4 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports allows the PIC32MX1XX/2XX 28/36/44-pin Family devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a change-of-state.

Five control registers are associated with the CN functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

**Note:** Pull-ups and pull-downs on change notification pins should always be disabled when the port pin is configured as a digital output.

An additional control register (CNCONx) is shown in Register 11-3.

## 11.2 CLR, SET and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR, or INV register, the base register must be read.

TABLE 11-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits   | RPnR Value to Peripheral Selection          |

|--------------|----------|-------------|---------------------------------------------|

| RPA0         | RPA0R    | RPA0R<3:0>  | 0000 = No Connect                           |

| RPB3         | RPB3R    | RPB3R<3:0>  | 0001 = <u>U1TX</u><br>0010 = <u>U2RTS</u>   |

| RPB4         | RPB4R    | RPB4R<3:0>  | 0011 = SS1                                  |

| RPB15        | RPB15R   | RPB15R<3:0> | 0100 = Reserved<br>0101 = OC1               |

| RPB7         | RPB7R    | RPB7R<3:0>  | 0110 = Reserved<br>0111 = C2OUT             |

| RPC7         | RPC7R    | RPC7R<3:0>  | 1000 = Reserved                             |

| RPC0         | RPC0R    | RPC0R<3:0>  | :                                           |

| RPC5         | RPC5R    | RPC5R<3:0>  | •<br>1111 = Reserved                        |

| RPA1         | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                           |

| RPB5         | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPB1         | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                 |

| RPB11        | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                   |

| RPB8         | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                             |

| RPA8         | RPA8R    | RPA8R<3:0>  | 0111 = C3OUT                                |

| RPC8         | RPC8R    | RPC8R<3:0>  | <b></b> :                                   |

| RPA9         | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                             |

| RPA2         | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                           |

| RPB6         | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPA4         | RPA4R    | RPA4R<3:0>  | 0011 = SDO1<br>0100 = SDO2                  |

| RPB13        | RPB13R   | RPB13R<3:0> | 0101 = OC4                                  |

| RPB2         | RPB2R    | RPB2R<3:0>  | 0110 = OC5<br>0111 = REFCLKO                |

| RPC6         | RPC6R    | RPC6R<3:0>  | 1000 = Reserved                             |

| RPC1         | RPC1R    | RPC1R<3:0>  | :                                           |

| RPC3         | RPC3R    | RPC3R<3:0>  | 1111 = Reserved                             |

| RPA3         | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                           |

| RPB14        | RPB14R   | RPB14R<3:0> | 0001 = U1RTS<br>0010 = U2TX                 |

| RPB0         | RPB0R    | RPB0R<3:0>  | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |

| RPB10        | RPB10R   | RPB10R<3:0> | 0101 = OC3                                  |

| RPB9         | RPB9R    | RPB9R<3:0>  | 0110 = Reserved<br>0111 = C1OUT             |

| RPC9         | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                             |

| RPC2         | RPC2R    | RPC2R<3:0>  | <b></b> :                                   |

| RPC4         | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                             |

## REGISTER 11-3: CNCONx: CHANGE NOTICE CONTROL FOR PORTX REGISTER (x = A, B, C)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | -                 | _                 |                   | _                 |                  | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 | _                 | _                | -                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ON: Change Notice (CN) Control ON bit

1 = CN is enabled0 = CN is disabled

bit 14 **Unimplemented:** Read as '0' bit 13 **SIDL:** Stop in Idle Control bit

1 = Idle mode halts CN operation0 = Idle does not affect CN operation

bit 12-0 Unimplemented: Read as '0'

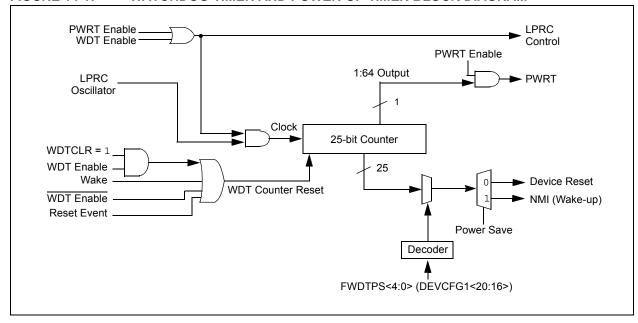

## 14.0 WATCHDOG TIMER (WDT)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 9. "Watchdog, Deadman, and Power-up Timers"** (DS60001114), which are available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are some of the key features of the WDT module:

- · Configuration or software controlled

- · User-configurable time-out period

- · Can wake the device from Sleep or Idle mode

Figure 14-1 illustrates a block diagram of the WDT and Power-up timer.

FIGURE 14-1: WATCHDOG TIMER AND POWER-UP TIMER BLOCK DIAGRAM

#### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0       |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 31.24        | _                    |                   | _                 | _                 | _                        | _                 | _                | -                      |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 23.10        | _                    | _                 | _                 | _                 | _                        | _                 | _                | _                      |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                  |

| 15.6         | SPISGNEXT            | _                 | _                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                 |

| 7.0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                  |

| 7:0          | AUDEN <sup>(1)</sup> | _                 | _                 | _                 | AUDMONO <sup>(1,2)</sup> | _                 | AUDMOD           | <1:0> <sup>(1,2)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

1 = Data from RX FIFO is sign extended

0 = Data from RX FIFO is not sign extended

bit 14-13 Unimplemented: Read as '0'

bit 12 **FRMERREN:** Enable Interrupt Events via FRMERR bit

1 = Frame Error overflow generates error events

0 = Frame Error does not generate error events

bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

1 = Receive overflow generates error events

0 = Receive overflow does not generate error events

bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit

1 = Transmit underrun generates error events

0 = Transmit underrun does not generate error events

bit 9 **IGNROV:** Ignore Receive Overflow bit (for Audio Data Transmissions)

1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data

0 = A ROV is a critical error that stops SPI operation

bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

0 = A TUR is a critical error that stops SPI operation

bit 7 AUDEN: Enable Audio CODEC Support bit (1)

1 = Audio protocol enabled

0 = Audio protocol disabled

bit 6-5 Unimplemented: Read as '0'

bit 3 **AUDMONO:** Transmit Audio Data Format bit<sup>(1,2)</sup>

1 = Audio data is mono (Each data word is transmitted on both left and right channels)

0 = Audio data is stereo

bit 2 **Unimplemented:** Read as '0'

bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit(1,2)

11 = PCM/DSP mode

10 = Right-Justified mode

01 = Left-Justified mode

$00 = I^2S \text{ mode}$

**Note 1:** This bit can only be written when the ON bit = 0.

2: This bit is only valid for AUDEN = 1.

# 18.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 24.** "InterIntegrated Circuit (I<sup>2</sup>C)" (DS60001116), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The  $\rm I^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $\rm I^2C$  serial communication standard. Figure 18-1 illustrates the  $\rm I^2C$  module block diagram.

Each I<sup>2</sup>C module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

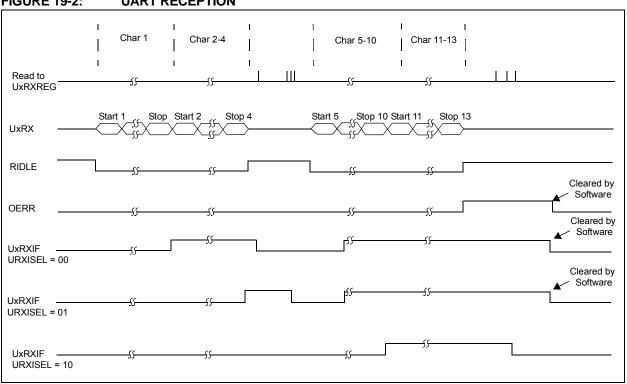

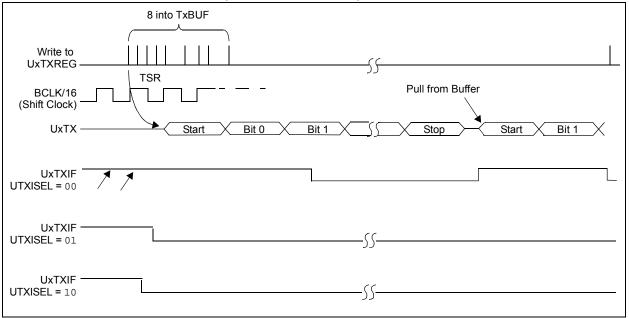

Figure 19-2 and Figure 19-3 illustrate typical receive and transmit timing for the UART module.

FIGURE 19-2: UART RECEPTION

FIGURE 19-3: TRANSMISSION (8-BIT OR 9-BIT DATA)

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- · On any form of device Reset

- · On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

#### 26.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator start-up delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN (OSCCON<4>) bit is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- · On any form of device Reset

- On a WDT time-out interrupt

# 26.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The Peripheral Bus can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as the USB, Interrupt Controller, DMA, and the bus matrix are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

# 26.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- · Control register lock sequence

- · Configuration bit select lock

### 26.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, PMDLOCK (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6. "Oscillator"** (DS60001112) in the "PIC32 Family Reference Manual" for details.

### 26.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The Configuration bit, PMDL1WAY (DEVCFG3<28>), blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

### REGISTER 27-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

- bit 15-14 FCKSM<1:0>: Clock Switching and Monitor Selection Configuration bits

- 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

- 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

- 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

- bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output disabled

- 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

- bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary Oscillator is disabled

- 10 = HS Oscillator mode is selected

- 01 = XT Oscillator mode is selected

- 00 = External Clock mode is selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 Reserved: Write '1'

- bit 5 FSOSCEN: Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 **Reserved:** Write '1'

- bit 2-0 FNOSC<2:0>: Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT. HS. EC)(1)

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

TABLE 30-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

| DC CHA        | ARACTER | RISTICS                                                 | stated)         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) $ -40^{\circ}C \leq TA \leq +85^{\circ}C \text{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \text{ for V-temp} $ |            |       |                                                                                                                      |  |  |  |

|---------------|---------|---------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param.<br>No. | Symbol  | Characteristics                                         | Min.            | Typical <sup>(1)</sup>                                                                                                                                                                                | Max.       | Units | Conditions                                                                                                           |  |  |  |

|               | VIL     | Input Low Voltage                                       |                 |                                                                                                                                                                                                       |            |       |                                                                                                                      |  |  |  |

| DI10          |         | I/O Pins with PMP                                       | Vss             | _                                                                                                                                                                                                     | 0.15 VDD   | V     |                                                                                                                      |  |  |  |

|               |         | I/O Pins                                                | Vss             | _                                                                                                                                                                                                     | 0.2 VDD    | V     |                                                                                                                      |  |  |  |

| DI18          |         | SDAx, SCLx                                              | Vss             | _                                                                                                                                                                                                     | 0.3 VDD    | V     | SMBus disabled (Note 4)                                                                                              |  |  |  |

| DI19          |         | SDAx, SCLx                                              | Vss             | _                                                                                                                                                                                                     | 0.8        | V     | SMBus enabled (Note 4)                                                                                               |  |  |  |

|               | VIH     | Input High Voltage                                      |                 |                                                                                                                                                                                                       |            |       |                                                                                                                      |  |  |  |

| DI20          |         | I/O Pins not 5V-tolerant <sup>(5)</sup>                 | 0.65 VDD        | _                                                                                                                                                                                                     | VDD        | V     | (Note 4,6)                                                                                                           |  |  |  |

|               |         | I/O Pins 5V-tolerant with PMP <sup>(5)</sup>            | 0.25 VDD + 0.8V | _                                                                                                                                                                                                     | 5.5        | V     | (Note 4,6)                                                                                                           |  |  |  |

|               |         | I/O Pins 5V-tolerant(5)                                 | 0.65 VDD        | _                                                                                                                                                                                                     | 5.5        | V     |                                                                                                                      |  |  |  |

| DI28          |         | SDAx, SCLx                                              | 0.65 VDD        | _                                                                                                                                                                                                     | 5.5        | V     | SMBus disabled (Note 4,6)                                                                                            |  |  |  |

| DI29          |         | SDAx, SCLx                                              | 2.1             | _                                                                                                                                                                                                     | 5.5        | V     | SMBus enabled, $2.3V \le VPIN \le 5.5$ (Note 4,6)                                                                    |  |  |  |

| DI30          | ICNPU   | Change Notification Pull-up Current                     | _               | _                                                                                                                                                                                                     | -50        | μА    | VDD = 3.3V, VPIN = VSS (Note 3,6)                                                                                    |  |  |  |

| DI31          | ICNPD   | Change Notification<br>Pull-down Current <sup>(4)</sup> | _               | _                                                                                                                                                                                                     | -50        | μA    | VDD = 3.3V, VPIN = VDD                                                                                               |  |  |  |

|               | liL     | Input Leakage Current (Note 3)                          |                 |                                                                                                                                                                                                       |            |       |                                                                                                                      |  |  |  |

| DI50          |         | I/O Ports                                               | _               | _                                                                                                                                                                                                     | <u>+</u> 1 | μΑ    | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance                                                                           |  |  |  |

| DI51          |         | Analog Input Pins                                       | _               | _                                                                                                                                                                                                     | <u>+</u> 1 | μΑ    | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance                                                                           |  |  |  |

| DI55          |         | MCLR <sup>(2)</sup>                                     | _               | _                                                                                                                                                                                                     | <u>+</u> 1 | μΑ    | $Vss \leq Vpin \leq Vdd$                                                                                             |  |  |  |

| DI56          |         | OSC1                                                    | _               | _                                                                                                                                                                                                     | <u>+</u> 1 | μΑ    | $\label{eq:VSS} \begin{array}{l} \text{VSS} \leq \text{VPIN} \leq \text{VDD}, \\ \text{XT and HS modes} \end{array}$ |  |  |  |

- **Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Pin Diagrams" section for the 5V-tolerant pins.

- **6:** The Vih specifications are only in relation to externally applied inputs, and not with respect to the user-selectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum Vih of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

# 30.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC32MX1XX/2XX 28/36/44-pin Family AC characteristics and timing parameters.

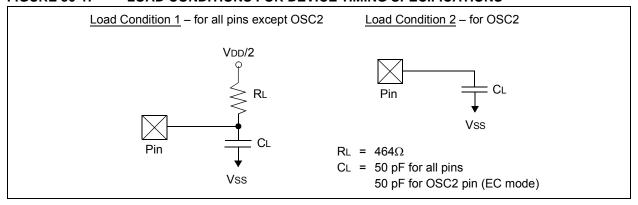

### FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

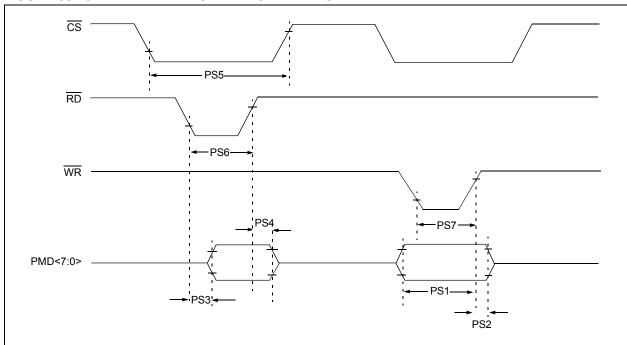

#### TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| TABLE OF TO. OAL AGITAL LOADING REGULATION OF COTT OF THE |        |                       |                                                                                                                                                                                                                                                |                        |      |       |                          |

|-----------------------------------------------------------|--------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------------|

| AC CHARACTERISTICS                                        |        |                       | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                        |      |       |                          |

| Param.<br>No.                                             | Symbol | Characteristics       | Min.                                                                                                                                                                                                                                           | Typical <sup>(1)</sup> | Max. | Units | Conditions               |

| DO56                                                      | Сю     | All I/O pins and OSC2 | _                                                                                                                                                                                                                                              | _                      | 50   | pF    | EC mode                  |

| DO58                                                      | Св     | SCLx, SDAx            | _                                                                                                                                                                                                                                              | _                      | 400  | pF    | In I <sup>2</sup> C mode |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

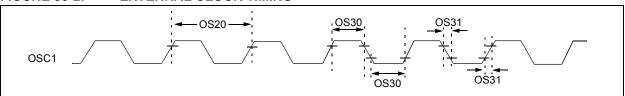

### FIGURE 30-2: EXTERNAL CLOCK TIMING

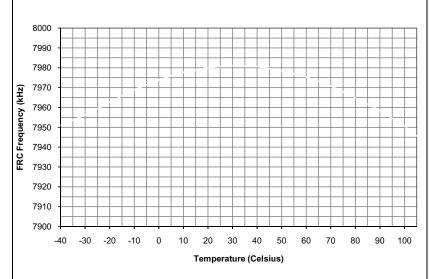

**FIGURE 32-7:** TYPICAL LPRC FREQUENCY @ VDD = 3.3V

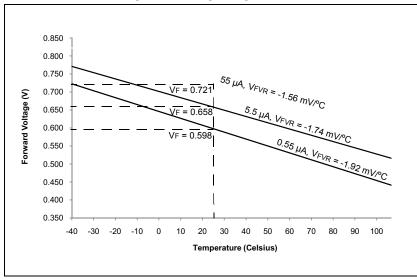

#### **FIGURE 32-8:** TYPICAL CTMU TEMPERATURE DIODE **FORWARD VOLTAGE**