Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

|                            |                                                                                 |

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                 |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f032bt-v-so |

#### TABLE 8: PIN NAMES FOR 36-PIN USB DEVICES

**36-PIN VTLA (TOP VIEW)**(1,2,3,5)

PIC32MX210F016C PIC32MX220F032C PIC32MX230F064C PIC32MX250F128C

36

1

| Pin# | Full Pin Name                             |

|------|-------------------------------------------|

| 1    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2    | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3    | PGED4 <sup>(4)</sup> /AN6/RPC0/RC0        |

| 4    | PGEC4 <sup>(4)</sup> /AN7/RPC1/RC1        |

| 5    | VDD                                       |

| 6    | Vss                                       |

| 7    | OSC1/CLKI/RPA2/RA2                        |

| 8    | OSC2/CLKO/RPA3/PMA0/RA3                   |

| 9    | SOSCI/RPB4/RB4                            |

| 10   | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4            |

| 11   | AN12/RPC3/RC3                             |

| 12   | Vss                                       |

| 13   | VDD                                       |

| 14   | VDD                                       |

| 15   | TMS/RPB5/USBID/RB5                        |

| 16   | VBUS                                      |

| 17   | TDI/RPB7/CTED3/PMD5/INT0/RB7              |

| 18   | TCK/RPB8/SCL1/CTED10/PMD4/RB8             |

| Pin# | Full Pin Name                                    |

|------|--------------------------------------------------|

| 19   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 20   | RPC9/CTED7/RC9                                   |

| 21   | Vss                                              |

| 22   | VCAP                                             |

| 23   | VDD                                              |

| 24   | PGED2/RPB10/D+/CTED11/RB10                       |

| 25   | PGEC2/RPB11/D-/RB11                              |

| 26   | Vusb3v3                                          |

| 27   | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 28   | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 29   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 30   | AVss                                             |

| 31   | AVDD                                             |

| 32   | MCLR                                             |

| 33   | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 34   | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

| 35   | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        |

| 36   | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and **Section 11.3** "**Peripheral Pin Select**" for restrictions.

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: This pin function is not available on PIC32MX210F016C and PIC32MX120F032C devices.

- 5: Shaded pins are 5V tolerant.

#### **Table of Contents**

| 1.0   | Device Overview                                    | 19  |

|-------|----------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 32-bit MCUs.   |     |

| 3.0   | CPU.                                               |     |

| 4.0   | Memory Organization                                |     |

| 5.0   | Flash Program Memory                               |     |

| 6.0   | Resets                                             |     |

| 7.0   | Interrupt Controller                               |     |

| 8.0   | Oscillator Configuration                           | 73  |

| 9.0   | Direct Memory Access (DMA) Controller              | 83  |

| 10.0  | USB On-The-Go (OTG)                                | 103 |

| 11.0  | I/O Ports                                          | 127 |

| 12.0  | Timer1                                             | 143 |

| 13.0  | Timer2/3, Timer4/5                                 | 147 |

| 14.0  | Watchdog Timer (WDT)                               | 153 |

| 15.0  | Input Capture                                      | 157 |

|       | Output Compare                                     |     |

| 17.0  | Serial Peripheral Interface (SPI)                  | 165 |

| 18.0  | Inter-Integrated Circuit (I <sup>2</sup> C)        |     |

| 19.0  | Universal Asynchronous Receiver Transmitter (UART) | 181 |

|       | Parallel Master Port (PMP)                         |     |

|       | Real-Time Clock and Calendar (RTCC)                |     |

| 22.0  | 10-bit Analog-to-Digital Converter (ADC)           | 209 |

| 23.0  | Comparator                                         |     |

| 24.0  | Comparator Voltage Reference (CVREF)               | 223 |

| 25.0  | Charge Time Measurement Unit (CTMU)                | 227 |

| 26.0  | Power-Saving Features                              | 233 |

| 27.0  | Special Features                                   | 239 |

| 28.0  | Instruction Set                                    |     |

| 29.0  | Development Support                                | 253 |

|       | Electrical Characteristics                         |     |

|       | 50 MHz Electrical Characteristics                  |     |

|       | DC and AC Device Characteristics Graphs            |     |

|       | Packaging Information                              |     |

|       | Aicrochip Web Site                                 |     |

|       | omer Change Notification Service                   |     |

|       | omer Support                                       |     |

| Produ | uct Identification System                          | 342 |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                   | Pin Nu                            | mber <sup>(1)</sup> | •                               |             |                |                                                                         |

|----------|-------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|-------------------------------------------------------------------------|

| Pin Name | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                             |

| USBID    | 11 <sup>(3)</sup> | 14 <sup>(3)</sup>                 | 15 <sup>(3)</sup>   | 41(3)                           | ı           | ST             | USB OTG ID detect                                                       |

| CTED1    | 27                | 2                                 | 33                  | 19                              | I           | ST             | CTMU External Edge Input                                                |

| CTED2    | 28                | 3                                 | 34                  | 20                              | I           | ST             | 1                                                                       |

| CTED3    | 13                | 16                                | 17                  | 43                              | I           | ST             | 1                                                                       |

| CTED4    | 15                | 18                                | 19                  | 1                               | I           | ST             | 1                                                                       |

| CTED5    | 22                | 25                                | 28                  | 14                              | I           | ST             | 1                                                                       |

| CTED6    | 23                | 26                                | 29                  | 15                              | I           | ST             | 1                                                                       |

| CTED7    | _                 | _                                 | 20                  | 5                               | I           | ST             | 1                                                                       |

| CTED8    | _                 | _                                 | -                   | 13                              | I           | ST             | 1                                                                       |

| CTED9    | 9                 | 12                                | 10                  | 34                              | I           | ST             | 1                                                                       |

| CTED10   | 14                | 17                                | 18                  | 44                              | I           | ST             | 1                                                                       |

| CTED11   | 18                | 21                                | 24                  | 8                               | I           | ST             | 1                                                                       |

| CTED12   | 2                 | 5                                 | 36                  | 22                              | I           | ST             | 1                                                                       |

| CTED13   | 3                 | 6                                 | 1                   | 23                              | I           | ST             | 1                                                                       |

| CTPLS    | 21                | 24                                | 27                  | 11                              | 0           | _              | CTMU Pulse Output                                                       |

| PGED1    | 1                 | 4                                 | 35                  | 21                              | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 1          |

| PGEC1    | 2                 | 5                                 | 36                  | 22                              | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 1 |

| PGED2    | 18                | 21                                | 24                  | 8                               | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 2          |

| PGEC2    | 19                | 22                                | 25                  | 9                               | I           | ST             | Clock input pin for<br>Programming/Debugging<br>Communication Channel 2 |

| PGED3    | 11 <sup>(2)</sup> | 14 <sup>(2)</sup>                 | 15 <sup>(2)</sup>   | 41 <sup>(2)</sup>               | I/O         | ST             | Data I/O pin for Programming/Debugging                                  |

| PGED3    | 27 <sup>(3)</sup> | 2 <sup>(3)</sup>                  | 33(3)               | 19 <sup>(3)</sup>               | 1/0         | 31             | Communication Channel 3                                                 |

| DCEC2    | 12 <sup>(2)</sup> | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup>   | 42 <sup>(2)</sup>               |             | ST             | Clock input pin for Programming/                                        |

| PGEC3    | 28 <sup>(3)</sup> | 3(3)                              | 34 <sup>(3)</sup>   | 20 <sup>(3)</sup>               | 1 '         | 31             | Debugging Communication Channel 3                                       |

| PGED4    | _                 | _                                 | 3                   | 12                              | I/O         | ST             | Data I/O pin for Programming/Debugging Communication Channel 4          |

| PGEC4    | _                 | _                                 | 4                   | 13                              | I           | ST             | Clock input pin for Programming/<br>Debugging Communication Channel 4   |

**Legend:** CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input O = Output P = Power I = Input

TTL = TTL input buffer

PPS = Peripheral Pin Select

--=N/A

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

2: Pin number for PIC32MX1XX devices only.

**3:** Pin number for PIC32MX2XX devices only.

### 6.1 Reset Control Registers

### TABLE 6-1: RESET CONTROL REGISTER MAP

| ess                       |                                 |           |       | Bits  |       |       |       |       |      |       |      |      |      |      | 8     |      |      |       |            |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|------|-------|------|------|-------|------------|

| Virtual Addrı<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1 | 16/0  | All Resets |

| F600                      | RCON                            | 31:16     | _     | _     |       | _     | _     | _     |      | _     | _    | _    |      |      |       |      | _    | _     | 0000       |

| F600                      | RCON                            | 15:0      |       | _     | _     | _     | _     | _     | CMR  | VREGS | EXTR | SWR  | _    | WDTO | SLEEP | IDLE | BOR  | POR   | XXXX(2)    |

| F640                      | RSWRST                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _     | _    | _    | _    | _    | _     | _    | _    | _     | 0000       |

| F010                      | KSWKSI                          | 15:0      | _     | _     | _     | _     | _     | _     | I    | _     | _    | _    |      | _    | _     | _    | _    | SWRST | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

#### REGISTER 10-4: U10TGCON: USB OTG CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | -                 | _                 | -                 | _                 | _                 | -                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG          | VBUSDIS          |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 **DPPULUP:** D+ Pull-Up Enable bit

1 = D+ data line pull-up resistor is enabled

0 = D+ data line pull-up resistor is disabled

bit 6 **DMPULUP:** D- Pull-Up Enable bit

1 = D- data line pull-up resistor is enabled

0 = D- data line pull-up resistor is disabled

bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

1 = D+ data line pull-down resistor is enabled

0 = D+ data line pull-down resistor is disabled

bit 4 DMPULDWN: D- Pull-Down Enable bit

1 = D- data line pull-down resistor is enabled

0 = D- data line pull-down resistor is disabled

bit 3 VBUSON: VBUS Power-on bit

1 = VBUS line is powered

0 = VBUS line is not powered

bit 2 OTGEN: OTG Functionality Enable bit

1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

bit 1 VBUSCHG: VBUS Charge Enable bit

1 = VBUS line is charged through a pull-up resistor

0 = VBUS line is not charged through a resistor

bit 0 VBUSDIS: VBUS Discharge Enable bit

1 = VBUS line is discharged through a pull-down resistor

0 = VBUS line is not discharged through a resistor

TABLE 11-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits   | RPnR Value to Peripheral Selection          |

|--------------|----------|-------------|---------------------------------------------|

| RPA0         | RPA0R    | RPA0R<3:0>  | 0000 = No Connect                           |

| RPB3         | RPB3R    | RPB3R<3:0>  | 0001 = <u>U1TX</u><br>0010 = <u>U2RTS</u>   |

| RPB4         | RPB4R    | RPB4R<3:0>  | 0011 = SS1                                  |

| RPB15        | RPB15R   | RPB15R<3:0> | 0100 = Reserved<br>0101 = OC1               |

| RPB7         | RPB7R    | RPB7R<3:0>  | 0110 = Reserved<br>0111 = C2OUT             |

| RPC7         | RPC7R    | RPC7R<3:0>  | 1000 = Reserved                             |

| RPC0         | RPC0R    | RPC0R<3:0>  | :                                           |

| RPC5         | RPC5R    | RPC5R<3:0>  | •<br>1111 = Reserved                        |

| RPA1         | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                           |

| RPB5         | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPB1         | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                 |

| RPB11        | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                   |

| RPB8         | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                             |

| RPA8         | RPA8R    | RPA8R<3:0>  | 0111 = C3OUT                                |

| RPC8         | RPC8R    | RPC8R<3:0>  | <b></b> :                                   |

| RPA9         | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                             |

| RPA2         | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                           |

| RPB6         | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPA4         | RPA4R    | RPA4R<3:0>  | 0011 = SDO1<br>0100 = SDO2                  |

| RPB13        | RPB13R   | RPB13R<3:0> | 0101 = OC4                                  |

| RPB2         | RPB2R    | RPB2R<3:0>  | 0110 = OC5<br>0111 = REFCLKO                |

| RPC6         | RPC6R    | RPC6R<3:0>  | 1000 = Reserved                             |

| RPC1         | RPC1R    | RPC1R<3:0>  | :                                           |

| RPC3         | RPC3R    | RPC3R<3:0>  | 1111 = Reserved                             |

| RPA3         | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                           |

| RPB14        | RPB14R   | RPB14R<3:0> | 0001 = U1RTS<br>0010 = U2TX                 |

| RPB0         | RPB0R    | RPB0R<3:0>  | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |

| RPB10        | RPB10R   | RPB10R<3:0> | 0101 = OC3                                  |

| RPB9         | RPB9R    | RPB9R<3:0>  | 0110 = Reserved<br>0111 = C1OUT             |

| RPC9         | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                             |

| RPC2         | RPC2R    | RPC2R<3:0>  | <b></b> :                                   |

| RPC4         | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                             |

#### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0       |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 31.24        | _                    |                   | _                 | _                 | -                        | _                 |                  |                        |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 23.10        | _                    |                   | _                 | _                 | _                        | _                 | _                | _                      |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                  |

| 15.6         | SPISGNEXT            | _                 | _                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                 |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                  |

| 7:0          | AUDEN <sup>(1)</sup> |                   | _                 | _                 | AUDMONO <sup>(1,2)</sup> | _                 | AUDMOD           | <1:0> <sup>(1,2)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

1 = Data from RX FIFO is sign extended

0 = Data from RX FIFO is not sign extended

bit 14-13 Unimplemented: Read as '0'

bit 12 **FRMERREN:** Enable Interrupt Events via FRMERR bit

1 = Frame Error overflow generates error events

0 = Frame Error does not generate error events

bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

1 = Receive overflow generates error events

0 = Receive overflow does not generate error events

bit 10 **SPITUREN:** Enable Interrupt Events via SPITUR bit

1 = Transmit underrun generates error events

0 = Transmit underrun does not generate error events

bit 9 **IGNROV:** Ignore Receive Overflow bit (for Audio Data Transmissions)

1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data

0 = A ROV is a critical error that stops SPI operation

bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

0 = A TUR is a critical error that stops SPI operation

bit 7 AUDEN: Enable Audio CODEC Support bit (1)

1 = Audio protocol enabled

0 = Audio protocol disabled

bit 6-5 Unimplemented: Read as '0'

bit 3 **AUDMONO:** Transmit Audio Data Format bit<sup>(1,2)</sup>

1 = Audio data is mono (Each data word is transmitted on both left and right channels)

0 = Audio data is stereo

bit 2 **Unimplemented:** Read as '0'

bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit(1,2)

11 = PCM/DSP mode

10 = Right-Justified mode

01 = Left-Justified mode

$00 = I^2S \text{ mode}$

**Note 1:** This bit can only be written when the ON bit = 0.

2: This bit is only valid for AUDEN = 1.

### REGISTER 18-1: I2CXCON: I<sup>2</sup>C CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 | -                 | -                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

**Legend:** HC = Cleared in Hardware

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

1 = Enables the I<sup>2</sup>C module and configures the SDA and SCL pins as serial port pins

$0 = \text{Disables the } I^2\text{C module}$ ; all  $I^2\text{C pins are controlled by PORT functions}$

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12 **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

1 = Release SCLx clock

0 = Hold SCLx clock low (clock stretch)

#### If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

#### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule not enabled

- bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control disabled

- 0 = Slew rate control enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| PIC32M | PIC32MX1XX/2XX 28/36/44-PIN FAMILY |  |  |  |  |  |  |  |  |

|--------|------------------------------------|--|--|--|--|--|--|--|--|

| NOTES: |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

|        |                                    |  |  |  |  |  |  |  |  |

| PIC32MX1XX/2XX 28/36/44-PIN FAMILY |  |                |                      |                             |                             |  |  |

|------------------------------------|--|----------------|----------------------|-----------------------------|-----------------------------|--|--|

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  |                |                      |                             |                             |  |  |

|                                    |  | 1XX/2XX 28/36/ | 1XX/2XX 28/36/44-PIN | 1XX/2XX 28/36/44-PIN FAMILY | 1XX/2XX 28/36/44-PIN FAMILY |  |  |

#### REGISTER 27-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2     | Bit<br>25/17/9/1        | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|----------------------|-----------------------|-------------------------|------------------|--|

| 31:24        | r-0               | r-1               | r-1               | R/P               | r-1                  | r-1                   | r-1                     | R/P              |  |

| 31.24        | _                 | _                 | _                 | CP                | _                    | _                     | _                       | BWP              |  |

| 22:40        | r-1               | r-1               | r-1               | r-1               | r-1                  | R/P                   | R/P                     | R/P              |  |

| 23:16        | _                 | _                 | _                 | _                 | _                    | ı                     | PWP<8:6> <sup>(3)</sup> |                  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P                  | R/P                   | r-1                     | r-1              |  |

| 15:8         | PWP<5:0>          |                   |                   |                   |                      |                       | _                       | _                |  |

| 7.0          | r-1               | r-1               | r-1               | R/P               | R/P                  | R/P                   | R/P                     | R/P              |  |

| 7:0          | _                 | _                 | _                 | ICESEL            | <1:0> <sup>(2)</sup> | JTAGEN <sup>(1)</sup> | DEBUG<1:0>              |                  |  |

Legend:r = Reserved bitP = Programmable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31 Reserved: Write '0' bit 30-29 Reserved: Write '1' bit 28 CP: Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external programming device.

1 = Protection is disabled0 = Protection is enabled

bit 27-25 Reserved: Write '1'

bit 24 **BWP:** Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

1 = Boot Flash is writable0 = Boot Flash is not writable

bit 23-19 Reserved: Write '1'

Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

- 2: The PGEC4/PGED4 pin pair is not available on all devices. Refer to the "Pin Diagrams" section for availability.

- **3:** The PWP<8:7> bits are only available on devices with 256 KB Flash.

#### TABLE 30-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHA                     | ARACTER | ISTICS                                                           | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +105^{\circ}\text{C}$ for V-temp |      |       |       |            |  |  |

|----------------------------|---------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|------------|--|--|

| Param. No. Characteristics |         |                                                                  | Min.                                                                                                                                                                                                                                           | Тур. | Max.  | Units | Conditions |  |  |

| Operating Voltage          |         |                                                                  |                                                                                                                                                                                                                                                |      |       |       |            |  |  |

| DC10                       | VDD     | Supply Voltage (Note 2)                                          | 2.3                                                                                                                                                                                                                                            | _    | 3.6   | V     | _          |  |  |

| DC12                       | VDR     | RAM Data Retention Voltage (Note 1)                              | 1.75                                                                                                                                                                                                                                           | _    | _     | V     | _          |  |  |

| DC16                       | VPOR    | VDD Start Voltage<br>to Ensure Internal Power-on Reset<br>Signal | 1.75                                                                                                                                                                                                                                           | _    | 2.1   | V     | _          |  |  |

| DC17                       | SVDD    | VDD Rise Rate<br>to Ensure Internal Power-on Reset<br>Signal     | 0.00005                                                                                                                                                                                                                                        | _    | 0.115 | V/μs  | _          |  |  |

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

<sup>2:</sup> Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 30-11 for BOR values.

#### TABLE 30-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHARACTERISTICS           |     |                             | (unless            | otherwi | se state | pnditions: 2.3V to 3.6V ed) $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                          |  |

|------------------------------|-----|-----------------------------|--------------------|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|

| Param. Symbol Characteristic |     |                             | Min.               | Тур.    | Max.     | Units                                                                                                                                                                          | Conditions               |  |

| DO10                         | VoL | Output Low Voltage I/O Pins | _                  | _       | 0.4      | V                                                                                                                                                                              | IOL ≤ 10 mA, VDD = 3.3V  |  |

|                              |     | Output High Voltage         | 1.5 <sup>(1)</sup> |         | _        |                                                                                                                                                                                | IOH ≥ -14 mA, VDD = 3.3V |  |

| DO20                         | Vou | I/O Pins                    | 2.0 <sup>(1)</sup> |         | _        | V                                                                                                                                                                              | IOH ≥ -12 mA, VDD = 3.3V |  |

| DO20                         | Vон |                             | 2.4                | _       | _        | V                                                                                                                                                                              | IOH ≥ -10 mA, VDD = 3.3V |  |

|                              |     |                             | 3.0(1)             | _       | _        |                                                                                                                                                                                | IOH ≥ -7 mA, VDD = 3.3V  |  |

Note 1: Parameters are characterized, but not tested.

#### TABLE 30-11: ELECTRICAL CHARACTERISTICS: BOR

| TABLE 30-11. ELECTRICAL CHARACTERISTICS. BOX |        |                                                        |                                                                                                                                                                                                                                                |         |      |       |            |  |  |  |

|----------------------------------------------|--------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|

| DC CHARACTERISTICS                           |        |                                                        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |         |      |       |            |  |  |  |

| Param.<br>No.                                | Symbol | Characteristics                                        | Min. <sup>(1)</sup>                                                                                                                                                                                                                            | Typical | Max. | Units | Conditions |  |  |  |

| BO10                                         | VBOR   | BOR Event on VDD transition high-to-low <sup>(2)</sup> | 2.0                                                                                                                                                                                                                                            | _       | 2.3  | V     | _          |  |  |  |

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

<sup>2:</sup> Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN.

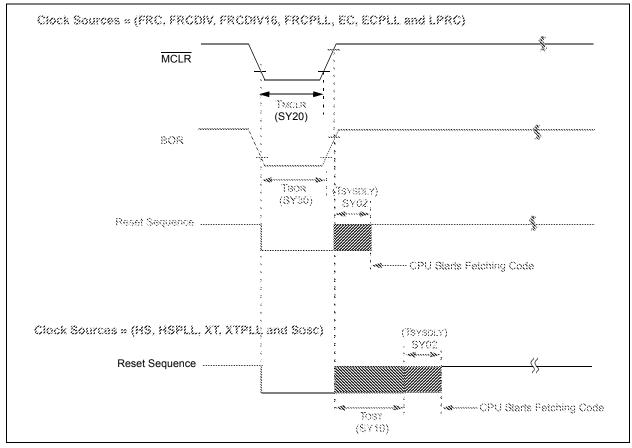

FIGURE 30-5: EXTERNAL RESET TIMING CHARACTERISTICS

**TABLE 30-22: RESETS TIMING**

| AC CHA        | RACTERI | STICS                                                                                                                          | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +105^{\circ}\text{C}$ for V-temp |                              |     |    |   |  |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----|----|---|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                                                                                 | Min. Typical <sup>(2)</sup> Max. Units Conditions                                                                                                                                                                                              |                              |     |    |   |  |

| SY00          | TPU     | Power-up Period<br>Internal Voltage Regulator Enabled                                                                          | _                                                                                                                                                                                                                                              | 400                          | 600 | μS | _ |  |

| SY02          | TSYSDLY | System Delay Period: Time Required to Reload Device Configuration Fuses plus SYSCLK Delay before First instruction is Fetched. | _                                                                                                                                                                                                                                              | 1 μs +<br>8 SYSCLK<br>cycles | l   | _  |   |  |

| SY20          | TMCLR   | MCLR Pulse Width (low)                                                                                                         | 2                                                                                                                                                                                                                                              | _                            | _   | μS | _ |  |

| SY30          | TBOR    | BOR Pulse Width (low)                                                                                                          | _                                                                                                                                                                                                                                              | 1                            | _   | μS |   |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

<sup>2:</sup> Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

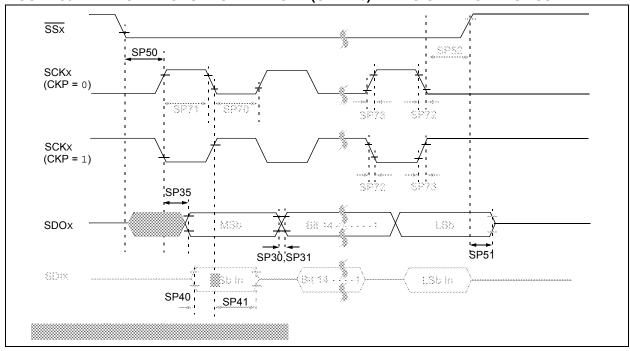

FIGURE 30-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

TABLE 30-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHA        | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-temp |                                                              |           |   |    |       |                    |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------|---|----|-------|--------------------|

| Param.<br>No. | Symbol                                                                                                                                                                                                                                         | Characteristics <sup>(1)</sup> Min. Typ. <sup>(2)</sup> Max. |           |   |    | Units | Conditions         |

| SP70          | TscL                                                                                                                                                                                                                                           | SCKx Input Low Time (Note 3)                                 | Tsck/2    | _ |    | ns    | _                  |

| SP71          | TscH                                                                                                                                                                                                                                           | SCKx Input High Time (Note 3)                                | Tsck/2    | _ | _  | ns    | _                  |

| SP72          | TscF                                                                                                                                                                                                                                           | SCKx Input Fall Time                                         | _         | _ | _  | ns    | See parameter DO32 |

| SP73          | TscR                                                                                                                                                                                                                                           | SCKx Input Rise Time                                         | _         | _ | _  | ns    | See parameter DO31 |

| SP30          | TDOF                                                                                                                                                                                                                                           | SDOx Data Output Fall Time (Note 4)                          | _         | _ |    | ns    | See parameter DO32 |

| SP31          | TDOR                                                                                                                                                                                                                                           | SDOx Data Output Rise Time (Note 4)                          | _         | _ |    | ns    | See parameter DO31 |

| SP35          | TscH2DoV,                                                                                                                                                                                                                                      | SDOx Data Output Valid after                                 | _         | _ | 15 | ns    | VDD > 2.7V         |

|               | TscL2doV                                                                                                                                                                                                                                       | SCKx Edge                                                    | _         | _ | 20 | ns    | VDD < 2.7V         |

| SP40          | TDIV2SCH,<br>TDIV2SCL                                                                                                                                                                                                                          | Setup Time of SDIx Data Input to SCKx Edge                   | 10        | _ | _  | ns    | _                  |

| SP41          | TSCH2DIL,<br>TSCL2DIL                                                                                                                                                                                                                          | Hold Time of SDIx Data Input to SCKx Edge                    | 10        | _ | _  | ns    | _                  |

| SP50          | TssL2scH,<br>TssL2scL                                                                                                                                                                                                                          | SSx ↓ to SCKx ↑ or SCKx Input                                | 175       | _ | _  | ns    | _                  |

| SP51          | TssH2DoZ                                                                                                                                                                                                                                       | SSx ↑ to SDOx Output<br>High-Impedance (Note 3)              | 5         | _ | 25 | ns    | _                  |

| SP52          | TscH2ssH<br>TscL2ssH                                                                                                                                                                                                                           | SSx after SCKx Edge                                          | Tsck + 20 | _ | _  | ns    | _                  |

- Note 1: These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- 4: Assumes 50 pF load on all SPIx pins.

#### TABLE 31-3: DC CHARACTERISTICS: IDLE CURRENT (IDLE)

| DC CHARACT                                                     | ERISTICS               |      | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)  Operating temperature -40°C ≤ TA ≤ +85°C for Industrial |            |  |  |  |  |

|----------------------------------------------------------------|------------------------|------|--------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|

| Parameter<br>No.                                               | Typical <sup>(2)</sup> | Max. | Units                                                                                                                          | Conditions |  |  |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Note 1) |                        |      |                                                                                                                                |            |  |  |  |  |

| MDC34a                                                         | 8                      | 13   | mA 50 MHz                                                                                                                      |            |  |  |  |  |

- **Note 1:** The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- · OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode (CPU core Halted), and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- · RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 31-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHAR                           | RACTERIST              | ics     | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial |            |                                                 |  |  |  |  |

|-----------------------------------|------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------|--|--|--|--|

| Param.<br>No.                     | Typical <sup>(2)</sup> | Max.    | Units                                                                                                                                                                  | Conditions |                                                 |  |  |  |  |

| Power-Down Current (IPD) (Note 1) |                        |         |                                                                                                                                                                        |            |                                                 |  |  |  |  |

| MDC40k                            | 10                     | 25      | μА                                                                                                                                                                     | -40°C      | Base Power-Down Current                         |  |  |  |  |

| MDC40n                            | 250                    | 500     | μА                                                                                                                                                                     | +85°C      | Base Power-Down Current                         |  |  |  |  |

| Module D                          | ifferential (          | Current |                                                                                                                                                                        |            |                                                 |  |  |  |  |

| MDC41e                            | 10                     | 55      | μА                                                                                                                                                                     | 3.6V       | Watchdog Timer Current: ΔIWDT (Note 3)          |  |  |  |  |

| MDC42e                            | 23                     | 55      | μА                                                                                                                                                                     | 3.6V       | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3) |  |  |  |  |

| MDC43d                            | 1100                   | 1300    | μА                                                                                                                                                                     | 3.6V       | ADC: ΔIADC (Notes 3,4)                          |  |  |  |  |

- **Note 1:** The test conditions for IPD current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- · OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- · RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The Δ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

NOTES:

#### 33.1 Package Marking Information (Continued)

36-Lead VTLA

44-Lead VTLA

44-Lead QFN

44-Lead TQFP

Example

Example

Example

Example

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3)

can be found on the outer packaging for this package.

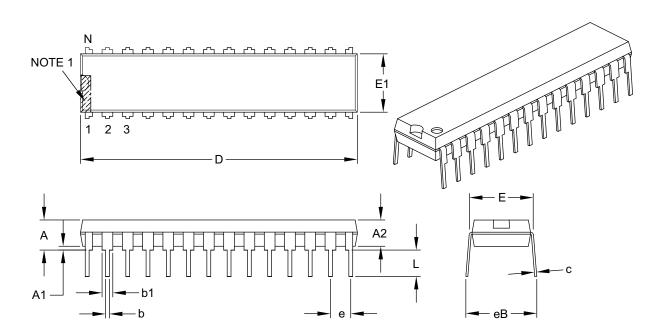

### 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            | INCHES |          |       |  |

|----------------------------|------------------|--------|----------|-------|--|

|                            | Dimension Limits | MIN    | NOM      | MAX   |  |

| Number of Pins             | N                |        | 28       |       |  |

| Pitch                      | е                |        | .100 BSC |       |  |

| Top to Seating Plane       | A                | -      | _        | .200  |  |

| Molded Package Thickness   | A2               | .120   | .135     | .150  |  |

| Base to Seating Plane      | A1               | .015   | _        | -     |  |

| Shoulder to Shoulder Width | E                | .290   | .310     | .335  |  |

| Molded Package Width       | E1               | .240   | .285     | .295  |  |

| Overall Length             | D                | 1.345  | 1.365    | 1.400 |  |

| Tip to Seating Plane       | L                | .110   | .130     | .150  |  |

| Lead Thickness             | С                | .008   | .010     | .015  |  |

| Upper Lead Width           | b1               | .040   | .050     | .070  |  |

| Lower Lead Width           | b                | .014   | .018     | .022  |  |

| Overall Row Spacing §      | eB               | -      | _        | .430  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B