#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f032bt-v-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 12: PIN NAMES FOR 44-PIN USB DEVICES

## 44-PIN TQFP (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

44

1

| Pin # | Full Pin Name                                    | Pin # | Full Pin Name                             |

|-------|--------------------------------------------------|-------|-------------------------------------------|

| 1     |                                                  | 23    |                                           |

|       | RPB9/SDA1/CTED4/PMD3/RB9                         | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2     | RPC6/PMA1/RC6                                    |       | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3     | RPC7/PMA0/RC7                                    | 25    | AN6/RPC0/RC0                              |

| 4     | RPC8/PMA5/RC8                                    | 26    | AN7/RPC1/RC1                              |

| 5     | RPC9/CTED7/PMA6/RC9                              | 27    | AN8/RPC2/PMA2/RC2                         |

| 6     | Vss                                              | 28    | VDD                                       |

| 7     | VCAP                                             | 29    | Vss                                       |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       | 30    | OSC1/CLKI/RPA2/RA2                        |

| 9     | PGEC2/RPB11/D-/RB11                              | 31    | OSC2/CLKO/RPA3/RA3                        |

| 10    | VUSB3V3                                          | 32    | TDO/RPA8/PMA8/RA8                         |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       | 33    | SOSCI/RPB4/RB4                            |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10             | 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7         | 35    | TDI/RPA9/PMA9/RA9                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 | 36    | AN12/RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            | 37    | RPC4/PMA4/RC4                             |

| 16    | AVss                                             | 38    | RPC5/PMA3/RC5                             |

| 17    | AVDD                                             | 39    | Vss                                       |

| 18    | MCLR                                             | 40    | Vdd                                       |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 | 41    | RPB5/USBID/RB5                            |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       | 42    | VBUS                                      |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        | 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       | 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX210F016D and PIC32MX220F032D devices.

5: Shaded pins are 5V tolerant.

NOTES:

## 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming™ (ICSP™)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: The Flash page size on PIC32MX-1XX/2XX 28/36/44-pin Family devices is 1 KB and the row size is 128 bytes (256 IW and 32 IW, respectively).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | -                 | —                 | _                 | _                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

|              | _                 | _                 |                   | _                 | RDWR              | Γ                 | DMACH<2:0>       | >                |

## REGISTER 9-2: DMASTAT: DMA STATUS REGISTER

## Legend:

| 0                 |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

## bit 31-4 Unimplemented: Read as '0'

- bit 3 RDWR: Read/Write Status bit

- 1 = Last DMA bus access was a read

- 0 = Last DMA bus access was a write

- bit 2-0 **DMACH<2:0>:** DMA Channel bits These bits contain the value of the most recent active DMA channel.

## REGISTER 9-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24        | DMAADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | DMAADDR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | DMAADD            | R<7:0>            |                   |                  |                  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | _                 | _                 | —                 | _                 | —                | —                |  |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                   | _                 |                   | _                 | _                 |                   | _                | —                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | CHSSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |  |

## REGISTER 9-12: DCHxSSIZ: DMA CHANNEL 'x' SOURCE SIZE REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

## bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

## **REGISTER 9-13: DCHxDSIZ: DMA CHANNEL 'x' DESTINATION SIZE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | _                 | —                 | _                 | _                 | —                 | _                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | CHDSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |  |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

## 10.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 Full-Speed and Low-Speed embedded host, Full-Speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 10-1.

The clock generator provides the 48 MHz clock required for USB Full-Speed and Low-Speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module. The PIC32 USB module includes the following features:

- · USB Full-Speed support for Host and Device

- Low-Speed Host support

- USB OTG support

- · Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- · Transaction handshaking performed by hardware

- · Endpoint buffering anywhere in system RAM

- · Integrated DMA to access system RAM and Flash

- Note: The implementation and use of the USB specifications, as well as other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc., also referred to as USB-IF (www.usb.org). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6       | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------------|-------------------------|-------------------|----------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 31.24        | —                 | _                       | _                       | _                 | —                    | —                 | -                     | —                       |

| 23:16        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 23.10        | —                 | _                       | _                       | _                 | —                    | —                 | -                     | —                       |

| 15:8         | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 15.6         | —                 | _                       | _                       | _                 | —                    | —                 | -                     | —                       |

|              | R/WC-0, HS        | R/WC-0, HS              | R/WC-0, HS              | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS        | R-0                   | R/WC-0, HS              |

| 7:0          | STALLIF           | ATTACHIF <sup>(1)</sup> | RESUMEIF <sup>(2)</sup> | IDLEIF            | TRNIF <sup>(3)</sup> | SOFIF             | UERRIF <sup>(4)</sup> | URSTIF <sup>(5)</sup>   |

|              | STALLIF           |                         | RESUMEIRY               | IDLEIF            |                      | SOFIE             | UERRIC'               | DETACHIF <sup>(6)</sup> |

## REGISTER 10-6: U1IR: USB INTERRUPT REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settat | ble bit            |

|-------------------|-------------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared | x = Bit is unknown |

## bit 31-8 Unimplemented: Read as '0'

| bit 7       | <b>STALLIF:</b> STALL Handshake Interrupt bit<br>1 = In Host mode a STALL handshake was received during the handshake phase of the transaction<br>In Device mode a STALL handshake was transmitted during the handshake phase of the transaction<br>0 = STALL handshake has not been sent                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6       | ATTACHIF: Peripheral Attach Interrupt bit <sup>(1)</sup><br>1 = Peripheral attachment was detected by the USB module<br>0 = Peripheral attachment was not detected                                                                                                                                                                                                                                                                               |

| bit 5       | <b>RESUMEIF:</b> Resume Interrupt bit <sup>(2)</sup><br>1 = K-State is observed on the D+ or D- pin for 2.5 μs<br>0 = K-State is not observed                                                                                                                                                                                                                                                                                                    |

| bit 4       | IDLEIF: Idle Detect Interrupt bit<br>1 = Idle condition detected (constant Idle state of 3 ms or more)<br>0 = No Idle condition detected                                                                                                                                                                                                                                                                                                         |

| bit 3       | <b>TRNIF:</b> Token Processing Complete Interrupt bit <sup>(3)</sup><br>1 = Processing of current token is complete; a read of the U1STAT register will provide endpoint information<br>0 = Processing of current token not complete                                                                                                                                                                                                             |

| bit 2       | <b>SOFIF:</b> SOF Token Interrupt bit<br>1 = SOF token received by the peripheral or the SOF threshold reached by the host<br>0 = SOF token was not received nor threshold reached                                                                                                                                                                                                                                                               |

| bit 1       | <b>UERRIF</b> : USB Error Condition Interrupt bit <sup>(4)</sup><br>1 = Unmasked error condition has occurred<br>0 = Unmasked error condition has not occurred                                                                                                                                                                                                                                                                                   |

| bit 0       | <pre>URSTIF: USB Reset Interrupt bit (Device mode)<sup>(5)</sup> 1 = Valid USB Reset has occurred 0 = No USB Reset has occurred DETACHIF: USB Detach Interrupt bit (Host mode)<sup>(6)</sup> 1 = Peripheral detachment was detected by the USB module 0 = Peripheral detachment was not detected</pre>                                                                                                                                           |

| 3<br>2<br>5 | <ul> <li>This bit is valid only if the HOSTEN bit is set (see Register 10-11), there is no activity on the USB for 2.5 µs, and the current bus state is not SE0.</li> <li>When not in Suspend mode, this interrupt should be disabled.</li> <li>Clearing this bit will cause the STAT FIFO to advance.</li> <li>Only error conditions enabled through the U1EIE register will set this bit.</li> <li>Device mode.</li> <li>Host mode.</li> </ul> |

|              |                   |                   |                          |                   | -                     |                       |                  |                      |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 |                       |                       | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

| 24.04        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 31:24        | —                 | —                 | —                        | _                 | —                     | —                     |                  | _                    |

| 22:16        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 23:16        | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 15.0         | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |

| 7:0          | JSTATE            | SE0               | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |

|              | JUNATE            | 320               | TOKBUSY <sup>(1,5)</sup> | USBROI            | TIOSTEIN /            | RESUMENT              | FFDROI           | SOFEN <sup>(5)</sup> |

## REGISTER 10-11: U1CON: USB CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

## bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE was detected on the USB

- 0 = No JSTATE was detected on the

- bit 6 **SE0:** Live Single-Ended Zero flag bit 1 = Single-Ended Zero was detected on the USB

- 0 = No Single-Ended Zero was detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing is disabled (set upon SETUP token received)

- 0 = Token and packet processing is enabled

- TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token is being executed by the USB module

- 0 = No token is being executed

## bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset generated

- 0 = USB reset terminated

- bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

- bit 2 RESUME: RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

| TABL                        | E 11-7:              | PEI       | RIPHER |       | SELEC |       | PUT RE | GISTER | MAP ( | CONTIN | IUED) |      |      |      |      |      |        |      |            |

|-----------------------------|----------------------|-----------|--------|-------|-------|-------|--------|--------|-------|--------|-------|------|------|------|------|------|--------|------|------------|

| SS                          |                      |           |        |       |       |       |        |        |       | В      | its   |      |      |      |      |      |        |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10  | 25/9  | 24/8   | 23/7  | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| FB4C                        | RPB8R                | 31:16     | _      | -     | —     | -     | _      | -      | _     | _      | -     | —    | _    | —    | _    | _    | _      | —    | 0000       |

| 1040                        | IN DOIX              | 15:0      | _      |       | —     |       | —      |        | _     | —      |       |      | —    | —    |      | RPB8 | <3:0>  |      | 0000       |

| FB50                        | RPB9R                | 31:16     | —      | —     | —     | —     | —      | —      | _     | —      | —     | —    | —    | —    | _    | —    | —      | —    | 0000       |

| 1 830                       | KF D9K               | 15:0      | —      | _     | —     | _     | —      | —      | -     |        | —     | —    | —    | —    |      | RPB9 | <3:0>  |      | 0000       |

| FB54                        | RPB10R               | 31:16     | —      | _     | —     | _     | —      | —      | -     |        | _     | —    | —    | —    | -    | _    | —      | —    | 0000       |

| FB34                        | REDIUR               | 15:0      | —      | —     | _     | —     | —      | —      |       |        | —     | —    | —    | —    |      | RPB1 | 0<3:0> |      | 0000       |

| FB58                        | RPB11R               | 31:16     | —      | —     | _     | —     | —      | —      |       |        | —     | —    | —    | —    |      |      | _      | —    | 0000       |

| FB30                        | RPBIIR               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 1<3:0> |      | 0000       |

| FB60                        | RPB13R               | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB00                        | RPBISR               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 3<3:0> |      | 0000       |

| FB64                        | RPB14R               | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB04                        | KPD14K               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 4<3:0> |      | 0000       |

| FB68                        | RPB15R               | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB00                        | RPBIOR               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 5<3:0> |      | 0000       |

| FB6C                        | RPC0R <sup>(3)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FBOC                        | RECOR                | 15:0      | —      | —     | —     | —     | —      | —      | -     |        | —     | —    | -    | —    |      | RPCC | <3:0>  |      | 0000       |

| FB70                        | RPC1R <sup>(3)</sup> | 31:16     | —      | —     | _     | —     | —      | _      |       |        | —     | —    | —    | —    |      |      | _      | —    | 0000       |

| FB/U                        | RPUIK                | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC1 | <3:0>  |      | 0000       |

| FB74                        | RPC2R <sup>(1)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/4                        | RP62R <sup>4</sup>   | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC2 | <3:0>  |      | 0000       |

| FB78                        | RPC3R <sup>(3)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/0                        | RPGSR                | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC3 | <3:0>  |      | 0000       |

| FB7C                        | RPC4R <sup>(1)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/C                        | RPC4R <sup>V</sup>   | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC4 | <3:0>  |      | 0000       |

| FB80                        | RPC5R <sup>(1)</sup> | 31:16     |        | —     | —     | —     | —      | —      | _     |        | —     | _    | —    | —    | _    | _    | —      | _    | 0000       |

| FB80                        | KPUSK"               | 15:0      |        |       |       |       | —      | _      | _     | _      | _     |      | —    | —    |      | RPC5 | i<3:0> |      | 0000       |

| FB84                        | RPC6R <sup>(1)</sup> | 31:16     |        |       |       |       | —      | _      | _     | _      | _     |      | —    | —    | _    | —    |        | —    | 0000       |

| FB04                        | RPU0K"               | 15:0      |        |       |       |       | —      | _      | _     | _      | _     |      | —    | —    |      | RPC  | <3:0>  |      | 0000       |

| ED00                        |                      | 31:16     |        | —     |       | —     | —      | —      | _     |        | —     |      | —    | —    | _    | _    | —      |      | 0000       |

| F B 08                      | FR88 PPC7P(1)        | 15:0      | _      | _     | —     | _     | _      | —      | —     | _      | —     |      | _    | _    |      | RPC7 | <3:0>  |      | 0000       |

#### OT AUTOUT DEALATED MAD

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is only available on 44-pin devices. Note 1:

2: 3:

This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices.

## 18.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

| Note: | This data sheet summarizes the features              |

|-------|------------------------------------------------------|

|       | of the PIC32MX1XX/2XX 28/36/44-pin                   |

|       | Family of devices. It is not intended to be          |

|       | a comprehensive reference source. To                 |

|       | complement the information in this data              |

|       | sheet, refer to Section 24. "Inter-                  |

|       | Integrated Circuit (I <sup>2</sup> C)" (DS60001116), |

|       | which is available from the Documentation            |

|       | > Reference Manual section of the Micro-             |

|       | chip PIC32 web site                                  |

|       | (www.microchip.com/pic32).                           |

The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard. Figure 18-1 illustrates the I<sup>2</sup>C module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

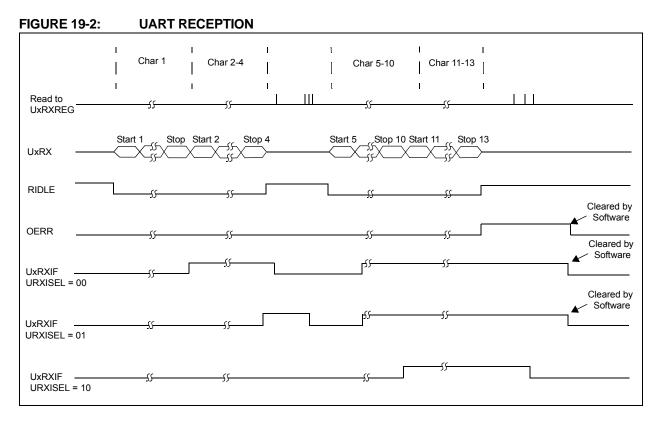

#### REGISTER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED) bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit 11 = Reserved; do not use 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (i.e., has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (i.e., has 4 or more data characters) 00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character) bit 5 ADDEN: Address Character Detect bit (bit 8 of received data = 1) 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect. 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 =Receiver is Idle 0 = Data is being received PERR: Parity Error Status bit (read-only) bit 3 1 = Parity error has been detected for the current character 0 = Parity error has not been detected bit 2 FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character 0 = Framing error has not been detected **OERR:** Receive Buffer Overrun Error Status bit. bit 1 This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and the RSR to an empty state. 1 = Receive buffer has overflowed 0 = Receive buffer has not overflowed bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

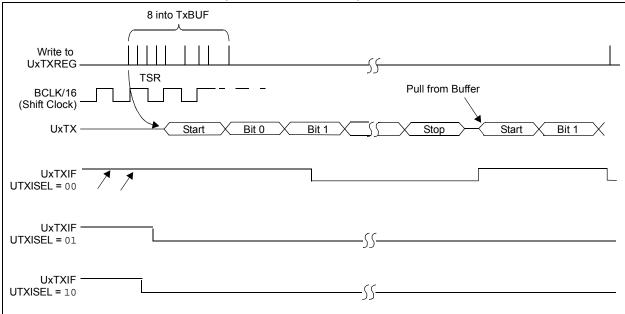

Figure 19-2 and Figure 19-3 illustrate typical receive and transmit timing for the UART module.

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------------|------------------|--|--|--|

| 24.24        | U-0                     | U-0               | U-0               | U-0               | U-0                    | U-0               | R/W-0                  | R/W-0            |  |  |  |

| 31:24        |                         |                   | _                 | _                 |                        |                   |                        |                  |  |  |  |

| 00.40        | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                  | R/W-0             | R/W-0                  | R/W-0            |  |  |  |

| 23:16        | CAL<7:0>                |                   |                   |                   |                        |                   |                        |                  |  |  |  |

| 45.0         | R/W-0                   | U-0               | R/W-0             | U-0               | U-0                    | U-0               | U-0                    | U-0              |  |  |  |

| 15:8         | ON <sup>(1,2)</sup>     | _                 | SIDL              | _                 | —                      | _                 | _                      |                  |  |  |  |

| 7.0          | R/W-0                   | R-0               | U-0               | U-0               | R/W-0                  | R-0               | R-0                    | R/W-0            |  |  |  |

| 7:0          | RTSECSEL <sup>(3)</sup> | RTCCLKON          |                   | _                 | RTCWREN <sup>(4)</sup> | RTCSYNC           | HALFSEC <sup>(5)</sup> | RTCOE            |  |  |  |

|              |                         |                   |                   |                   |                        |                   |                        |                  |  |  |  |

## REGISTER 21-1: RTCCON: RTC CONTROL REGISTER

## Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-26 Unimplemented: Read as '0'

bit 25-16 CAL<9:0>: RTC Drift Calibration bits, which contain a signed 10-bit integer value 0111111111 = Maximum positive adjustment, adds 511 RTC clock pulses every one minute 000000001 = Minimum positive adjustment, adds 1 RTC clock pulse every one minute 000000000 = No adjustment 1111111111 = Minimum negative adjustment, subtracts 1 RTC clock pulse every one minute 100000000 = Maximum negative adjustment, subtracts 512 clock pulses every one minute ON: RTCC On bit<sup>(1,2)</sup> bit 15 1 = RTCC module is enabled 0 = RTCC module is disabled bit 14 Unimplemented: Read as '0' bit 13 SIDL: Stop in Idle Mode bit 1 = Disables the PBCLK to the RTCC when the device enters Idle mode 0 = Continue normal operation when the device enters Idle mode bit 12-8 Unimplemented: Read as '0' bit 7 RTSECSEL: RTCC Seconds Clock Output Select bit<sup>(3)</sup> 1 = RTCC Seconds Clock is selected for the RTCC pin 0 = RTCC Alarm Pulse is selected for the RTCC pin bit 6 RTCCLKON: RTCC Clock Enable Status bit 1 = RTCC Clock is actively running 0 = RTCC Clock is not running **Note 1:** The ON bit is only writable when RTCWREN = 1. 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. 3: Requires RTCOE = 1 (RTCCON<0>) for the output to be active. 4: The RTCWREN bit can be set only when the write sequence is enabled. 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

**Note:** This register is reset only on a Power-on Reset (POR).

© 2011-2016 Microchip Technology Inc.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | —                 | —                 | _                 |                   | —                | _                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | —                | _                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | CSSL15            | CSSL14            | CSSL13            | CSSL12            | CSSL11            | CSSL10            | CSSL9            | CSSL8            |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | CSSL7             | CSSL6             | CSSL5             | CSSL4             | CSSL3             | CSSL2             | CSSL1            | CSSL0            |  |  |  |

## REGISTER 22-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

## Legend:

| Logena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CSSL<15:0>: ADC Input Pin Scan Selection bits<sup>(1,2)</sup>

1 = Select ANx for input scan

0 = Skip ANx for input scan

- **Note 1:** CSSL = ANx, where 'x' = 0-12; CSSL13 selects CTMU input for scan; CSSL14 selects IVREF for scan; CSSL15 selects Vss for scan.

- 2: On devices with less than 13 analog inputs, all CSSLx bits can be selected; however, inputs selected for scan without a corresponding input on the device will convert to VREFL.

## 23.1 Comparator Control Registers

## TABLE 23-1: COMPARATOR REGISTER MAP

| ess                         |                                 | 0         |       |       |       |       |       |       |      | Bi   | its  |        |      |      |      |       |       |       |           |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|-------|-------|-------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0  | All Reset |

| 4000                        | CM1CON                          | 31:16     | _     | _     | -     | _     | -     | _     |      | -    | —    | _      | -    | —    | —    | —     | _     | —     | 0000      |

| A000                        | CIVITCON                        | 15:0      | ON    | COE   | CPOL  | _     | -     | _     | _    | COUT | EVPO | L<1:0> | -    | CREF | _    | —     | CCH   | <1:0> | 00C3      |

| A010                        | CM2CON                          | 31:16     | _     | _     |       | _     |       | _     |      |      | _    | _      |      | _    | _    | _     | _     | _     | 0000      |

| 7010                        | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  |       | -     |       | -    | COUT | EVPO | L<1:0> | -    | CREF | —    | —     | CCH   | <1:0> | 00C3      |

| A020                        | CM3CON                          | 31:16     | -     |       |       |       | -     |       | -    | -    | —    | —      | -    | _    | —    | —     |       | —     | 0000      |

| A020                        | CIVISCON                        | 15:0      | ON    | COE   | CPOL  | _     | —     | _     | —    | COUT | EVPO | L<1:0> | —    | CREF | _    | —     | CCH   | <1:0> | 00C3      |

| A060                        | CMSTAT                          | 31:16     | _     | —     | _     | _     | -     | _     | _    | -    | —    | _      | -    | _    | _    | —     | _     | —     | 0000      |

| 7000                        | A060 CMSTAT 1                   | 15:0      | _     | _     | SIDL  | _     |       | _     |      |      | -    | _      |      | _    |      | C3OUT | C2OUT | C10UT | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

## 30.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC32MX1XX/2XX 28/36/44-pin Family AC characteristics and timing parameters.

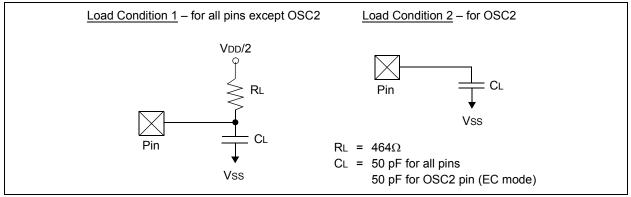

## FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

## TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| АС СНА        | RACTERI                                         | STICS           | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |            |     |    |                          |  |  |

|---------------|-------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|----|--------------------------|--|--|

| Param.<br>No. | Symbol                                          | Characteristics | Min.                                                                                                                                                                                               | Conditions |     |    |                          |  |  |

| DO56          | D56 CIO All I/O pins and OSC2 — — 50 pF EC mode |                 |                                                                                                                                                                                                    |            |     |    |                          |  |  |

| DO58          | Св                                              | SCLx, SDAx      | —                                                                                                                                                                                                  | —          | 400 | pF | In I <sup>2</sup> C mode |  |  |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

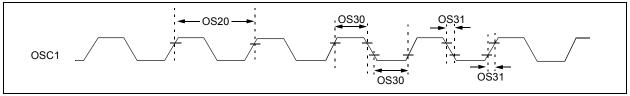

## FIGURE 30-2: EXTERNAL CLOCK TIMING

| AC CHA        | ARACTER   | ISTICS                                                               | (unless | d Operating<br>otherwise<br>ng temperati | <b>stated)</b><br>ure -40° | C ≤ TA ≤ · | Note 4): 2.5V to 3.6V<br>+85°C for Industrial<br>+105°C for V-temp |

|---------------|-----------|----------------------------------------------------------------------|---------|------------------------------------------|----------------------------|------------|--------------------------------------------------------------------|

| Param.<br>No. | Symbol    | Characteristics                                                      | Min.    | Typical <sup>(1)</sup>                   | Max.                       | Units      | Conditions                                                         |

| Clock P       | arameters | S                                                                    | •       | •                                        |                            |            |                                                                    |

| AD50          | TAD       | ADC Clock Period <sup>(2)</sup>                                      | 65      | _                                        | —                          | ns         | See Table 30-35                                                    |

| Convers       | sion Rate |                                                                      |         |                                          |                            |            |                                                                    |

| AD55          | TCONV     | Conversion Time                                                      | _       | 12 Tad                                   | —                          | _          | —                                                                  |

| AD56          | FCNV      | Throughput Rate                                                      | —       | —                                        | 1000                       | ksps       | AVDD = 3.0V to 3.6V                                                |

|               |           | (Sampling Speed)                                                     | —       | —                                        | 400                        | ksps       | AVDD = 2.5V to 3.6V                                                |

| AD57          | TSAMP     | Sample Time                                                          | 1 Tad   | —                                        | —                          | —          | TSAMP must be $\geq$ 132 ns                                        |

| Timing        | Paramete  | rs                                                                   |         |                                          |                            |            |                                                                    |

| AD60          | TPCS      | Conversion Start from Sample<br>Trigger <sup>(3)</sup>               |         | 1.0 Tad                                  |                            | _          | Auto-Convert Trigger<br>(SSRC<2:0> = 111)<br>not selected          |

| AD61          | TPSS      | Sample Start from Setting<br>Sample (SAMP) bit                       | 0.5 Tad | —                                        | 1.5 Tad                    | _          | _                                                                  |

| AD62          | TCSS      | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(3)</sup>   | —       | 0.5 Tad                                  | —                          |            | _                                                                  |

| AD63          | TDPU      | Time to Stabilize Analog Stage from ADC Off to ADC On <sup>(3)</sup> | _       | _                                        | 2                          | μS         | _                                                                  |

## TABLE 30-36: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

**3:** Characterized by design but not tested.

**4:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

## TABLE 30-37: PARALLEL SLAVE PORT REQUIREMENTS

| AC CH         | ARACTE       | RISTICS                                                                          | (unless o | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |            |  |  |  |

|---------------|--------------|----------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|

| Para<br>m.No. | Symbol       | Characteristics <sup>(1)</sup>                                                   | Min.      | Тур.                                                                                                                                                                                                                                                                                  | Max. | Units | Conditions |  |  |  |

| PS1           | TdtV2wr<br>H | Data In Valid before $\overline{WR}$ or $\overline{CS}$<br>Inactive (setup time) | 20        |                                                                                                                                                                                                                                                                                       |      | ns    | _          |  |  |  |

| PS2           | TwrH2dt<br>I | WR or CS Inactive to Data-In Invalid (hold time)                                 | 40        | —                                                                                                                                                                                                                                                                                     | _    | ns    | _          |  |  |  |

| PS3           | TrdL2dt<br>V | $\overline{\text{RD}}$ and $\overline{\text{CS}}$ Active to Data-Out Valid       | _         | —                                                                                                                                                                                                                                                                                     | 60   | ns    | _          |  |  |  |

| PS4           | TrdH2dtl     | RD Active or CS Inactive to Data-Out Invalid                                     | 0         | —                                                                                                                                                                                                                                                                                     | 10   | ns    | _          |  |  |  |

| PS5           | Tcs          | CS Active Time                                                                   | Трв + 40  | _                                                                                                                                                                                                                                                                                     | _    | ns    | —          |  |  |  |

| PS6           | Twr          | WR Active Time                                                                   | Трв + 25  |                                                                                                                                                                                                                                                                                       | _    | ns    | —          |  |  |  |

| PS7           | Trd          | RD Active Time                                                                   | Трв + 25  | _                                                                                                                                                                                                                                                                                     | —    | ns    | —          |  |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

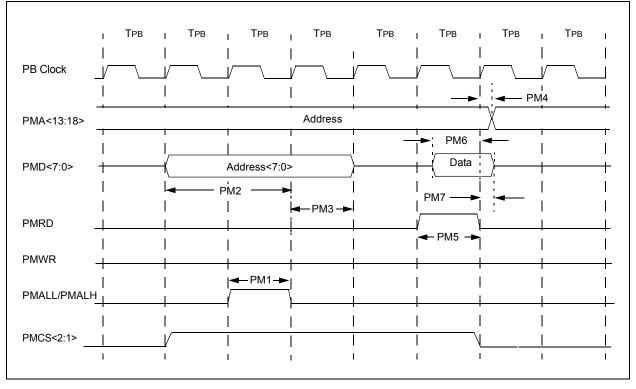

## FIGURE 30-21: PARALLEL MASTER PORT READ TIMING DIAGRAM

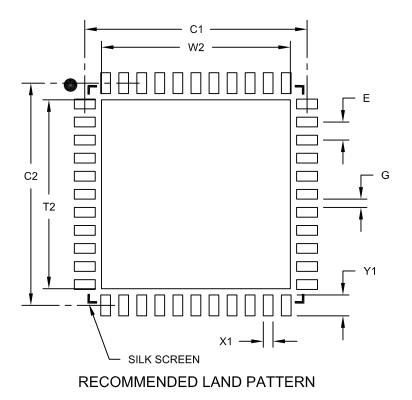

## 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |    | MILLIMETERS |          |      |

|----------------------------|----|-------------|----------|------|

| Dimension Limits           |    | MIN         | NOM      | MAX  |

| Contact Pitch              | E  |             | 0.65 BSC |      |

| Optional Center Pad Width  | W2 |             |          | 6.80 |

| Optional Center Pad Length | T2 |             |          | 6.80 |

| Contact Pad Spacing        | C1 |             | 8.00     |      |

| Contact Pad Spacing        | C2 |             | 8.00     |      |

| Contact Pad Width (X44)    | X1 |             |          | 0.35 |

| Contact Pad Length (X44)   | Y1 |             |          | 0.80 |

| Distance Between Pads      | G  | 0.25        |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103A

## Revision J (April 2016)

This revision includes the following major changes as described in Table A-8, as well as minor updates to text and formatting, which were incorporated throughout the document.

## TABLE A-8: MAJOR SECTION UPDATES

| Section                                                                                                                                | Update Description                                                                                                                |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

| "32-bit Microcontrollers (up to<br>256 KB Flash and 64 KB<br>SRAM) with Audio and<br>Graphics Interfaces, USB, and<br>Advanced Analog" | The PIC32MX270FDB device and Note 4 were added to <b>TABLE 2: "PIC32MX2XX</b><br><b>28/36/44-pin USB Family Features"</b> .       |  |  |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                               | EXAMPLE 2-1: "Crystal Load Capacitor Calculation" was updated.                                                                    |  |  |

| 30.0 "Electrical<br>Characteristics"                                                                                                   | Parameter DO50a (Csosc) was removed from the Capacitive Loading Requirements on Output Pins AC Characteristics (see Table 30-16). |  |  |

| "Product Identification<br>System"                                                                                                     | The device mapping was updated to include type B for Software Targeting.                                                          |  |  |