Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f032d-50i-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

| Note: | To access the following documents, refer |

|-------|------------------------------------------|

|       | to the Documentation > Reference         |

|       | Manuals section of the Microchip PIC32   |

|       | website: http://www.microchip.com/pic32  |

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 3. "Memory Organization" (DS60001115)

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer" (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167)

## 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX1XX/2XX 28/36/44-pin Family devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming™ (ICSP™)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: The Flash page size on PIC32MX-1XX/2XX 28/36/44-pin Family devices is 1 KB and the row size is 128 bytes (256 IW and 32 IW, respectively).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|----------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|

| 24.24        | U-0               | U-0                  | R/W-y             | R/W-y             | R/W-y             | R/W-0                 | R/W-0            | R/W-1            |

| 31:24        | —                 | —                    | PLLODIV<2:0>      |                   |                   | F                     | RCDIV<2:0>       |                  |

| 00.40        | U-0               | R-0                  | R-1               | R/W-y             | R/W-y             | R/W-y                 | R/W-y            | R/W-y            |

| 23:16        | —                 | SOSCRDY              | PBDIVRDY          | PBDI              | /<1:0>            | PLLMULT<2:0>          |                  |                  |

| 45.0         | U-0               | R-0                  | R-0               | R-0               | U-0               | R/W-y                 | R/W-y            | R/W-y            |

| 15:8         | —                 |                      | COSC<2:0>         |                   | —                 |                       | NOSC<2:0>        |                  |

| 7:0          | R/W-0             | R-0                  | R-0               | R/W-0             | R/W-0             | R/W-0                 | R/W-y            | R/W-0            |

| 7:0          | CLKLOCK           | ULOCK <sup>(1)</sup> | SLOCK             | SLPEN             | CF                | UFRCEN <sup>(1)</sup> | SOSCEN           | OSWEN            |

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| Legend:           | y = Value set from Co | y = Value set from Configuration bits on POR |                    |  |  |

|-------------------|-----------------------|----------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bi                         | t, read as '0'     |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared                         | x = Bit is unknown |  |  |

### bit 31-30 **Unimplemented:** Read as '0'

#### bit 29-27 **PLLODIV<2:0>:** Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

#### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

- 1 = The Secondary Oscillator is running and is stable

- 0 = The Secondary Oscillator is still warming up or is turned off

- bit 21 **PBDIVRDY:** Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

Note 1: This bit is only available on PIC32MX2XX devices.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   | ROTRIM<8:1>       |                   |                   |                   |                   |                  |                  |

| 00.40        | R/W-0             | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | ROTRIM<0>         | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | —                 | _                 | _                | —                |

## REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

## Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

Note: While the ON (REFOCON<15>) bit is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

### REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0            |

| 31:24 —      |                   | _                     | BYTO<1:0>         |                   | WBO <sup>(1)</sup> | —                 | _                | BITO             |

| 22:16        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                     | —                 | _                 | —                  | —                 | _                | _                |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   | _                     | _                 |                   |                    | PLEN<4:0>         |                  |                  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | _                 | _                  | (                 | CRCCH<2:0>       |                  |

## Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-30 Unimplemented: Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

#### <u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

#### bit 23-13 Unimplemented: Read as '0'

bit 12-8 **PLEN<4:0>:** Polynomial Length bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | —                 | —                 |                   |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   | —                 | —                 |                   | -                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | _                 | —                 | _                 | —                 | —                 | -                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | UOEMON            | _                 | USBSIDL           | _                 | _                 | _                | UASUSPND         |

## REGISTER 10-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test is enabled

- 0 = Eye-Pattern Test is disabled

#### bit 6 **UOEMON:** USB OE Monitor Enable bit

1 = OE signal is active; it indicates intervals during which the D+/D- lines are driving

0 = OE signal is inactive

#### bit 5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

#### bit 3-1 Unimplemented: Read as '0'

### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 10-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock.

## TABLE 11-1: INPUT PIN SELECTION

| Peripheral Pin | [pin name]R SFR | [pin name]R bits | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection                                                                                   |

|----------------|-----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| INT4           | INT4R           | INT4R<3:0>       | 0000 = RPA0<br>0001 = RPB3                                                                                                           |

| T2CK           | T2CKR           | T2CKR<3:0>       | 0010 = RPB4<br>0011 = RPB15<br>0100 = RPB7                                                                                           |

| IC4            | IC4R            | IC4R<3:0>        | 0101 = RPC7 <sup>(2)</sup><br>0110 = RPC0 <sup>(1)</sup><br>0111 = RPC5 <sup>(2)</sup>                                               |

| SS1            | SS1R            | SS1R<3:0>        | 1000 = Reserved                                                                                                                      |

| REFCLKI        | REFCLKIR        | REFCLKIR<3:0>    | :<br>1111 = Reserved                                                                                                                 |

| INT3           | INT3R           | INT3R<3:0>       | 0000 = RPA1<br>0001 = RPB5                                                                                                           |

| ТЗСК           | T3CKR           | T3CKR<3:0>       | 0010 = RPB1<br>0011 = RPB11                                                                                                          |

| IC3            | IC3R            | IC3R<3:0>        | 0100 = RPB8<br>0101 = RPA8 <sup>(2)</sup>                                                                                            |

| U1CTS          | U1CTSR          | U1CTSR<3:0>      | 0110 = RPC8 <sup>(2)</sup><br>0111 = RPA9 <sup>(2)</sup>                                                                             |

| U2RX           | U2RXR           | U2RXR<3:0>       | 1000 = Reserved                                                                                                                      |

| SDI1           | SDI1R           | SDI1R<3:0>       | 1111 = Reserved                                                                                                                      |

| INT2           | INT2R           | INT2R<3:0>       | 0000 = RPA2                                                                                                                          |

| T4CK           | T4CKR           | T4CKR<3:0>       |                                                                                                                                      |

| IC1            | IC1R            | IC1R<3:0>        | 0011 = RPB13<br>0100 = RPB2                                                                                                          |

| IC5            | IC5R            | IC5R<3:0>        | 0101 = RPC6 <sup>(2)</sup>                                                                                                           |

| U1RX           | U1RXR           | U1RXR<3:0>       | 0110 = RPC1 <sup>(1)</sup><br>0111 = RPC3 <sup>(1)</sup>                                                                             |

| U2CTS          | U2CTSR          | U2CTSR<3:0>      | 1000 = Reserved                                                                                                                      |

| SDI2           | SDI2R           | SDI2R<3:0>       | •                                                                                                                                    |

| OCFB           | OCFBR           | OCFBR<3:0>       | •<br>1111 = Reserved                                                                                                                 |

| INT1           | INT1R           | INT1R<3:0>       | 0000 = RPA3<br>0001 = RPB14                                                                                                          |

| T5CK           | T5CKR           | T5CKR<3:0>       | 0010 = RPB0<br>0011 = RPB10<br>0100 = RPB9<br>0101 = RPC9 <sup>(1)</sup><br>0110 = RPC2 <sup>(2)</sup><br>0111 = RPC4 <sup>(2)</sup> |

| IC2            | IC2R            | IC2R<3:0>        |                                                                                                                                      |

| SS2            | SS2R            | SS2R<3:0>        | 1000 = Reserved                                                                                                                      |

| OCFA           | OCFAR           | OCFAR<3:0>       | •<br>•<br>1111 = Reserved                                                                                                            |

Note 1: This pin is not available on 28-pin devices.

2: This pin is only available on 44-pin devices.

## TABLE 11-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection       |

|--------------|----------|-------------|---------------------------------------------|

| RPA0         | RPA0R    | RPA0R<3:0>  | 0000 = No Connect                           |

| RPB3         | RPB3R    | RPB3R<3:0>  | 0001 = <u>U1TX</u><br>0010 = <u>U2RTS</u>   |

| RPB4         | RPB4R    | RPB4R<3:0>  | 0011 = SS1                                  |

| RPB15        | RPB15R   | RPB15R<3:0> |                                             |

| RPB7         | RPB7R    | RPB7R<3:0>  | 0110 = Reserved<br>0111 = C2OUT             |

| RPC7         | RPC7R    | RPC7R<3:0>  | 1000 = Reserved                             |

| RPC0         | RPC0R    | RPC0R<3:0>  | •                                           |

| RPC5         | RPC5R    | RPC5R<3:0>  | •<br>1111 = Reserved                        |

| RPA1         | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                           |

| RPB5         | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPB1         | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                 |

| RPB11        | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                   |

| RPB8         | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                             |

| RPA8         | RPA8R    | RPA8R<3:0>  |                                             |

| RPC8         | RPC8R    | RPC8R<3:0>  | •                                           |

| RPA9         | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                             |

| RPA2         | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                           |

| RPB6         | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPA4         | RPA4R    | RPA4R<3:0>  | 0011 = SDO1<br>0100 = SDO2                  |

| RPB13        | RPB13R   | RPB13R<3:0> | 0101 <b>= OC4</b>                           |

| RPB2         | RPB2R    | RPB2R<3:0>  |                                             |

| RPC6         | RPC6R    | RPC6R<3:0>  | 1000 = Reserved                             |

| RPC1         | RPC1R    | RPC1R<3:0>  |                                             |

| RPC3         | RPC3R    | RPC3R<3:0>  | 1111 = Reserved                             |

| RPA3         | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                           |

| RPB14        | RPB14R   | RPB14R<3:0> |                                             |

| RPB0         | RPB0R    | RPB0R<3:0>  | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |

| RPB10        | RPB10R   | RPB10R<3:0> | 0101 <b>= OC3</b>                           |

| RPB9         | RPB9R    | RPB9R<3:0>  |                                             |

| RPC9         | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                             |

| RPC2         | RPC2R    | RPC2R<3:0>  |                                             |

| RPC4         | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                             |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 |                   |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | -                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 |                   |                  | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              |                   | _                 |                   |                   |                   |                   | _                | _                |

## **REGISTER 11-3:** CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (X = A, B, C)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = Idle mode halts CN operation

- 0 = Idle does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

| REGIST    | ER 17-1: SPIXCON: SPI CONTROL REGISTER (CONTINUED)                                                                                                                                              |  |  |  |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| bit 17    | SPIFE: Frame Sync Pulse Edge Select bit (Framed SPI mode only)                                                                                                                                  |  |  |  |  |  |  |  |

|           | 1 = Frame synchronization pulse coincides with the first bit clock                                                                                                                              |  |  |  |  |  |  |  |

|           | 0 = Frame synchronization pulse precedes the first bit clock                                                                                                                                    |  |  |  |  |  |  |  |

| bit 16    | ENHBUF: Enhanced Buffer Enable bit <sup>(2)</sup>                                                                                                                                               |  |  |  |  |  |  |  |

|           | 1 = Enhanced Buffer mode is enabled                                                                                                                                                             |  |  |  |  |  |  |  |

|           | 0 = Enhanced Buffer mode is disabled                                                                                                                                                            |  |  |  |  |  |  |  |

| bit 15    | ON: SPI Peripheral On bit <sup>(1)</sup>                                                                                                                                                        |  |  |  |  |  |  |  |

|           | 1 = SPI Peripheral is enabled                                                                                                                                                                   |  |  |  |  |  |  |  |

|           | 0 = SPI Peripheral is disabled                                                                                                                                                                  |  |  |  |  |  |  |  |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                      |  |  |  |  |  |  |  |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                                                                                                     |  |  |  |  |  |  |  |

|           | 1 = Discontinue module operation when the device enters Idle mode                                                                                                                               |  |  |  |  |  |  |  |

|           | 0 = Continue module operation when the device enters Idle mode                                                                                                                                  |  |  |  |  |  |  |  |

| bit 12    | DISSDO: Disable SDOx pin bit                                                                                                                                                                    |  |  |  |  |  |  |  |

|           | 1 = SDOx pin is not used by the module. Pin is controlled by associated PORT register                                                                                                           |  |  |  |  |  |  |  |

|           | 0 = SDOx pin is controlled by the module                                                                                                                                                        |  |  |  |  |  |  |  |

| bit 11-10 | MODE<32,16>: 32/16-Bit Communication Select bits                                                                                                                                                |  |  |  |  |  |  |  |

|           | When AUDEN = 1:                                                                                                                                                                                 |  |  |  |  |  |  |  |

|           | MODE32 MODE16 Communication                                                                                                                                                                     |  |  |  |  |  |  |  |

|           | 1 1 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                                                       |  |  |  |  |  |  |  |

|           | 1 0 32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                                                       |  |  |  |  |  |  |  |

|           | 0116-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame0016-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame                                                                                  |  |  |  |  |  |  |  |

|           |                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|           | When AUDEN = 0:                                                                                                                                                                                 |  |  |  |  |  |  |  |

|           | MODE32 MODE16 Communication                                                                                                                                                                     |  |  |  |  |  |  |  |

|           | $1 \times 32$ -bit                                                                                                                                                                              |  |  |  |  |  |  |  |

|           | 0 1 <b>16-bit</b>                                                                                                                                                                               |  |  |  |  |  |  |  |

|           | 0 0 <b>8-bit</b>                                                                                                                                                                                |  |  |  |  |  |  |  |

| bit 9     | SMP: SPI Data Input Sample Phase bit                                                                                                                                                            |  |  |  |  |  |  |  |

|           | Master mode (MSTEN = 1):                                                                                                                                                                        |  |  |  |  |  |  |  |

|           | 1 = Input data sampled at end of data output time                                                                                                                                               |  |  |  |  |  |  |  |

|           | 0 = Input data sampled at middle of data output time                                                                                                                                            |  |  |  |  |  |  |  |

|           | <u>Slave mode (MSTEN = 0):</u><br>SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.                                                                          |  |  |  |  |  |  |  |

|           | -                                                                                                                                                                                               |  |  |  |  |  |  |  |

| hit 0     | To write a '1' to this bit, the MSTEN value = 1 must first be written.<br><b>CKE:</b> SPI Clock Edge Select bit <sup>(3)</sup>                                                                  |  |  |  |  |  |  |  |

| bit 8     | 1 = Serial output data changes on transition from active clock state to Idle clock state (see the CKP bit)                                                                                      |  |  |  |  |  |  |  |

|           | 0 = Serial output data changes on transition from Idle clock state to active clock state (see the CKP bit)                                                                                      |  |  |  |  |  |  |  |

| bit 7     | SSEN: Slave Select Enable (Slave mode) bit                                                                                                                                                      |  |  |  |  |  |  |  |

|           | 1 = SSx pin used for Slave mode                                                                                                                                                                 |  |  |  |  |  |  |  |

|           | $0 = \overline{SSx}$ pin not used for Slave mode, pin controlled by port function.                                                                                                              |  |  |  |  |  |  |  |

| bit 6     | CKP: Clock Polarity Select bit <sup>(4)</sup>                                                                                                                                                   |  |  |  |  |  |  |  |

|           | 1 = Idle state for clock is a high level; active state is a low level                                                                                                                           |  |  |  |  |  |  |  |

|           | 0 = Idle state for clock is a low level; active state is a high level                                                                                                                           |  |  |  |  |  |  |  |

|           |                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Note 1:   | When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. |  |  |  |  |  |  |  |

| 2:        | This bit can only be written when the ON bit = $0$ .                                                                                                                                            |  |  |  |  |  |  |  |

| 3:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI                                                                                         |  |  |  |  |  |  |  |

| 5.        | mode (FRMEN = 1).                                                                                                                                                                               |  |  |  |  |  |  |  |

| 4:        | When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value                                                                                      |  |  |  |  |  |  |  |

|           | of CKP.                                                                                                                                                                                         |  |  |  |  |  |  |  |

|           |                                                                                                                                                                                                 |  |  |  |  |  |  |  |

2

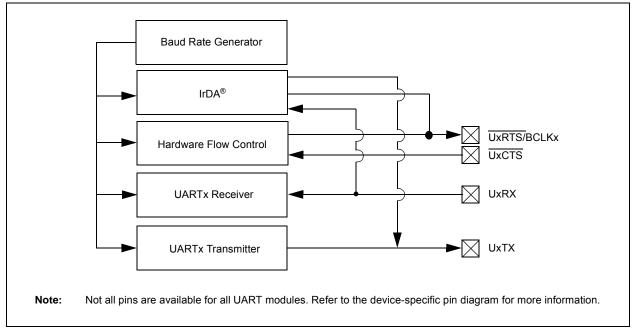

## 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The UART module is one of the serial I/O modules available in PIC32MX1XX/2XX 28/36/44-pin Family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN, and IrDA<sup>®</sup>. The UART module also supports the hardware flow control option, with UXCTS and UXRTS pins, and also includes an IrDA encoder and decoder.

Key features of the UART module include:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- · One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 38 bps to 12.5 Mbps at 50 MHz

- 8-level deep First In First Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9th bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the UART module.

### FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

## REGISTER 19-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | <ul> <li>ABAUD: Auto-Baud Enable bit</li> <li>1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55); cleared by hardware upon completion</li> <li>0 = Baud rate measurement disabled or completed</li> </ul> |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | RXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                           |

| bit 3   | BRGH: High Baud Rate Enable bit<br>1 = High-Speed mode – 4x baud clock enabled<br>0 = Standard Speed mode – 16x baud clock enabled                                                                                                                          |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits<br>11 = 9-bit data, no parity<br>10 = 8-bit data, odd parity<br>01 = 8-bit data, even parity<br>00 = 8-bit data, no parity                                                                                       |

| bit 0   | <b>STSEL:</b> Stop Selection bit<br>1 = 2 Stop bits<br>0 = 1 Stop bit                                                                                                                                                                                       |

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED) bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit 11 = Reserved; do not use 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (i.e., has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (i.e., has 4 or more data characters) 00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character) bit 5 ADDEN: Address Character Detect bit (bit 8 of received data = 1) 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect. 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 =Receiver is Idle 0 = Data is being received PERR: Parity Error Status bit (read-only) bit 3 1 = Parity error has been detected for the current character 0 = Parity error has not been detected bit 2 FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character 0 = Framing error has not been detected **OERR:** Receive Buffer Overrun Error Status bit. bit 1 This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and the RSR to an empty state. 1 = Receive buffer has overflowed 0 = Receive buffer has not overflowed bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

## REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

- bit 10 EDGSEQEN: Edge Sequence Enable bit 1 = Edge1 must occur before Edge2 can occur 0 = No edge sequence is needed IDISSEN: Analog Current Source Control bit<sup>(2)</sup> bit 9 1 = Analog current source output is grounded 0 = Analog current source output is not grounded bit 8 **CTTRIG:** Trigger Control bit 1 = Trigger output is enabled 0 = Trigger output is disabled bit 7-2 ITRIM<5:0>: Current Source Trim bits 011111 = Maximum positive change from nominal current 011110 000001 = Minimum positive change from nominal current 000000 = Nominal current output specified by IRNG<1:0> 111111 = Minimum negative change from nominal current 100010 100001 = Maximum negative change from nominal current bit 1-0 IRNG<1:0>: Current Range Select bits<sup>(3)</sup> 11 = 100 times base current 10 = 10 times base current

- 01 = Base current level

- 00 = 1000 times base current<sup>(4)</sup>

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical 3: Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

## 26.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- · Configuration bit select lock

### 26.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, PMDLOCK (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6.** "**Oscillator**" (DS60001112) in the "*PIC32 Family Reference Manual*" for details.

## 26.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The Configuration bit, PMDL1WAY (DEVCFG3<28>), blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

## 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

|                                  |       | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |                                                                                                                                                                                            |                        |            |       |                                                   |  |

|----------------------------------|-------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|-------|---------------------------------------------------|--|

|                                  |       |                                                                       | $\begin{array}{ll} \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |            |       |                                                   |  |

| Param.<br>No. Symbol Characteris |       | Characteristics                                                       | Min.                                                                                                                                                                                       | Typical <sup>(1)</sup> | Max.       | Units | Conditions                                        |  |

|                                  | VIL   | Input Low Voltage                                                     |                                                                                                                                                                                            |                        |            |       |                                                   |  |

| DI10                             |       | I/O Pins with PMP                                                     | Vss                                                                                                                                                                                        | —                      | 0.15 Vdd   | V     |                                                   |  |

|                                  |       | I/O Pins                                                              | Vss                                                                                                                                                                                        | —                      | 0.2 Vdd    | V     |                                                   |  |

| DI18                             |       | SDAx, SCLx                                                            | Vss                                                                                                                                                                                        | _                      | 0.3 Vdd    | V     | SMBus disabled<br>(Note 4)                        |  |

| DI19                             |       | SDAx, SCLx                                                            | Vss                                                                                                                                                                                        | —                      | 0.8        | V     | SMBus enabled<br>(Note 4)                         |  |

|                                  | VIH   | Input High Voltage                                                    |                                                                                                                                                                                            |                        |            |       |                                                   |  |

| DI20                             |       | I/O Pins not 5V-tolerant <sup>(5)</sup>                               | 0.65 VDD                                                                                                                                                                                   | _                      | Vdd        | V     | (Note 4,6)                                        |  |

|                                  |       | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>                       | 0.25 VDD + 0.8V                                                                                                                                                                            | —                      | 5.5        | V     | (Note 4,6)                                        |  |

|                                  |       | I/O Pins 5V-tolerant <sup>(5)</sup>                                   | 0.65 VDD                                                                                                                                                                                   | —                      | 5.5        | V     |                                                   |  |

| DI28                             |       | SDAx, SCLx                                                            | 0.65 VDD                                                                                                                                                                                   | _                      | 5.5        | V     | SMBus disabled<br>(Note 4,6)                      |  |

| DI29                             |       | SDAx, SCLx                                                            | 2.1                                                                                                                                                                                        | _                      | 5.5        | V     | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |  |

| DI30                             | ICNPU | Change Notification<br>Pull-up Current                                | _                                                                                                                                                                                          | —                      | -50        | μA    | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |  |

| DI31                             | ICNPD | Change Notification<br>Pull-down Current <sup>(4)</sup>               | _                                                                                                                                                                                          | —                      | -50        | μA    | VDD = 3.3V, VPIN = VDD                            |  |

|                                  | lı∟   | Input Leakage Current<br>(Note 3)                                     |                                                                                                                                                                                            |                        |            |       |                                                   |  |

| DI50                             |       | I/O Ports                                                             | _                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD$ ,<br>Pin at high-impedance |  |

| DI51                             |       | Analog Input Pins                                                     | _                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance  |  |

| DI55                             |       | MCLR <sup>(2)</sup>                                                   | —                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA    | $Vss \leq V PIN \leq V DD$                        |  |

| DI56                             |       | OSC1                                                                  | _                                                                                                                                                                                          | _                      | <u>+</u> 1 | μA    | $Vss \le VPIN \le VDD,$<br>XT and HS modes        |  |

## TABLE 30-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Pin Diagrams" section for the 5V-tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

## 31.1 DC Characteristics

## TABLE 31-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range                 | Temp. Range    | Max. Frequency                     |  |

|----------------|---------------------------|----------------|------------------------------------|--|

| Characteristic | (in Volts) <sup>(1)</sup> | (in °C)        | PIC32MX1XX/2XX 28/36/44-pin Family |  |

| MDC5           | 2.3-3.6V                  | -40°C to +85°C | 50 MHz                             |  |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 30-11 for BOR values.

## TABLE 31-2: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS                  |                        |      | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |        |  |  |  |  |

|-------------------------------------|------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|--|--|

| Parameter<br>No.                    | Typical <sup>(3)</sup> | Max. | Units Conditions                                                                                                                                    |        |  |  |  |  |

| Operating Current (IDD) (Note 1, 2) |                        |      |                                                                                                                                                     |        |  |  |  |  |

| MDC24                               | 25                     | 37   | mA                                                                                                                                                  | 50 MHz |  |  |  |  |

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, Program Flash, and SRAM data memory are operational, SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- 3: RTCC and JTAG are disabled

- **4:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

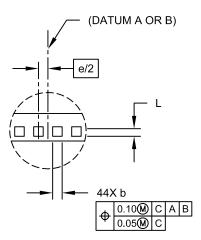

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | MILLIMETERS |          |      |       |  |

|-------------------------|-------------|----------|------|-------|--|

| Dimensior               | MIN         | NOM      | MAX  |       |  |

| Number of Pins          | N           | 44       |      |       |  |

| Number of Pins per Side | ND          | 12       |      |       |  |

| Number of Pins per Side | NE          |          | 10   |       |  |

| Pitch                   | е           | 0.50 BSC |      |       |  |

| Overall Height          | Α           | 0.80     | 0.90 | 1.00  |  |

| Standoff                | A1          | 0.025    | -    | 0.075 |  |

| Overall Width           | E           | 6.00 BSC |      |       |  |

| Exposed Pad Width       | E2          | 4.40     | 4.55 | 4.70  |  |

| Overall Length          | D           | 6.00 BSC |      |       |  |

| Exposed Pad Length      | D2          | 4.40     | 4.55 | 4.70  |  |

| Contact Width           | b           | 0.20     | 0.25 | 0.30  |  |

| Contact Length          | L           | 0.20     | 0.25 | 0.30  |  |

| Contact-to-Exposed Pad  | K           | 0.20     | -    | -     |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-157C Sheet 2 of 2

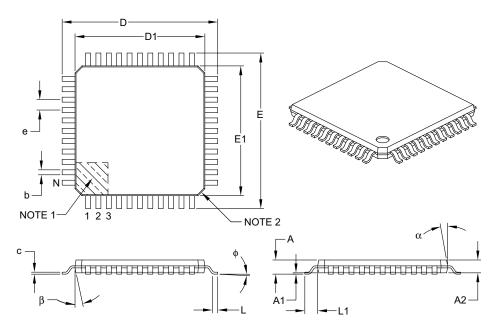

## 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |             |           | MILLIMETERS |  |  |  |

|--------------------------|------------------|-------------|-----------|-------------|--|--|--|

| Dime                     | Dimension Limits |             |           | MAX         |  |  |  |

| Number of Leads          | N                | 44          |           |             |  |  |  |

| Lead Pitch               | е                |             | 0.80 BSC  |             |  |  |  |

| Overall Height           | А                | _           | -         | 1.20        |  |  |  |

| Molded Package Thickness | A2               | 0.95        | 1.00      | 1.05        |  |  |  |

| Standoff                 | A1               | 0.05        | -         | 0.15        |  |  |  |

| Foot Length              | L                | 0.45        | 0.60      | 0.75        |  |  |  |

| Footprint                | L1 1.00 REF      |             |           |             |  |  |  |

| Foot Angle               | φ                | 0° 3.5° 7°  |           |             |  |  |  |

| Overall Width            | E                | 12.00 BSC   |           |             |  |  |  |

| Overall Length           | D                |             | 12.00 BSC |             |  |  |  |

| Molded Package Width     | E1               | 10.00 BSC   |           |             |  |  |  |

| Molded Package Length    | D1               |             | 10.00 BSC |             |  |  |  |

| Lead Thickness           | С                | 0.09        | -         | 0.20        |  |  |  |

| Lead Width               | b                | 0.30        | 0.37      | 0.45        |  |  |  |

| Mold Draft Angle Top     | α                | 11° 12° 13° |           |             |  |  |  |

| Mold Draft Angle Bottom  | β                | 11°         | 12°       | 13°         |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B