Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f032d-i-ml |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| (1)                                 | IRQ | Vector |              | Interru        | pt Bit Location |              | Persistent |

|-------------------------------------|-----|--------|--------------|----------------|-----------------|--------------|------------|

| Interrupt Source <sup>(1)</sup>     | #   | #      | Flag         | Enable         | Priority        | Sub-priority | Interrupt  |

|                                     |     | Highes | st Natural C | order Priority | 1               |              | •          |

| CT – Core Timer Interrupt           | 0   | 0      | IFS0<0>      | IEC0<0>        | IPC0<4:2>       | IPC0<1:0>    | No         |

| CS0 – Core Software Interrupt 0     | 1   | 1      | IFS0<1>      | IEC0<1>        | IPC0<12:10>     | IPC0<9:8>    | No         |

| CS1 – Core Software Interrupt 1     | 2   | 2      | IFS0<2>      | IEC0<2>        | IPC0<20:18>     | IPC0<17:16>  | No         |

| INT0 – External Interrupt           | 3   | 3      | IFS0<3>      | IEC0<3>        | IPC0<28:26>     | IPC0<25:24>  | No         |

| T1 – Timer1                         | 4   | 4      | IFS0<4>      | IEC0<4>        | IPC1<4:2>       | IPC1<1:0>    | No         |

| IC1E – Input Capture 1 Error        | 5   | 5      | IFS0<5>      | IEC0<5>        | IPC1<12:10>     | IPC1<9:8>    | Yes        |

| IC1 – Input Capture 1               | 6   | 5      | IFS0<6>      | IEC0<6>        | IPC1<12:10>     | IPC1<9:8>    | Yes        |

| OC1 – Output Compare 1              | 7   | 6      | IFS0<7>      | IEC0<7>        | IPC1<20:18>     | IPC1<17:16>  | No         |

| INT1 – External Interrupt 1         | 8   | 7      | IFS0<8>      | IEC0<8>        | IPC1<28:26>     | IPC1<25:24>  | No         |

| T2 – Timer2                         | 9   | 8      | IFS0<9>      | IEC0<9>        | IPC2<4:2>       | IPC2<1:0>    | No         |

| IC2E – Input Capture 2              | 10  | 9      | IFS0<10>     | IEC0<10>       | IPC2<12:10>     | IPC2<9:8>    | Yes        |

| IC2 – Input Capture 2               | 11  | 9      | IFS0<11>     | IEC0<11>       | IPC2<12:10>     | IPC2<9:8>    | Yes        |

| OC2 – Output Compare 2              | 12  | 10     | IFS0<12>     | IEC0<12>       | IPC2<20:18>     | IPC2<17:16>  | No         |

| INT2 – External Interrupt 2         | 13  | 11     | IFS0<13>     | IEC0<13>       | IPC2<28:26>     | IPC2<25:24>  | No         |

| T3 – Timer3                         | 14  | 12     | IFS0<14>     | IEC0<14>       | IPC3<4:2>       | IPC3<1:0>    | No         |

| IC3E – Input Capture 3              | 15  | 13     | IFS0<15>     | IEC0<15>       | IPC3<12:10>     | IPC3<9:8>    | Yes        |

| IC3 – Input Capture 3               | 16  | 13     | IFS0<16>     | IEC0<16>       | IPC3<12:10>     | IPC3<9:8>    | Yes        |

| OC3 – Output Compare 3              | 17  | 14     | IFS0<17>     | IEC0<17>       | IPC3<20:18>     | IPC3<17:16>  | No         |

| INT3 – External Interrupt 3         | 18  | 15     | IFS0<18>     | IEC0<18>       | IPC3<28:26>     | IPC3<25:24>  | No         |

| T4 – Timer4                         | 19  | 16     | IFS0<19>     | IEC0<19>       | IPC4<4:2>       | IPC4<1:0>    | No         |

| IC4E – Input Capture 4 Error        | 20  | 17     | IFS0<20>     | IEC0<20>       | IPC4<12:10>     | IPC4<9:8>    | Yes        |

| IC4 – Input Capture 4               | 21  | 17     | IFS0<21>     | IEC0<21>       | IPC4<12:10>     | IPC4<9:8>    | Yes        |

| OC4 – Output Compare 4              | 22  | 18     | IFS0<22>     | IEC0<22>       | IPC4<20:18>     | IPC4<17:16>  | No         |

| INT4 – External Interrupt 4         | 23  | 19     | IFS0<23>     | IEC0<23>       | IPC4<28:26>     | IPC4<25:24>  | No         |

| T5 – Timer5                         | 24  | 20     | IFS0<24>     | IEC0<24>       | IPC5<4:2>       | IPC5<1:0>    | No         |

| IC5E – Input Capture 5 Error        | 25  | 21     | IFS0<25>     | IEC0<25>       | IPC5<12:10>     | IPC5<9:8>    | Yes        |

| IC5 – Input Capture 5               | 26  | 21     | IFS0<26>     | IEC0<26>       | IPC5<12:10>     | IPC5<9:8>    | Yes        |

| OC5 – Output Compare 5              | 27  | 22     | IFS0<27>     | IEC0<27>       | IPC5<20:18>     | IPC5<17:16>  | No         |

| AD1 – ADC1 Convert done             | 28  | 23     | IFS0<28>     | IEC0<28>       | IPC5<28:26>     | IPC5<25:24>  | Yes        |

| FSCM – Fail-Safe Clock Monitor      | 29  | 24     | IFS0<29>     | IEC0<29>       | IPC6<4:2>       | IPC6<1:0>    | No         |

| RTCC – Real-Time Clock and Calendar | 30  | 25     | IFS0<30>     | IEC0<30>       | IPC6<12:10>     | IPC6<9:8>    | No         |

| FCE – Flash Control Event           | 31  | 26     | IFS0<31>     | IEC0<31>       | IPC6<20:18>     | IPC6<17:16>  | No         |

| CMP1 – Comparator Interrupt         | 32  | 27     | IFS1<0>      | IEC1<0>        | IPC6<28:26>     | IPC6<25:24>  | No         |

| CMP2 – Comparator Interrupt         | 33  | 28     | IFS1<1>      | IEC1<1>        | IPC7<4:2>       | IPC7<1:0>    | No         |

| CMP3 – Comparator Interrupt         | 34  | 29     | IFS1<2>      | IEC1<2>        | IPC7<12:10>     | IPC7<9:8>    | No         |

| USB – USB Interrupts                | 35  | 30     | IFS1<3>      | IEC1<3>        | IPC7<20:18>     | IPC7<17:16>  | Yes        |

| SPI1E – SPI1 Fault                  | 36  | 31     | IFS1<4>      | IEC1<4>        | IPC7<28:26>     | IPC7<25:24>  | Yes        |

| SPI1RX – SPI1 Receive Done          | 37  | 31     | IFS1<5>      | IEC1<5>        | IPC7<28:26>     | IPC7<25:24>  | Yes        |

| SPI1TX – SPI1 Transfer Done         | 38  | 31     | IFS1<6>      | IEC1<6>        | IPC7<28:26>     | IPC7<25:24>  | Yes        |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX1XX 28/36/44-Pin General Purpose Family Features" and TABLE 2: "PIC32MX2XX 28/36/44-pin USB Family Features" for the lists of available peripherals.

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

- bit 18-16 **PLLMULT<2:0>:** Phase-Locked Loop (PLL) Multiplier bits

- 111 = Clock is multiplied by 24

- 110 = Clock is multiplied by 21

- 101 = Clock is multiplied by 20

- 100 = Clock is multiplied by 19

- 011 = Clock is multiplied by 18

- 010 = Clock is multiplied by 17

- 001 = Clock is multiplied by 16

- 000 =Clock is multiplied by 15

- bit 15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (OSCCON<26:24>)

- 110 = Internal Fast RC (FRC) Oscillator divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (Posc) (XT, HS or EC)

- 001 = Internal Fast RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast RC (FRC) Oscillator

- bit 11 Unimplemented: Read as '0'

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits

- 111 = Internal Fast RC Oscillator (FRC) divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC Oscillator (FRC) divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (XT, HS or EC)

- 001 = Internal Fast Internal RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast Internal RC Oscillator (FRC)

On Reset, these bits are set to the value of the FNOSC Configuration bits (DEVCFG1<2:0>).

bit 7 CLKLOCK: Clock Selection Lock Enable bit

If clock switching and monitoring is disabled (FCKSM<1:0> = 1x):

- 1 = Clock and PLL selections are locked

- 0 = Clock and PLL selections are not locked and may be modified

If clock switching and monitoring is enabled (FCKSM<1:0> = 0x):

Clock and PLL selections are never locked and may be modified.

- bit 6 ULOCK: USB PLL Lock Status bit<sup>(1)</sup>

- 1 = The USB PLL module is in lock or USB PLL module start-up timer is satisfied

- 0 =The USB PLL module is out of lock or USB PLL module start-up timer is in progress or the USB PLL is disabled

- bit 5 SLOCK: PLL Lock Status bit

- 1 = The PLL module is in lock or PLL module start-up timer is satisfied

- 0 = The PLL module is out of lock, the PLL start-up timer is running, or the PLL is disabled

- bit 4 SLPEN: Sleep Mode Enable bit

- 1 = The device will enter Sleep mode when a WAIT instruction is executed

- 0 = The device will enter Idle mode when a WAIT instruction is executed

- **Note 1:** This bit is only available on PIC32MX2XX devices.

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

## TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP (CONTINUED)

| ess                         |                                 | ē             |        |                   |       |       | -      |       |      | Bi     | ts      |        |        |        |              |        |        |        | s          |

|-----------------------------|---------------------------------|---------------|--------|-------------------|-------|-------|--------|-------|------|--------|---------|--------|--------|--------|--------------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14             | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3         | 18/2   | 17/1   | 16/0   | All Resets |

| 3280                        | DCH2CPTR                        | 31:16         | —      | _                 | —     | _     |        | _     |      | —      |         | _      | _      |        |              | _      | _      |        | 0000       |

| 5200                        | DONZOFIK                        | 15:0          |        |                   |       |       |        |       |      | CHCPT  | R<15:0> |        |        |        |              |        |        |        | 0000       |

| 3290                        | DCH2DAT                         | 31:16         | _      | _                 | —     | —     |        | _     |      | —      | _       | _      | —      | _      | —            | _      | _      |        | 0000       |

| 3290                        | DCHZDAI                         | 15:0          | _      |                   | _     | _     |        | -     |      | -      |         |        |        | CHPDA  | AT<7:0>      |        |        |        | 0000       |

| 2240                        | DCH3CON                         | 31:16         | _      | _                 | _     | _     | _      | _     | _    | _      | _       | _      | _      | _      | _            | _      | _      | _      | 0000       |

| 32A0                        | DCH3CON                         | 15:0          | CHBUSY | _                 | _     | _     |        |       |      | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  | —            | CHEDET | CHPR   | l<1:0> | 0000       |

| 3280                        | DCH3ECON                        | 31:16         | —      | _                 | —     | —     | _      | _     | _    | —      |         |        |        | CHAIR  | Q<7:0>       |        |        |        | OOFF       |

| 5200                        |                                 | 15:0          |        |                   |       | CHSIR | Q<7:0> |       |      |        | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN       | _      | _      | _      | FF00       |

| 32C0                        | DCH3INT                         | 31:16         | —      | —                 | —     | —     | -      | _     | -    | —      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE       | CHCCIE | CHTAIE | CHERIE | 0000       |

| 0200                        |                                 | 15:0          | —      |                   |       | _     | —      | _     | —    | —      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF       | CHCCIF | CHTAIF | CHERIF | 0000       |

| 32D0                        | DCH3SSA                         | 31:16<br>15:0 |        |                   |       |       |        |       |      | CHSSA  | <31:0>  |        |        |        |              |        |        |        | 0000       |

|                             |                                 | 31:16         |        |                   |       |       |        |       |      |        |         |        |        |        |              |        |        |        | 0000       |

| 32E0                        | DCH3DSA                         | 15:0          |        |                   |       |       |        |       |      | CHDSA  | <31:0>  |        |        |        |              |        |        |        | 0000       |

| 0050                        | 00100017                        | 31:16         |        | _                 |       |       | _      | _     | _    |        |         |        |        |        |              | _      |        | _      | 0000       |

| 32FU                        | DCH3SSIZ                        | 15:0          |        |                   |       |       |        |       |      | CHSSIZ | 2<15:0> |        |        |        |              |        |        |        | 0000       |

| 2200                        | DCH3DSIZ                        | 31:16         | —      | —                 | —     | —     | _      | —     | —    | —      | _       | —      | —      | —      | —            | _      | —      | _      | 0000       |

| 3300                        | DCH3D3IZ                        | 15:0          |        |                   |       |       |        |       |      | CHDSIZ | 2<15:0> |        |        |        |              |        |        |        | 0000       |

| 3310                        | DCH3SPTR                        | 31:16         | —      | _                 | —     | _     |        |       |      | _      | —       |        | _      |        | _            |        |        |        | 0000       |

| 3310                        | DOI IJOF I K                    | 15:0          |        |                   |       |       |        |       |      | CHSPTF | ۲<15:0> |        |        |        |              |        |        |        | 0000       |

| 3320                        | DCH3DPTR                        | 31:16         | —      | —                 | —     | —     | _      | _     | _    | —      | _       | _      | —      | —      | —            | _      | —      | _      | 0000       |

| 0020                        |                                 | 15:0          |        |                   |       |       |        |       |      | CHDPT  | R<15:0> |        |        |        |              |        |        |        | 0000       |

| 3330                        | <b>DCH3CSIZ</b>                 | 31:16         | —      | _                 | —     | —     | —      | —     | —    | —      | —       | —      | —      | —      | —            | —      | —      | —      | 0000       |

|                             |                                 | 15:0          |        | CHCSIZ<15:0> 0000 |       |       |        |       |      |        |         |        |        |        |              |        |        |        |            |

| 3340                        | DCH3CPTR                        | 31:16         |        |                   |       |       |        |       |      |        |         |        |        |        |              |        |        |        |            |

|                             |                                 | 15:0          |        | CHCPTR<15:0> 0000 |       |       |        |       |      |        |         |        |        |        |              |        |        |        |            |

| 3350                        | DCH3DAT                         | 31:16         | —      | _                 | —     | _     | _      | _     | —    | _      | _       | —      | —      | -      | —<br>T :7 0: | —      | —      | —      | 0000       |

| <u> </u>                    |                                 | 15:0          | —      | —                 | —     | —     | —      | —     | —    | _      |         |        |        | CHPDA  | AT<7:0>      |        |        |        | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

NOTES:

## 11.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin-count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only option.

The Peripheral Pin Select (PPS) configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

## 11.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

## 11.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digitalonly peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the PPS feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin.

Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

### 11.3.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

## 11.3.4 INPUT MAPPING

The inputs of the PPS options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 11-1, are used to configure peripheral input mapping (see Register 11-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 11-1.

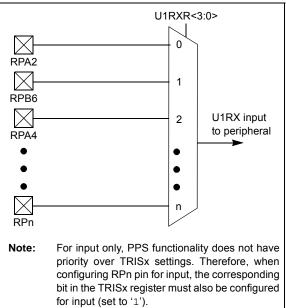

For example, Figure 11-2 illustrates the remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT EXAMPLE FOR U1RX

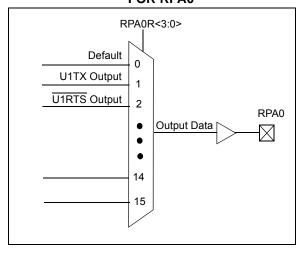

### 11.3.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the PPS options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 11-2) are used to control output mapping. Like the [*pin name*]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 11-2 and Figure 11-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPA0

## 11.3.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to the peripheral map:

- Control register lock sequence

- Configuration bit select lock

## 11.3.6.1 Control Register Lock Sequence

Under normal operation, writes to the RPnR and [*pin name*]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, IOLOCK (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

## 11.3.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [*pin name*]R registers. The Configuration bit, IOL1WAY (DEVCFG3<29>), blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the PPS control registers cannot be written to. The only way to clear the bit and reenable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

| TABL                        | E 11-7:              | PEI       | RIPHER |       | SELEC |       | PUT RE | GISTER | MAP ( | CONTIN | IUED) |      |      |      |      |      |        |      |            |

|-----------------------------|----------------------|-----------|--------|-------|-------|-------|--------|--------|-------|--------|-------|------|------|------|------|------|--------|------|------------|

| SS                          |                      |           |        |       |       |       |        |        |       | В      | its   |      |      |      |      |      |        |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10  | 25/9  | 24/8   | 23/7  | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| FB4C                        | RPB8R                | 31:16     | _      | -     | —     | -     | _      | -      | _     | _      | -     | —    | _    | —    | _    | _    | _      | —    | 0000       |

| 1040                        | IN DOIX              | 15:0      | _      |       | —     |       | —      |        | _     | —      |       |      | —    | —    |      | RPB8 | <3:0>  |      | 0000       |

| FB50                        | RPB9R                | 31:16     | —      | —     | —     | —     | —      | —      | _     | —      | —     | —    | —    | —    | _    | —    | —      | —    | 0000       |

| 1 830                       | KF D9K               | 15:0      | —      | _     | —     | _     | —      | —      | -     |        | —     | —    | —    | —    |      | RPB9 | <3:0>  |      | 0000       |

| FB54                        | RPB10R               | 31:16     | —      | _     | —     | _     | —      | —      | -     |        | —     | —    | —    | —    | -    | _    | —      | —    | 0000       |

| FB34                        | REDIUR               | 15:0      | —      | —     | _     | —     | —      | _      |       |        | —     | —    | —    | —    |      | RPB1 | 0<3:0> |      | 0000       |

| FB58                        | RPB11R               | 31:16     | —      | —     | _     | —     | —      | _      |       |        | —     | —    | —    | —    |      |      | _      | —    | 0000       |

| FB30                        | RPBIIR               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 1<3:0> |      | 0000       |

| FB60                        | RPB13R               | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB00                        | RPBISR               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 3<3:0> |      | 0000       |

| FB64                        | RPB14R               | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB04                        | KPD14K               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 4<3:0> |      | 0000       |

| FB68                        | RPB15R               | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB00                        | RPBIOR               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 5<3:0> |      | 0000       |

| FB6C                        | RPC0R <sup>(3)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FBOC                        | RECOR                | 15:0      | —      | —     | —     | —     | —      | —      | -     |        | —     | —    | -    | —    |      | RPCC | <3:0>  |      | 0000       |

| FB70                        | RPC1R <sup>(3)</sup> | 31:16     | —      | —     | _     | —     | —      | _      |       |        | —     | —    | —    | —    |      |      | _      | —    | 0000       |

| FB/U                        | RPUIK                | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC1 | <3:0>  |      | 0000       |

| FB74                        | RPC2R <sup>(1)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/4                        | RP62R <sup>4</sup>   | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC2 | <3:0>  |      | 0000       |

| FB78                        | RPC3R <sup>(3)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/0                        | RPGSR                | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC3 | <3:0>  |      | 0000       |

| FB7C                        | RPC4R <sup>(1)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/C                        | RPC4R <sup>V</sup>   | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC4 | <3:0>  |      | 0000       |

| FB80                        | RPC5R <sup>(1)</sup> | 31:16     |        | —     | —     | —     | —      | —      | _     |        | —     | _    | —    | —    | _    | _    | _      | _    | 0000       |

| FB80                        | RPUSK"               | 15:0      |        |       |       |       | —      | _      | _     | _      | _     |      | —    | —    |      | RPC5 | i<3:0> |      | 0000       |

| FB84                        | RPC6R <sup>(1)</sup> | 31:16     |        |       |       |       | —      | _      | _     | _      | _     |      | —    | —    | _    | —    |        | —    | 0000       |

| FB04                        | RPU0K"               | 15:0      |        |       |       |       | —      | _      | _     | _      | _     |      | —    | —    |      | RPC  | <3:0>  |      | 0000       |

| FB88                        | RPC7R <sup>(1)</sup> | 31:16     |        | —     |       | —     | —      | —      | _     |        | —     |      | —    | —    | _    | _    | —      |      | 0000       |

| F B 08                      | RPU/R <sup>(1)</sup> | 15:0      | _      | _     | —     | _     | _      | —      | —     | _      | —     |      | _    | _    |      | RPC7 | <3:0>  |      | 0000       |

#### OT AUTOUT DEALATED MAD

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is only available on 44-pin devices. Note 1:

2: 3:

This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices.

NOTES:

| REGIST    | ER 17-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)                                                         |

|-----------|------------------------------------------------------------------------------------------------------------|

| bit 17    | SPIFE: Frame Sync Pulse Edge Select bit (Framed SPI mode only)                                             |

|           | 1 = Frame synchronization pulse coincides with the first bit clock                                         |

|           | 0 = Frame synchronization pulse precedes the first bit clock                                               |

| bit 16    | ENHBUF: Enhanced Buffer Enable bit <sup>(2)</sup>                                                          |

|           | 1 = Enhanced Buffer mode is enabled                                                                        |

|           | 0 = Enhanced Buffer mode is disabled                                                                       |

| bit 15    | ON: SPI Peripheral On bit <sup>(1)</sup>                                                                   |

|           | 1 = SPI Peripheral is enabled                                                                              |

|           | 0 = SPI Peripheral is disabled                                                                             |

| bit 14    | Unimplemented: Read as '0'                                                                                 |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                |

|           | 1 = Discontinue module operation when the device enters Idle mode                                          |

|           | 0 = Continue module operation when the device enters Idle mode                                             |

| bit 12    | DISSDO: Disable SDOx pin bit                                                                               |

|           | 1 = SDOx pin is not used by the module. Pin is controlled by associated PORT register                      |

|           | 0 = SDOx pin is controlled by the module                                                                   |

| bit 11-10 | MODE<32,16>: 32/16-Bit Communication Select bits                                                           |

|           | When AUDEN = 1:                                                                                            |

|           | MODE32 MODE16 Communication                                                                                |

|           | 1 1 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                  |

|           | 1 0 32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                  |

|           | 0 1 16-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame                                                  |

|           | 0 0 16-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame                                                  |

|           |                                                                                                            |

|           | When AUDEN = 0:                                                                                            |

|           | MODE32 MODE16 Communication                                                                                |

|           | 1 x 32-bit<br>0 1 16-bit                                                                                   |

|           | 0 	 1 	 10-51                                                                                              |

| bit 9     | SMP: SPI Data Input Sample Phase bit                                                                       |

| bit 5     | Master mode (MSTEN = 1):                                                                                   |

|           | 1 = Input data sampled at end of data output time                                                          |

|           | 0 = Input data sampled at middle of data output time                                                       |

|           | Slave mode (MSTEN = 0):                                                                                    |

|           | SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.                       |

|           | To write a '1' to this bit, the MSTEN value = 1 must first be written.                                     |

| bit 8     | CKE: SPI Clock Edge Select bit <sup>(3)</sup>                                                              |

|           | 1 = Serial output data changes on transition from active clock state to Idle clock state (see the CKP bit) |

|           | 0 = Serial output data changes on transition from Idle clock state to active clock state (see the CKP bit) |

| bit 7     | SSEN: Slave Select Enable (Slave mode) bit                                                                 |

|           | $1 = \overline{SSx}$ pin used for Slave mode                                                               |

|           | 0 = SSx pin not used for Slave mode, pin controlled by port function.                                      |

| bit 6     | <b>CKP:</b> Clock Polarity Select bit <sup>(4)</sup>                                                       |

|           | 1 = Idle state for clock is a high level; active state is a low level                                      |

|           | 0 = Idle state for clock is a low level; active state is a high level                                      |

| Note 1:   | When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in    |

|           | the SYSCLK cycle immediately following the instruction that clears the module's ON bit.                    |

| 2:        | This bit can only be written when the ON bit = $0$ .                                                       |

| 3:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI    |

|           | mode (FRMEN = 1).                                                                                          |

| 4:        | When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value |

|           | of CKP.                                                                                                    |

|           |                                                                                                            |

2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | _                 | —                 | -                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 |                   | —                 | —                 | -                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |

#### REGISTER 19-1: UXMODE: UARTX MODE REGISTER

## Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by the UEN<1:0> and UTXEN control bits.

- 0 = UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal.

- bit 14 Unimplemented: Read as '0'

#### bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- $1 = \overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

- bit 10 Unimplemented: Read as '0'

- bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up enabled

- 0 = Wake-up disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 19-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED) bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit 11 = Reserved; do not use 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (i.e., has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (i.e., has 4 or more data characters) 00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character) bit 5 ADDEN: Address Character Detect bit (bit 8 of received data = 1) 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect. 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 =Receiver is Idle 0 = Data is being received PERR: Parity Error Status bit (read-only) bit 3 1 = Parity error has been detected for the current character 0 = Parity error has not been detected bit 2 FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character 0 = Framing error has not been detected **OERR:** Receive Buffer Overrun Error Status bit. bit 1 This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and the RSR to an empty state. 1 = Receive buffer has overflowed 0 = Receive buffer has not overflowed bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

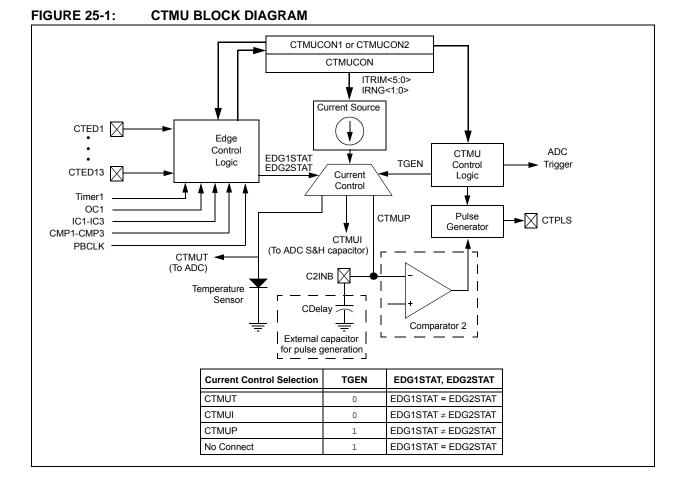

## 25.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that has a configurable current source with a digital configuration circuit built around it. The CTMU can be used for differential time measurement between pulse sources and can be used for generating an asynchronous pulse. By working with other on-chip analog modules, the CTMU can be used for high resolution time measurement, measure capacitance, measure relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

- Up to 13 channels available for capacitive or time measurement input

- · On-chip precision current source

- 16-edge input trigger sources

- · Selection of edge or level-sensitive inputs

- · Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · High precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- · Integrated temperature sensing diode

- · Control of current source during auto-sampling

- · Four current source ranges

- · Time measurement resolution of one nanosecond

A block diagram of the CTMU is shown in Figure 25-1.

© 2011-2016 Microchip Technology Inc.

#### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED) bit 24 EDG1STAT: Edge1 Status bit Indicates the status of Edge1 and can be written to control edge source 1 = Edge1 has occurred 0 = Edge1 has not occurred EDG2MOD: Edge2 Edge Sampling Select bit bit 23 1 = Input is edge-sensitive 0 = Input is level-sensitive bit 22 EDG2POL: Edge 2 Polarity Select bit 1 = Edge2 programmed for a positive edge response 0 = Edge2 programmed for a negative edge response bit 21-18 EDG2SEL<3:0>: Edge 2 Source Select bits 1111 = C3OUT pin is selected 1110 = C2OUT pin is selected 1101 = C1OUT pin is selected 1100 = PBCLK clock is selected 1011 = IC3 Capture Event is selected 1010 = IC2 Capture Event is selected 1001 = IC1 Capture Event is selected 1000 = CTED13 pin is selected 0111 = CTED12 pin is selected 0110 = CTED11 pin is selected 0101 = CTED10 pin is selected 0100 = CTED9 pin is selected 0011 = CTED1 pin is selected 0010 = CTED2 pin is selected 0001 = OC1 Compare Event is selected 0000 = Timer1 Event is selected bit 17-16 Unimplemented: Read as '0' bit 15 **ON:** ON Enable bit 1 = Module is enabled 0 = Module is disabled bit 14 Unimplemented: Read as '0' bit 13 CTMUSIDL: Stop in Idle Mode bit 1 = Discontinue module operation when the device enters Idle mode 0 = Continue module operation when the device enters Idle mode TGEN: Time Generation Enable bit<sup>(1)</sup> bit 12 1 = Enables edge delay generation 0 = Disables edge delay generation bit 11 EDGEN: Edge Enable bit 1 = Edges are not blocked 0 = Edges are blocked

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

NOTES:

| DC CHARACTERISTICS |        |                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |      |       |                                                             |  |

|--------------------|--------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------------------------------------------------------------|--|

| Param.             | Symbol | Characteristic      | Min.                                                                                                                                                                                                                                                                                | Тур. | Max. | Units | Conditions                                                  |  |

| DO10               | Vol    | Output Low Voltage  | _                                                                                                                                                                                                                                                                                   | _    | 0.4  | V     | $\text{IOL} \leq 10 \text{ mA}, \text{ VDD} = 3.3 \text{V}$ |  |

|                    |        | Output High Voltage | 1.5(1)                                                                                                                                                                                                                                                                              | _    | _    |       | IOH $\geq$ -14 mA, VDD = 3.3V                               |  |

| DO20               | Vон    | I/O Pins            | 2.0 <sup>(1)</sup>                                                                                                                                                                                                                                                                  | _    | _    | v     | IOH $\geq$ -12 mA, VDD = 3.3V                               |  |

| D020               | VOH    |                     | 2.4                                                                                                                                                                                                                                                                                 | _    | _    | v     | IOH $\geq$ -10 mA, VDD = 3.3V                               |  |

|                    |        |                     | 3.0(1)                                                                                                                                                                                                                                                                              | —    | —    |       | $IOH \ge -7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$         |  |

## TABLE 30-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized, but not tested.

### TABLE 30-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHA        | DC CHARACTERISTICS                                                 |                 |                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |                       |   |  |  |  |

|---------------|--------------------------------------------------------------------|-----------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|---|--|--|--|

| Param.<br>No. | Symbol                                                             | Characteristics | Min. <sup>(1)</sup> | Typical                                                                                                                                                                                                                                                                               | Max. | Max. Units Conditions |   |  |  |  |

| BO10          | O10 VBOR BOR Event on VDD transition<br>high-to-low <sup>(2)</sup> |                 |                     |                                                                                                                                                                                                                                                                                       | 2.3  | V                     | _ |  |  |  |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN.

### TABLE 30-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA          |         | ISTICS          |                               | Standard Operatin<br>(unless otherwise<br>Operating tempera | <b>stated)</b><br>iture -40 | )°C ≤ Ta ≤ | V to 3.6V<br>+85°C for Industrial<br>+105°C for V-temp |

|-----------------|---------|-----------------|-------------------------------|-------------------------------------------------------------|-----------------------------|------------|--------------------------------------------------------|

| Param.<br>No.   | Symbol  | Charact         | eristics                      | Min. <sup>(1)</sup>                                         | Max.                        | Units      | Conditions                                             |

| IM10 TLO:SCL CI |         | Clock Low Time  | 100 kHz mode                  | Трв * (BRG + 2)                                             | —                           | μs         | —                                                      |

|                 |         |                 | 400 kHz mode                  | Трв * (BRG + 2)                                             | _                           | μS         | —                                                      |

|                 |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | _                           | μs         | _                                                      |

| IM11            | THI:SCL | Clock High Time | 100 kHz mode                  | Трв * (BRG + 2)                                             | _                           | μs         | —                                                      |

|                 |         |                 | 400 kHz mode                  | Трв * (BRG + 2)                                             | _                           | μs         | —                                                      |

|                 |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2) —                                           |                             | μs         | —                                                      |

| IM20            | TF:SCL  | SDAx and SCLx   | 100 kHz mode                  | —                                                           | 300                         | ns         | CB is specified to be                                  |

|                 |         | Fall Time       | 400 kHz mode                  | 20 + 0.1 Св                                                 | 300                         | ns         | from 10 to 400 pF                                      |

|                 |         |                 | 1 MHz mode<br><b>(Note 2)</b> | _                                                           | 100                         | ns         |                                                        |

| IM21            | TR:SCL  | SDAx and SCLx   | 100 kHz mode                  | —                                                           | 1000                        | ns         | CB is specified to be                                  |

|                 |         | Rise Time       | 400 kHz mode                  | 20 + 0.1 Св                                                 | 300                         | ns         | from 10 to 400 pF                                      |

|                 |         |                 | 1 MHz mode<br><b>(Note 2)</b> | _                                                           | 300                         | ns         |                                                        |

| IM25            | TSU:DAT | Data Input      | 100 kHz mode                  | 250                                                         | _                           | ns         | —                                                      |

|                 |         | Setup Time      | 400 kHz mode                  | 100                                                         | —                           | ns         |                                                        |

|                 |         |                 | 1 MHz mode<br><b>(Note 2)</b> | 100                                                         | _                           | ns         |                                                        |

| IM26            | THD:DAT | Data Input      | 100 kHz mode                  | 0                                                           | _                           | μS         | —                                                      |

|                 |         | Hold Time       | 400 kHz mode                  | 0                                                           | 0.9                         | μs         |                                                        |

|                 |         |                 | 1 MHz mode<br>(Note 2)        | 0                                                           | 0.3                         | μs         |                                                        |

| IM30            | TSU:STA | Start Condition | 100 kHz mode                  | Трв * (BRG + 2)                                             | _                           | μS         | Only relevant for                                      |

|                 |         | Setup Time      | 400 kHz mode                  | Трв * (BRG + 2)                                             | —                           | μS         | Repeated Start condition                               |

|                 |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | —                           | μs         | condition                                              |

| IM31            | THD:STA | Start Condition | 100 kHz mode                  | Трв * (BRG + 2)                                             | —                           | μS         | After this period, the                                 |

|                 |         | Hold Time       | 400 kHz mode                  | Трв * (BRG + 2)                                             | —                           | μs         | first clock pulse is generated                         |

|                 |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | —                           | μS         | generaleu                                              |

| IM33            | Tsu:sto | Stop Condition  | 100 kHz mode                  | Трв * (BRG + 2)                                             |                             | μS         |                                                        |

|                 |         | Setup Time      | 400 kHz mode                  | Трв * (BRG + 2)                                             |                             | μs         |                                                        |

|                 |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             |                             | μs         |                                                        |

| IM34            | THD:STO | Stop Condition  | 100 kHz mode                  | Трв * (BRG + 2)                                             |                             | ns         | —                                                      |

|                 |         | Hold Time       | 400 kHz mode                  | Трв * (BRG + 2)                                             |                             | ns         | ]                                                      |

|                 |         |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | —                           | ns         |                                                        |

**Note 1:** BRG is the value of the  $I^2C$  Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

| AC CHARAG                         | CTERISTIC | S <sup>(2)</sup>      | (unless of | Operating<br>herwise state<br>temperature |                            |

|-----------------------------------|-----------|-----------------------|------------|-------------------------------------------|----------------------------|

| ADC Speed                         | TAD Min.  | Sampling<br>Time Min. | Rs Max.    | Vdd                                       | ADC Channels Configuration |

| 1 Msps to 400 ksps <sup>(1)</sup> | 65 ns     | 132 ns                | 500Ω       | 3.0V to<br>3.6V                           | ANX CHX ADC                |

| Up to 400 ksps                    | 200 ns    | 200 ns                | 5.0 kΩ     | 2.5V to<br>3.6V                           | ANX CHX<br>ANX OF VREF-    |

### TABLE 30-35:10-BIT CONVERSION RATE PARAMETERS

**Note 1:** External VREF- and VREF+ pins must be used for correct operation.

2: These parameters are characterized, but not tested in manufacturing.

**3:** The ADC module is functional at VBORMIN < VDD < 2.5V, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

NOTES:

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

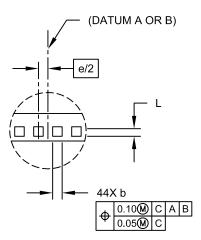

## 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | N      | <b>IILLIMETER</b> | S        |       |

|-------------------------|--------|-------------------|----------|-------|

| Dimensior               | Limits | MIN               | NOM      | MAX   |

| Number of Pins          | N      |                   | 44       |       |

| Number of Pins per Side | ND     |                   | 12       |       |

| Number of Pins per Side | NE     |                   | 10       |       |

| Pitch                   | е      |                   | 0.50 BSC |       |

| Overall Height          | A      | 0.80              | 0.90     | 1.00  |

| Standoff                | A1     | 0.025             | -        | 0.075 |

| Overall Width           | E      |                   | 6.00 BSC |       |

| Exposed Pad Width       | E2     | 4.40              | 4.55     | 4.70  |

| Overall Length          | D      |                   | 6.00 BSC |       |

| Exposed Pad Length      | D2     | 4.40              | 4.55     | 4.70  |

| Contact Width           | b      | 0.20              | 0.25     | 0.30  |

| Contact Length          | L      | 0.20              | 0.25     | 0.30  |

| Contact-to-Exposed Pad  | K      | 0.20              | -        | -     |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-157C Sheet 2 of 2

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support