Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f032d-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.2 Architecture Overview

The MIPS32 M4K processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- · Enhanced JTAG (EJTAG) Controller

### 3.2.1 EXECUTION UNIT

The MIPS32 M4K processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- · 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter and store aligner

### 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32 M4K processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

# TABLE 3-1:MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGERMULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES

| Opcode                  | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |

|-------------------------|------------------------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                                        | 2       | 2           |

| MUL                     | 16 bits                                        | 2       | 1           |

|                         | 32 bits                                        | 3       | 2           |

| DIV/DIVU                | 8 bits                                         | 12      | 11          |

|                         | 16 bits                                        | 19      | 18          |

|                         | 24 bits                                        | 26      | 25          |

|                         | 32 bits                                        | 33      | 32          |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        |                   | —                 | —                 | _                 | _                 | _                 | _                | —                |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | _                 | -                 | _                 |                   |                  | —                |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         |                   |                   |                   | CHSPTR            | <15:8>            |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          | CHSPTR<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

### REGISTER 9-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

### REGISTER 9-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   |                   | _                 | _                 | —                 |                   | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   |                   | _                 | _                 | —                 |                   | —                | —                |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | CHDPTR            | <15:8>            |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | CHDPTF            | R<7:0>            |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

1111111111111111 = Points to byte 65,535 of the destination

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

### REGISTER 10-3: U1OTGSTAT: USB OTG STATUS REGISTER

|              |                   |                   |                   | • • • • • • •     |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24        | -                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | —                 | —                 | —                 | _                 | —                 |                  | —                |

| 7:0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |

| 7.0          | ID                |                   | LSTATE            | _                 | SESVD             | SESEND            | _                | VBUSVD           |

### Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a "type B" cable has been inserted into the USB receptacle

- 0 = A "type A" OTG cable has been inserted into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (SE0 (U1CON<6>) bit and JSTATE (U1CON<7>)) bit has been stable for previous 1 ms 0 = USB line state (SE0 and JSTATE) has not been stable for previous 1 ms

### bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A or B device

- 0 = VBUS voltage is below Session Valid on the A or B device

- bit 2 SESEND: B-Device Session End Indicator bit

- 1 = VBUS voltage is below Session Valid on the B device

- 0 = VBUS voltage is above Session Valid on the B device

### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A device

- 0 = VBUS voltage is below Session Valid on the A device

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

### REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER (CONTINUED)

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup>

- 1 = Token packet rejected due to CRC5 error

- 0 = Token packet accepted

- EOFEF: EOF Error Flag bit<sup>(3,5)</sup>

- 1 = An EOF error condition was detected

- 0 = No EOF error condition was detected

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check failed

- 0 = PID check passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

### 11.4 Ports Control Registers

### TABLE 11-3: PORTA REGISTER MAP

| ess                         |                                 | 0         |       |       |       |       |       |                          |                       | Bits                    | 6                       |      |      |          |          |          |          |          | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|--------------------------|-----------------------|-------------------------|-------------------------|------|------|----------|----------|----------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10                    | 25/9                  | 24/8                    | 23/7                    | 22/6 | 21/5 | 20/4     | 19/3     | 18/2     | 17/1     | 16/0     | All Resets |

| 6000                        | ANSELA                          | 31:16     | _     | —     | —     | —     | _     | _                        | _                     | _                       | —                       |      | _    | _        | _        | —        | —        | _        | 0000       |

|                             |                                 | 15:0      | _     | —     | —     | —     | —     | -                        |                       |                         | —                       | _    | _    | —        | _        | _        | ANSA1    | ANSA0    | 0003       |

| 6010                        | TRISA                           | 31:16     | _     | —     | —     | —     | —     | —                        |                       |                         | —                       | _    | —    |          | —        | _        | _        | —        | 0000       |

| 0010                        |                                 | 15:0      | —     | —     | —     | —     | _     | TRISA10 <sup>(2)</sup>   | TRISA9 <sup>(2)</sup> | TRISA8 <sup>(2)</sup>   | TRISA7 <sup>(2)</sup>   | _    | —    | TRISA4   | TRISA3   | TRISA2   | TRISA1   | TRISA0   | 079F       |

| 6020                        | PORTA                           | 31:16     | —     | —     | —     | —     | _     | —                        | —                     | _                       | —                       | _    | —    |          |          |          |          |          | 0000       |

| 0020                        |                                 | 15:0      | —     | —     | —     | —     | _     | RA10 <sup>(2)</sup>      | RA9 <sup>(2)</sup>    | RA8 <sup>(2)</sup>      | RA7 <sup>(2)</sup>      | _    | —    | RA4      | RA3      | RA2      | RA1      | RA0      | xxxx       |

| 6030                        | LATA                            | 31:16     | _     | —     | —     | —     | _     |                          | _                     | _                       | —                       | —    | —    | _        | _        | _        |          | _        | 0000       |

| 0000                        |                                 | 15:0      | —     | —     | —     | —     | —     | LATA10 <sup>(2)</sup>    | LATA9 <sup>(2)</sup>  | LATA8 <sup>(2)</sup>    | LATA7 <sup>(2)</sup>    | —    | —    | LATA4    | LATA3    | LATA2    | LATA1    | LATA0    | xxxx       |

| 6040                        | ODCA                            | 31:16     | —     | —     | —     | —     | —     | —                        |                       | _                       | —                       | —    | —    | —        |          | —        |          |          | 0000       |

| 0040                        | ODOA                            | 15:0      | —     | —     | —     | —     | —     | ODCA10 <sup>(2)</sup>    | ODCA9 <sup>(2)</sup>  | ODCA8 <sup>(2)</sup>    | ODCA7 <sup>(2)</sup>    | —    | —    | ODCA4    | ODCA3    | ODCA2    | ODCA1    | ODCA0    | 0000       |

| 6050                        | CNPUA                           | 31:16     | —     | —     | —     | —     | —     | —                        | _                     | _                       | —                       | —    | —    | —        |          | —        |          |          | 0000       |

| 0030                        | CINFUA                          | 15:0      | _     | _     | —     | —     | _     | CNPUA10 <sup>(2)</sup>   | CNPUA9 <sup>(2)</sup> | CNPUA8 <sup>(2)</sup>   | CNPUA7 <sup>(2)</sup>   | _    | —    | CNPUA4   | CNPUA3   | CNPUA2   | CNPUA1   | CNPUA0   | 0000       |

| 6060                        | CNPDA                           | 31:16     | —     | —     | —     | —     |       | _                        |                       |                         |                         | —    | —    |          |          | —        |          |          | 0000       |

| 0000                        | CINFDA                          | 15:0      | _     | _     | —     | —     | _     | CNPDA10 <sup>(2)</sup>   | CNPDA9 <sup>(2)</sup> | CNPDA8 <sup>(2)</sup>   | CNPDA7 <sup>(2)</sup>   | _    | —    | CNPDA4   | CNPDA3   | CNPDA2   | CNPDA1   | CNPDA0   | 0000       |

| 6070                        | CNCONA                          | 31:16     | —     | —     | —     | —     |       | _                        |                       | _                       | _                       | —    | —    |          |          | —        |          |          | 0000       |

| 0070                        | CINCONA                         | 15:0      | ON    | —     | SIDL  | —     | _     | _                        | _                     | _                       | —                       | _    | _    | _        | —        | —        | —        | —        | 0000       |

| 6080                        | CNENA                           | 31:16     | _     | —     | —     | —     | _     | _                        | _                     | _                       | —                       | _    | —    | —        | _        | _        | _        | _        | 0000       |

| 0000                        | CINEINA                         | 15:0      | _     | _     | —     | —     |       | CNIEA10 <sup>(2)</sup>   | CNIEA9 <sup>(2)</sup> | CNIEA8 <sup>(2)</sup>   | CNIEA7 <sup>(2)</sup>   |      |      | CNIEA4   | CNIEA3   | CNIEA2   | CNIEA1   | CNIEA0   | 0000       |

| 6000                        | CNISTATA                        | 31:16     | _     | _     | —     | —     |       |                          |                       |                         | _                       |      | _    |          |          | —        | _        |          | 0000       |

| 0090                        | CNSTATA                         | 15:0      | _     | _     | —     | —     |       | CNSTATA10 <sup>(2)</sup> | CNSTATA9(2)           | CNSTATA8 <sup>(2)</sup> | CNSTATA7 <sup>(2)</sup> |      |      | CNSTATA4 | CNSTATA3 | CNSTATA2 | CNSTATA1 | CNSTATA0 | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This bit is only available on 44-pin devices.

| TABL                        | E 11-7:              | PEI       | RIPHER |       | SELEC |       | PUT RE | GISTER | MAP ( | CONTIN | IUED) |      |      |      |      |      |        |      |            |

|-----------------------------|----------------------|-----------|--------|-------|-------|-------|--------|--------|-------|--------|-------|------|------|------|------|------|--------|------|------------|

| SS                          |                      |           |        |       |       |       |        |        |       | В      | its   |      |      |      |      |      |        |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10  | 25/9  | 24/8   | 23/7  | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| FB4C                        | RPB8R                | 31:16     | _      | -     | —     | -     | _      | -      | _     | _      | -     | —    | _    | —    | _    | _    | _      | —    | 0000       |

| 1040                        | IN DOIX              | 15:0      | _      |       |       |       | —      |        | _     | —      |       |      | —    | —    |      | RPB8 | <3:0>  |      | 0000       |

| FB50                        | RPB9R                | 31:16     | —      | —     | —     | —     | —      | —      | _     | —      | —     | —    | —    | —    | _    | —    | —      | —    | 0000       |

| 1 830                       | KF D9K               | 15:0      | —      | _     | —     | _     | —      | —      | -     |        | _     | —    | —    | —    |      | RPB9 | <3:0>  |      | 0000       |

| FB54                        | RPB10R               | 31:16     | —      | _     | —     | _     | —      | —      | -     |        | _     | —    | _    | —    | -    | _    | —      | —    | 0000       |

| FB34                        | REDIUR               | 15:0      | —      | —     | _     | —     | —      | —      |       |        | —     | —    | —    | —    |      | RPB1 | 0<3:0> |      | 0000       |

| FB58                        | RPB11R               | 31:16     | —      | —     | _     | —     | —      | —      |       |        | —     | —    | —    | —    |      |      | _      | —    | 0000       |

| FB30                        | RPBIIR               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 1<3:0> |      | 0000       |

| FB60                        | RPB13R               | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB00                        | RPBISR               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 3<3:0> |      | 0000       |

| FB64                        | RPB14R               | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB04                        | KPD14K               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 4<3:0> |      | 0000       |

| FB68                        | RPB15R               | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB00                        | RPBIOR               | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPB1 | 5<3:0> |      | 0000       |

| FB6C                        | RPC0R <sup>(3)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FBOC                        | RECOR                | 15:0      | —      | —     | —     | —     | —      | —      | -     |        | —     | —    | -    | —    |      | RPCC | <3:0>  |      | 0000       |

| FB70                        | RPC1R <sup>(3)</sup> | 31:16     | —      | —     | _     | —     | —      | _      |       |        | —     | —    | —    | —    |      |      | _      | —    | 0000       |

| FB/U                        | RPUIK                | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC1 | <3:0>  |      | 0000       |

| FB74                        | RPC2R <sup>(1)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/4                        | RP62R <sup>V</sup>   | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC2 | <3:0>  |      | 0000       |

| FB78                        | RPC3R <sup>(3)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/0                        | RPGSR                | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC3 | <3:0>  |      | 0000       |

| FB7C                        | RPC4R <sup>(1)</sup> | 31:16     | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    | _    | _    | _      | _    | 0000       |

| FB/C                        | RPC4R <sup>V</sup>   | 15:0      | _      | —     | _     | _     | -      | —      | _     | _      | _     | _    | _    | —    |      | RPC4 | <3:0>  |      | 0000       |

| FB80                        | RPC5R <sup>(1)</sup> | 31:16     |        | —     | —     | —     | —      | —      | _     |        | —     |      | —    | —    | _    | _    | —      | _    | 0000       |

| FB80                        | KPUSK"               | 15:0      |        |       |       |       | —      | _      | _     | _      | —     |      | —    | —    |      | RPC5 | i<3:0> |      | 0000       |

| FB84                        | RPC6R <sup>(1)</sup> | 31:16     |        |       |       |       | —      | _      | _     | _      | _     |      | —    | —    | _    | —    |        | —    | 0000       |

| FB04                        | RPU0K"               | 15:0      |        |       |       |       | —      | _      | _     | _      | _     |      | —    | —    |      | RPC  | <3:0>  |      | 0000       |

| FB88                        | RPC7R <sup>(1)</sup> | 31:16     |        | —     |       | —     | —      | —      | _     |        | —     |      | —    | —    | _    | _    | —      |      | 0000       |

| F B 08                      | RPU/R <sup>(1)</sup> | 15:0      | _      | _     | —     | _     | _      | —      | —     | _      | —     |      | _    | _    |      | RPC7 | <3:0>  |      | 0000       |

### OT AUTOUT DEALATED MAD

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is only available on 44-pin devices. Note 1:

2: 3:

This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices.

### REGISTER 12-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

- bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit When TCS = 1: 1 = External clock input is synchronized 0 = External clock input is not synchronized When TCS = 0: This bit is ignored.

bit 1 TCS: Timer Clock Source Select bit 1 = External clock from TxCKI pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCmLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

### REGISTER 17-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    |     |     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1         | Bit<br>24/16/8/0 |        |                         |

|--------------|----------------------|-----|-----|-------------------|--------------------------|------------------|--------|-------------------------|

| 31:24        | U-0                  | U-0 | U-0 | U-0               | U-0                      | U-0              | U-0    | U-0                     |

| 31.24        | —                    | —   | —   | —                 | —                        | —                | _      | —                       |

| 23:16        | U-0                  | U-0 | U-0 | U-0               | U-0                      | U-0              | U-0    | U-0                     |

| 23.10        |                      |     | —   | —                 | —                        | —                | _      | —                       |

| 15:8         | R/W-0                | U-0 | U-0 | R/W-0             | R/W-0                    | R/W-0            | R/W-0  | R/W-0                   |

| 10.0         | SPISGNEXT            | —   | —   | FRMERREN          | SPIROVEN                 | SPITUREN         | IGNROV | IGNTUR                  |

| 7:0          | R/W-0                | U-0 | U-0 | U-0               | R/W-0                    | U-0              | R/W-0  | R/W-0                   |

| 7:0          | AUDEN <sup>(1)</sup> | _   | —   | —                 | AUDMONO <sup>(1,2)</sup> | —                | AUDMOD | )<1:0> <sup>(1,2)</sup> |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-16 Unimplemented: Read as '0'

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extended

- bit 14-13 Unimplemented: Read as '0'

- bit 12 **FRMERREN:** Enable Interrupt Events via FRMERR bit

- 1 = Frame Error overflow generates error events

- 0 = Frame Error does not generate error events

- bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

- 1 = Receive overflow generates error events

- 0 = Receive overflow does not generate error events

- bit 10 SPITUREN: Enable Interrupt Events via SPITUR bit

- 1 = Transmit underrun generates error events

- 0 = Transmit underrun does not generate error events

- bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions)

- 1 = A ROV is not a critical error; during ROV data in the FIFO is not overwritten by receive data

0 = A ROV is a critical error that stops SPI operation

- bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

- 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

- 0 = A TUR is a critical error that stops SPI operation

- bit 7 AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup>

- 1 = Audio protocol enabled

- 0 = Audio protocol disabled

- bit 6-5 Unimplemented: Read as '0'

- bit 3 AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup>

- 1 = Audio data is mono (Each data word is transmitted on both left and right channels)

- 0 = Audio data is stereo

- bit 2 Unimplemented: Read as '0'

- bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup>

- 11 = PCM/DSP mode

- 10 = Right-Justified mode

- 01 = Left-Justified mode

- $00 = I^2S \mod$

- **Note 1:** This bit can only be written when the ON bit = 0.

- **2:** This bit is only valid for AUDEN = 1.

### REGISTER 20-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Wait of 4 Трв

- 10 = Wait of 3 Трв

- 01 = Wait of 2 TPB

- 00 = Wait of 1 TPB (default)

For Read operations:

- 11 = Wait of 3 Трв

- 10 = Wait of 2 TPB

- 01 = Wait of 1 Трв

- 00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bit A14 is not subject to auto-increment/decrement if configured as Chip Select CS1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                   | _                     | -                 | _                 | -                 | -                 | _                | _                |  |

| 22:16        | U-0               | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                     |                   | _                 |                   | _                 | _                | _                |  |

|              | U-0               | R/W-0                 | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         |                   | CS1 <sup>(1)</sup>    |                   |                   | —                 | ADDR<10:8>        |                  |                  |  |

|              | —                 | ADDR14 <sup>(2)</sup> | _                 | _                 |                   |                   |                  |                  |  |

| 7:0          | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | ADDR<7:0>         |                       |                   |                   |                   |                   |                  |                  |  |

### REGISTER 20-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

- bit 31-15 **Unimplemented:** Read as '0'

- bit 14 **CS1:** Chip Select 1 bit<sup>(1)</sup>

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Destination Address bit 14<sup>(2)</sup>

- bit 13-11 Unimplemented: Read as '0'

- bit 10-0 ADDR<10:0>: Destination Address bits

- Note 1: When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | _                 | _                 | —                 | —                 | _                 | —                | —                |  |  |  |

| 22.16        | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        |                   | —                 | _                 | MONTH10           | MONTH01<3:0>      |                   |                  |                  |  |  |  |

| 45.0         | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         |                   | _                 | DAY1              | 0<1:0>            | DAY01<3:0>        |                   |                  |                  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          | —                 | _                 | _                 | _                 | —                 | V                 | VDAY01<2:0       | >                |  |  |  |

### REGISTER 21-6: ALRMDATE: ALARM DATE VALUE REGISTER

### Legend:

| Legena:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-21 Unimplemented: Read as '0'

bit 20 MONTH10: Binary Coded Decimal value of months bits, 10s place digit; contains a value of 0 or 1

bit 19-16 **MONTH01<3:0>:** Binary Coded Decimal value of months bits, 1s place digit; contains a value from 0 to 9 bit 15-14 **Unimplemented:** Read as '0'

bit 13-12 DAY10<1:0>: Binary Coded Decimal value of days bits, 10s place digit; contains a value from 0 to 3

bit 11-8 **DAY01<3:0>:** Binary Coded Decimal value of days bits, 1s place digit; contains a value from 0 to 9

bit 7-3 Unimplemented: Read as '0'

bit 2-0 WDAY01<2:0>: Binary Coded Decimal value of weekdays bits; contains a value from 0 to 6

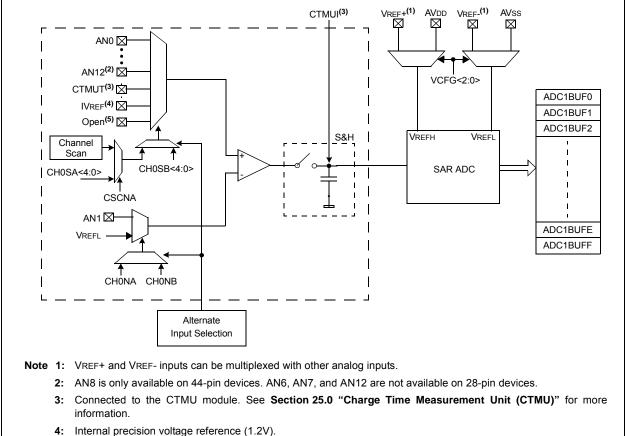

### 22.0 **10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)**

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- · Up to 1 Msps conversion speed

**FIGURE 22-1:**

- Up to 13 analog input pins

- External voltage reference input pins

- · One unipolar, differential Sample and Hold Amplifier (SHA)

- Automatic Channel Scan mode

- Selectable conversion trigger source

- · 16-word conversion result buffer

- Selectable buffer fill modes

- Eight conversion result format options

- · Operation during Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 22-1. Figure 22-2 illustrates a block diagram of the ADC conversion clock period. The 10-bit ADC has up to 13 analog input pins, designated AN0-AN12. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

### 5: This selection is only used with CTMU capacitive and time measurement.

ADC1 MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7                                   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------------------------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R                                                   | R                 | R                 | R                 | R                    | R                 | R                | R                |  |  |

| 31:24        | VER<3:0> <sup>(1)</sup> DEVID<27:24> <sup>(1)</sup> |                   |                   |                   |                      |                   |                  |                  |  |  |

| 00.40        | R                                                   | R                 | R                 | R                 | R                    | R                 | R                | R                |  |  |

| 23:16        | DEVID<23:16> <sup>(1)</sup>                         |                   |                   |                   |                      |                   |                  |                  |  |  |

| 45.0         | R                                                   | R                 | R                 | R                 | R                    | R                 | R                | R                |  |  |

| 15:8         |                                                     |                   |                   | DEVID<            | 15:8> <sup>(1)</sup> |                   |                  |                  |  |  |

| 7.0          | R                                                   | R                 | R                 | R                 | R                    | R                 | R                | R                |  |  |

| 7:0          |                                                     |                   |                   | DEVID             | <7:0>(1)             |                   |                  |                  |  |  |

### REGISTER 27-6: DEVID: DEVICE AND REVISION ID REGISTER

### Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 DEVID<27:0>: Device ID bits<sup>(1)</sup>

**Note 1:** See the "*PIC32 Flash Programming Specification*" (DS60001145) for a list of Revision and Device ID values.

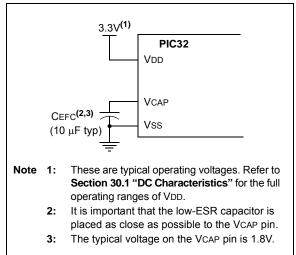

### 27.3 On-Chip Voltage Regulator

All PIC32MX1XX/2XX 28/36/44-pin Family devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX1XX/2XX 28/36/44-pin Family family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 30.1 "DC Characteristics"**.

| Note: | It is important that the low-ESR capacitor |

|-------|--------------------------------------------|

|       | is placed as close as possible to the VCAP |

|       | pin.                                       |

### 27.3.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

### 27.3.2 ON-CHIP REGULATOR AND BOR

PIC32MX1XX/2XX 28/36/44-pin Family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 30.1 "DC Characteristics"**.

## FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

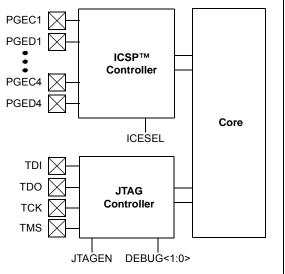

### 27.4 Programming and Diagnostics

PIC32MX1XX/2XX 28/36/44-pin Family devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

Figure 27-2 illustrates a block diagram of the programming, debugging, and trace ports.

### 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

### 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

### 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

### TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS                                  |       |                                                                     | Standard<br>(unless ot<br>Operating | herwise | ture -40°C | $\leq$ Ta $\leq$ + | -85°C fo                       | r Industrial<br>or V-temp            |

|-----------------------------------------------------|-------|---------------------------------------------------------------------|-------------------------------------|---------|------------|--------------------|--------------------------------|--------------------------------------|

| Param.<br>No. Symbol Characteristics <sup>(1)</sup> |       |                                                                     | cs <sup>(1)</sup>                   | Min.    | Typical    | Max.               | Units                          | Conditions                           |

| OS50                                                | Fplli | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |                                     | 3.92    | _          | 5                  | MHz                            | ECPLL, HSPLL, XTPLL,<br>FRCPLL modes |

| OS51                                                | Fsys  | On-Chip VCO System<br>Frequency                                     |                                     | 60      | —          | 120                | MHz                            | _                                    |

| OS52                                                | TLOCK | PLL Start-up Time (Lock Time)                                       |                                     | _       | _          | 2                  | ms                             | —                                    |

| OS53                                                | DCLK  | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Cum              | -0.25                               | —       | +0.25      | %                  | Measured over 100 ms<br>period |                                      |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

### TABLE 30-19: INTERNAL FRC ACCURACY

| АС СНА                        | AC CHARACTERISTICS                              |                 | Standard Operating Conditions: 2.3V to 3.6Vunless otherwise stated)Dperating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |       |            |  |  |  |  |

|-------------------------------|-------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|--|

| Param.<br>No. Characteristics |                                                 | Min.            | Typical                                                                                                                                                                                           | Max. | Units | Conditions |  |  |  |  |

| Internal                      | Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |                 |                                                                                                                                                                                                   |      |       |            |  |  |  |  |

| F20b                          | FRC                                             | -0.9 — +0.9 % — |                                                                                                                                                                                                   |      |       |            |  |  |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

### TABLE 30-20: INTERNAL LPRC ACCURACY

| АС СНА                        | RACTERISTICS               | (unless | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |            |  |  |  |

|-------------------------------|----------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|

| Param.<br>No. Characteristics |                            | Min.    | Typical                                                                                                                                                                                                                                                                               | Max. | Units | Conditions |  |  |  |

| LPRC @                        | 2 31.25 kHz <sup>(1)</sup> |         |                                                                                                                                                                                                                                                                                       |      |       |            |  |  |  |

| F21                           | LPRC                       | _       |                                                                                                                                                                                                                                                                                       |      |       |            |  |  |  |

**Note 1:** Change of LPRC frequency as VDD changes.

### TABLE 30-24: TIMER2, 3, 4, 5 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS (unle |           |                                                           |                                | (unless   | Standard Operating Conditions: 2.3V to 3.6V<br>unless otherwise stated)<br>Deprating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |       |                                     |                       |  |

|--------------------------|-----------|-----------------------------------------------------------|--------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------------------------------------|-----------------------|--|

| Param.<br>No.            | Symbol    | Characteristics <sup>(1)</sup>                            |                                |           | Min.                                                                                                                                                                                                         | Max. | Units | Condit                              | ions                  |  |

| TB10                     | ТтхН      | TxCK<br>High Time                                         | Synchronous, with<br>prescaler |           | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns                                                                                                                                                                            | —    | ns    | Must also meet<br>parameter<br>TB15 | value<br>(1, 2, 4, 8, |  |

| TB11                     | ΤτχL      | TxCK<br>Low Time                                          | Synchron<br>prescaler          | ous, with | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns                                                                                                                                                                            | _    | ns    | Must also meet<br>parameter<br>TB15 | 16, 32, 64,<br>256)   |  |

| TB15                     | ΤτχΡ      | TxCK<br>Input                                             | Synchrono<br>prescaler         | ous, with | [(Greater of [(25 ns or<br>2 ТРВ)/N] + 30 ns                                                                                                                                                                 | -    | ns    | VDD > 2.7V                          |                       |  |

|                          |           | Period                                                    |                                |           | [(Greater of [(25 ns or<br>2 ТРВ)/N] + 50 ns                                                                                                                                                                 |      |       |                                     |                       |  |

| TB20                     | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer Increment |                                |           |                                                                                                                                                                                                              | 1    | Трв   | _                                   |                       |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

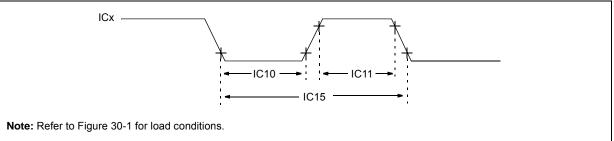

### FIGURE 30-7: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

### TABLE 30-25: INPUT CAPTURE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | $\label{eq:standard operating Conditions: 2.3V to 3.6V} \end{tabular} \begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                                   |      |       |                                         |                                  |

|--------------------|--------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------|-------|-----------------------------------------|----------------------------------|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup> |                                                                                                                            | Min.                              | Max. | Units | Conditions                              |                                  |

| IC10               | TccL   | ICx Input                      | Low Time                                                                                                                   | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns | _    | ns    | Must also<br>meet<br>parameter<br>IC15. | N = prescale<br>value (1, 4, 16) |

| IC11               | ТссН   | ICx Input                      | : High Time                                                                                                                | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns | —    | ns    | Must also<br>meet<br>parameter<br>IC15. |                                  |

| IC15               | TCCP   | ICx Input                      | Period                                                                                                                     | [(25 ns or 2 Трв)/N]<br>+ 50 ns   | _    | ns    | —                                       |                                  |

| Note 1: | These parameters are | characterized, but not | t tested in manufacturing. |

|---------|----------------------|------------------------|----------------------------|

|---------|----------------------|------------------------|----------------------------|

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

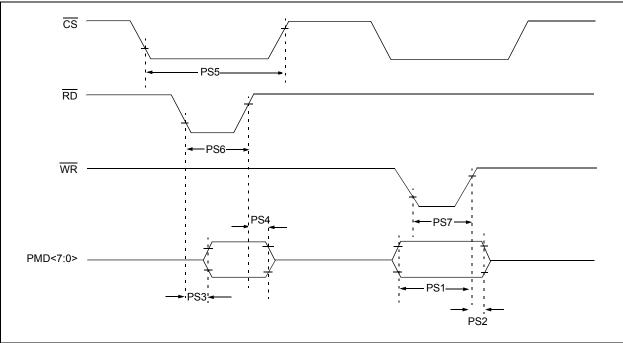

### FIGURE 30-20: PARALLEL SLAVE PORT TIMING

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support