Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 44-VTLA (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f032d-v-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

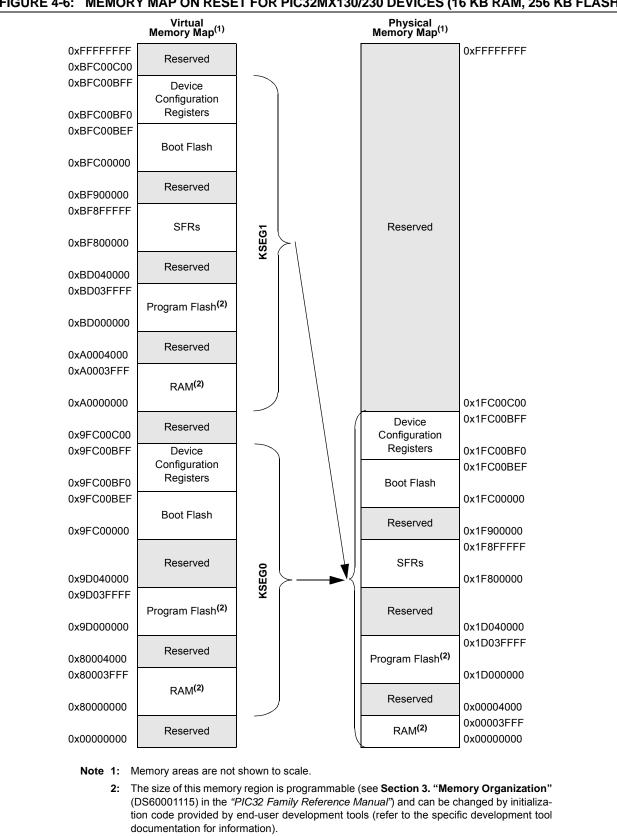

#### FIGURE 4-6: MEMORY MAP ON RESET FOR PIC32MX130/230 DEVICES (16 KB RAM, 256 KB FLASH)

|              | -                 |                   |                      |                       |                        |                   |                  |                  |

|--------------|-------------------|-------------------|----------------------|-----------------------|------------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                    | —                     | —                      |                   | _                |                  |

| 00.40        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                    | —                     | —                      | —                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0                   | R-0                    | U-0               | U-0              | U-0              |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | LVDSTAT <sup>(1)</sup> |                   | _                |                  |

| 7.0          | U-0               | U-0               | U-0                  | U-0                   | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 |                      | —                     |                        | NVMOF             | P<3:0>           |                  |

|              |                   |                   |                      |                       |                        |                   |                  |                  |

#### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re- | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

| 011 31-10           | Unimplemented. Read as 0                                                                                              |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|

| bit 15              | WR: Write Control bit                                                                                                 |

|                     | This bit is writable when WREN = 1 and the unlock sequence is followed.                                               |

|                     | 1 = Initiate a Flash operation. Hardware clears this bit when the operation completes                                 |

|                     | 0 = Flash operation is complete or inactive                                                                           |

| bit 14              | WREN: Write Enable bit                                                                                                |

|                     | This is the only bit in this register reset by a device Reset.                                                        |

|                     | 1 = Enable writes to WR bit and enables LVD circuit                                                                   |

|                     | 0 = Disable writes to WR bit and disables LVD circuit                                                                 |

| bit 13              | WRERR: Write Error bit <sup>(1)</sup>                                                                                 |

|                     | This bit is read-only and is automatically set by hardware.                                                           |

|                     | 1 = Program or erase sequence did not complete successfully                                                           |

|                     | 0 = Program or erase sequence completed normally                                                                      |

| bit 12              | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(1)</sup>                                     |

|                     | This bit is read-only and is automatically set by hardware.                                                           |

|                     | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                                                  |

|                     | 0 = Voltage level is acceptable for programming                                                                       |

| bit 11              | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(1)</sup>                                   |

|                     | This bit is read-only and is automatically set and cleared by the hardware.                                           |

|                     | 1 = Low-voltage event is active                                                                                       |

| hit 10 1            | 0 = Low-voltage event is not active                                                                                   |

| bit 10-4<br>bit 3-0 | Unimplemented: Read as '0'                                                                                            |

| 0-6 110             | <b>NVMOP&lt;3:0&gt;:</b> NVM Operation bits<br>These bits are writable when WREN = 0.                                 |

|                     |                                                                                                                       |

|                     | 1111 = Reserved                                                                                                       |

|                     | •                                                                                                                     |

|                     | •                                                                                                                     |

|                     | 0111 = Reserved<br>0110 = No operation                                                                                |

|                     | 0101 = Program Flash Memory (PFM) erase operation: erases PFM, if all pages are not write-protected                   |

|                     | 0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected                            |

|                     | 0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected                          |

|                     | 0010 = No operation                                                                                                   |

|                     | 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected<br>0000 = No operation |

|                     |                                                                                                                       |

**Note 1:** This bit is cleared by setting NVMOP == `b0000, and initiating a Flash operation (i.e., WR).

|              |                   |                      | OULEAIO           |                   |                   |                       |                  |                  |

|--------------|-------------------|----------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0                  | R/W-y             | R/W-y             | R/W-y             | R/W-0                 | R/W-0            | R/W-1            |

| 31:24        | —                 | —                    | Р                 | LLODIV<2:0        | <b>`</b>          | F                     | RCDIV<2:0>       |                  |

| 00.40        | U-0               | R-0                  | R-1               | R/W-y             | R/W-y             | R/W-y                 | R/W-y            | R/W-y            |

| 23:16        | —                 | SOSCRDY              | PBDIVRDY          | PBDI              | /<1:0>            | Р                     | LLMULT<2:0>      | •                |

| 45.0         | U-0               | R-0                  | R-0               | R-0               | U-0               | R/W-y                 | R/W-y            | R/W-y            |

| 15:8         | —                 |                      | COSC<2:0>         |                   | —                 |                       | NOSC<2:0>        |                  |

| 7:0          | R/W-0             | R-0                  | R-0               | R/W-0             | R/W-0             | R/W-0                 | R/W-y            | R/W-0            |

| 7:0          | CLKLOCK           | ULOCK <sup>(1)</sup> | SLOCK             | SLPEN             | CF                | UFRCEN <sup>(1)</sup> | SOSCEN           | OSWEN            |

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| Legend:           | y = Value set from Co | onfiguration bits on POR |                    |

|-------------------|-----------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bi     | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-30 **Unimplemented:** Read as '0'

#### bit 29-27 **PLLODIV<2:0>:** Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

#### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

- 1 = The Secondary Oscillator is running and is stable

- 0 = The Secondary Oscillator is still warming up or is turned off

- bit 21 **PBDIVRDY:** Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

Note 1: This bit is only available on PIC32MX2XX devices.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | DCRCDAT           | 4<31:24>          |                   |                  |                  |

| 00.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | DCRCDAT           | 4<23:16>          |                   |                  |                  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | DCRCDAT           | A<15:8>           |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | DCRCDA            | TA<7:0>           |                   |                  |                  |

#### REGISTER 9-5: DCRCDATA: DMA CRC DATA REGISTER

# Legend:

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

### REGISTER 9-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   | DCRCXOR<31:24>    |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   | DCRCXOR<15:8>     |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

| ILCIOIC L    |                   |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | —                 | _                 | —                 | _                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 |                   | _                 | _                 |                   | _                |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHCSIZ            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHCSIZ            | <7:0>             |                   |                  |                  |

# REGISTER 9-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell Size bits

1111111111111111 = 65,535 bytes transferred on an event

### REGISTER 9-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER

|              |                   |                   | ••••••••••••••••••••••••••••••••••••••• |                   |                   |                   | -                |                  |

|--------------|-------------------|-------------------|-----------------------------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5                       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.04        | U-0               | U-0               | U-0                                     | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | —                                       | —                 | _                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0                                     | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                                       | —                 | —                 | —                 | —                | —                |

| 45.0         | R-0               | R-0               | R-0                                     | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                                         | CHCPTR            | <15:8>            |                   |                  |                  |

| 7:0          | R-0               | R-0               | R-0                                     | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                                         | CHCPTF            | R<7:0>            |                   |                  |                  |

| Legend:           |                                      |                      |                    |  |  |

|-------------------|--------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | Readable bit W = Writable bit U = Un |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                     | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 31-16 Unimplemented: Read as '0'

Note: When in Pattern Detect mode, this register is reset on a pattern detect.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | —                 | _                 | -                 | _                 | _                 | -                | —                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | —                 | —                 | _                 | -                 | _                 | _                 | -                | —                |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         |                   | —                 |                   | _                 | _                 |                   | _                | —                |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | CHPDAT<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

# REGISTER 9-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

# Legend:

| =0901141          |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 CHPDAT<7:0>: Channel Data Register bits

Pattern Terminate mode: Data to be matched must be stored in this register to allow a "terminate on match".

All other modes: Unused.

| REGIST       | Cedister 101. Ototoir. Osboro interrort Statos register |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

|--------------|---------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

| 31:24        | U-0                                                     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31.24        | -                                                       | —                 | —                 | -                 | -                 | —                 | -                | —                |  |  |  |  |  |

| 23:16        | U-0                                                     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23.10        | -                                                       | —                 | —                 | -                 | -                 | —                 | -                | —                |  |  |  |  |  |

| 15:8         | U-0                                                     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 15.6         |                                                         | _                 | -                 |                   |                   | —                 |                  | —                |  |  |  |  |  |

| 7.0          | R/WC-0, HS                                              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS        | U-0              | R/WC-0, HS       |  |  |  |  |  |

| 7:0          | IDIF                                                    | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          |                  | VBUSVDIF         |  |  |  |  |  |

# REGISTER 10-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit         |                    |  |  |  |

|-------------------|-------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIF:** ID State Change Indicator bit

- 1 = A change in the ID state was detected

- 0 = No change in the ID state was detected

- bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

#### bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1 ms, but different from last time

- 0 = USB line state has not been stable for 1 ms

- bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

- bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = A change on the session valid input was detected

- 0 = No change on the session valid input was detected

#### REGISTER 10-10: U1STAT: USB STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   |                   | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | —                 |                   |                   |                   | _                 | _                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | _                 | —                 |                   |                   |                   | _                 | _                | —                |

| 7:0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | U-0              | U-0              |

| 7.0          |                   | ENDP              | T<3:0>            |                   | DIR               | PPBI              |                  |                  |

#### Legend:

|                   |                  |                           |                    | wn |

|-------------------|------------------|---------------------------|--------------------|----|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |    |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7-4 **ENDPT<3:0>:** Encoded Number of Last Endpoint Activity bits (Represents the number of the Buffer Descriptor Table, updated by the last USB transfer.)

- 1111 = Endpoint 15 1110 = Endpoint 14 . . 0001 = Endpoint 1 0000 = Endpoint 0

- bit 3 **DIR:** Last Buffer Descriptor Direction Indicator bit

- 1 = Last transaction was a transmit (TX) transfer

- 0 = Last transaction was a receive (RX) transfer

- bit 2 **PPBI:** Ping-Pong Buffer Descriptor Pointer Indicator bit

- 1 = The last transaction was to the ODD Buffer Descriptor bank

- 0 = The last transaction was to the EVEN Buffer Descriptor bank

- bit 1-0 Unimplemented: Read as '0'

**Note:** The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when the TRNIF (U1IR<3>) bit is active. Clearing the TRNIF bit advances the FIFO. Data in register is invalid when the TRNIF bit = 0.

# TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                      |           |       | Bits  |       |       |       |       |      |      |      |      |      |      |             |      |      |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|-------------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3        | 18/2 | 17/1 | 16/0 | All Resets |

| 5000                        | RPC8R <sup>(1)</sup> | 31:16     | _     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _           | —    | —    | —    | 0000       |

| FB8C                        | RPCort               | 15:0      | —     | —     | —     | —     | —     | _     | —    | —    | _    | —    | —    | —    | RPC8<3:0>   |      |      |      | 0000       |

| 5000                        | RPC9R <sup>(3)</sup> | 31:16     | —     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _           | —    | —    |      | 0000       |

| FB90                        | RPC9R**              | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    | RPC9<3:0> 0 |      |      |      | 0000       |

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1:

2:

This register is only available on 44-pin devices. This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices. 3:

NOTES:

# 18.1 I2C Control Registers

# TABLE 18-1: I2C1 AND I2C2 REGISTER MAP

| ess                         |                                 |               |              |            |                       |              |              |              |                    | Bi         | ts        |                  |                |            |           |          |           |          |            |

|-----------------------------|---------------------------------|---------------|--------------|------------|-----------------------|--------------|--------------|--------------|--------------------|------------|-----------|------------------|----------------|------------|-----------|----------|-----------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15        | 30/14      | 29/13                 | 28/12        | 27/11        | 26/10        | 25/9               | 24/8       | 23/7      | 22/6             | 21/5           | 20/4       | 19/3      | 18/2     | 17/1      | 16/0     | All Resets |

| 5000                        | I2C1CON                         | 31:16<br>15:0 | —<br>ON      |            | —<br>SIDL             | —<br>SCLREL  | —<br>STRICT  | —<br>A10M    | —<br>DISSLW        | —<br>SMEN  | —<br>GCEN | —<br>STREN       | —<br>ACKDT     | —<br>ACKEN | —<br>RCEN | —<br>PEN | —<br>RSEN | —<br>SEN | 0000       |

|                             | 100 10717                       | 31:16         | _            | _          | _                     | _            | _            | _            | _                  | _          | _         | _                | _              | _          | _         | _        | _         | _        | 0000       |

| 5010                        | I2C1STAT                        | 15:0          | ACKSTAT      | TRSTAT     | _                     | _            | _            | BCL          | GCSTAT             | ADD10      | IWCOL     | I2COV            | D_A            | Р          | S         | R_W      | RBF       | TBF      | 0000       |

| 5000                        | I2C1ADD                         | 31:16         | _            | _          | _                     | —            | —            | -            | —                  | _          | —         | _                | _              | _          | -         | _        | _         | _        | 0000       |

| 5020                        | IZCIADD                         | 15:0          | _            | —          | _                     | —            | —            | _            | Address Register 0 |            |           |                  |                |            |           |          | 0000      |          |            |

| 5030                        | I2C1MSK                         | 31:16         | _            | _          |                       | -            |              |              |                    |            |           |                  |                |            |           |          | 0000      |          |            |

| 5050                        | 120 11031                       | 15:0          | _            | —          | Address Mask Register |              |              |              |                    |            |           |                  |                |            | 0000      |          |           |          |            |

| 5040                        | I2C1BRG                         |               |              |            |                       |              |              |              | —                  | 0000       |           |                  |                |            |           |          |           |          |            |

| 0040                        | 1201BIXO                        | 15:0          | —            | —          | _                     | —            |              |              |                    |            | Bau       | id Rate Ger      | erator Reg     | ister      |           |          |           |          | 0000       |

| 5050                        | I2C1TRN                         | 31:16         | —            | —          | —                     | —            | —            | —            | —                  | —          | —         | —                | —              | —          | —         |          | —         | —        | 0000       |

|                             | 15:0 —                          |               |              |            | _                     | —            | —            | _            | —                  | _          |           |                  |                | Transmit   | Register  |          |           |          | 0000       |

| 5060                        | I2C1RCV                         | 31:16         | _            | _          |                       |              |              |              |                    | _          | _         | —                |                | —          | —         | —        | —         | —        | 0000       |

|                             |                                 | 15:0          | _            | —          |                       |              | —            |              | —                  | _          |           |                  |                | Receive    |           |          |           |          | 0000       |

| 5100                        | I2C2CON                         | 31:16         | _            | —          | _                     | —            | —            | _            | —                  | _          | —         | —                | _              | —          | _         | —        | —         | —        | 0000       |

|                             |                                 | 15:0          | ON           | _          | SIDL                  | SCLREL       | STRICT       | A10M         | DISSLW             | SMEN       | GCEN      | STREN            | ACKDT          | ACKEN      | RCEN      | PEN      | RSEN      | SEN      | 1000       |

| 5110                        | I2C2STAT                        | 31:16         | -            | -          |                       |              |              | -            | —                  | -          | -         | —                | —              | -          | _         | _        | -         | -        | 0000       |

|                             |                                 |               | ACKSTAT      | TRSTAT     |                       | —            | —            | BCL          | GCSTAT             | ADD10      | IWCOL     | I2COV            | D_A            | Р          | S         | R_W      | RBF       | TBF      | 0000       |

| 5120                        | I2C2ADD                         | 31:16         | _            | _          | —                     | _            | _            | _            | _                  | _          | _         | _                |                | —          | -         | _        |           | _        | 0000       |

|                             |                                 | 15:0<br>31:16 |              |            |                       | —            |              |              |                    |            |           |                  | Address        | Register   |           |          |           |          | 0000       |

| 5130                        | I2C2MSK                         | 15:0          | _            |            | _                     |              |              |              | _                  | _          | _         | _                | <br>Addross Mr |            | -         | _        | _         | _        | 0000       |

|                             |                                 |               |              |            |                       |              |              |              | _                  | 0000       |           |                  |                |            |           |          |           |          |            |

| 5140                        | I2C2BRG                         | 15:0          | _            |            |                       |              |              |              |                    |            | Bai       | I<br>Id Rate Ger | erator Reg     | ister      |           |          |           |          | 0000       |

|                             |                                 | 31:16         | _            | _          | _                     |              | _            | _            | _                  | _          |           | _                | _              | _          | _         |          | _         | _        | 0000       |

| 5150                        | I2C2TRN                         | 15:0          | _            | _          | _                     | _            | _            | _            | _                  | _          |           |                  |                | Transmit   | Register  |          |           |          | 0000       |

|                             |                                 | 31:16         | _            | _          | _                     | _            | _            | _            | _                  | _          | _         | _                | _              | _          | _         |          | _         | _        | 0000       |

| 5160                        | I2C2RCV                         | 15:0          | _            | _          | _                     | _            | _            | _            | _                  | _          |           |                  |                | Receive    | Register  |          |           |          | 0000       |

| Legen                       | d: x=u                          | nknow         | n value on l | Reset; — = | unimpleme             | nted, read a | as '0'. Rese | t values are | e shown in h       | exadecimal |           |                  |                |            | •         |          |           |          |            |

All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information. Note 1:

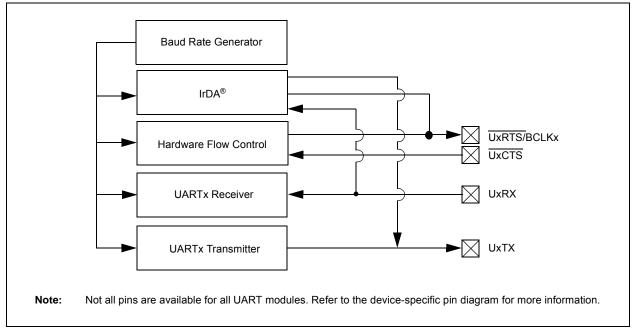

# 19.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The UART module is one of the serial I/O modules available in PIC32MX1XX/2XX 28/36/44-pin Family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN, and IrDA<sup>®</sup>. The UART module also supports the hardware flow control option, with UXCTS and UXRTS pins, and also includes an IrDA encoder and decoder.

Key features of the UART module include:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- · One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 38 bps to 12.5 Mbps at 50 MHz

- 8-level deep First In First Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9th bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 19-1 illustrates a simplified block diagram of the UART module.

#### FIGURE 19-1: UART SIMPLIFIED BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | _                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | _                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |  |  |

| 45.0         | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | _                 | PTEN14            | _                 | _                 | —                 | PTEN<10:8>        |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          | PTEN<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

# REGISTER 20-4: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-15 Unimplemented: Read as '0'

- bit 15-14 **PTEN14:** PMCS1 Address Port Enable bits

- 1 = PMA14 functions as either PMA14 or PMCS1<sup>(1)</sup>

- 0 = PMA14 functions as port I/O

- bit 13-11 Unimplemented: Read as '0'

- bit 10-2 PTEN<10:2>: PMP Address Port Enable bits

- 1 = PMA<10:2> function as PMP address lines

- 0 = PMA<10:2> function as port I/O

#### bit 1-0 PTEN<1:0>: PMALH/PMALL Address Port Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads functions as port I/O

- Note 1: The use of this pin as PMA14 or CS1 is selected by the CSF<1:0> bits in the PMCON register.

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by bits ADRMUX<1:0> in the PMCON register.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        |                   |                   | HR10              | <1:0>             | HR01<3:0>         |                   |                  |                  |  |  |

| 00.40        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        |                   |                   | MIN10<2:0>        |                   | MIN01<3:0>        |                   |                  |                  |  |  |

| 45.0         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         |                   |                   | SEC10<2:0>        |                   | SEC01<3:0>        |                   |                  |                  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

|              |                   | 1                 | 1                 |                   |                   |                   |                  |                  |  |  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 21-3: RTCTIME: RTC TIME VALUE REGISTER

# R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary-Coded Decimal Value of Hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 **HR01<3:0>:** Binary-Coded Decimal Value of Hours bits, 1s place digit; contains a value from 0 to 9 bit 23 **Unimplemented:** Read as '0'

bit 22-20 MIN10<2:0>: Binary-Coded Decimal Value of Minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 **MIN01<3:0>:** Binary-Coded Decimal Value of Minutes bits, 1s place digit; contains a value from 0 to 9 bit 15 **Unimplemented:** Read as '0'

bit 14-12 SEC10<2:0>: Binary-Coded Decimal Value of Seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 **SEC01<3:0>:** Binary-Coded Decimal Value of Seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

x = Bit is unknown

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 31.24        | EDG1MOD           | EDG1POL           |                   | EDG1S               | EDG2STAT          | EDG1STAT          |                        |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | U-0                    | U-0              |

| 23.10        | EDG2MOD           | EDG2POL           |                   | EDG2S               | —                 | —                 |                        |                  |

| 15:8         | R/W-0             | U-0               | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 15.0         | ON                | —                 | CTMUSIDL          | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN          | IDISSEN <sup>(2)</sup> | CTTRIG           |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 7.0          | ITRIM<5:0>        |                   |                   |                     |                   | IRNG<1:0>         |                        |                  |

#### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER

# Legend:

| Logona.                           |                  |                           |                    |

|-----------------------------------|------------------|---------------------------|--------------------|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

- bit 31 EDG1MOD: Edge1 Edge Sampling Select bit

- 1 = Input is edge-sensitive

- 0 = Input is level-sensitive

- bit 30 EDG1POL: Edge 1 Polarity Select bit

- 1 = Edge1 programmed for a positive edge response

- 0 = Edge1 programmed for a negative edge response

- bit 29-26 EDG1SEL<3:0>: Edge 1 Source Select bits

- 1111 = C3OUT pin is selected

- 1110 = C2OUT pin is selected

- 1101 = C1OUT pin is selected

- 1100 = IC3 Capture Event is selected

- 1011 = IC2 Capture Event is selected

- 1010 = IC1 Capture Event is selected

- 1001 = CTED8 pin is selected

- 1000 = CTED7 pin is selected

- 0111 = CTED6 pin is selected

- 0110 = CTED5 pin is selected

- 0101 = CTED4 pin is selected

- 0100 = CTED3 pin is selected

- 0011 = CTED1 pin is selected

- 0010 = CTED2 pin is selected

- 0001 = OC1 Compare Event is selected 0000 = Timer1 Event is selected

#### bit 25 EDG2STAT: Edge2 Status bit

Indicates the status of Edge2 and can be written to control edge source

- 1 = Edge2 has occurred

- 0 = Edge2 has not occurred

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

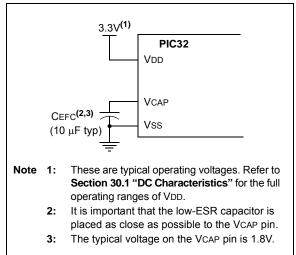

# 27.3 On-Chip Voltage Regulator

All PIC32MX1XX/2XX 28/36/44-pin Family devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX1XX/2XX 28/36/44-pin Family family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 30.1 "DC Characteristics"**.

| Note: | It is important that the low-ESR capacitor |

|-------|--------------------------------------------|

|       | is placed as close as possible to the VCAP |

|       | pin.                                       |

# 27.3.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

# 27.3.2 ON-CHIP REGULATOR AND BOR

PIC32MX1XX/2XX 28/36/44-pin Family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 30.1 "DC Characteristics"**.

# FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

# 27.4 Programming and Diagnostics

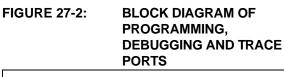

PIC32MX1XX/2XX 28/36/44-pin Family devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

Figure 27-2 illustrates a block diagram of the programming, debugging, and trace ports.

# 28.0 INSTRUCTION SET

The PIC32MX1XX/2XX family instruction set complies with the MIPS32<sup>®</sup> Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

**Note:** Refer to "*MIPS32*<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set" at www.imgtec.com for more information.

| TABLE 30-0.                                                        |          |     |                                                                                                                                                                                                                                                                                   |                 |      |               |  |  |

|--------------------------------------------------------------------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|---------------|--|--|

| DC CHARACT                                                         | ERISTICS |     | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |                 |      |               |  |  |

| Parameter Typical <sup>(2)</sup> Max.                              |          |     | Units Conditions                                                                                                                                                                                                                                                                  |                 |      |               |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (Notes 1, 4) |          |     |                                                                                                                                                                                                                                                                                   |                 |      |               |  |  |

| DC30a                                                              | 1        | 1.5 | mA                                                                                                                                                                                                                                                                                | 4 MHz (Note 3)  |      |               |  |  |

| DC31a                                                              | 2        | 3   | mA                                                                                                                                                                                                                                                                                | 10 MHz          |      |               |  |  |

| DC32a                                                              | 4        | 6   | mA                                                                                                                                                                                                                                                                                | 20 MHz (Note 3) |      |               |  |  |

| DC33a                                                              | 5.5      | 8   | mA                                                                                                                                                                                                                                                                                | 30 MHz (Note 3) |      |               |  |  |

| DC34a                                                              | 7.5      | 11  | mA                                                                                                                                                                                                                                                                                | 40 MHz          |      |               |  |  |

| DC37a                                                              | 100      | _   | μA                                                                                                                                                                                                                                                                                | -40°C           |      | LPRC (31 kHz) |  |  |

| DC37b                                                              | 250      | _   | μA                                                                                                                                                                                                                                                                                | +25°C           | 3.3V | (Note 3)      |  |  |

| DC37c                                                              | 380      |     | μA                                                                                                                                                                                                                                                                                | +85°C           | 1    |               |  |  |

#### TABLE 30-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

**Note 1:** The test conditions for IIDLE current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

OSC2/CLKO is configured as an I/O input pin

- UCD DLL as sillator is dischard if the LLCD readule is implemented

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode (CPU core Halted), and SRAM data memory Wait states = 1  $\,$

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- 4: IIDLE electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

| DC CHARACTERISTICS |        |                     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |   |       |            |                                                     |

|--------------------|--------|---------------------|------------------------------------------------------|---|-------|------------|-----------------------------------------------------|

| Param.             | Symbol | Characteristic      | Min. Typ. Max. Un                                    |   | Units | Conditions |                                                     |

| DO10               | Vol    | Output Low Voltage  | _                                                    | _ | 0.4   | V          | $\text{IOL} \leq 10 \text{ mA, VDD} = 3.3 \text{V}$ |

| DO20               | Vон    | Output High Voltage | 1.5(1)                                               | _ | _     |            | IOH $\geq$ -14 mA, VDD = 3.3V                       |

|                    |        | I/O Pins            | 2.0 <sup>(1)</sup>                                   | _ | _     | v          | IOH $\geq$ -12 mA, VDD = 3.3V                       |

|                    |        |                     | 2.4                                                  | _ | _     | v          | IOH $\geq$ -10 mA, VDD = 3.3V                       |

|                    |        |                     | 3.0(1)                                               | — | —     |            | $IOH \ge -7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$ |

### TABLE 30-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized, but not tested.

#### TABLE 30-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        |                                                           | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |         |      |       |            |

|--------------------|--------|-----------------------------------------------------------|------------------------------------------------------|---------|------|-------|------------|

| Param.<br>No.      | Symbol | Characteristics                                           | Min. <sup>(1)</sup>                                  | Typical | Max. | Units | Conditions |

| BO10               | VBOR   | BOR Event on VDD transition<br>high-to-low <sup>(2)</sup> | 2.0                                                  | —       | 2.3  | V     | _          |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN.

# **Revision F (February 2014)**

This revision includes the addition of the following devices:

In addition, this revision includes the following major changes as described in Table A-5, as well as minor updates to text and formatting, which were incorporated throughout the document.

- PIC32MX170F256B PIC32MX270F256B

- PIC32MX170F256D

PIC32MX270F256D

### TABLE A-5: MAJOR SECTION UPDATES

| Section                                                                                                                           | Update Description                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32-bit Microcontrollers (up to 256<br>KB Flash and 64 KB SRAM) with<br>Audio and Graphics Interfaces,<br>USB, and Advanced Analog | Added new devices to the family features (see Table 1 and Table 2).<br>Updated pin diagrams to include new devices (see " <b>Pin Diagrams</b> ").    |

| 1.0 "Device Overview"                                                                                                             | Added Note 3 reference to the following pin names: VBUS, VUSB3V3, VBUSON, D+, D-, and USBID.                                                         |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                          | Replaced Figure 2-1: Recommended Minimum Connection.<br>Updated Figure 2-2: MCLR Pin Connections.<br>Added <b>2.9 "Sosc Design Recommendation"</b> . |

| 4.0 "Memory Organization"                                                                                                         | Added memory tables for devices with 64 KB RAM (see Table 4-4 through Table 4-5).                                                                    |

|                                                                                                                                   | Changed the Virtual Addresses for all registers and updated the PWP bits in the DEVCFG: Device Configuration Word Summary (see Table 4-17).          |

|                                                                                                                                   | Updated the ODCA, ODCB, and ODCC port registers (see Table 4-19, Table 4-20, and Table 4-21).                                                        |

|                                                                                                                                   | The RTCTIME, RTCDATE, ALRMTIME, and ALRMDATE registers were updated (see Table 4-25).                                                                |

|                                                                                                                                   | Added Data Ram Size value for 64 KB RAM devices (see Register 4-5).                                                                                  |

|                                                                                                                                   | Added Program Flash Size value for 256 KB Flash devices (see Register 4-5).                                                                          |

| 12.0 "Timer1"                                                                                                                     | The Timer1 block diagram was updated to include the 16-bit data bus (see Figure 12-1).                                                               |

| 13.0 "Timer2/3, Timer4/5"                                                                                                         | The Timer2-Timer5 block diagram (16-bit) was updated to include the 16-bit data bus (see Figure 13-1).                                               |

|                                                                                                                                   | The Timer2/3, Timer4/5 block diagram (32-bit) was updated to include the 32-<br>bit data bus (see Figure 13-1).                                      |

| 19.0 "Parallel Master Port (PMP)"                                                                                                 | The CSF<1:0> bit value definitions for '00' and '01' were updated (see Register 19-1).                                                               |

|                                                                                                                                   | Bit 14 in the Parallel Port Address register (PMADDR) was updated (see Register 19-3).                                                               |