Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · · · · · · · · · · · · · · · · · · ·                                           |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

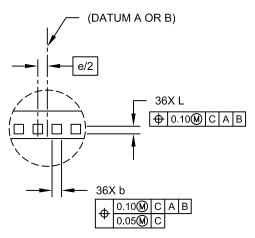

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx120f032dt-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 12: PIN NAMES FOR 44-PIN USB DEVICES

#### 44-PIN TQFP (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016D PIC32MX220F032D PIC32MX230F064D PIC32MX230F256D PIC32MX250F128D PIC32MX270F256D

44

1

| Pin # | Full Pin Name                                    | Pin # | Full Pin Name                             |

|-------|--------------------------------------------------|-------|-------------------------------------------|

| 1     |                                                  | 23    |                                           |

|       | RPB9/SDA1/CTED4/PMD3/RB9                         | 23    | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2 |

| 2     | RPC6/PMA1/RC6                                    |       | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3   |

| 3     | RPC7/PMA0/RC7                                    | 25    | AN6/RPC0/RC0                              |

| 4     | RPC8/PMA5/RC8                                    | 26    | AN7/RPC1/RC1                              |

| 5     | RPC9/CTED7/PMA6/RC9                              | 27    | AN8/RPC2/PMA2/RC2                         |

| 6     | Vss                                              | 28    | VDD                                       |

| 7     | VCAP                                             | 29    | Vss                                       |

| 8     | PGED2/RPB10/D+/CTED11/RB10                       | 30    | OSC1/CLKI/RPA2/RA2                        |

| 9     | PGEC2/RPB11/D-/RB11                              | 31    | OSC2/CLKO/RPA3/RA3                        |

| 10    | VUSB3V3                                          | 32    | TDO/RPA8/PMA8/RA8                         |

| 11    | AN11/RPB13/CTPLS/PMRD/RB13                       | 33    | SOSCI/RPB4/RB4                            |

| 12    | PGED4 <sup>(4)</sup> /TMS/PMA10/RA10             | 34    | SOSCO/RPA4/T1CK/CTED9/RA4                 |

| 13    | PGEC4 <sup>(4)</sup> /TCK/CTED8/PMA7/RA7         | 35    | TDI/RPA9/PMA9/RA9                         |

| 14    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 | 36    | AN12/RPC3/RC3                             |

| 15    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            | 37    | RPC4/PMA4/RC4                             |

| 16    | AVss                                             | 38    | RPC5/PMA3/RC5                             |

| 17    | AVDD                                             | 39    | Vss                                       |

| 18    | MCLR                                             | 40    | Vdd                                       |

| 19    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 | 41    | RPB5/USBID/RB5                            |

| 20    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       | 42    | VBUS                                      |

| 21    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        | 43    | RPB7/CTED3/PMD5/INT0/RB7                  |

| 22    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       | 44    | RPB8/SCL1/CTED10/PMD4/RB8                 |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

4: This pin function is not available on PIC32MX210F016D and PIC32MX220F032D devices.

5: Shaded pins are 5V tolerant.

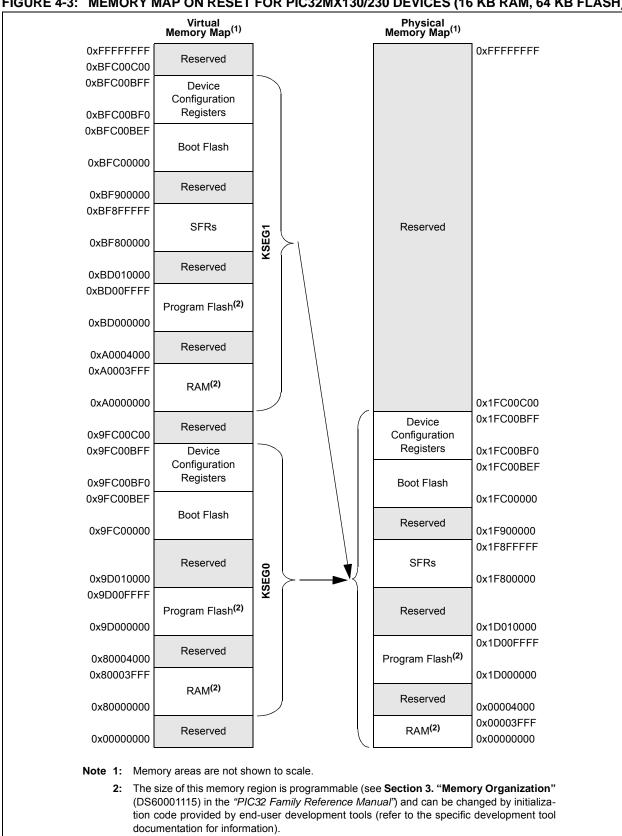

#### FIGURE 4-3: MEMORY MAP ON RESET FOR PIC32MX130/230 DEVICES (16 KB RAM, 64 KB FLASH)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | _                 | _                 |                   | _                 | _                 | —                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 |                   | _                 | _                 | _                 | —                | —                |  |  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | —                 | _                 | —                 | MVEC              | _                 |                   | TPC<2:0>         |                  |  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | _                 | _                 | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |  |  |

#### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

#### Legend:

| Logona.           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-13 Unimplemented: Read as '0'

- bit 12 MVEC: Multi Vector Configuration bit

- 1 = Interrupt controller configured for Multi-vectored mode

- 0 = Interrupt controller configured for Single-vectored mode

- bit 11 Unimplemented: Read as '0'

- bit 10-8 **TPC<2:0>:** Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer

- 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

- 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

- 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

- 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

#### bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

#### TABLE 10-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       | - /   |       |      |      | Bit  | s    |      |          |        |        |         |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | _     | —     | —     | —     | —     | —     | _    | —    |      | _    | —    | —        | —      | _      | —       | —      | 0000       |

| 5390                        | UIEF9                           | 15:0      |       |       | —     | —     | —     | —     | _    | —    |      |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5240                        | U1EP10                          | 31:16     | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | —        | _      | _      | —       | _      | 0000       |

| 53A0                        | UIEPIU                          | 15:0      |       | _     | _     | -     | _     | _     | _    | -    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 53BU                        | UIEPII                          | 15:0      | _     | —     | _     | _     |       |       | _    | —    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEFIZ                          | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | —        | —      | _      | _       | —      | 0000       |

| 5500                        | UIEF 13                         | 15:0      |       | —     | _     | -     | -     | _     | —    | —    | —    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     |       | _     | _     |       | -     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     | _     | _     |       | _     |       | _    | _    |      | _    | _    | —        | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | —    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8, and 0xC respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

|              |                   | —                 |                   | —                 |                   |                   |                  | —                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        |                   | —                 |                   | —                 | -                 |                   |                  | —                |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15.0         | -                 | —                 | -                 | —                 | _                 | -                 | —                | —                |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7.0          | LSPDEN            | DEVADDR<6:0>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 10-12: U1ADDR: USB ADDRESS REGISTER

#### Legend:

| U                                 |                  |                                    |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-8 Unimplemented: Read as '0'

bit 7 LSPDEN: Low-Speed Enable Indicator bit

1 = Next token command to be executed at Low-Speed

0 = Next token command to be executed at Full-Speed

bit 6-0 **DEVADDR<6:0>:** 7-bit USB Device Address bits

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

|              | —                 | —                 | —                 | _                 | —                 | _                 | —                | -                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | _                 | —                 | _                 | —                | -                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         | —                 | —                 | —                 | -                 | —                 | _                 | —                | -                |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | FRML              | <7:0>             |                   |                  |                  |  |  |

#### REGISTER 10-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FRML<7:0>:** The 11-bit Frame Number Lower bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          | —                 | —                 | _                 | —                 | —                 |                   | FRMH<2:0>        |                  |  |  |

#### REGISTER 10-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

#### Legend:

| 0                 |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** The Upper 3 bits of the Frame Numbers bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### Bit Bit Bit Bit Bit Bit Bit Bit Bit 30/22/14/6 27/19/11/3 26/18/10/2 25/17/9/1 24/16/8/0 Range 31/23/15/7 29/21/13/5 28/20/12/4 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 31:24 \_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 23:16 \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 15:8 \_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 7:0 PID < 3:0 > (1)EP<3:0>

#### **REGISTER 10-15: U1TOK: USB TOKEN REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-4 **PID<3:0>:** Token Type Indicator bits<sup>(1)</sup>

1101 = SETUP (TX) token type transaction

- 1001 = IN (RX) token type transaction

- 0001 = OUT (TX) token type transaction

Note: All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

Note 1: All other values are reserved and must not be used.

#### TABLE 11-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits        | RPnR Value to Peripheral<br>Selection       |  |  |  |

|--------------|----------|------------------|---------------------------------------------|--|--|--|

| RPA0         | RPA0R    | RPA0R<3:0>       | 0000 = No Connect                           |  |  |  |

| RPB3         | RPB3R    | RPB3R<3:0>       | 0001 = <u>U1TX</u><br>0010 = <u>U2RTS</u>   |  |  |  |

| RPB4         | RPB4R    | RPB4R<3:0>       | 0011 = SS1                                  |  |  |  |

| RPB15        | RPB15R   | RPB15R<3:0>      |                                             |  |  |  |

| RPB7         | RPB7R    | RPB7R<3:0>       | 0110 = Reserved<br>0111 = C2OUT             |  |  |  |

| RPC7         | RPC7R    | RPC7R<3:0>       | 1000 = Reserved                             |  |  |  |

| RPC0         | RPC0R    | RPC0R<3:0>       | •                                           |  |  |  |

| RPC5         | RPC5R    | RPC5R<3:0>       | •<br>1111 = Reserved                        |  |  |  |

| RPA1         | RPA1R    | RPA1R<3:0>       | 0000 = No Connect                           |  |  |  |

| RPB5         | RPB5R    | RPB5R<3:0>       | 0001 = Reserved<br>0010 = Reserved          |  |  |  |

| RPB1         | RPB1R    | RPB1R<3:0>       | 0011 = SDO1                                 |  |  |  |

| RPB11        | RPB11R   | RPB11R<3:0>      | 0100 = SDO2<br>0101 = OC2                   |  |  |  |

| RPB8         | RPB8R    | RPB8R<3:0>       | 0110 = Reserved                             |  |  |  |

| RPA8         | RPA8R    | RPA8R<3:0>       |                                             |  |  |  |

| RPC8         | RPC8R    | RPC8R<3:0>       | •                                           |  |  |  |

| RPA9         | RPA9R    | R RPA9R<3:0> 111 | 1111 = Reserved                             |  |  |  |

| RPA2         | RPA2R    | RPA2R<3:0>       | 0000 = No Connect                           |  |  |  |

| RPB6         | RPB6R    | RPB6R<3:0>       | 0001 = Reserved<br>0010 = Reserved          |  |  |  |

| RPA4         | RPA4R    | RPA4R<3:0>       | 0011 = SDO1<br>0100 = SDO2                  |  |  |  |

| RPB13        | RPB13R   | RPB13R<3:0>      | 0101 <b>= OC4</b>                           |  |  |  |

| RPB2         | RPB2R    | RPB2R<3:0>       | 0110 = OC5<br>0111 = REFCLKO                |  |  |  |

| RPC6         | RPC6R    | RPC6R<3:0>       | 1000 = Reserved                             |  |  |  |

| RPC1         | RPC1R    | RPC1R<3:0>       |                                             |  |  |  |

| RPC3         | RPC3R    | RPC3R<3:0>       | 1111 = Reserved                             |  |  |  |

| RPA3         | RPA3R    | RPA3R<3:0>       | 0000 = No Connect                           |  |  |  |

| RPB14        | RPB14R   | RPB14R<3:0>      |                                             |  |  |  |

| RPB0         | RPB0R    | RPB0R<3:0>       | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |  |  |  |

| RPB10        | RPB10R   | RPB10R<3:0>      | 0101 <b>= OC3</b>                           |  |  |  |

| RPB9         | RPB9R    | RPB9R<3:0>       |                                             |  |  |  |

| RPC9         | RPC9R    | RPC9R<3:0>       | 1000 = Reserved                             |  |  |  |

| RPC2         | RPC2R    | RPC2R<3:0>       |                                             |  |  |  |

| RPC4         | RPC4R    | RPC4R<3:0>       | 1111 = Reserved                             |  |  |  |

### 12.2 Timer1 Control Registers

#### TABLE 12-1: TIMER1 REGISTER MAP

| ess                       |                                 | 0         |                   |       |       |       |       |       |      | В    | its    |      |       |        |      |       |      |      | s          |

|---------------------------|---------------------------------|-----------|-------------------|-------|-------|-------|-------|-------|------|------|--------|------|-------|--------|------|-------|------|------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15             | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5  | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Resets |

| 0600                      | T1CON                           | 31:16     | —                 | _     | _     | _     | _     | —     | _    | —    | _      | —    | —     | —      | _    | —     | _    | _    | 0000       |

| 0600                      | TICON                           | 15:0      | ON                | —     | SIDL  | TWDIS | TWIP  | —     | _    | —    | TGATE  | _    | TCKPS | S<1:0> | —    | TSYNC | TCS  | _    | 0000       |

| 0610                      | TMR1                            | 31:16     | —                 | -     | —     | —     | —     | —     | —    | —    | —      | —    | _     | _      | —    | —     | —    | —    | 0000       |

| 0010                      |                                 | 15:0      | 10 TMR1<15:0> 000 |       |       |       |       |       |      |      |        | 0000 |       |        |      |       |      |      |            |

| 0620                      | PR1                             | 31:16     | —                 | _     | _     | _     | _     | —     | -    | —    | —      | _    | —     | _      | _    | _     | _    |      | 0000       |

| 0020                      | FRI                             | 15:0      |                   |       |       |       |       |       |      | PR1< | :15:0> |      |       |        |      |       |      |      | FFFF       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

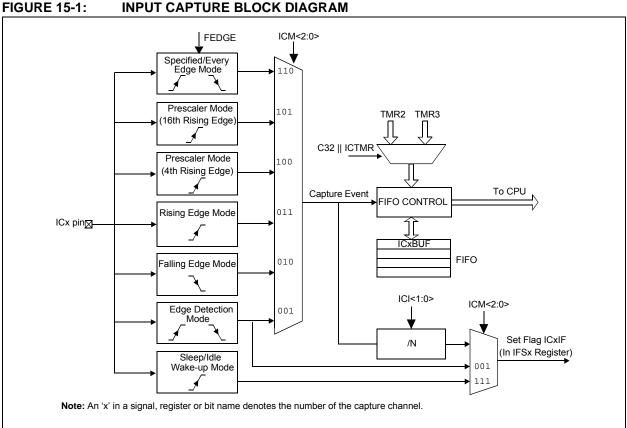

#### **INPUT CAPTURE** 15.0

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- · Simple capture event modes:

- Capture timer value on every rising and falling edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- · Device wake-up from capture pin during Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values (interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled)

- · Input capture can also be used to provide additional sources of external interrupts

Figure 15-1 illustrates a general block diagram of the Input Capture module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | —                 | _                    | _                 | -                 | —                | —                |

| 00.10        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 | _                    | _                 |                   | —                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | _                    | _                 | _                 | —                | _                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | —                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

#### REGISTER 16-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when the device enters Idle mode

- 0 = Continue module operation when the device enters Idle mode

#### bit 12-6 Unimplemented: Read as '0'

- bit 5 OC32: 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (cleared in hardware only)

- 0 = No PWM Fault condition has occurred

- bit 3 **OCTSEL:** Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

### **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

**2:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

### REGISTER 18-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        |                   | -                 | _                 | -                 | —                 | _                 | _                | _                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                 | _                 | _                 | _                 | _                 | —                 | _                | -                |  |  |  |  |

| 15.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |  |  |  |  |

| 15:8         | ACKSTAT           | TRSTAT            | -                 | -                 | _                 | BCL               | GCSTAT           | ADD10            |  |  |  |  |

| 7:0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |  |  |  |  |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |  |  |  |  |

| Legend:           | HS = Set in hardware | HSC = Hardware set/cleared |                   |  |  |  |

|-------------------|----------------------|----------------------------|-------------------|--|--|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, r   | ead as '0'        |  |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared       | C = Clearable bit |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) 1 = Acknowledge was not received from slave 0 = Acknowledge was received from slave Hardware set or clear at end of slave Acknowledge. bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) 1 = Master transmit is in progress (8 bits + ACK) 0 = Master transmit is not in progress Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge. bit 13-11 Unimplemented: Read as '0' bit 10 BCL: Master Bus Collision Detect bit 1 = A bus collision has been detected during a master operation 0 = No collisionHardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module. bit 9 GCSTAT: General Call Status bit 1 = General call address was received 0 = General call address was not received Hardware set when address matches general call address. Hardware clear at Stop detection. bit 8 ADD10: 10-bit Address Status bit 1 = 10-bit address was matched 0 = 10-bit address was not matched Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

#### bit 7 IWCOL: Write Collision Detect bit

| 1 = An attempt to write the I2CxTRN register failed because the I <sup>2</sup> C module is busy |  |

|-------------------------------------------------------------------------------------------------|--|

| 0 = No collision                                                                                |  |

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

#### bit 6 I2COV: Receive Overflow Flag bit

1 = A byte was received while the I2CxRCV register is still holding the previous byte 0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

#### bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

#### 19.1 UART Control Registers

#### TABLE 19-1: UART1 AND UART2 REGISTER MAP

| np for point | ess                         |                  | 6         |        |        |        |       |        |       |                     | Bi          | ts          |         |       |             |        |       |        |       | 6          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|-----------|--------|--------|--------|-------|--------|-------|---------------------|-------------|-------------|---------|-------|-------------|--------|-------|--------|-------|------------|

| 6000         0 MODE         15.0         ON         -         SIDL         IREN         RTSMD         -         UEN<1:0>         WAKE         LPBACK         ABAUD         RXINV         BRGH         PDEL<1:0>         STSL         0.00           610         U1STA(1)         31:16         -         -         -         -         ADM_EN         VERSE         LPBACK         ABAUD         RXINV         BRGH         PDEL<1:0>         STSL         0.00           600         U1STA(1)         15.0         UTXINV         URXEN         UTXENK         UTXEN         TRM         URXEN         TRMT         URXEN         ADDEN         RIDE         PERR         PERR         OER         URXDA         0100           600         U1TXREG         31:16         -         -         -         -         -         -         -         -         0000           6100         U1RXREG         31:16         -         -         -         -         -         -         -         -         -         0000           6100         U1RXREG         31:16         -         -         -         -         -         -         -         -         0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15  | 30/14  | 29/13  | 28/12 | 27/11  | 26/10 | 25/9                | 24/8        | 23/7        | 22/6    | 21/5  | 20/4        | 19/3   | 18/2  | 17/1   | 16/0  | All Resets |

| 610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610         610 <td>6000</td> <td></td> <td>31:16</td> <td></td> <td></td> <td>_</td> <td>_</td> <td>—</td> <td>_</td> <td></td> <td>_</td> <td>_</td> <td>—</td> <td></td> <td></td> <td>—</td> <td>_</td> <td>_</td> <td>_</td> <td>0000</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6000                        |                  | 31:16     |        |        | _      | _     | —      | _     |                     | _           | _           | —       |       |             | —      | _     | _      | _     | 0000       |

| 600         UTXIST         15.0         UTXIST         UTXINV         UTXRNV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0000                        | OTWODE           | 15:0      | ON     |        | SIDL   | IREN  | RTSMD  | —     | UEN                 | -           | WAKE        | LPBACK  | ABAUD | RXINV       | BRGH   | PDSEI | L<1:0> | STSEL | 0000       |

| 15:0         15:0         01XBE         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6010                        | 111STA(1)        | 31:16     | _      | _      | _      | —     | —      | _     | _                   | ADM_EN      |             |         |       | ADDR        | 2<7:0> |       |        |       | 0000       |

| 600         UTXRE         1         -         -         -         -         -         -         -         -         -         -         000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0010                        | UIUIA            | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF               | TRMT        | URXIS       | EL<1:0> | ADDEN | RIDLE       | PERR   | FERR  | OERR   | URXDA | 0110       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6020                        |                  | 31:16     | —      | -      | —      | _     | —      | —     | -                   | —           | _           | —       | —     | _           | _      | _     | —      | _     | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0020                        | UTTAKLG          | 15:0      | _      |        | _      |       | _      | -     |                     |             |             |         | Tra   | nsmit Regis | ster   |       |        |       | 0000       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6030                        |                  | 31:16     | _      |        | _      |       | _      | -     |                     | _           |             | _       | _     |             | -      |       | _      |       | 0000       |

| 600       11       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       1.50       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0030                        | UINAREG          | 15:0      | _      |        | _      |       | _      | -     |                     |             |             |         | Re    | ceive Regis | ster   |       |        |       | 0000       |

| 15:0         Bale Rate Generator Present         1000           6200         16:0 $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6040                        |                  | 31:16     | -      |        | -      |       | _      | -     |                     | —           |             | _       | -     |             | -      |       | -      |       | 0000       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00+0                        | 0 IDIXO          | 15:0      |        |        |        |       |        |       | Bau                 | d Rate Gene | erator Pres | caler   |       |             |        |       |        |       | 0000       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6200                        | 112MODE(1)       | 31:16     | _      | _      | _      | —     | —      | _     | _                   | —           | -           | —       | _     | -           | —      | _     | —      | _     | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0200                        | OZINODL          | 15:0      | ON     |        | SIDL   | IREN  | RTSMD  | —     | UEN                 | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV       | BRGH   | PDSE  | L<1:0> | STSEL | 0000       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6210                        | 112974(1)        | 31:16     | _      |        | _      |       | _      | -     |                     | ADM_EN      |             |         |       | ADDR        | <7:0>  |       |        |       | 0000       |

| 6220     U2TXREG     15:0     -     -     -     -     -     -     -     -     000       6230     U2RXREG     31:16     -     -     -     -     -     -     -     -     0000       6230     U2RXREG     31:16     -     -     -     -     -     -     -     -     0000       6240     U2BRG(1)     31:16     -     -     -     -     -     -     -     0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0210                        | 0231A. /         | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF               | TRMT        | URXISE      | EL<1:0> | ADDEN | RIDLE       | PERR   | FERR  | OERR   | URXDA | 0110       |

| 150     -     -     -     -     -     -     -     -     000       620     U2RXEG     31:16     -     -     -     -     -     -     -     -     000       620     U2BRG(1)     31:16     -     -     -     -     -     -     -     -     -     000       6240     U2BRG(1)     31:16     -     -     -     -     -     -     -     -     000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6220                        |                  | 31:16     | _      |        | _      |       | _      | -     |                     | _           |             | _       | _     |             | -      |       | _      |       | 0000       |