#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f064b-i-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

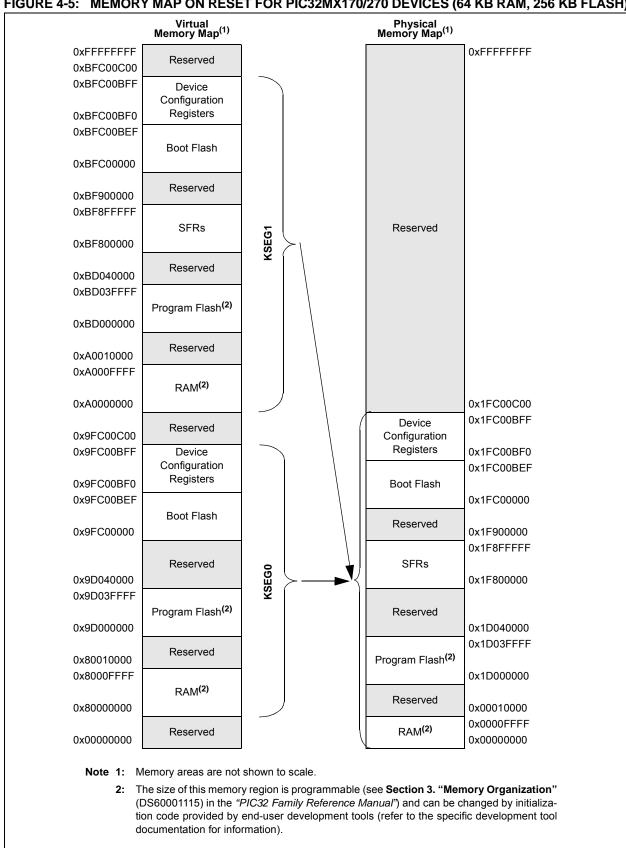

#### FIGURE 4-5: MEMORY MAP ON RESET FOR PIC32MX170/270 DEVICES (64 KB RAM, 256 KB FLASH)

#### TABLE 9-3: DMA CHANNELS 0-3 REGISTER MAP

| ess                            |                                 |                                                             |                   |            |            |             |             |            |            | Bi          | its      |        |        |        |         |        |        |        |            |

|--------------------------------|---------------------------------|-------------------------------------------------------------|-------------------|------------|------------|-------------|-------------|------------|------------|-------------|----------|--------|--------|--------|---------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#)    | Register<br>Name <sup>(1)</sup> | Bit Range                                                   | 31/15             | 30/14      | 29/13      | 28/12       | 27/11       | 26/10      | 25/9       | 24/8        | 23/7     | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

| 3060                           | DCH0CON                         | 31:16                                                       | _                 | _          | _          | —           | _           |            | _          | —           | _        | _      | _      | —      | _       | _      |        | -      | 0000       |

| 3000                           | DCHUCON                         | 15:0 CHBUSY CHCHNS CHEN CHAED CHCHN CHAEN CHEDET CHPRI<1:0> |                   |            |            |             |             |            | l<1:0>     | 0000        |          |        |        |        |         |        |        |        |            |

| 3070                           |                                 | 31:16                                                       | _                 | _          | —          |             |             | _          | —          | —           |          | •      |        | CHAIR  | Q<7:0>  |        |        |        | 00FF       |

| 3070 DCH0ECON 15:0 CHSIRQ<7:0> |                                 |                                                             |                   |            | Q<7:0>     |             |             |            | CFORCE     | CABORT      | PATEN    | SIRQEN | AIRQEN | —      | _       |        | FF00   |        |            |

| 3080                           | DCH0INT                         | 31:16                                                       | —                 | _          | —          | —           | —           | _          | —          | —           | CHSDIE   | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 5000                           | DCHOINT                         | 15:0                                                        | _                 | _          | —          | —           | —           | _          | —          | —           | CHSDIF   | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3090                           | DCH0SSA                         | 31:16                                                       |                   |            |            |             |             |            |            | СНАЗА       | <31:0>   |        |        |        |         |        |        |        | 0000       |

| 0000                           | Donooon                         | 15:0                                                        |                   |            |            |             |             |            |            | 01100/      | ( 101.04 |        |        |        |         |        |        |        | 0000       |

| 3040                           | DCH0DSA                         | 31:16                                                       | CHDSA<31:0>       |            |            |             |             |            |            |             |          |        |        |        |         |        |        |        |            |

| 3070                           | DOI 10DOA                       | 15:0                                                        |                   |            |            |             |             |            |            | 01100/      | 1.02     |        |        |        |         |        |        |        | 0000       |

| 30B0                           | DCH0SSIZ                        | 31:16                                                       | —                 | —          | —          | —           |             | _          | —          | —           | —        | —      | —      |        | —       | —      | —      | —      | 0000       |

| 0000                           | DOI100012                       | 15:0 CHSSIZ<15:0>                                           |                   |            |            |             |             |            | 0000       |             |          |        |        |        |         |        |        |        |            |

| 3000                           |                                 |                                                             |                   |            |            |             | —           | 0000       |            |             |          |        |        |        |         |        |        |        |            |

| 0000                           | DOMODOL                         | 15:0         CHDSIZ<15:0>         0000                      |                   |            |            |             |             |            |            | 0000        |          |        |        |        |         |        |        |        |            |

| 3000                           | DCH0SPTR                        | 31:16                                                       | —                 | —          | —          | —           |             | _          | —          | —           | —        | —      | —      |        | —       | —      | —      | —      | 0000       |

| 0000                           | Donioor IIX                     | 15:0                                                        | CHSPTR<15:0> 0000 |            |            |             |             |            |            |             |          |        |        |        |         |        |        |        |            |

| 30E0                           | DCH0DPTR                        | 31:16                                                       | _                 | _          | —          | —           |             |            | —          | —           | —        | —      | —      | —      | —       | —      | _      | —      | 0000       |

| OOLO                           |                                 | 15:0                                                        |                   |            |            |             |             |            |            | CHDPT       | R<15:0>  |        |        |        |         |        |        |        | 0000       |

| 30E0                           | DCH0CSIZ                        | 31:16                                                       | _                 | _          | —          | —           |             |            | —          | —           | —        | —      | —      | —      | —       | —      | _      | —      | 0000       |

| 001 0                          | DOI100012                       | 15:0                                                        |                   |            |            |             |             |            |            | CHCSIZ      | Z<15:0>  |        |        |        |         |        |        |        | 0000       |

| 3100                           | DCH0CPTR                        | 31:16                                                       | _                 | _          | —          | —           |             |            | —          | —           | —        | —      | —      | —      | —       | —      | _      | —      | 0000       |

| 0100                           | Donioor IIX                     | 15:0                                                        |                   |            |            |             |             |            |            | CHCPT       | R<15:0>  |        |        |        |         |        |        |        | 0000       |

| 3110                           | DCH0DAT                         | 31:16                                                       |                   | _          | —          |             |             |            | —          | —           | —        | —      | —      | —      | —       | —      | _      | —      | 0000       |

| 0110                           | DOITODAT                        | 15:0                                                        | —                 | —          | —          |             |             |            | —          | —           |          |        |        | CHPDA  | \T<7:0> |        |        |        | 0000       |

| 3120                           | DCH1CON                         | 31:16                                                       |                   | _          | —          |             |             |            | —          | —           | —        | —      | —      |        | —       | —      |        | —      | 0000       |

| 0120                           | Donnoon                         | 15:0                                                        | CHBUSY            | —          | —          |             |             |            | —          | CHCHNS      | CHEN     | CHAED  | CHCHN  | CHAEN  | —       | CHEDET | CHPR   | l<1:0> | 0000       |

| 3130                           | DCH1ECON                        | 31:16                                                       | —                 | _          | —          | —           | —           | -          | —          | —           |          |        |        | CHAIR  | Q<7:0>  |        |        |        | OOFF       |

| 5150                           | DOITILOON                       | 15:0                                                        |                   |            |            | CHSIR       | Q<7:0>      |            |            |             | CFORCE   | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | —      | _      | FF00       |

| 3140                           | DCH1INT                         | 31:16                                                       | _                 | _          | —          |             |             | _          | —          | —           | CHSDIE   | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 5140                           | DOLLING                         | 15:0                                                        | _                 | _          | _          | _           | —           | _          | _          | —           | CHSDIF   | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3150                           | DCH1SSA                         | 31:16                                                       |                   |            |            |             |             |            |            | CHSSA       | <31.0>   |        |        |        |         |        |        |        | 0000       |

| 5150                           | DOITIOGA                        | 15:0                                                        |                   |            |            |             |             |            |            | 0100        |          |        |        |        |         |        |        |        | 0000       |

| 3160                           | DCH1DSA                         | 31:16                                                       |                   |            |            |             |             |            |            | CHDSA       | 1<31.0>  |        |        |        |         |        |        |        | 0000       |

| 3100                           | DONIDSA                         | 15:0                                                        |                   |            |            |             |             |            |            |             | ~~~~     |        |        |        |         |        |        |        | 0000       |

| Leger                          | od∙ v=u                         | nknown                                                      | value on R        | leset: — = | unimplemer | nted read a | s '0' Reset | values are | shown in h | nexadecimal |          |        |        |        |         |        |        |        |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| REGISTE | R 9-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | CHDHIF: Channel Destination Half Full Interrupt Flag bit                                                                                                                                   |

|         | <ul> <li>1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)</li> <li>0 = No interrupt is pending</li> </ul>                                           |

| bit 3   | CHBCIF: Channel Block Transfer Complete Interrupt Flag bit                                                                                                                                 |

|         | <ul> <li>1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs</li> <li>0 = No interrupt is pending</li> </ul> |

| bit 2   | CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit                                                                                                                                  |

|         | <ul><li>1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)</li><li>0 = No interrupt is pending</li></ul>                                                          |

| bit 1   | CHTAIF: Channel Transfer Abort Interrupt Flag bit                                                                                                                                          |

|         | <ul> <li>1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted</li> <li>0 = No interrupt is pending</li> </ul>                                          |

| bit 0   | CHERIF: Channel Address Error Interrupt Flag bit                                                                                                                                           |

|         | <ul> <li>1 = A channel address error has been detected (either the source or the destination address is invalid)</li> <li>0 = No interrupt is pending</li> </ul>                           |

DS60001168J-page 96

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| INE OIOT     |                   |                   |                   |                   |                        |                   |                  |                  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | -                 | —                 | _                      | _                 | —                | _                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | —                 | —                 | -                 | —                 | _                      | _                 | —                | _                |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |  |  |

| 15.0         | —                 | —                 |                   | —                 | _                      | —                 | —                | —                |  |  |  |  |

| 7.0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | UACTPND           |                   |                   | USLPGRD           | USBBUSY <sup>(1)</sup> | _                 | USUSPEND         | USBPWR           |  |  |  |  |

#### REGISTER 10-5: U1PWRC: USB POWER CONTROL REGISTER

## Legend:

| zogonai           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; however, an interrupt is pending, which has yet to be generated

0 = An interrupt is not pending

- bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

- bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

# **Note 1:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

## TABLE 11-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection       |

|--------------|----------|-------------|---------------------------------------------|

| RPA0         | RPA0R    | RPA0R<3:0>  | 0000 = No Connect                           |

| RPB3         | RPB3R    | RPB3R<3:0>  | 0001 = <u>U1TX</u><br>0010 = <u>U2RTS</u>   |

| RPB4         | RPB4R    | RPB4R<3:0>  | 0011 = SS1                                  |

| RPB15        | RPB15R   | RPB15R<3:0> |                                             |

| RPB7         | RPB7R    | RPB7R<3:0>  | 0110 = Reserved<br>0111 = C2OUT             |

| RPC7         | RPC7R    | RPC7R<3:0>  | 1000 = Reserved                             |

| RPC0         | RPC0R    | RPC0R<3:0>  | •                                           |

| RPC5         | RPC5R    | RPC5R<3:0>  | •<br>1111 = Reserved                        |

| RPA1         | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                           |

| RPB5         | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPB1         | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                 |

| RPB11        | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                   |

| RPB8         | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                             |

| RPA8         | RPA8R    | RPA8R<3:0>  |                                             |

| RPC8         | RPC8R    | RPC8R<3:0>  | •                                           |

| RPA9         | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                             |

| RPA2         | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                           |

| RPB6         | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPA4         | RPA4R    | RPA4R<3:0>  | 0011 = SDO1<br>0100 = SDO2                  |

| RPB13        | RPB13R   | RPB13R<3:0> | 0101 <b>= OC4</b>                           |

| RPB2         | RPB2R    | RPB2R<3:0>  |                                             |

| RPC6         | RPC6R    | RPC6R<3:0>  | 1000 = Reserved                             |

| RPC1         | RPC1R    | RPC1R<3:0>  |                                             |

| RPC3         | RPC3R    | RPC3R<3:0>  | 1111 = Reserved                             |

| RPA3         | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                           |

| RPB14        | RPB14R   | RPB14R<3:0> |                                             |

| RPB0         | RPB0R    | RPB0R<3:0>  | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |

| RPB10        | RPB10R   | RPB10R<3:0> | 0101 <b>= OC3</b>                           |

| RPB9         | RPB9R    | RPB9R<3:0>  |                                             |

| RPC9         | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                             |

| RPC2         | RPC2R    | RPC2R<3:0>  |                                             |

| RPC4         | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                             |

## REGISTER 19-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | <ul> <li>ABAUD: Auto-Baud Enable bit</li> <li>1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55); cleared by hardware upon completion</li> <li>0 = Baud rate measurement disabled or completed</li> </ul> |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | RXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                           |

| bit 3   | BRGH: High Baud Rate Enable bit<br>1 = High-Speed mode – 4x baud clock enabled<br>0 = Standard Speed mode – 16x baud clock enabled                                                                                                                          |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits<br>11 = 9-bit data, no parity<br>10 = 8-bit data, odd parity<br>01 = 8-bit data, even parity<br>00 = 8-bit data, no parity                                                                                       |

| bit 0   | <b>STSEL:</b> Stop Selection bit<br>1 = 2 Stop bits<br>0 = 1 Stop bit                                                                                                                                                                                       |

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# 21.1 RTCC Control Registers

#### TABLE 21-1: RTCC REGISTER MAP

| ess                         |                                                         | ē         |        |       |          |          |            |            |        |      | Bits                  |          |           |         |         |         |            |       | ŝ          |

|-----------------------------|---------------------------------------------------------|-----------|--------|-------|----------|----------|------------|------------|--------|------|-----------------------|----------|-----------|---------|---------|---------|------------|-------|------------|

| Virtual Address<br>(BF80_#) | (BF80_#)<br>(BF80_#)<br>Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13    | 28/12    | 27/11      | 26/10      | 25/9   | 24/8 | 23/7                  | 22/6     | 21/5      | 20/4    | 19/3    | 18/2    | 17/1       | 16/0  | All Resets |

| 0200                        | RTCCON                                                  | 31:16     | _      | _     | —        | —        | —          | —          |        |      |                       |          | CAL<      | <9:0>   |         |         |            |       | 0000       |

| 0200                        | RICCON                                                  | 15:0      | ON     | _     | SIDL     | —        | —          | —          |        | —    | RTSECSEL              | RTCCLKON | —         |         | RTCWREN | RTCSYNC | HALFSEC    | RTCOE | 0000       |

| 0210                        | 210 RTCALRM 3'                                          | 31:16     | —      |       |          | —        | —          | _          |        | —    | —                     | _        | —         |         | —       | —       | _          | —     | 0000       |

| 0210                        | 15:0 ALRI                                               |           | ALRMEN | CHIME | PIV      | ALRMSYNC | AMASK<3:0> |            |        |      | ARPT<7:0>             |          |           |         |         |         | 0000       |       |            |

| 0220                        | RTCTIME                                                 | 31:16     | —      | _     | HR1      | 0<1:0>   |            | HR01       | <3:0>  |      | MIN10<2:0> MIN01<3:0> |          |           |         | xxxx    |         |            |       |            |

| 0220                        |                                                         | 15:0      | —      |       | SEC10<2: | 0>       |            | SEC01<3:0> |        | —    | —                     | —        | _         | _       | _       | —       | —          | xx00  |            |

| 0230                        | RTCDATE                                                 | 31:16     |        | YEAR  | 10<3:0>  |          |            | YEAR0      | 1<3:0> |      | —                     | —        | —         | MONTH10 |         | MONTH   | 01<3:0>    |       | xxxx       |

| 0230                        | RICDAIL                                                 | 15:0      | _      | _     | DAY      | 10<1:0>  |            | DAY01      | 1<3:0> |      | —                     | —        | —         |         | _       | W       | /DAY01<2:0 | >     | xx00       |

| 0240                        | ALRMTIME                                                | 31:16     | _      |       | HR1      | 0<1:0>   |            | HR01       | <3:0>  |      | _                     | М        | IN10<2:0> |         |         | MIN01   | <3:0>      |       | xxxx       |

| 0240                        |                                                         | 15:0      | —      |       | SEC10<2: | 0>       |            | SEC02      | 1<3:0> |      | —                     | _        | —         |         | —       | —       | _          | —     | xx00       |

| 0250                        |                                                         | 31:16     | _      | _     | _        | _        | _          | _          |        | _    | —                     | _        | —         | MONTH10 |         | MONTH   | 01<3:0>    |       | 00xx       |

| 0250                        | 250 ALRMDATE                                            |           |        | DAY1  | 0<3:0>   |          |            | DAY01      | <3:0>  |      | _                     | _        | _         | -       | _       | W       | /DAY01<2:0 | >     | xx0x       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 22-3: AD1CON3: ADC CONTROL REGISTER 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4        | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|--------------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |  |  |  |

|              | —                 | —                 | —                 | _                        | —                 | —                 | —                | -                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | _                        | —                 | —                 | _                | -                |  |  |  |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0                    | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | ADRC              | _                 | —                 | SAMC<4:0> <sup>(1)</sup> |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0                    | R/W-0             | R/W-0             | R/W              | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | ADCS<                    | 7:0> <b>(2)</b>   |                   |                  |                  |  |  |  |

## Legend:

| =ogona.           |                  |                                                 |                    |  |  |

|-------------------|------------------|-------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                            | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ADRC: ADC Conversion Clock Source bit

- 1 = Clock derived from FRC

- 0 = Clock derived from Peripheral Bus Clock (PBCLK)

- bit 14-13 Unimplemented: Read as '0'

- - 00000001 =TPB • 2 • (ADCS<7:0> + 1) = 4 • TPB = TAD 00000000 =TPB • 2 • (ADCS<7:0> + 1) = 2 • TPB = TAD

- **Note 1:** This bit is only used if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

- 2: This bit is not used if the ADRC (AD1CON3<15>) bit = 1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 51.24        | _                 | —                 |                   | —                 | _                 |                   | -                | —                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | _                 | —                 |                   | —                 | _                 | _                 | _                | —                |  |  |  |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.6         | -                 | —                 | SIDL              | —                 | _                 | _                 |                  | —                |  |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   |                   | _                 | C3OUT             | C2OUT            | C10UT            |  |  |  |

#### REGISTER 23-2: CMSTAT: COMPARATOR STATUS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | table bit U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|----------------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                         | x = Bit is unknown |  |  |  |

#### bit 31-14 Unimplemented: Read as '0'

#### bit 13 SIDL: Stop in Idle Control bit

1 = All Comparator modules are disabled when the device enters Idle mode

0 = All Comparator modules continue to operate when the device enters Idle mode

#### bit 12-3 Unimplemented: Read as '0'

#### bit 2 C3OUT: Comparator Output bit

- 1 = Output of Comparator 3 is a '1'

- 0 = Output of Comparator 3 is a '0'

#### bit 1 C2OUT: Comparator Output bit

- 1 = Output of Comparator 2 is a '1'

- 0 = Output of Comparator 2 is a '0'

#### bit 0 **C1OUT:** Comparator Output bit

- 1 = Output of Comparator 1 is a '1'

- 0 = Output of Comparator 1 is a '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 51.24        | EDG1MOD           | EDG1POL           |                   | EDG1S               | EDG2STAT          | EDG1STAT          |                        |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | U-0                    | U-0              |

| 23.10        | EDG2MOD           | EDG2POL           |                   | EDG2S               | —                 | —                 |                        |                  |

| 15:8         | R/W-0             | U-0               | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 15.0         | ON                | —                 | CTMUSIDL          | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN          | IDISSEN <sup>(2)</sup> | CTTRIG           |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 7.0          | ITRIM<5:0>        |                   |                   |                     |                   |                   | IRNG                   | <1:0>            |

#### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER

### Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

- bit 31 EDG1MOD: Edge1 Edge Sampling Select bit

- 1 = Input is edge-sensitive

- 0 = Input is level-sensitive

- bit 30 EDG1POL: Edge 1 Polarity Select bit

- 1 = Edge1 programmed for a positive edge response

- 0 = Edge1 programmed for a negative edge response

- bit 29-26 EDG1SEL<3:0>: Edge 1 Source Select bits

- 1111 = C3OUT pin is selected

- 1110 = C2OUT pin is selected

- 1101 = C1OUT pin is selected

- 1100 = IC3 Capture Event is selected

- 1011 = IC2 Capture Event is selected

- 1010 = IC1 Capture Event is selected

- 1001 = CTED8 pin is selected

- 1000 = CTED7 pin is selected

- 0111 = CTED6 pin is selected

- 0110 = CTED5 pin is selected

- 0101 = CTED4 pin is selected

- 0100 = CTED3 pin is selected

- 0011 = CTED1 pin is selected

- 0010 = CTED2 pin is selected

- 0001 = OC1 Compare Event is selected 0000 = Timer1 Event is selected

#### bit 25 EDG2STAT: Edge2 Status bit

Indicates the status of Edge2 and can be written to control edge source

- 1 = Edge2 has occurred

- 0 = Edge2 has not occurred

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

# 26.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- · Configuration bit select lock

#### 26.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, PMDLOCK (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6.** "**Oscillator**" (DS60001112) in the "*PIC32 Family Reference Manual*" for details.

#### 26.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The Configuration bit, PMDL1WAY (DEVCFG3<28>), blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

## REGISTER 27-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 18-10 **PWP<8:0>:** Program Flash Write-Protect bits<sup>(3)</sup>

| DIT 18-10 | PWP<8:0>: Program Flash Write-Protect bits <sup>30</sup>                                                       |

|-----------|----------------------------------------------------------------------------------------------------------------|

|           | Prevents selected program Flash memory pages from being modified during code execution.<br>11111111 = Disabled |

|           | 111111110 = Memory below 0x0400 address is write-protected                                                     |

|           | 111111101 = Memory below 0x0400 address is write-protected                                                     |

|           | 111111100 = Memory below 0x0000 address is write-protected                                                     |

|           | 111111001 = Memory below 0x0000 address is write-protected                                                     |

|           | 111111010 = Memory below 0x1000 (44) address is write-protected                                                |

|           | 111111001 = Memory below 0x1400 address is write-protected                                                     |

|           | 111111000 = Memory below 0x1000 address is write-protected                                                     |

|           | 111110111 = Memory below 0x2000 (8K) address is write-protected                                                |

|           | 111110110 = Memory below 0x2400 address is write-protected                                                     |

|           | 111110101 = Memory below 0x2800 address is write-protected                                                     |

|           | 111110100 = Memory below 0x2C00 address is write-protected                                                     |

|           | 111110011 = Memory below 0x3000 address is write-protected                                                     |

|           | 111110010 = Memory below 0x3400 address is write-protected                                                     |

|           | 111110001 = Memory below 0x3800 address is write-protected                                                     |

|           | 111110000 = Memory below 0x3C00 address is write-protected                                                     |

|           | 111101111 = Memory below 0x4000 (16K) address is write-protected                                               |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | •<br>110111111 = Memory below 0x10000 (64K) address is write-protected                                         |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | 101111111 = Memory below 0x20000 (128K) address is write-protected                                             |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | 011111111 = Memory below 0x40000 (256K) address is write-protected                                             |

|           | •                                                                                                              |

|           | •                                                                                                              |

|           | 00000000 = All possible memory is write-protected                                                              |

|           |                                                                                                                |

| bit 9-5   | Reserved: Write '1'                                                                                            |

| bit 4-3   | ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits <sup>(2)</sup>                     |

|           | 11 = PGEC1/PGED1 pair is used                                                                                  |

|           | 10 = PGEC2/PGED2 pair is used                                                                                  |

|           | 01 = PGEC3/PGED3 pair is used                                                                                  |

|           | 00 = PGEC4/PGED4 pair is used <sup>(2)</sup>                                                                   |

| bit 2     | JTAGEN: JTAG Enable bit <sup>(1)</sup>                                                                         |

| bit 2     | 1 = JTAG is enabled                                                                                            |

|           | 0 = JTAG is disabled                                                                                           |

| bit 1-0   | <b>DEBUG&lt;1:0&gt;:</b> Background Debugger Enable bits (forced to '11' if code-protect is enabled)           |

|           |                                                                                                                |

|           | 1x = Debugger is disabled                                                                                      |

|           | 0x = Debugger is enabled                                                                                       |

| Note 1:   | This bit sets the value for the JTAGEN bit in the CFGCON register.                                             |

|           | -                                                                                                              |

| 2:        | The PGEC4/PGED4 pin pair is not available on all devices. Refer to the " <b>Pin Diagrams</b> " section for     |

|           | availability.                                                                                                  |

| -         |                                                                                                                |

3: The PWP<8:7> bits are only available on devices with 256 KB Flash.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | r-1               | r-1               | r-1               | r-1                 | r-1               | r-1               | R/P              | R/P              |  |

| 31:24        | —                 | _                 | _                 | — — — FWDTWINSZ<1:0 |                   |                   |                  |                  |  |

| 00.40        | R/P               | R/P               | r-1               | R/P                 | R/P               | R/P               | R/P              | R/P              |  |

| 23:16        | FWDTEN            | WINDIS            | _                 | WDTPS<4:0>          |                   |                   |                  |                  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P                 | r-1               | R/P               | R/P              | R/P              |  |

| 15:8         | FCKSM             | 1<1:0>            | FPBDI             | V<1:0>              | —                 | OSCIOFNC          | POSCM            | OD<1:0>          |  |

| 7.0          | R/P               | r-1               | R/P               | r-1                 | r-1               | R/P               | R/P              | R/P              |  |

| 7:0          | IESO              | _                 | FSOSCEN           | _                   | —                 | FNOSC<2:0>        |                  |                  |  |

#### REGISTER 27-2: DEVCFG1: DEVICE CONFIGURATION WORD 1

| Legend:           | r = Reserved bit | P = Programmable bit     |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-26 Reserved: Write '1'

bit 25-24 FWDTWINSZ<1:0>: Watchdog Timer Window Size bits

- 11 = Window size is 25%

- 10 = Window size is 37.5%

- 01 = Window size is 50%

- 00 = Window size is 75%

#### bit 23 FWDTEN: Watchdog Timer Enable bit

- 1 = Watchdog Timer is enabled and cannot be disabled by software

- 0 = Watchdog Timer is not enabled; it can be enabled in software

#### bit 22 WINDIS: Watchdog Timer Window Enable bit

- 1 = Watchdog Timer is in non-Window mode

- 0 = Watchdog Timer is in Window mode

#### bit 21 Reserved: Write '1'

#### bit 20-16 WDTPS<4:0>: Watchdog Timer Postscale Select bits

| 10100 <b>= 1:1048576</b>                                     |

|--------------------------------------------------------------|

| 10011 <b>= 1:524288</b>                                      |

| 10010 <b>= 1:262144</b>                                      |

| 10001 <b>= 1:131072</b>                                      |

| 10000 <b>= 1:65536</b>                                       |

| 01111 <b>= 1:32768</b>                                       |

| 01110 <b>= 1:16384</b>                                       |

| 01101 = 1:8192                                               |

| 01100 = 1:4096                                               |

| 01011 = <b>1:2048</b>                                        |

| 01010 = 1:1024                                               |

| 01001 = 1:512                                                |

| 01000 <b>= 1:256</b>                                         |

| 00111 <b>= 1:128</b>                                         |

| 00110 <b>= 1:64</b>                                          |

| 00101 <b>= 1:32</b>                                          |

| 00100 <b>= 1:16</b>                                          |

| 00011 <b>= 1:8</b>                                           |

| 00010 <b>= 1</b> :4                                          |

| 00001 = 1:2                                                  |

| 00000 = 1:1                                                  |

| All other combinations not shown result in operation = 10100 |

| ······································                       |

**Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

| DC CHARACTERISTICS |        |                                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40 \ ^\circ C \leq TA \leq +85 \ ^\circ C \ for \ Industrial \\ -40 \ ^\circ C \leq TA \leq +105 \ ^\circ C \ for \ V-temp \end{array}$ |                        |      |        |                                               |

|--------------------|--------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|--------|-----------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                      | Min.                                                                                                                                                                                                                                                                                | Typical <sup>(1)</sup> | Max. | Units  | Conditions                                    |

|                    |        | Program Flash Memory <sup>(3)</sup>  |                                                                                                                                                                                                                                                                                     |                        |      |        |                                               |

| D130               | Eр     | Cell Endurance                       | 20,000                                                                                                                                                                                                                                                                              | —                      | _    | E/W    | —                                             |

| D131               | Vpr    | VDD for Read                         | 2.3                                                                                                                                                                                                                                                                                 | —                      | 3.6  | V      | —                                             |

| D132               | VPEW   | VDD for Erase or Write               | 2.3                                                                                                                                                                                                                                                                                 | —                      | 3.6  | V      | —                                             |

| D134               | Tretd  | Characteristic Retention             | 20                                                                                                                                                                                                                                                                                  | —                      | _    | Year   | Provided no other specifications are violated |

| D135               | IDDP   | Supply Current during<br>Programming | _                                                                                                                                                                                                                                                                                   | 10                     | _    | mA     | —                                             |

|                    | Tww    | Word Write Cycle Time                | —                                                                                                                                                                                                                                                                                   | 411                    | _    | es     | See Note 4                                    |

| D136               | Trw    | Row Write Cycle Time                 | —                                                                                                                                                                                                                                                                                   | 6675                   | _    | Cycles | See Note 2,4                                  |

| D137               | TPE    | Page Erase Cycle Time                | —                                                                                                                                                                                                                                                                                   | 20011                  | _    |        | See Note 4                                    |

|                    | TCE    | Chip Erase Cycle Time                | —                                                                                                                                                                                                                                                                                   | 80180                  | _    | FRC    | See Note 4                                    |

#### TABLE 30-12: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: The minimum SYSCLK for row programming is 4 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

**3:** Refer to the *"PIC32 Flash Programming Specification"* (DS60001145) for operating conditions during programming and erase cycles.

4: This parameter depends on FRC accuracy (See Table 30-19) and FRC tuning values (See Register 8-2).

#### TABLE 30-41: CTMU CURRENT SOURCE SPECIFICATIONS

| DC CHARACTERISTICS  |        |                                                    | $\label{eq:standard operating Conditions (see Note 3):2.3V to 3.6V (unless otherwise stated) \\ Operating temperature & -40^{\circ}C \leq TA \leq +85^{\circ}C \text{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \text{ for V-temp} \\ \end{array}$ |       |      |       |                                  |

|---------------------|--------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|----------------------------------|

| Param<br>No.        | Symbol | Characteristic                                     | Min.                                                                                                                                                                                                                                                                | Тур.  | Max. | Units | Conditions                       |

| CTMU CURRENT SOURCE |        |                                                    |                                                                                                                                                                                                                                                                     |       |      |       |                                  |

| CTMUI1              | Ιουτ1  | Base Range <sup>(1)</sup>                          | _                                                                                                                                                                                                                                                                   | 0.55  | _    | μA    | CTMUCON<9:8> = 01                |

| CTMUI2              | Ιουτ2  | 10x Range <sup>(1)</sup>                           | _                                                                                                                                                                                                                                                                   | 5.5   | _    | μA    | CTMUCON<9:8> = 10                |

| CTMUI3              | Ιουτ3  | 100x Range <sup>(1)</sup>                          | _                                                                                                                                                                                                                                                                   | 55    |      | μA    | CTMUCON<9:8> = 11                |

| CTMUI4              | IOUT4  | 1000x Range <sup>(1)</sup>                         | _                                                                                                                                                                                                                                                                   | 550   |      | μA    | CTMUCON<9:8> = 00                |

| CTMUFV1             | VF     | Temperature Diode Forward Voltage <sup>(1,2)</sup> | —                                                                                                                                                                                                                                                                   | 0.598 | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 01 |

|                     |        |                                                    | _                                                                                                                                                                                                                                                                   | 0.658 | _    | V     | TA = +25°C,<br>CTMUCON<9:8> = 10 |

|                     |        |                                                    | —                                                                                                                                                                                                                                                                   | 0.721 |      | V     | TA = +25°C,<br>CTMUCON<9:8> = 11 |

| CTMUFV2             | VFVR   | Temperature Diode Rate of                          | —                                                                                                                                                                                                                                                                   | -1.92 |      | mV/ºC | CTMUCON<9:8> = 01                |

|                     |        | Change <sup>(1,2)</sup>                            | _                                                                                                                                                                                                                                                                   | -1.74 |      | mV/ºC | CTMUCON<9:8> = 10                |

|                     |        |                                                    | _                                                                                                                                                                                                                                                                   | -1.56 |      | mV/ºC | CTMUCON<9:8> = 11                |

**Note 1:** Nominal value at center point of current trim range (CTMUCON<15:10> = 000000).

**2:** Parameters are characterized but not tested in manufacturing. Measurements taken with the following conditions:

- VREF+ = AVDD = 3.3V

- ADC module configured for conversion speed of 500 ksps

- All PMD bits are cleared (PMDx = 0)

- Executing a while(1) statement

- Device operating from the FRC with no PLL

- **3:** The CTMU module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

NOTES:

# 33.0 PACKAGING INFORMATION

# 33.1 Package Marking Information

28-Lead SOIC

#### 28-Lead SPDIP

Example

#### Example

#### 28-Lead SSOP

#### 28-Lead QFN

Example

#### Example

| Legenc | I: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (@3)<br>can be found on the outer packaging for this package. |

|--------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  |                                           | Aicrochip part number cannot be marked on one line, it is carried over to the next limiting the number of available characters for customer-specific information.                                                                                                                                                                                                            |

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

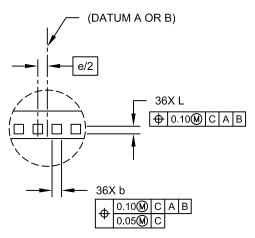

# 36-Terminal Very Thin Thermal Leadless Array Package (TL) – 5x5x0.9 mm Body with Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | N      | <b>IILLIMETER</b> | S        |       |

|-------------------------|--------|-------------------|----------|-------|

| Dimensior               | Limits | MIN               | NOM      | MAX   |

| Number of Pins          | Ν      |                   | 36       |       |

| Number of Pins per Side | ND     |                   | 10       |       |

| Number of Pins per Side | NE     |                   | 8        |       |

| Pitch                   | е      |                   | 0.50 BSC | _     |

| Overall Height          | А      | 0.80              | 0.90     | 1.00  |

| Standoff                | A1     | 0.025             | -        | 0.075 |

| Overall Width           | Е      |                   | 5.00 BSC |       |

| Exposed Pad Width       | E2     | 3.60              | 3.75     | 3.90  |

| Overall Length          | D      |                   | 5.00 BSC |       |

| Exposed Pad Length      | D2     | 3.60              | 3.75     | 3.90  |

| Contact Width           | b      | 0.20              | 0.25     | 0.30  |

| Contact Length          | L      | 0.20              | 0.25     | 0.30  |

| Contact-to-Exposed Pad  | K      | 0.20              | -        | -     |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-187C Sheet 2 of 2

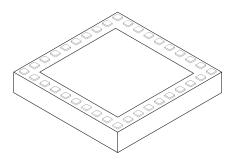

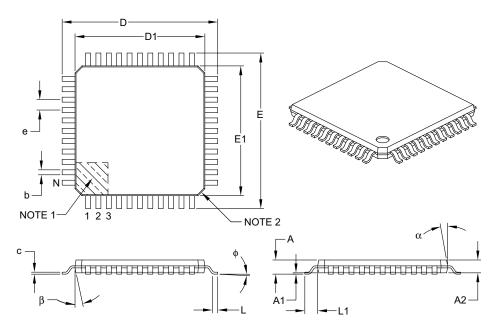

# 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          |              | MILLIMETERS |           |      |

|--------------------------|--------------|-------------|-----------|------|

| Dime                     | nsion Limits | MIN         | NOM       | MAX  |

| Number of Leads          | N            |             | 44        |      |

| Lead Pitch               | е            |             | 0.80 BSC  |      |

| Overall Height           | А            | _           | -         | 1.20 |

| Molded Package Thickness | A2           | 0.95        | 1.00      | 1.05 |

| Standoff                 | A1           | 0.05        | -         | 0.15 |

| Foot Length              | L            | 0.45        | 0.60      | 0.75 |

| Footprint                | L1           |             | 1.00 REF  |      |

| Foot Angle               | φ            | 0°          | 3.5°      | 7°   |

| Overall Width            | E            |             | 12.00 BSC |      |

| Overall Length           | D            |             | 12.00 BSC |      |

| Molded Package Width     | E1           |             | 10.00 BSC |      |

| Molded Package Length    | D1           |             | 10.00 BSC |      |

| Lead Thickness           | С            | 0.09        | -         | 0.20 |

| Lead Width               | b            | 0.30        | 0.37      | 0.45 |

| Mold Draft Angle Top     | α            | 11°         | 12°       | 13°  |

| Mold Draft Angle Bottom  | β            | 11°         | 12°       | 13°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

# APPENDIX A: REVISION HISTORY

# Revision A (May 2011)

This is the initial released version of this document.

# **Revision B (October 2011)**

The following two global changes are included in this revision:

- All packaging references to VLAP have been changed to VTLA throughout the document

- All references to VCORE have been removed

- All occurrences of the ASCL1, ASCL2, ASDA1, and ASDA2 pins have been removed

- V-temp temperature range (-40°C to +105°C) was added to all electrical specification tables

This revision includes the addition of the following devices:

- PIC32MX130F064B

- PIC32MX130F064C

- PIC32MX130F064D

- PIC32MX150F128B

- PIC32MX150F128CPIC32MX150F128D

- PIC32MX250F128C

PIC32MX250F128D

PIC32MX230F064B

PIC32MX230F064C

PIC32MX230F064D

PIC32MX250F128B

Text and formatting changes were incorporated throughout the document.

All other major changes are referenced by their respective section in Table A-1.

| Section                                                                    | Update Description                                                                                                                                                        |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to 128 KB<br>Flash and 32 KB SRAM) with Audio | Split the existing Features table into two: PIC32MX1XX General Purpose Family Features (Table 1) and PIC32MX2XX USB Family Features (Table 2).                            |

| and Graphics Interfaces, USB, and Advanced Analog"                         | Added the SPDIP package reference (see Table 1, Table 2, and " <b>Pin Diagrams</b> ").                                                                                    |

|                                                                            | Added the new devices to the applicable pin diagrams.                                                                                                                     |

|                                                                            | Changed PGED2 to PGED1 on pin 35 of the 36-pin VTLA diagram for PIC32MX220F032C, PIC32MX220F016C, PIC32MX230F064C, and PIC32MX250F128C devices.                           |

| 1.0 "Device Overview"                                                      | Added the SPDIP package reference and updated the pin number for AN12 for 44-pin QFN devices in the Pinout I/O Descriptions (see Table 1-1).                              |

|                                                                            | Added the PGEC4/PGED4 pin pair and updated the C1INA-C1IND and C2INA-C2IND pin numbers for 28-pin SSOP/SPDIP/SOIC devices in the Pinout I/O Descriptions (see Table 1-1). |

| 2.0 "Guidelines for Getting Started with 32-bit Microcontrollers"          | Updated the Recommended Minimum Connection diagram (see Figure 2-1).                                                                                                      |

### TABLE A-1: MAJOR SECTION UPDATES