#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 64KB (64K × 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 28-SPDIP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f064b-v-sp |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

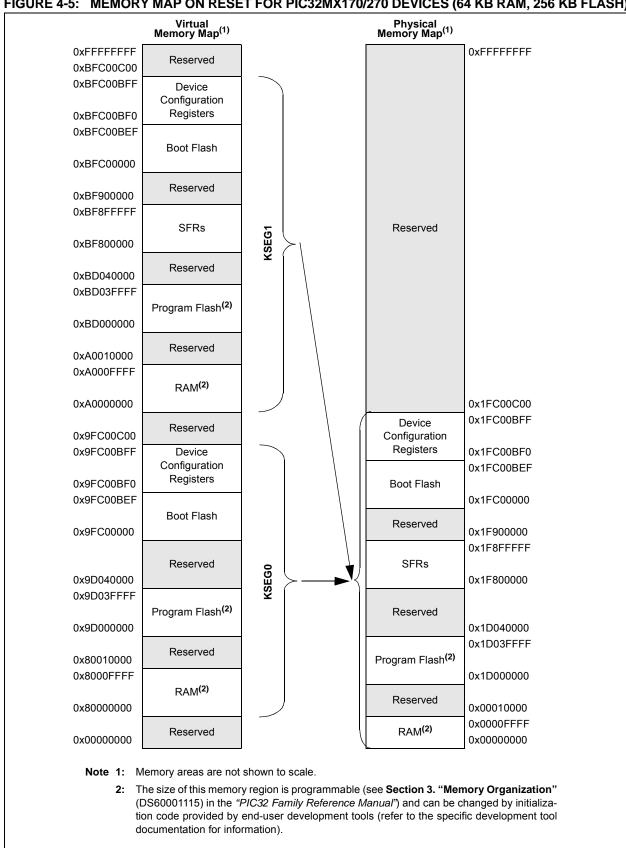

### FIGURE 4-5: MEMORY MAP ON RESET FOR PIC32MX170/270 DEVICES (64 KB RAM, 256 KB FLASH)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | —                 |                  | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 | -                 | _                 | —                 |                  | _                |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |

| 15:8         |                   |                   |                   | BMXDU             | PBA<15:8>         |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | BMXDU             | PBA<7:0>          |                   |                  |                  |

### REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

### Legend:

| Legena.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 **BMXDUPBA<9:0>:** Read-Only bits This value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |

| 31:24        |                   |                   |                   | BMXDRM            | ISZ<31:24>        |                   |                  |                  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |

| 23:16        |                   |                   |                   | BMXDRM            | ISZ<23:16>        |                   |                  |                  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |

| 15:8         |                   |                   |                   | BMXDR             | MSZ<15:8>         |                   |                  |                  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |

| 7:0          |                   |                   |                   | BMXDR             | MSZ<7:0>          |                   |                  |                  |

#### **BMXDRMSZ: DATA RAM SIZE REGISTER REGISTER 4-5:**

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXDRMSZ<31:0>: Data RAM Memory (DRM) Size bits

Static value that indicates the size of the Data RAM in bytes: 0x00001000 = Device has 4 KB RAM 0x00002000 = Device has 8 KB RAM 0x00004000 = Device has 16 KB RAM 0x00008000 = Device has 32 KB RAM 0x00010000 = Device has 64 KB RAM

#### **REGISTER 4-6: BMXPUPBA: PROGRAM FLASH (PFM) USER PROGRAM BASE ADDRESS** REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | _                 | —                 | —                 | _                 | _                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | _                 | _                 | _                 | _                 |                   | BMXPUPE           | 3A<19:16>        |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | BMXPU             | PBA<15:8>         |                   |                  |                  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | BMXPU             | PBA<7:0>          |                   |                  |                  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-20 Unimplemented: Read as '0'

bit 19-11 BMXPUPBA<19:11>: Program Flash (PFM) User Program Base Address bits

### bit 10-0 BMXPUPBA<10:0>: Read-Only bits This value is always '0', which forces 2 KB increments

Note 1: At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXPFMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS09            | IFS08            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IFS07             | IFS06             | IFS05             | IFS04             | IFS03             | IFS02             | IFS01            | IFS00            |

### REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

### Legend:

| <b>L</b> ogonan   |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-0 IFS31-IFS00: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit definitions.

### REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC09            | IEC08            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IEC07             | IEC06             | IEC05             | IEC04             | IEC03             | IEC02             | IEC01            | IEC00            |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### bit 31-0 IEC31-IEC00: Interrupt Enable bits

1 = Interrupt is enabled

0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

| REGIOTE      | CIOTER 3-12. DETASSIZ. DINA CHANNEL X SOURCE SIZE REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |

|--------------|------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 24.24        | U-0                                                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                                                          | —                 | _                 | _                 | —                 | _                 | —                | —                |  |  |

| 22:46        | U-0                                                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                                                            | _                 |                   | _                 | _                 |                   | _                | —                |  |  |

| 45.0         | R/W-0                                                      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CHSSIZ<15:8>                                               |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0                                                      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                                                            |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |  |  |

### REGISTER 9-12: DCHxSSIZ: DMA CHANNEL 'x' SOURCE SIZE REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

### **REGISTER 9-13: DCHxDSIZ: DMA CHANNEL 'x' DESTINATION SIZE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | —                 | _                 | _                 | —                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 15:8 CHDSIZ<15:8> |                   |                   |                   |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

### REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER (CONTINUED)

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup>

- 1 = Token packet rejected due to CRC5 error

- 0 = Token packet accepted

- EOFEF: EOF Error Flag bit<sup>(3,5)</sup>

- 1 = An EOF error condition was detected

- 0 = No EOF error condition was detected

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check failed

- 0 = PID check passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

|              |                   |                   |                          |                   | -                     |                       |                  |                      |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

| 31:24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 31.24        | —                 | —                 | —                        | _                 | —                     | —                     |                  | _                    |

| 22:16        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 23:16        | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 15.0         | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |

| 7:0          | JSTATE            | ATE SE0           | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |

|              | JUNATE            | 320               | TOKBUSY <sup>(1,5)</sup> | USBROI            | TIOSTEIN /            | RESUME                | FFDROI           | SOFEN <sup>(5)</sup> |

### REGISTER 10-11: U1CON: USB CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE was detected on the USB

- 0 = No JSTATE was detected on the

- bit 6 **SE0:** Live Single-Ended Zero flag bit 1 = Single-Ended Zero was detected on the USB

- 0 = No Single-Ended Zero was detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing is disabled (set upon SETUP token received)

- 0 = Token and packet processing is enabled

- TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token is being executed by the USB module

- 0 = No token is being executed

### bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset generated

- 0 = USB reset terminated

- bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

- bit 2 RESUME: RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

### 11.4 Ports Control Registers

### TABLE 11-3: PORTA REGISTER MAP

| ess                         |                                 | 0         |       |       |       |       |       |                          |                       | Bits                    | 6                       |      |      |          |          |          |          |          | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|--------------------------|-----------------------|-------------------------|-------------------------|------|------|----------|----------|----------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10                    | 25/9                  | 24/8                    | 23/7                    | 22/6 | 21/5 | 20/4     | 19/3     | 18/2     | 17/1     | 16/0     | All Resets |

| 6000                        | ANSELA                          | 31:16     | _     | —     | —     | —     | _     | _                        | _                     | _                       | —                       |      | _    | _        | _        | —        | —        | _        | 0000       |

|                             |                                 | 15:0      | _     | —     | —     | —     | —     | -                        |                       |                         | —                       | _    | —    | —        | _        | _        | ANSA1    | ANSA0    | 0003       |

| 6010                        | TRISA                           | 31:16     | _     | —     | —     | —     | —     | —                        |                       |                         | —                       | _    | —    |          | —        | _        | _        | —        | 0000       |

| 0010                        |                                 | 15:0      | —     | —     | —     | —     | _     | TRISA10 <sup>(2)</sup>   | TRISA9 <sup>(2)</sup> | TRISA8 <sup>(2)</sup>   | TRISA7 <sup>(2)</sup>   | _    | —    | TRISA4   | TRISA3   | TRISA2   | TRISA1   | TRISA0   | 079F       |

| 6020                        | PORTA                           | 31:16     | —     | —     | —     | —     | _     | —                        | —                     | _                       | —                       | _    | —    |          |          |          |          |          | 0000       |

| 0020                        |                                 | 15:0      | —     | —     | —     | —     | _     | RA10 <sup>(2)</sup>      | RA9 <sup>(2)</sup>    | RA8 <sup>(2)</sup>      | RA7 <sup>(2)</sup>      | _    | —    | RA4      | RA3      | RA2      | RA1      | RA0      | xxxx       |

| 6030                        | LATA                            | 31:16     | _     | —     | —     | —     | _     |                          | _                     | _                       | —                       | —    | —    | _        | _        | _        |          | _        | 0000       |

| 0000                        |                                 | 15:0      | —     | —     | —     | —     | —     | LATA10 <sup>(2)</sup>    | LATA9 <sup>(2)</sup>  | LATA8 <sup>(2)</sup>    | LATA7 <sup>(2)</sup>    | —    | —    | LATA4    | LATA3    | LATA2    | LATA1    | LATA0    | xxxx       |

| 6040                        | ODCA                            | 31:16     | —     | —     | —     | —     | —     | —                        |                       | _                       | —                       | —    | —    | —        |          | —        |          |          | 0000       |

| 0040                        | ODOA                            | 15:0      | —     | —     | —     | —     | —     | ODCA10 <sup>(2)</sup>    | ODCA9 <sup>(2)</sup>  | ODCA8 <sup>(2)</sup>    | ODCA7 <sup>(2)</sup>    | —    | —    | ODCA4    | ODCA3    | ODCA2    | ODCA1    | ODCA0    | 0000       |

| 6050                        | CNPUA                           | 31:16     | —     | —     | —     | —     | —     | —                        | _                     | _                       | —                       | —    | —    | —        |          | —        |          |          | 0000       |

| 0030                        | CINFUA                          | 15:0      | _     | _     | —     | —     | _     | CNPUA10 <sup>(2)</sup>   | CNPUA9 <sup>(2)</sup> | CNPUA8 <sup>(2)</sup>   | CNPUA7 <sup>(2)</sup>   | _    | —    | CNPUA4   | CNPUA3   | CNPUA2   | CNPUA1   | CNPUA0   | 0000       |

| 6060                        | CNPDA                           | 31:16     | —     | —     | —     | —     |       | _                        |                       |                         |                         | —    | —    |          |          | —        |          |          | 0000       |

| 0000                        | CINFDA                          | 15:0      | _     | _     | —     | —     | _     | CNPDA10 <sup>(2)</sup>   | CNPDA9 <sup>(2)</sup> | CNPDA8 <sup>(2)</sup>   | CNPDA7 <sup>(2)</sup>   | _    | —    | CNPDA4   | CNPDA3   | CNPDA2   | CNPDA1   | CNPDA0   | 0000       |

| 6070                        | CNCONA                          | 31:16     | —     | —     | —     | —     |       | _                        |                       | _                       | _                       | —    | —    |          |          | —        |          |          | 0000       |

| 0070                        | CINCONA                         | 15:0      | ON    | —     | SIDL  | —     | _     | _                        | _                     | _                       | —                       | _    | _    | _        | —        | —        | —        | —        | 0000       |

| 6080                        | CNENA                           | 31:16     | _     | —     | —     | —     | _     | _                        | _                     | _                       | —                       | _    | —    | —        | _        | _        | _        | _        | 0000       |

| 0000                        | CINEINA                         | 15:0      | _     | _     | —     | —     |       | CNIEA10 <sup>(2)</sup>   | CNIEA9 <sup>(2)</sup> | CNIEA8 <sup>(2)</sup>   | CNIEA7 <sup>(2)</sup>   |      |      | CNIEA4   | CNIEA3   | CNIEA2   | CNIEA1   | CNIEA0   | 0000       |

| 6000                        | CNISTATA                        | 31:16     | _     | _     | —     | —     |       |                          |                       |                         | _                       |      | _    |          |          | —        | _        |          | 0000       |

| 0090                        | CNSTATA                         | 15:0      | _     | _     | —     | —     |       | CNSTATA10 <sup>(2)</sup> | CNSTATA9(2)           | CNSTATA8 <sup>(2)</sup> | CNSTATA7 <sup>(2)</sup> |      |      | CNSTATA4 | CNSTATA3 | CNSTATA2 | CNSTATA1 | CNSTATA0 | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This bit is only available on 44-pin devices.

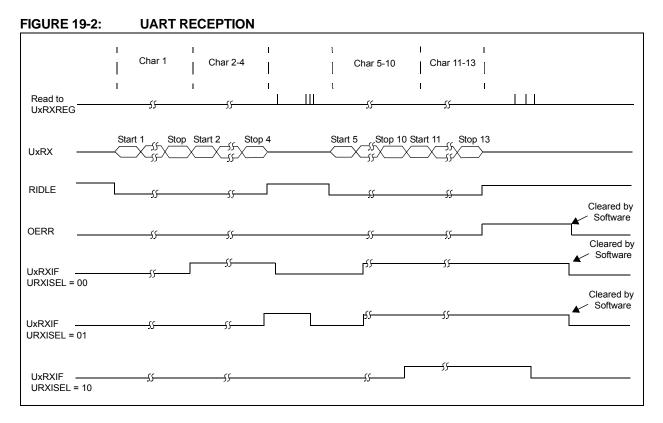

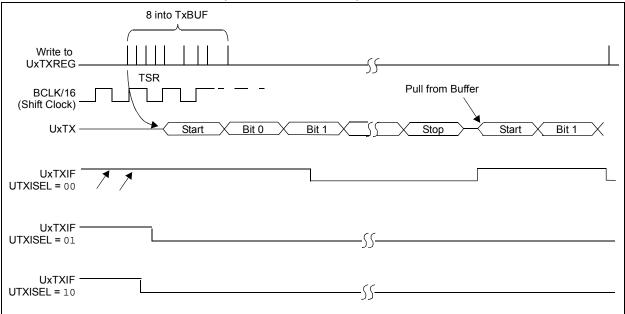

Figure 19-2 and Figure 19-3 illustrate typical receive and transmit timing for the UART module.

NOTES:

### REGISTER 20-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

- bit 4 Unimplemented: Read as '0' CS1P: Chip Select 0 Polarity bit<sup>(2)</sup> bit 3 1 = Active-high (PMCS1)  $0 = \text{Active-low}(\overline{PMCS1})$ bit 2 Unimplemented: Read as '0' bit 1 WRSP: Write Strobe Polarity bit For Slave Modes and Master mode 2 (MODE<1:0> = 00,01,10): 1 = Write strobe active-high (PMWR) 0 = Write strobe active-low (PMWR) For Master mode 1 (MODE<1:0> = 11): 1 = Enable strobe active-high (PMENB) 0 = Enable strobe active-low (PMENB) bit 0 RDSP: Read Strobe Polarity bit For Slave modes and Master mode 2 (MODE<1:0> = 00,01,10): 1 = Read Strobe active-high (PMRD)  $0 = \text{Read Strobe active-low}(\overline{PMRD})$ For Master mode 1 (MODE<1:0> = 11): 1 = Read/write strobe active-high (PMRD/PMWR)

- 0 = Read/write strobe active-low (PMRD/PMWR)

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | —                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |

| 45.0         | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | _                 | PTEN14            | _                 | _                 | —                 |                   | PTEN<10:8>       |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | PTEN<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

### REGISTER 20-4: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-15 Unimplemented: Read as '0'

- bit 15-14 **PTEN14:** PMCS1 Address Port Enable bits

- 1 = PMA14 functions as either PMA14 or PMCS1<sup>(1)</sup>

- 0 = PMA14 functions as port I/O

- bit 13-11 Unimplemented: Read as '0'

- bit 10-2 PTEN<10:2>: PMP Address Port Enable bits

- 1 = PMA<10:2> function as PMP address lines

- 0 = PMA<10:2> function as port I/O

### bit 1-0 PTEN<1:0>: PMALH/PMALL Address Port Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads functions as port I/O

- Note 1: The use of this pin as PMA14 or CS1 is selected by the CSF<1:0> bits in the PMCON register.

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by bits ADRMUX<1:0> in the PMCON register.

### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

- bit 10 EDGSEQEN: Edge Sequence Enable bit 1 = Edge1 must occur before Edge2 can occur 0 = No edge sequence is needed IDISSEN: Analog Current Source Control bit<sup>(2)</sup> bit 9 1 = Analog current source output is grounded 0 = Analog current source output is not grounded bit 8 **CTTRIG:** Trigger Control bit 1 = Trigger output is enabled 0 = Trigger output is disabled bit 7-2 ITRIM<5:0>: Current Source Trim bits 011111 = Maximum positive change from nominal current 011110 000001 = Minimum positive change from nominal current 000000 = Nominal current output specified by IRNG<1:0> 111111 = Minimum negative change from nominal current 100010 100001 = Maximum negative change from nominal current bit 1-0 IRNG<1:0>: Current Range Select bits<sup>(3)</sup> 11 = 100 times base current 10 = 10 times base current

- 01 = Base current level

- 00 = 1000 times base current<sup>(4)</sup>

- Note 1: When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical 3: Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

### 26.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- · Configuration bit select lock

### 26.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, PMDLOCK (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6.** "**Oscillator**" (DS60001112) in the "*PIC32 Family Reference Manual*" for details.

### 26.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The Configuration bit, PMDL1WAY (DEVCFG3<28>), blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | r-1                   | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |

|              | —                     |                   |                   | _                 | _                 |                   | _                | -                |  |

| 00.40        | r-1                   | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |  |

| 23:16        | —                     | _                 | —                 | -                 | —                 | FPLLODIV<2:0>     |                  |                  |  |

| 45.0         | R/P                   | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |  |

| 15:8         | UPLLEN <sup>(1)</sup> |                   | —                 | _                 | _                 | UPLLIDIV<2:0>(1)  |                  |                  |  |

| 7.0          | r-1                   | R/P-1             | R/P               | R/P-1             | r-1               | R/P               | R/P              | R/P              |  |

| 7:0          | —                     | F                 | PLLMUL<2:0>       |                   | _                 | F                 | PLLIDIV<2:0      | >                |  |

#### **DEVCFG2: DEVICE CONFIGURATION WORD 2 REGISTER 27-3:**

| Legend:           | r = Reserved bit | P = Programmable bit                    |

|-------------------|------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

### bit 31-19 Reserved: Write '1'

bit 15

bit 7

bit 18-16 FPLLODIV<2:0>: Default PLL Output Divisor bits

- 111 = PLL output divided by 256 110 = PLL output divided by 64 101 = PLL output divided by 32 100 = PLL output divided by 16 011 = PLL output divided by 8 010 = PLL output divided by 4 001 = PLL output divided by 2 000 = PLL output divided by 1 UPLLEN: USB PLL Enable bit<sup>(1)</sup> 1 = Disable and bypass USB PLL 0 = Enable USB PLL bit 14-11 Reserved: Write '1' bit 10-8 UPLLIDIV<2:0>: USB PLL Input Divider bits<sup>(1)</sup> 111 = 12x divider 110 = 10x divider 101 = 6x divider100 = 5x divider 011 = 4x divider 010 = 3x divider 010 = 3x divider 001 = 2x divider000 = 1x divider Reserved: Write '1'

- bit 6-4 FPLLMUL<2:0>: PLL Multiplier bits

- 111 = 24x multiplier 110 = 21x multiplier

- 101 = 20x multiplier

- 100 = 19x multiplier

- 011 = 18x multiplier

- 010 = 17x multiplier

- 001 = 16x multiplier

- 000 = 15x multiplier

- bit 3 Reserved: Write '1'

Note 1: This bit is only available on PIC32MX2XX devices.

| DC CHARACTERISTICS                    |                        |         |       | $\begin{array}{ll} \mbox{Standard Operating Conditions: } 2.3V \ to \ 3.6V \ (unless \ otherwise \ stated) \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \ for \ Industrial \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \ for \ V-temp \end{array}$ |                                                 |  |  |  |  |

|---------------------------------------|------------------------|---------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|--|--|

| Param.<br>No.                         | Typical <sup>(2)</sup> | Max.    | Units | Conditions                                                                                                                                                                                                                                                                    |                                                 |  |  |  |  |

| Power-Down Current (IPD) (Notes 1, 5) |                        |         |       |                                                                                                                                                                                                                                                                               |                                                 |  |  |  |  |

| DC40k                                 | 44                     | 70      | μA    | -40°C                                                                                                                                                                                                                                                                         |                                                 |  |  |  |  |

| DC40I                                 | 44                     | 70      | μA    | +25°C                                                                                                                                                                                                                                                                         |                                                 |  |  |  |  |

| DC40n                                 | 168                    | 259     | μA    | +85°C                                                                                                                                                                                                                                                                         | Base Power-Down Current                         |  |  |  |  |

| DC40m                                 | 335                    | 536     | μA    | +105°C                                                                                                                                                                                                                                                                        |                                                 |  |  |  |  |

| Module                                | Differential           | Current |       |                                                                                                                                                                                                                                                                               |                                                 |  |  |  |  |

| DC41e                                 | 5                      | 20      | μA    | 3.6V                                                                                                                                                                                                                                                                          | Watchdog Timer Current: AIWDT (Note 3)          |  |  |  |  |

| DC42e                                 | 23                     | 50      | μA    | 3.6V                                                                                                                                                                                                                                                                          | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3) |  |  |  |  |

| DC43d                                 | 1000                   | 1100    | μA    | 3.6V ADC: △IADC (Notes 3,4)                                                                                                                                                                                                                                                   |                                                 |  |  |  |  |

### TABLE 30-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** The test conditions for IPD current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

OSC2/CLKO is configured as an I/O input pin

• USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

• CPU is in Sleep mode, and SRAM data memory Wait states = 1

• No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

• WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

• All I/O pins are configured as inputs and pulled to Vss

• MCLR = VDD

• RTCC and JTAG are disabled

2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

#### FIGURE 30-10: SPIx MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS SCKx (CKP = 0) SP11 SP10 SP21 SP20 SCKx (CKP = 1) SP35 SP20 SP21 SDOx MSb Bit 14 -1 LSb **SP31** SP30 SDIx LSb In MSb In Bit 14 SP40 'SP41' Note: Refer to Figure 30-1 for load conditions.

### TABLE 30-28: SPIx MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHA        | RACTERIST             | TICS                                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |      |       |                    |  |  |

|---------------|-----------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>             | Min.                                                                                                                                                                                                                                                                                  | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |  |

| SP10          | TscL                  | SCKx Output Low Time<br>(Note 3)           | Тѕск/2                                                                                                                                                                                                                                                                                | _                      |      | ns    | _                  |  |  |

| SP11          | TscH                  | SCKx Output High Time<br>(Note 3)          | Тѕск/2                                                                                                                                                                                                                                                                                | —                      | _    | ns    | _                  |  |  |

| SP20          | TscF                  | SCKx Output Fall Time (Note 4)             | —                                                                                                                                                                                                                                                                                     | —                      |      | ns    | See parameter DO32 |  |  |

| SP21          | TscR                  | SCKx Output Rise Time<br>(Note 4)          | —                                                                                                                                                                                                                                                                                     | —                      | _    | ns    | See parameter DO31 |  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)        | —                                                                                                                                                                                                                                                                                     | —                      | _    | ns    | See parameter DO32 |  |  |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)        | —                                                                                                                                                                                                                                                                                     | —                      | _    | ns    | See parameter DO31 |  |  |

| SP35          | TscH2doV,             | SDOx Data Output Valid after               | —                                                                                                                                                                                                                                                                                     | —                      | 15   | ns    | VDD > 2.7V         |  |  |

|               | TscL2doV              | SCKx Edge                                  |                                                                                                                                                                                                                                                                                       | _                      | 20   | ns    | VDD < 2.7V         |  |  |

| SP40          | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge | 10                                                                                                                                                                                                                                                                                    | —                      | —    | ns    | —                  |  |  |

| SP41          | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDIx Data Input to SCKx Edge  | 10                                                                                                                                                                                                                                                                                    | —                      |      | ns    |                    |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 50 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

### 33.1 Package Marking Information (Continued)

### 44-Lead VTLA

### 44-Lead QFN

### 44-Lead TQFP

Example

### Example

### Example

### Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                 | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (@3) |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|        |                                                                                                                                                                                          | can be found on the outer packaging for this package.                                                                                                                                                                                                                                                               |  |  |  |

| Note:  | If the full Microchip part number cannot be marked on one line, it is carried over to the next line, thus limiting the number of available characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                     |  |  |  |

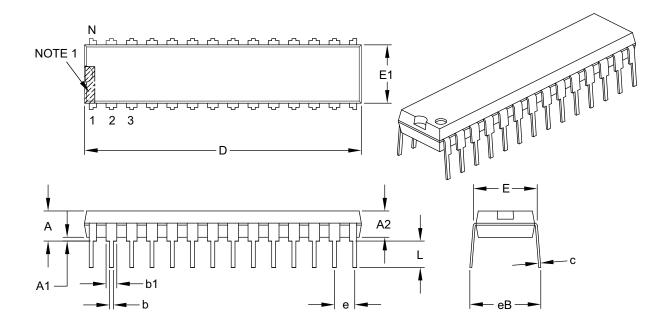

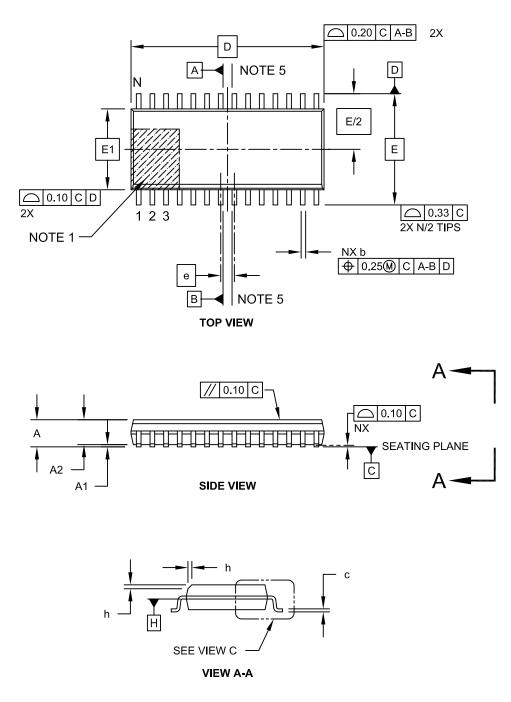

### 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units |          | INCHES |       |  |

|----------------------------|-------|----------|--------|-------|--|

| Dimension Limits           |       | MIN      | NOM    | MAX   |  |

| Number of Pins             | Ν     | 28       |        |       |  |

| Pitch                      | е     | .100 BSC |        |       |  |

| Top to Seating Plane       | Α     | -        | -      | .200  |  |

| Molded Package Thickness   | A2    | .120     | .135   | .150  |  |

| Base to Seating Plane      | A1    | .015     | -      | -     |  |

| Shoulder to Shoulder Width | Е     | .290     | .310   | .335  |  |

| Molded Package Width       | E1    | .240     | .285   | .295  |  |

| Overall Length             | D     | 1.345    | 1.365  | 1.400 |  |

| Tip to Seating Plane       | L     | .110     | .130   | .150  |  |

| Lead Thickness             | С     | .008     | .010   | .015  |  |

| Upper Lead Width           | b1    | .040     | .050   | .070  |  |

| Lower Lead Width           | b     | .014     | .018   | .022  |  |

| Overall Row Spacing §      | eВ    | -        | -      | .430  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2