Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f064bt-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 8: **PIN NAMES FOR 36-PIN USB DEVICES**

# 36-PIN VTLA (TOP VIEW)<sup>(1,2,3,5)</sup>

PIC32MX210F016C

|       | PIC32MX220F032C<br>PIC32MX230F064C<br>PIC32MX250F128C |       |                                                  |

|-------|-------------------------------------------------------|-------|--------------------------------------------------|

|       |                                                       |       | 36                                               |

|       |                                                       |       | 1                                                |

| Pin # | Full Pin Name                                         | Pin # | Full Pin Name                                    |

| 1     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2             | 19    | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 2     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3               | 20    | RPC9/CTED7/RC9                                   |

| 3     | PGED4 <sup>(4)</sup> /AN6/RPC0/RC0                    | 21    | Vss                                              |

| 4     | PGEC4 <sup>(4)</sup> /AN7/RPC1/RC1                    | 22    | VCAP                                             |

| 5     | VDD                                                   | 23    | VDD                                              |

| 6     | Vss                                                   | 24    | PGED2/RPB10/D+/CTED11/RB10                       |

| 7     | OSC1/CLKI/RPA2/RA2                                    | 25    | PGEC2/RPB11/D-/RB11                              |

| 8     | OSC2/CLKO/RPA3/PMA0/RA3                               | 26    | VUSB3V3                                          |

| 9     | SOSCI/RPB4/RB4                                        | 27    | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 10    | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4                        | 28    | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 11    | AN12/RPC3/RC3                                         | 29    | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 12    | Vss                                                   | 30    | AVss                                             |

| 13    | Vdd                                                   | 31    | AVdd                                             |

| 14    | VDD                                                   | 32    | MCLR                                             |

| 15    | TMS/RPB5/USBID/RB5                                    | 33    | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 16    | VBUS                                                  | 34    | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

| 17    | TDI/RPB7/CTED3/PMD5/INT0/RB7                          | 35    | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0        |

| 18    | TCK/RP88/SCL1/CTED10/PM04/RB8                         | 36    | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1       |

Note The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin 1: Select" for restrictions.

Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information. 2:

The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally. 3:

4: This pin function is not available on PIC32MX210F016C and PIC32MX120F032C devices.

5: Shaded pins are 5V tolerant.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 31:24        |                   |                   |                   | NVMDA             | TA<31:24>         |                   |                  |                  |  |  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 23:16        | NVMDATA<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 15:8         | NVMDATA<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | NVMD              | ATA<7:0>          |                   |                  |                  |  |  |  |  |  |  |  |

### REGISTER 5-4: NVMDATA: FLASH PROGRAM DATA REGISTER

### Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 NVMDATA<31:0>: Flash Programming Data bits

Note: The bits in this register are only reset by a Power-on Reset (POR).

# REGISTER 5-5: NVMSRCADDR: SOURCE DATA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |  |

| 31:24        | NVMSRCADDR<31:24> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |  |

| 23:16        |                   | NVMSRCADDR<23:16> |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |  |

| 15:8         |                   |                   |                   | NVMSRC/           | ADDR<15:8>        |                   |                  |                  |  |  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | NVMSRC            | ADDR<7:0>         |                   |                  |                  |  |  |  |  |  |  |  |  |

| Legend:           |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

### bit 31-0 NVMSRCADDR<31:0>: Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

# REGISTER 9-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 **CRCTYP:** CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

NOTES:

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31.24        | -                 | —                 | —                 | -                 | -                 | —                 | -                | —                |  |  |  |  |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | -                 | —                 | —                 | -                 | -                 | —                 | -                | —                |  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 15.6         |                   | _                 | -                 |                   |                   | —                 |                  | —                |  |  |  |  |  |

| 7.0          | R/WC-0, HS        | U-0              | R/WC-0, HS       |  |  |  |  |  |

| 7:0          | IDIF              | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          |                  | VBUSVDIF         |  |  |  |  |  |

# REGISTER 10-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable b  | pit                |

|-------------------|-------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIF:** ID State Change Indicator bit

- 1 = A change in the ID state was detected

- 0 = No change in the ID state was detected

- bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

### bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1 ms, but different from last time

- 0 = USB line state has not been stable for 1 ms

- bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

- bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = A change on the session valid input was detected

- 0 = No change on the session valid input was detected

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                 | —                 | -                 | —                 | _                      | _                 | —                | _                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                 | —                 | -                 | —                 | _                      | _                 | —                | _                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |

| 15.0         | —                 | —                 |                   | —                 | _                      | _                 | —                | _                |  |  |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0            |  |  |

| 7:0          | UACTPND           |                   |                   | USLPGRD           | USBBUSY <sup>(1)</sup> | _                 | USUSPEND         | USBPWR           |  |  |

### REGISTER 10-5: U1PWRC: USB POWER CONTROL REGISTER

# Legend:

| zogonai           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; however, an interrupt is pending, which has yet to be generated

0 = An interrupt is not pending

- bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

- bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

# **Note 1:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

# REGISTER 10-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the EVEN Buffer Descriptor banks

- 0 = Even/Odd buffer pointers are not Reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit<sup>(5)</sup>

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

# TABLE 11-6: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| ssa                         |                  |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FA04                        | INT1R            | 31:16     |       | _     |       |       | _     | _     |      |      |      | _    |      |      |      | _     | _      |      | 0000       |

| FA04                        |                  | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | INT1F | R<3:0> |      | 0000       |

| FA08                        | INT2R            | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | _     | —      | —    | 0000       |

| FAUO                        | INTZR            | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | INT2F | R<3:0> |      | 0000       |

| FA0C                        | INT3R            | 31:16     | _     | _     | _     | _     | —     | —     | _    | _    | —    | _    |      | —    | _    |       | —      | —    | 0000       |

| FAUC                        | IN I 3R          | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | INT3F | R<3:0> |      | 0000       |

| 5440                        |                  | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | -    | 0000       |

| FA10                        | INT4R            | 15:0      | -     | _     | _     | _     | -     | -     | _    | _    | _    | _    | _    | _    |      | INT4F | R<3:0> |      | 0000       |

| 5440                        | TAOKA            | 31:16     | _     | _     | _     | _     | —     | —     | _    | _    | _    | _    | _    | _    | _    | _     | _      | —    | 0000       |

| FA18                        | T2CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T2CK  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    | _    |       | _      | _    | 0000       |

| FA1C                        | T3CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    |      | T3CK  | R<3:0> | •    | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    |      | _    | _    |       | _      | _    | 0000       |

| FA20                        | T4CKR            | 15:0      | _     |       | _     |       | _     | _     | _    | _    | _    |      |      | _    |      | T4CK  | R<3:0> | •    | 0000       |

|                             |                  | 31:16     | _     |       | _     |       | _     | _     | _    | _    | _    |      |      | _    | _    |       | _      | _    | 0000       |

| FA24                        | T5CKR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T5CK  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |       | —      | _    | 0000       |

| FA28                        | IC1R             | 15:0      | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | IC1R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _     | _      | _    | 0000       |

| FA2C                        | IC2R             | 15:0      | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      |      | IC2R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | _     | _      | _    | 0000       |

| FA30                        | IC3R             | 15:0      | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | IC3R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _     | _      | _    | 0000       |

| FA34                        | IC4R             | 15:0      | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      |      | IC4R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | _    |      | _    |      | _    | _     | _      | _    | 0000       |

| FA38                        | IC5R             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | IC5R  | <3:0>  |      | 0000       |

|                             |                  | 31:16     | _     | _     |       |       | _     | _     |      | _    | _    | _    | _    | _    |      | _     |        | _    | 0000       |

| FA48                        | OCFAR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFA  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA4C                        | OCFBR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | OCFB  | R<3:0> |      | 0000       |

|                             |                  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FA50                        | U1RXR            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U1RX  | R<3:0> |      | 0000       |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

# TABLE 11-7: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                      |           |       | Bits  |       |       |       |       |      |      |      |      |      |      |      |      |       |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|-------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0 | All Resets |

| 5000                        | RPC8R <sup>(1)</sup> | 31:16     | _     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _    | —    | —     | —    | 0000       |

| FB8C                        | RPCoR                | 15:0      | —     | —     | —     | —     | —     | _     | —    | —    | _    | —    | —    | —    |      | RPC8 | <3:0> |      | 0000       |

| 5000                        | RPC9R <sup>(3)</sup> | 31:16     | —     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    | _    | —    | —     |      | 0000       |

| FB90                        | RPC9R                | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    |      | RPC  | <3:0> |      | 0000       |

x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Note 1:

2:

This register is only available on 44-pin devices. This register is only available on PIC32MX1XX devices. This register is only available on 36-pin and 44-pin devices. 3:

NOTES:

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

# REGISTER 20-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

- bit 4 Unimplemented: Read as '0' CS1P: Chip Select 0 Polarity bit<sup>(2)</sup> bit 3 1 = Active-high (PMCS1)  $0 = \text{Active-low}(\overline{PMCS1})$ bit 2 Unimplemented: Read as '0' bit 1 WRSP: Write Strobe Polarity bit For Slave Modes and Master mode 2 (MODE<1:0> = 00,01,10): 1 = Write strobe active-high (PMWR) 0 = Write strobe active-low (PMWR) For Master mode 1 (MODE<1:0> = 11): 1 = Enable strobe active-high (PMENB) 0 = Enable strobe active-low (PMENB) bit 0 RDSP: Read Strobe Polarity bit For Slave modes and Master mode 2 (MODE<1:0> = 00,01,10): 1 = Read Strobe active-high (PMRD)  $0 = \text{Read Strobe active-low}(\overline{PMRD})$ For Master mode 1 (MODE<1:0> = 11): 1 = Read/write strobe active-high (PMRD/PMWR)

- 0 = Read/write strobe active-low (PMRD/PMWR)

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------------|------------------|--|--|

| 24.24        | U-0                     | U-0               | U-0               | U-0               | U-0                    | U-0               | R/W-0                  | R/W-0            |  |  |

| 31:24        | —                       |                   | _                 | _                 | —                      | —                 | CAL<9                  | :8>              |  |  |

| 00.40        | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                  | R/W-0             | R/W-0                  | R/W-0            |  |  |

| 23:16        | CAL<7:0>                |                   |                   |                   |                        |                   |                        |                  |  |  |

| 45.0         | R/W-0                   | U-0               | R/W-0             | U-0               | U-0                    | U-0               | U-0                    | U-0              |  |  |

| 15:8         | ON <sup>(1,2)</sup>     | _                 | SIDL              | _                 | —                      | _                 | _                      |                  |  |  |

| 7.0          | R/W-0                   | R-0               | U-0               | U-0               | R/W-0                  | R-0               | R-0                    | R/W-0            |  |  |

| 7:0          | RTSECSEL <sup>(3)</sup> | RTCCLKON          |                   | _                 | RTCWREN <sup>(4)</sup> | RTCSYNC           | HALFSEC <sup>(5)</sup> | RTCOE            |  |  |

|              |                         |                   |                   |                   |                        |                   |                        |                  |  |  |

## REGISTER 21-1: RTCCON: RTC CONTROL REGISTER

# Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-26 Unimplemented: Read as '0'

bit 25-16 CAL<9:0>: RTC Drift Calibration bits, which contain a signed 10-bit integer value 0111111111 = Maximum positive adjustment, adds 511 RTC clock pulses every one minute 000000001 = Minimum positive adjustment, adds 1 RTC clock pulse every one minute 000000000 = No adjustment 1111111111 = Minimum negative adjustment, subtracts 1 RTC clock pulse every one minute 100000000 = Maximum negative adjustment, subtracts 512 clock pulses every one minute ON: RTCC On bit<sup>(1,2)</sup> bit 15 1 = RTCC module is enabled 0 = RTCC module is disabled bit 14 Unimplemented: Read as '0' bit 13 SIDL: Stop in Idle Mode bit 1 = Disables the PBCLK to the RTCC when the device enters Idle mode 0 = Continue normal operation when the device enters Idle mode bit 12-8 Unimplemented: Read as '0' bit 7 RTSECSEL: RTCC Seconds Clock Output Select bit<sup>(3)</sup> 1 = RTCC Seconds Clock is selected for the RTCC pin 0 = RTCC Alarm Pulse is selected for the RTCC pin bit 6 RTCCLKON: RTCC Clock Enable Status bit 1 = RTCC Clock is actively running 0 = RTCC Clock is not running **Note 1:** The ON bit is only writable when RTCWREN = 1. 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. 3: Requires RTCOE = 1 (RTCCON<0>) for the output to be active. 4: The RTCWREN bit can be set only when the write sequence is enabled. 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

**Note:** This register is reset only on a Power-on Reset (POR).

© 2011-2016 Microchip Technology Inc.

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- · On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

# 26.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor ratio.

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator startup delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN (OSCCON<4>) bit is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- On any form of device Reset

- On a WDT time-out interrupt

### 26.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The Peripheral Bus can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as the USB, Interrupt Controller, DMA, and the bus matrix are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

| DC CHA                                | RACTERIS               | TICS    | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                             |                                                 |  |  |  |

|---------------------------------------|------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------|--|--|--|

| Param.<br>No.                         | Typical <sup>(2)</sup> | Max.    | Units                                                                                                                                                                                               | Conditions                  |                                                 |  |  |  |

| Power-Down Current (IPD) (Notes 1, 5) |                        |         |                                                                                                                                                                                                     |                             |                                                 |  |  |  |

| DC40k                                 | 44                     | 70      | μA                                                                                                                                                                                                  | -40°C                       |                                                 |  |  |  |

| DC40I                                 | 44                     | 70      | μA                                                                                                                                                                                                  | +25°C                       | Base Power-Down Current                         |  |  |  |

| DC40n                                 | 168                    | 259     | μA                                                                                                                                                                                                  | +85°C                       |                                                 |  |  |  |

| DC40m                                 | 335                    | 536     | μA                                                                                                                                                                                                  | +105°C                      |                                                 |  |  |  |

| Module                                | Differential           | Current |                                                                                                                                                                                                     |                             |                                                 |  |  |  |

| DC41e                                 | 5                      | 20      | μA                                                                                                                                                                                                  | 3.6V                        | Watchdog Timer Current: AIWDT (Note 3)          |  |  |  |

| DC42e                                 | 23                     | 50      | μA                                                                                                                                                                                                  | 3.6V                        | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3) |  |  |  |

| DC43d                                 | 1000                   | 1100    | μA                                                                                                                                                                                                  | 3.6V ADC: △IADC (Notes 3,4) |                                                 |  |  |  |

# TABLE 30-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** The test conditions for IPD current measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

OSC2/CLKO is configured as an I/O input pin

• USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

• CPU is in Sleep mode, and SRAM data memory Wait states = 1

• No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

• WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

• All I/O pins are configured as inputs and pulled to Vss

• MCLR = VDD

• RTCC and JTAG are disabled

2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: IPD electrical characteristics for devices with 256 KB Flash are only provided as Preliminary information.

### TABLE 30-9: DC CHARACTERISTICS: I/O PIN INPUT INJECTION CURRENT SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                                       | $ \begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array} $ |   |                       |    |                                                                                                                                       |  |

|--------------------|--------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------|----|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics                                                       | Min. Typ. <sup>(1)</sup> Max. Units Conditions                                                                                                                                                                                                                           |   |                       |    |                                                                                                                                       |  |

| Dl60a              | licl   | Input Low Injection<br>Current                                        | 0                                                                                                                                                                                                                                                                        |   | <sub>-5</sub> (2,5)   | mA | This parameter applies to all pins,<br>with the exception of the power<br>pins.                                                       |  |

| DI60b              | ІІСН   | Input High Injection<br>Current                                       | 0                                                                                                                                                                                                                                                                        | — | +5 <sup>(3,4,5)</sup> | mA | This parameter applies to all pins,<br>with the exception of all 5V tolerant<br>pins, and the SOSCI, SOSCO,<br>OSC1, D+, and D- pins. |  |

| DI60c              | ∑lict  | Total Input Injection<br>Current (sum of all I/O<br>and Control pins) | -20 <b>(6)</b>                                                                                                                                                                                                                                                           | — | +20 <b>(6)</b>        | mA | Absolute instantaneous sum of all $\pm$ input injection currents from all I/O pins (   IICL +   IICH   ) $\leq \sum$ IICT )           |  |

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: VIL source < (VSS - 0.3). Characterized but not tested.

**3:** VIH source > (VDD + 0.3) for non-5V tolerant pins only.

4: Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

5: Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (VSS - 0.3)).

6: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 2, IICL = (((Vss - 0.3) - VIL source) / Rs). If Note 3, IICH = ((IICH source - (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss - 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

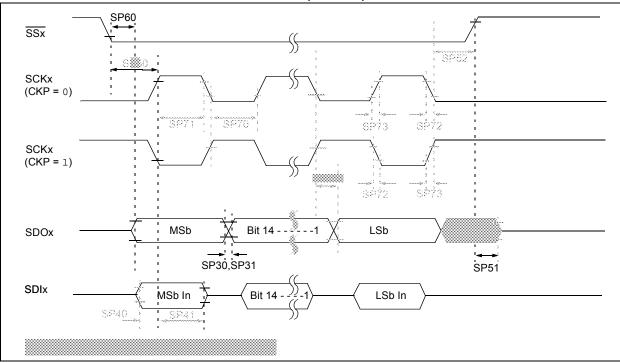

### FIGURE 30-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

### TABLE 30-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        | RACTERIS              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature } -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |        |                        |      |       |                    |

|---------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------|------|-------|--------------------|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                                                                                                                                                                                                                                 | Min.   | Typical <sup>(2)</sup> | Max. | Units | Conditions         |

| SP70          | TscL                  | SCKx Input Low Time (Note 3)                                                                                                                                                                                                                                                   | Tsck/2 | _                      | _    | ns    | —                  |

| SP71          | TscH                  | SCKx Input High Time (Note 3)                                                                                                                                                                                                                                                  | Tsck/2 | —                      | _    | ns    | —                  |

| SP72          | TscF                  | SCKx Input Fall Time                                                                                                                                                                                                                                                           | _      | 5                      | 10   | ns    | —                  |

| SP73          | TscR                  | SCKx Input Rise Time                                                                                                                                                                                                                                                           | —      | 5                      | 10   | ns    | —                  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)                                                                                                                                                                                                                                            | —      | —                      | _    | ns    | See parameter DO32 |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)                                                                                                                                                                                                                                            | —      | —                      | _    | ns    | See parameter DO31 |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                                                                                                                                                                                                                                                   | _      | —                      | 20   | ns    | VDD > 2.7V         |

|               | TscL2DoV              | SCKx Edge                                                                                                                                                                                                                                                                      | _      | —                      | 30   | ns    | VDD < 2.7V         |

| SP40          | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                                                                                                                                     | 10     | —                      | _    | ns    | —                  |

| SP41          | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                                                                                                                                                                                                                      | 10     | —                      |      | ns    | —                  |

| SP50          | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input                                                                                                                                                                                                      | 175    | —                      |      | ns    | _                  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 50 ns.

- **4:** Assumes 50 pF load on all SPIx pins.

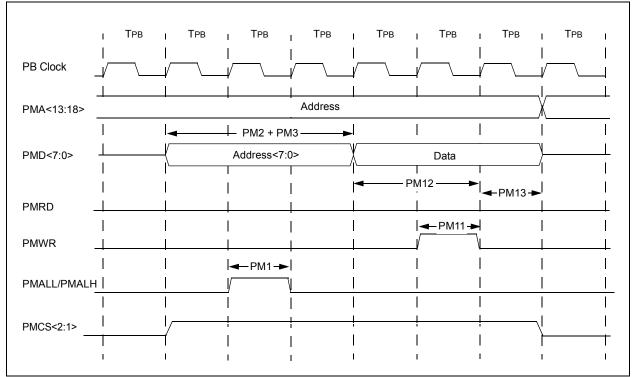

|               |         |                                                                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |       |      |       |            |  |

|---------------|---------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                       | Min.                                                                                                                                                                                                                                                                            | Тур.  | Max. | Units | Conditions |  |

| PM1           | Tlat    | PMALL/PMALH Pulse Width                                              |                                                                                                                                                                                                                                                                                 | 1 Трв | _    | _     | _          |  |

| PM2           | TADSU   | Address Out Valid to<br>PMALL/PMALH Invalid (address<br>setup time)  | _                                                                                                                                                                                                                                                                               | 2 Трв | _    | _     | _          |  |

| PM3           | Tadhold | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | —                                                                                                                                                                                                                                                                               | 1 Трв | _    | —     | _          |  |

| PM4           | TAHOLD  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5                                                                                                                                                                                                                                                                               | _     | _    | ns    | _          |  |

| PM5           | Trd     | PMRD Pulse Width                                                     | _                                                                                                                                                                                                                                                                               | 1 Трв | _    | _     | —          |  |

| PM6           | TDSU    | PMRD or PMENB Active to Data<br>In Valid (data setup time)           | 15                                                                                                                                                                                                                                                                              | —     | —    | ns    | _          |  |

| PM7           | TDHOLD  | PMRD or PMENB Inactive to Data In Invalid (data hold time)           | —                                                                                                                                                                                                                                                                               | 80    | —    | ns    |            |  |

### TABLE 30-38: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

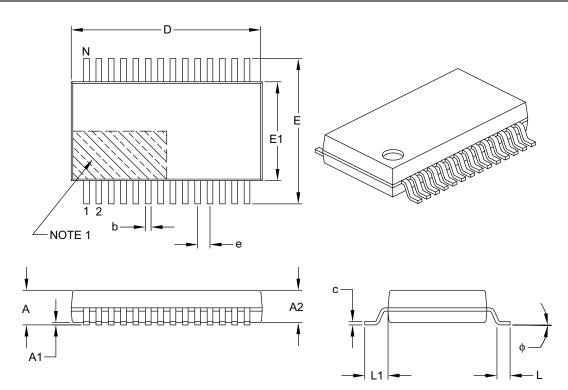

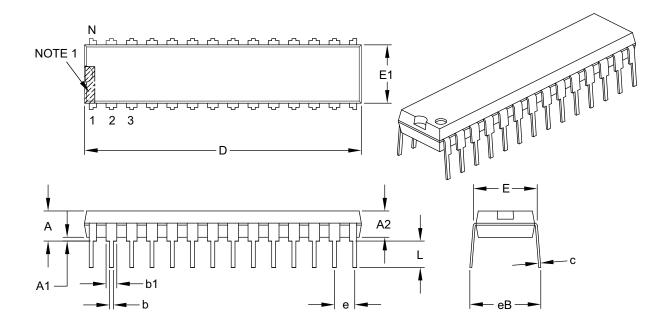

# 33.2 Package Details

This section provides the technical details of the packages.

# 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          | MILLIMETERS |       |  |  |

|--------------------------|------------------|----------|-------------|-------|--|--|

|                          | Dimension Limits | MIN      | NOM         | MAX   |  |  |

| Number of Pins           | N                |          | 28          |       |  |  |

| Pitch                    | e                |          | 0.65 BSC    |       |  |  |

| Overall Height           | A                | -        | -           | 2.00  |  |  |

| Molded Package Thickness | A2               | 1.65     | 1.75        | 1.85  |  |  |

| Standoff                 | A1               | 0.05     | -           | -     |  |  |

| Overall Width            | E                | 7.40     | 7.80        | 8.20  |  |  |

| Molded Package Width     | E1               | 5.00     | 5.30        | 5.60  |  |  |

| Overall Length           | D                | 9.90     | 10.20       | 10.50 |  |  |

| Foot Length              | L                | 0.55     | 0.75        | 0.95  |  |  |

| Footprint                | L1               | 1.25 REF |             |       |  |  |

| Lead Thickness           | С                | 0.09     | -           | 0.25  |  |  |

| Foot Angle               | φ                | 0°       | 4°          | 8°    |  |  |

| Lead Width               | b                | 0.22     | -           | 0.38  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

# 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |       | INCHES   |       |

|----------------------------|------------------|-------|----------|-------|

| Dimension                  | Dimension Limits |       | NOM      | MAX   |

| Number of Pins             | Ν                |       | 28       |       |

| Pitch                      | е                |       | .100 BSC |       |

| Top to Seating Plane       | Α                | -     | -        | .200  |

| Molded Package Thickness   | A2               | .120  | .135     | .150  |

| Base to Seating Plane      | A1               | .015  | -        | -     |

| Shoulder to Shoulder Width | Е                | .290  | .310     | .335  |

| Molded Package Width       | E1               | .240  | .285     | .295  |

| Overall Length             | D                | 1.345 | 1.365    | 1.400 |

| Tip to Seating Plane       | L                | .110  | .130     | .150  |

| Lead Thickness             | С                | .008  | .010     | .015  |

| Upper Lead Width           | b1               | .040  | .050     | .070  |

| Lower Lead Width           | b                | .014  | .018     | .022  |

| Overall Row Spacing §      | eB               | -     | -        | .430  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

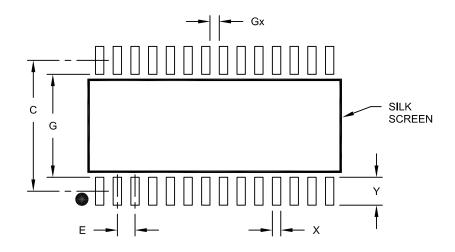

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | Units    |          |      | S    |

|--------------------------|----------|----------|------|------|

| Dimensio                 | n Limits | MIN      | NOM  | MAX  |

| Contact Pitch            | E        | 1.27 BSC |      |      |

| Contact Pad Spacing      | С        |          | 9.40 |      |

| Contact Pad Width (X28)  | X        |          |      | 0.60 |

| Contact Pad Length (X28) | Y        |          |      | 2.00 |

| Distance Between Pads    | Gx       | 0.67     |      |      |

| Distance Between Pads    | G        | 7.40     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A