Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | MIPS32 ® M4K™                                                                  |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 25                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 12x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 36-VFTLA Exposed Pad                                                           |

| Supplier Device Package    | 36-VTLA (5x5)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f064c-i-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error.<br>Fetch reference to protected address.                                                                 |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error.<br>Load reference to protected address.                                                                   |

| AdES      | Store address alignment error.<br>Store to protected address.                                                                           |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

## TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

## 3.3 Power Management

The MIPS M4K processor core offers many power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

## 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 26.0 "Power-Saving Features".

## 3.4 EJTAG Debug Support

The MIPS M4K processor core provides an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | —                 | —                 |                   | —                | —                |

|              | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |

| 23:16        | _                 | —                 | _                 | BMX<br>ERRIXI     | BMX<br>ERRICD     | BMX<br>ERRDMA     | BMX<br>ERRDS     | BMX<br>ERRIS     |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | —                 | -                 | —                 | _                 |                  | —                |

|              | U-0               | R/W-1             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |

| 7:0          | _                 | BMX<br>WSDRM      | _                 | _                 | _                 | E                 | 3MXARB<2:0       | >                |

## REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

## Legend:

| 5                 |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

## bit 31-21 Unimplemented: Read as '0'

|          | Ommplemented. Read as 0                                                                                                                                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 20   | BMXERRIXI: Enable Bus Error from IXI bit                                                                                                                                                                                              |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> </ul>                 |

| bit 19   | BMXERRICD: Enable Bus Error from ICD Debug Unit bit                                                                                                                                                                                   |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from ICD</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from ICD</li> </ul>                                       |

| bit 18   | BMXERRDMA: Bus Error from DMA bit                                                                                                                                                                                                     |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from DMA</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from DMA</li> </ul>                                       |

| bit 17   | BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)                                                                                                                                                                 |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access</li> </ul>               |

| bit 16   | BMXERRIS: Bus Error from CPU Instruction Access bit (disabled in Debug mode)                                                                                                                                                          |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> </ul> |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 6    | BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit                                                                                                                                                                 |

|          | <ul> <li>1 = Data RAM accesses from CPU have one wait state for address setup</li> <li>0 = Data RAM accesses from CPU have zero wait states for address setup</li> </ul>                                                              |

| bit 5-3  | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 2-0  | BMXARB<2:0>: Bus Matrix Arbitration Mode bits                                                                                                                                                                                         |

|          | 111 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          | •                                                                                                                                                                                                                                     |

|          | •                                                                                                                                                                                                                                     |

|          | <ul><li>011 = Reserved (using these Configuration modes will produce undefined behavior)</li><li>010 = Arbitration Mode 2</li></ul>                                                                                                   |

|          | 001 = Arbitration Mode 1 (default)<br>000 = Arbitration Mode 0                                                                                                                                                                        |

|          |                                                                                                                                                                                                                                       |

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                   | —                 | —                 | _                 | _                 | _                 | _                | —                |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | _                 | -                 | _                 |                   |                  | —                |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8         | CHSPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          | CHSPTR<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |

## REGISTER 9-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

#### REGISTER 9-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                   |                   | _                 | _                 | —                 |                   | —                | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        |                   |                   | _                 | _                 | —                 |                   | —                | —                |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8         | CHDPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          |                   |                   |                   | CHDPTF            | R<7:0>            |                   |                  |                  |  |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

1111111111111111 = Points to byte 65,535 of the destination

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

## REGISTER 10-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER (CONTINUED)

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup>

- 1 = Token packet rejected due to CRC5 error

- 0 = Token packet accepted

- EOFEF: EOF Error Flag bit<sup>(3,5)</sup>

- 1 = An EOF error condition was detected

- 0 = No EOF error condition was detected

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check failed

- 0 = PID check passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|--|

| 31:24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |

| 31.24        | —                 | —                 | —                        | _                 | —                     | —                     |                  | _                    |  |

| 22:16        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |

| 23:16        | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |  |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |

| 15.0         | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |  |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |  |

| 7:0          | JSTATE            | ISTATE SE0        | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |  |

|              | JUNATE            | 320               | TOKBUSY <sup>(1,5)</sup> |                   |                       |                       |                  | SOFEN <sup>(5)</sup> |  |

## REGISTER 10-11: U1CON: USB CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE was detected on the USB

- 0 = No JSTATE was detected on the

- bit 6 **SE0:** Live Single-Ended Zero flag bit 1 = Single-Ended Zero was detected on the USB

- 0 = No Single-Ended Zero was detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing is disabled (set upon SETUP token received)

- 0 = Token and packet processing is enabled

- TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token is being executed by the USB module

- 0 = No token is being executed

#### bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset generated

- 0 = USB reset terminated

- bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

- bit 2 RESUME: RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

## PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 |                   | _                 | —                 |                   | -                | -                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   | _                 | —                 |                   | -                | -                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | _                 |                   | _                 | —                 |                   | -                | -                |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | LSPD              | RETRYDIS          |                   | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

#### REGISTER 10-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

#### Legend:

| =0901141          |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

- 1 = Direct connection to a Low-Speed device enabled

- 0 = Direct connection to a Low-Speed device disabled; hub required with PRE\_PID

- bit 6 **RETRYDIS:** Retry Disable bit (Host mode and U1EP0 only)

- 1 = Retry NAKed transactions disabled

- 0 = Retry NAKed transactions enabled; retry done in hardware

#### bit 5 Unimplemented: Read as '0'

bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

If EPTXEN = 1 and EPRXEN = 1:

1 = Disable Endpoint n from Control transfers; only TX and RX transfers allowed

0 = Enable Endpoint n for Control (SETUP) transfers; TX and RX transfers also allowed Otherwise, this bit is ignored.

- bit 3 **EPRXEN:** Endpoint Receive Enable bit

- 1 = Endpoint n receive is enabled

- 0 = Endpoint n receive is disabled

- bit 2 EPTXEN: Endpoint Transmit Enable bit

- 1 = Endpoint n transmit is enabled

- 0 = Endpoint n transmit is disabled

- bit 1 EPSTALL: Endpoint Stall Status bit

- 1 = Endpoint n was stalled

- 0 = Endpoint n was not stalled

- bit 0 EPHSHK: Endpoint Handshake Enable bit

- 1 = Endpoint Handshake is enabled

- 0 = Endpoint Handshake is disabled (typically used for isochronous endpoints)

## TABLE 11-2: OUTPUT PIN SELECTION

| RPn Port Pin | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection       |

|--------------|----------|-------------|---------------------------------------------|

| RPA0         | RPA0R    | RPA0R<3:0>  | 0000 = No Connect                           |

| RPB3         | RPB3R    | RPB3R<3:0>  | 0001 = <u>U1TX</u><br>0010 = <u>U2RTS</u>   |

| RPB4         | RPB4R    | RPB4R<3:0>  | 0011 = SS1                                  |

| RPB15        | RPB15R   | RPB15R<3:0> |                                             |

| RPB7         | RPB7R    | RPB7R<3:0>  | 0110 = Reserved<br>0111 = C2OUT             |

| RPC7         | RPC7R    | RPC7R<3:0>  | 1000 = Reserved                             |

| RPC0         | RPC0R    | RPC0R<3:0>  | •                                           |

| RPC5         | RPC5R    | RPC5R<3:0>  | •<br>1111 = Reserved                        |

| RPA1         | RPA1R    | RPA1R<3:0>  | 0000 = No Connect                           |

| RPB5         | RPB5R    | RPB5R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPB1         | RPB1R    | RPB1R<3:0>  | 0011 = SDO1                                 |

| RPB11        | RPB11R   | RPB11R<3:0> | 0100 = SDO2<br>0101 = OC2                   |

| RPB8         | RPB8R    | RPB8R<3:0>  | 0110 = Reserved                             |

| RPA8         | RPA8R    | RPA8R<3:0>  |                                             |

| RPC8         | RPC8R    | RPC8R<3:0>  | •                                           |

| RPA9         | RPA9R    | RPA9R<3:0>  | 1111 = Reserved                             |

| RPA2         | RPA2R    | RPA2R<3:0>  | 0000 = No Connect                           |

| RPB6         | RPB6R    | RPB6R<3:0>  | 0001 = Reserved<br>0010 = Reserved          |

| RPA4         | RPA4R    | RPA4R<3:0>  | 0011 = SDO1<br>0100 = SDO2                  |

| RPB13        | RPB13R   | RPB13R<3:0> | 0101 <b>= OC4</b>                           |

| RPB2         | RPB2R    | RPB2R<3:0>  |                                             |

| RPC6         | RPC6R    | RPC6R<3:0>  | 1000 = Reserved                             |

| RPC1         | RPC1R    | RPC1R<3:0>  |                                             |

| RPC3         | RPC3R    | RPC3R<3:0>  | 1111 = Reserved                             |

| RPA3         | RPA3R    | RPA3R<3:0>  | 0000 = No Connect                           |

| RPB14        | RPB14R   | RPB14R<3:0> |                                             |

| RPB0         | RPB0R    | RPB0R<3:0>  | 0011 = <u>Reserved</u><br>0100 = <u>SS2</u> |

| RPB10        | RPB10R   | RPB10R<3:0> | 0101 <b>= OC3</b>                           |

| RPB9         | RPB9R    | RPB9R<3:0>  | 0110 = Reserved<br>0111 = C1OUT             |

| RPC9         | RPC9R    | RPC9R<3:0>  | 1000 = Reserved                             |

| RPC2         | RPC2R    | RPC2R<3:0>  |                                             |

| RPC4         | RPC4R    | RPC4R<3:0>  | 1111 = Reserved                             |

## 11.4 Ports Control Registers

## TABLE 11-3: PORTA REGISTER MAP

| ess                         |                                 | 0         |       |       |       |       |       |                          |                       | Bits                    | 6                       |      |      |          |          |          |          |          | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|--------------------------|-----------------------|-------------------------|-------------------------|------|------|----------|----------|----------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10                    | 25/9                  | 24/8                    | 23/7                    | 22/6 | 21/5 | 20/4     | 19/3     | 18/2     | 17/1     | 16/0     | All Resets |

| 6000                        | ANSELA                          | 31:16     | _     | —     | —     | —     | _     | _                        | _                     | _                       | —                       |      | _    | _        | _        | —        | —        | _        | 0000       |

|                             |                                 | 15:0      | _     | —     | —     | —     | —     | -                        |                       |                         | —                       | _    | _    | —        | _        | _        | ANSA1    | ANSA0    | 0003       |

| 6010                        | TRISA                           | 31:16     | _     | —     | —     | —     | —     | —                        |                       |                         | —                       | _    | _    |          | —        | _        | _        | —        | 0000       |

| 0010                        |                                 | 15:0      | —     | —     | —     | —     | _     | TRISA10 <sup>(2)</sup>   | TRISA9 <sup>(2)</sup> | TRISA8 <sup>(2)</sup>   | TRISA7 <sup>(2)</sup>   | _    | —    | TRISA4   | TRISA3   | TRISA2   | TRISA1   | TRISA0   | 079F       |

| 6020                        | PORTA                           | 31:16     | —     | —     | —     | —     | _     | —                        | —                     | _                       | —                       | _    | —    |          |          |          |          |          | 0000       |

| 0020                        |                                 | 15:0      | —     | —     | —     | —     | _     | RA10 <sup>(2)</sup>      | RA9 <sup>(2)</sup>    | RA8 <sup>(2)</sup>      | RA7 <sup>(2)</sup>      | _    | —    | RA4      | RA3      | RA2      | RA1      | RA0      | xxxx       |

| 6030                        | LATA                            | 31:16     | _     | —     | —     | —     | _     |                          | _                     | _                       | —                       | —    | —    | _        | _        | _        |          | _        | 0000       |

| 0000                        |                                 | 15:0      | —     | —     | —     | —     | —     | LATA10 <sup>(2)</sup>    | LATA9 <sup>(2)</sup>  | LATA8 <sup>(2)</sup>    | LATA7 <sup>(2)</sup>    | —    | —    | LATA4    | LATA3    | LATA2    | LATA1    | LATA0    | xxxx       |

| 6040                        | ODCA                            | 31:16     | —     | —     | —     | —     | —     | —                        | _                     | _                       | —                       | —    | —    | —        |          | —        |          |          | 0000       |

| 0040                        | ODOA                            | 15:0      | —     | —     | —     | —     | —     | ODCA10 <sup>(2)</sup>    | ODCA9 <sup>(2)</sup>  | ODCA8 <sup>(2)</sup>    | ODCA7 <sup>(2)</sup>    | —    | —    | ODCA4    | ODCA3    | ODCA2    | ODCA1    | ODCA0    | 0000       |

| 6050                        | CNPUA                           | 31:16     | —     | —     | —     | —     | —     | —                        | _                     | _                       | —                       | —    | —    | —        |          | —        |          |          | 0000       |

| 0030                        | CINFUA                          | 15:0      | _     | _     | —     | —     | _     | CNPUA10 <sup>(2)</sup>   | CNPUA9 <sup>(2)</sup> | CNPUA8 <sup>(2)</sup>   | CNPUA7 <sup>(2)</sup>   | _    | —    | CNPUA4   | CNPUA3   | CNPUA2   | CNPUA1   | CNPUA0   | 0000       |

| 6060                        | CNPDA                           | 31:16     | —     | —     | —     | —     |       | _                        |                       |                         |                         | —    | —    |          |          | —        |          |          | 0000       |

| 0000                        | CINFDA                          | 15:0      | _     | _     | —     | —     | _     | CNPDA10 <sup>(2)</sup>   | CNPDA9 <sup>(2)</sup> | CNPDA8 <sup>(2)</sup>   | CNPDA7 <sup>(2)</sup>   | _    | —    | CNPDA4   | CNPDA3   | CNPDA2   | CNPDA1   | CNPDA0   | 0000       |

| 6070                        | CNCONA                          | 31:16     | —     | —     | —     | —     |       | _                        |                       | _                       | _                       | —    | —    |          |          | —        |          |          | 0000       |

| 0070                        | CINCONA                         | 15:0      | ON    | —     | SIDL  | —     | _     | _                        | _                     | _                       | —                       | _    | _    | _        | —        | —        | —        | —        | 0000       |

| 6080                        | CNENA                           | 31:16     | _     | —     | —     | —     | _     | _                        | _                     | _                       | —                       | _    | —    | —        | _        | _        | _        | _        | 0000       |

| 0000                        | CINEINA                         | 15:0      | _     | _     | —     | —     |       | CNIEA10 <sup>(2)</sup>   | CNIEA9 <sup>(2)</sup> | CNIEA8 <sup>(2)</sup>   | CNIEA7 <sup>(2)</sup>   |      |      | CNIEA4   | CNIEA3   | CNIEA2   | CNIEA1   | CNIEA0   | 0000       |

| 6000                        | CNISTATA                        | 31:16     | _     | _     | —     | —     |       |                          |                       |                         | _                       |      | _    |          |          | —        | _        |          | 0000       |

| 0090                        | CNSTATA                         | 15:0      | _     | _     | —     | —     |       | CNSTATA10 <sup>(2)</sup> | CNSTATA9(2)           | CNSTATA8 <sup>(2)</sup> | CNSTATA7 <sup>(2)</sup> |      |      | CNSTATA4 | CNSTATA3 | CNSTATA2 | CNSTATA1 | CNSTATA0 | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: This bit is only available on 44-pin devices.

|              |                   |                   |                   |                   |                   |                   |                  | ., _, _,         |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 |                   |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | -                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 |                   |                  | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 |                   |                   |                   |                   | _                | _                |

## **REGISTER 11-3:** CNCONX: CHANGE NOTICE CONTROL FOR PORTX REGISTER (X = A, B, C)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = Idle mode halts CN operation

- 0 = Idle does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

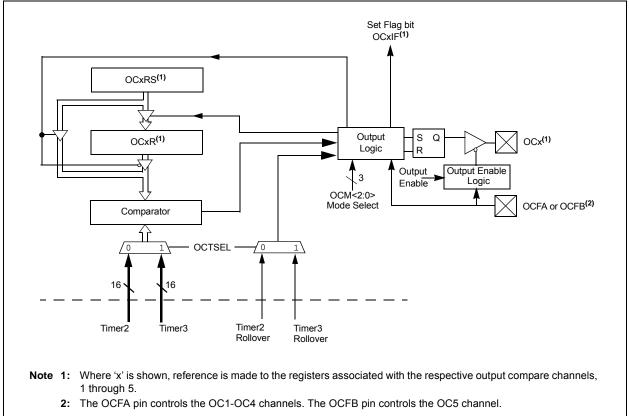

## 16.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Output Compare" (DS60001111), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation. The following are some of the key features:

- · Multiple Output Compare Modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

| REGIST    | ER 17-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)                                                         |  |  |  |  |  |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| bit 17    | SPIFE: Frame Sync Pulse Edge Select bit (Framed SPI mode only)                                             |  |  |  |  |  |  |  |  |

|           | 1 = Frame synchronization pulse coincides with the first bit clock                                         |  |  |  |  |  |  |  |  |

|           | 0 = Frame synchronization pulse precedes the first bit clock                                               |  |  |  |  |  |  |  |  |

| bit 16    | ENHBUF: Enhanced Buffer Enable bit <sup>(2)</sup>                                                          |  |  |  |  |  |  |  |  |

|           | 1 = Enhanced Buffer mode is enabled                                                                        |  |  |  |  |  |  |  |  |

|           | 0 = Enhanced Buffer mode is disabled                                                                       |  |  |  |  |  |  |  |  |

| bit 15    | ON: SPI Peripheral On bit <sup>(1)</sup>                                                                   |  |  |  |  |  |  |  |  |

|           | 1 = SPI Peripheral is enabled                                                                              |  |  |  |  |  |  |  |  |

|           | 0 = SPI Peripheral is disabled                                                                             |  |  |  |  |  |  |  |  |

| bit 14    | Unimplemented: Read as '0'                                                                                 |  |  |  |  |  |  |  |  |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                |  |  |  |  |  |  |  |  |

|           | 1 = Discontinue module operation when the device enters Idle mode                                          |  |  |  |  |  |  |  |  |

|           | 0 = Continue module operation when the device enters Idle mode                                             |  |  |  |  |  |  |  |  |

| bit 12    | DISSDO: Disable SDOx pin bit                                                                               |  |  |  |  |  |  |  |  |

|           | 1 = SDOx pin is not used by the module. Pin is controlled by associated PORT register                      |  |  |  |  |  |  |  |  |

|           | 0 = SDOx pin is controlled by the module                                                                   |  |  |  |  |  |  |  |  |

| bit 11-10 | MODE<32,16>: 32/16-Bit Communication Select bits                                                           |  |  |  |  |  |  |  |  |

|           | When AUDEN = 1:                                                                                            |  |  |  |  |  |  |  |  |

|           | MODE32 MODE16 Communication                                                                                |  |  |  |  |  |  |  |  |

|           | 1 1 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                  |  |  |  |  |  |  |  |  |

|           | 1 0 32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                  |  |  |  |  |  |  |  |  |

|           | 0 1 16-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame                                                  |  |  |  |  |  |  |  |  |

|           | 0 0 16-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame                                                  |  |  |  |  |  |  |  |  |

|           |                                                                                                            |  |  |  |  |  |  |  |  |

|           | When AUDEN = 0:                                                                                            |  |  |  |  |  |  |  |  |

|           | MODE32 MODE16 Communication                                                                                |  |  |  |  |  |  |  |  |

|           | 1 x 32-bit<br>0 1 16-bit                                                                                   |  |  |  |  |  |  |  |  |

|           | 0 	 1 	 10-51                                                                                              |  |  |  |  |  |  |  |  |

| bit 9     | SMP: SPI Data Input Sample Phase bit                                                                       |  |  |  |  |  |  |  |  |

| bit 5     | Master mode (MSTEN = 1):                                                                                   |  |  |  |  |  |  |  |  |

|           | 1 = Input data sampled at end of data output time                                                          |  |  |  |  |  |  |  |  |

|           | 0 = Input data sampled at middle of data output time                                                       |  |  |  |  |  |  |  |  |

|           | Slave mode (MSTEN = 0):                                                                                    |  |  |  |  |  |  |  |  |

|           | SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.                       |  |  |  |  |  |  |  |  |

|           | To write a '1' to this bit, the MSTEN value = 1 must first be written.                                     |  |  |  |  |  |  |  |  |

| bit 8     | CKE: SPI Clock Edge Select bit <sup>(3)</sup>                                                              |  |  |  |  |  |  |  |  |

|           | 1 = Serial output data changes on transition from active clock state to Idle clock state (see the CKP bit) |  |  |  |  |  |  |  |  |

|           | 0 = Serial output data changes on transition from Idle clock state to active clock state (see the CKP bit) |  |  |  |  |  |  |  |  |

| bit 7     | SSEN: Slave Select Enable (Slave mode) bit                                                                 |  |  |  |  |  |  |  |  |

|           | $1 = \overline{SSx}$ pin used for Slave mode                                                               |  |  |  |  |  |  |  |  |

|           | 0 = SSx pin not used for Slave mode, pin controlled by port function.                                      |  |  |  |  |  |  |  |  |

| bit 6     | <b>CKP:</b> Clock Polarity Select bit <sup>(4)</sup>                                                       |  |  |  |  |  |  |  |  |

|           | 1 = Idle state for clock is a high level; active state is a low level                                      |  |  |  |  |  |  |  |  |

|           | 0 = Idle state for clock is a low level; active state is a high level                                      |  |  |  |  |  |  |  |  |

| Note 1:   | When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in    |  |  |  |  |  |  |  |  |

|           | the SYSCLK cycle immediately following the instruction that clears the module's ON bit.                    |  |  |  |  |  |  |  |  |

| 2:        | This bit can only be written when the ON bit = $0$ .                                                       |  |  |  |  |  |  |  |  |

| 3:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI    |  |  |  |  |  |  |  |  |

|           | mode (FRMEN = 1).                                                                                          |  |  |  |  |  |  |  |  |

| 4:        | When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value |  |  |  |  |  |  |  |  |

|           | of CKP.                                                                                                    |  |  |  |  |  |  |  |  |

|           |                                                                                                            |  |  |  |  |  |  |  |  |

2

## REGISTER 18-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | -                 | —                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | —                 | _                | _                |

| 45.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |

| 15:8         | ACKSTAT           | TRSTAT            | -                 | -                 | _                 | BCL               | GCSTAT           | ADD10            |

| 7.0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |

| Legend:           | HS = Set in hardware                                | HSC = Hardware set/cleared |                   |  |  |  |

|-------------------|-----------------------------------------------------|----------------------------|-------------------|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                            | ead as '0'        |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared       | C = Clearable bit |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) 1 = Acknowledge was not received from slave 0 = Acknowledge was received from slave Hardware set or clear at end of slave Acknowledge. bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) 1 = Master transmit is in progress (8 bits + ACK) 0 = Master transmit is not in progress Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge. bit 13-11 Unimplemented: Read as '0' bit 10 BCL: Master Bus Collision Detect bit 1 = A bus collision has been detected during a master operation 0 = No collisionHardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module. bit 9 GCSTAT: General Call Status bit 1 = General call address was received 0 = General call address was not received Hardware set when address matches general call address. Hardware clear at Stop detection. bit 8 ADD10: 10-bit Address Status bit 1 = 10-bit address was matched 0 = 10-bit address was not matched Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

bit 7 IWCOL: Write Collision Detect bit

| 1 = An attempt to write the I2CxTRN register failed because the I <sup>2</sup> | C module is busy |

|--------------------------------------------------------------------------------|------------------|

| 0 = No collision                                                               |                  |

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

- bit 6 I2COV: Receive Overflow Flag bit

- 1 = A byte was received while the I2CxRCV register is still holding the previous byte 0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

### bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

## **30.0 ELECTRICAL CHARACTERISTICS**

This section provides an overview of the PIC32MX1XX/2XX 28/36/44-pin Family electrical characteristics for devices that operate at 40 MHz. Refer to **Section 31.0** "**50 MHz Electrical Characteristics**" for additional specifications for operations at higher frequency. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MX1XX/2XX 28/36/44-pin Family devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

## **Absolute Maximum Ratings**

### (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +105°C           |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             |                          |

| Voltage on VDD with respect to Vss                                              |                          |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 2.3V$ (Note 3) | 0.3V to +5.5V            |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | 0.3V to +5.5V            |

| Maximum current out of Vss pin(s)                                               |                          |

| Maximum current into VDD pin(s) (Note 2)                                        |                          |

| Maximum output current sunk by any I/O pin                                      | 15 mA                    |

| Maximum output current sourced by any I/O pin                                   | 15 mA                    |

| Maximum current sunk by all ports                                               | 200 mA                   |

| Maximum current sourced by all ports (Note 2)                                   | 200 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

3: See the "Pin Diagrams" section for the 5V tolerant pins.

## TABLE 30-14: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHARACTERISTICS |         |                                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |      |                    |       |                                                                 |  |  |

|--------------------|---------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-------|-----------------------------------------------------------------|--|--|

| Param.<br>No.      | Symbol  | Characteristics                                             | Min.                                                                                                                                                                                                                                                                              | Тур. | Max.               | Units | Comments                                                        |  |  |

| D312               | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time | _                                                                                                                                                                                                                                                                                 | _    | 10                 | μs    | See Note 1                                                      |  |  |

| D313               | DACREFH | CVREF Input Voltage                                         | AVss                                                                                                                                                                                                                                                                              | _    | AVDD               | V     | CVRSRC with CVRSS = 0                                           |  |  |

|                    |         | Reference Range                                             | VREF-                                                                                                                                                                                                                                                                             | _    | VREF+              | V     | CVRSRC with CVRSS = 1                                           |  |  |

| D314               | DVREF   | CVREF Programmable<br>Output Range                          | 0                                                                                                                                                                                                                                                                                 | _    | 0.625 x<br>DACREFH | V     | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                 |  |  |

|                    |         |                                                             | 0.25 x<br>DACREFH                                                                                                                                                                                                                                                                 | _    | 0.719 x<br>DACREFH | V     | 0.25 x DACREFH to 0.719<br>DACREFH with<br>DACREFH/32 step size |  |  |

| D315               | DACRES  | Resolution                                                  | —                                                                                                                                                                                                                                                                                 | _    | DACREFH/24         |       | CVRCON <cvrr> = 1</cvrr>                                        |  |  |

|                    |         |                                                             | _                                                                                                                                                                                                                                                                                 | —    | DACREFH/32         | _     | CVRCON <cvrr> = 0</cvrr>                                        |  |  |

| D316               | DACACC  | Absolute Accuracy <sup>(2)</sup>                            |                                                                                                                                                                                                                                                                                   | _    | 1/4                | LSB   | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                         |  |  |

|                    |         |                                                             |                                                                                                                                                                                                                                                                                   | _    | 1/2                | LSB   | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                         |  |  |

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

**2:** These parameters are characterized but not tested.

#### TABLE 30-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |    |  |          | TA $\leq$ +85°C for Industrial                                                                     |

|--------------------|--------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|----------|----------------------------------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                 | Min. Typical Max. Units Comments                                                                                                                                                                                                                                                      |    |  | Comments |                                                                                                    |

| D321               | Cefc   | External Filter Capacitor Value | 8                                                                                                                                                                                                                                                                                     | 10 |  | μF       | Capacitor must be low series<br>resistance (1 ohm). Typical<br>voltage on the VCAP pin is<br>1.8V. |

| TABLE 30-32: | <b>I2Cx BUS DATA</b> | TIMING REQUIREMENTS | (MASTER MODE) | (CONTINUED) |

|--------------|----------------------|---------------------|---------------|-------------|

|              |                      |                     |               |             |

| AC CHARACTERISTICS |         |                  |                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |                                        |

|--------------------|---------|------------------|-------------------------------|-------------------------------------------------------|------|-------|----------------------------------------|

| Param.<br>No.      | Symbol  | Charac           | teristics                     | Min. <sup>(1)</sup>                                   | Max. | Units | Conditions                             |

| IM40               | TAA:SCL | Output Valid     | 100 kHz mode                  | —                                                     | 3500 | ns    | —                                      |

|                    |         | from Clock       | 400 kHz mode                  | —                                                     | 1000 | ns    | —                                      |

|                    |         |                  | 1 MHz mode<br><b>(Note 2)</b> | —                                                     | 350  | ns    | —                                      |

| IM45               | TBF:SDA | Bus Free Time    | 100 kHz mode                  | 4.7                                                   | _    | μS    | The amount of time the                 |

|                    |         |                  | 400 kHz mode                  | 1.3                                                   | —    | μS    | bus must be free                       |

|                    |         |                  | 1 MHz mode<br><b>(Note 2)</b> | 0.5                                                   | —    | μS    | before a new<br>transmission can start |

| IM50               | Св      | Bus Capacitive L | oading                        | —                                                     | 400  | pF    | —                                      |

| IM51               | Tpgd    | Pulse Gobbler D  | elay                          | 52                                                    | 312  | ns    | See Note 3                             |

**Note 1:** BRG is the value of the  $I^2C$  Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

| AC CHARACTERISTICS |         |                                                                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |      |       |            |

|--------------------|---------|----------------------------------------------------------------------|------------------------------------------------------|-------|------|-------|------------|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                       | Min.                                                 | Тур.  | Max. | Units | Conditions |

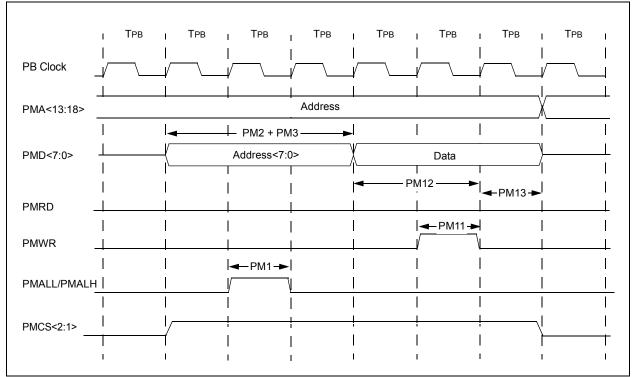

| PM1                | Tlat    | PMALL/PMALH Pulse Width                                              |                                                      | 1 Трв | _    | _     | _          |

| PM2                | TADSU   | Address Out Valid to<br>PMALL/PMALH Invalid (address<br>setup time)  | _                                                    | 2 Трв | _    | _     | _          |

| PM3                | Tadhold | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | —                                                    | 1 Трв | _    | —     | _          |

| PM4                | TAHOLD  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5                                                    | _     | _    | ns    | _          |

| PM5                | Trd     | PMRD Pulse Width                                                     | _                                                    | 1 Трв | _    | _     | —          |

| PM6                | TDSU    | PMRD or PMENB Active to Data<br>In Valid (data setup time)           | 15                                                   | —     | —    | ns    | _          |

| PM7                | TDHOLD  | PMRD or PMENB Inactive to Data In Invalid (data hold time)           | —                                                    | 80    | —    | ns    |            |

#### TABLE 30-38: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

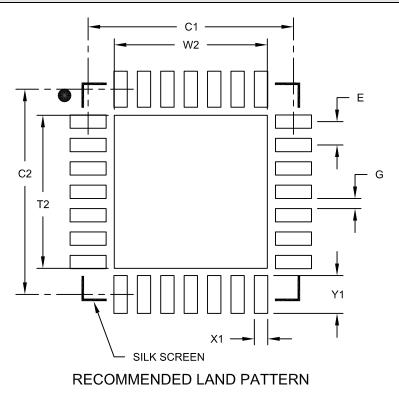

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |                  | MILLIMETERS |          |      |  |

|----------------------------|------------------|-------------|----------|------|--|

| Dimensi                    | Dimension Limits |             | NOM      | MAX  |  |

| Contact Pitch              | Contact Pitch E  |             | 0.65 BSC |      |  |

| Optional Center Pad Width  | W2               |             |          | 4.25 |  |

| Optional Center Pad Length | T2               |             |          | 4.25 |  |

| Contact Pad Spacing        | C1               |             | 5.70     |      |  |

| Contact Pad Spacing        | C2               |             | 5.70     |      |  |

| Contact Pad Width (X28)    | X1               |             |          | 0.37 |  |

| Contact Pad Length (X28)   | Y1               |             |          | 1.00 |  |

| Distance Between Pads      | G                | 0.20        |          |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

## INDEX

| 50 MHz Electrical Characteristics         | 301 |

|-------------------------------------------|-----|

| Α                                         |     |

| AC Characteristics                        | 269 |

| 10-Bit Conversion Rate Parameters         | 291 |

| ADC Specifications                        | 289 |

| Analog-to-Digital Conversion Requirements | 292 |

| EJTAG Timing Requirements                 | 300 |

| Internal FRC Accuracy                     |     |

| Internal RC Accuracy                      | 271 |

| OTG Electrical Specifications             | 298 |

| Parallel Master Port Read Requirements    | 297 |

| Parallel Master Port Write                | 298 |

| Parallel Master Port Write Requirements   | 298 |

| Parallel Slave Port Requirements          | 296 |

| PLL Clock Timing                          | 271 |

| Analog-to-Digital Converter (ADC)         | 209 |

| Assembler                                 |     |

| MPASM Assembler                           | 254 |

## В

| Block Diagrams                                     |  |

|----------------------------------------------------|--|

| ADC Module                                         |  |

| Comparator I/O Operating Modes                     |  |

| Comparator Voltage Reference                       |  |

| Connections for On-Chip Voltage Regulator          |  |

| Core and Peripheral Modules 19                     |  |