Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| /oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f064d-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 6: PIN NAMES FOR 28-PIN USB DEVICES

28-PIN QFN (TOP VIEW)(1,2,3,4)

PIC32MX210F016B PIC32MX220F032B PIC32MX230F064B PIC32MX230F256B PIC32MX250F128B PIC32MX270F256B

28

| Pin # | Full Pin Name                              |

|-------|--------------------------------------------|

| 1     | PGED1/AN2/C1IND/C2INB/C3IND/RPB0/PMD0/RB0  |

| 2     | PGEC1/AN3/C1INC/C2INA/RPB1/CTED12/PMD1/RB1 |

| 3     | AN4/C1INB/C2IND/RPB2/SDA2/CTED13/PMD2/RB2  |

| 4     | AN5/C1INA/C2INC/RTCC/RPB3/SCL2/PMWR/RB3    |

| 5     | Vss                                        |

| 6     | OSC1/CLKI/RPA2/RA2                         |

| 7     | OSC2/CLKO/RPA3/PMA0/RA3                    |

| 8     | SOSCI/RPB4/RB4                             |

| 9     | SOSCO/RPA4/T1CK/CTED9/PMA1/RA4             |

| 10    | VDD                                        |

| 11    | TMS/RPB5/USBID/RB5                         |

| 12    | VBUS                                       |

| 13    | TDI/RPB7/CTED3/PMD5/INT0/RB7               |

| 14    | TCK/RPB8/SCL1/CTED10/PMD4/RB8              |

| Pin# | Full Pin Name                                    |

|------|--------------------------------------------------|

| 15   | TDO/RPB9/SDA1/CTED4/PMD3/RB9                     |

| 16   | Vss                                              |

| 17   | VCAP                                             |

| 18   | PGED2/RPB10/D+/CTED11/RB10                       |

| 19   | PGEC2/RPB11/D-/RB11                              |

| 20   | Vusb3v3                                          |

| 21   | AN11/RPB13/CTPLS/PMRD/RB13                       |

| 22   | CVREFOUT/AN10/C3INB/RPB14/VBUSON/SCK1/CTED5/RB14 |

| 23   | AN9/C3INA/RPB15/SCK2/CTED6/PMCS1/RB15            |

| 24   | AVss                                             |

| 25   | AVDD                                             |

| 26   | MCLR                                             |

| 27   | PGED3/VREF+/CVREF+/AN0/C3INC/RPA0/CTED1/PMD7/RA0 |

| 28   | PGEC3/VREF-/CVREF-/AN1/RPA1/CTED2/PMD6/RA1       |

1

Note 1:

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 11.3 "Peripheral Pin Select" for restrictions.

- 2: Every I/O port pin (RAx-RCx) can be used as a change notification pin (CNAx-CNCx). See Section 11.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- 4: Shaded pins are 5V tolerant.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| IABLE I-I |                   | Pin Nu                            |                   |                                 |             |                |                                                                                           |

|-----------|-------------------|-----------------------------------|-------------------|---------------------------------|-------------|----------------|-------------------------------------------------------------------------------------------|

| Pin Name  | 28-pin<br>QFN     | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA    | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                                               |

| PMA0      | 7                 | 10                                | 8                 | 3                               | I/O         | TTL/ST         | Parallel Master Port Address bit 0 input (Buffered Slave modes) and output (Master modes) |

| PMA1      | 9                 | 12                                | 10                | 2                               | I/O         | TTL/ST         | Parallel Master Port Address bit 1 input (Buffered Slave modes) and output (Master modes) |

| PMA2      |                   | _                                 | _                 | 27                              | 0           | _              | Parallel Master Port address                                                              |

| PMA3      |                   | _                                 | _                 | 38                              | 0           | _              | (Demultiplexed Master modes)                                                              |

| PMA4      |                   | _                                 | _                 | 37                              | 0           | _              |                                                                                           |

| PMA5      |                   | _                                 | _                 | 4                               | 0           | _              | 1                                                                                         |

| PMA6      |                   | _                                 | _                 | 5                               | 0           | _              | 1                                                                                         |

| PMA7      |                   | _                                 |                   | 13                              | 0           | _              | 1                                                                                         |

| PMA8      |                   | _                                 |                   | 32                              | 0           | _              | 1                                                                                         |

| PMA9      |                   | _                                 | _                 | 35                              | 0           | _              | †                                                                                         |

| PMA10     |                   | _                                 | _                 | 12                              | 0           | _              | †                                                                                         |

| PMCS1     | 23                | 26                                | 29                | 15                              | 0           | _              | Parallel Master Port Chip Select 1 strobe                                                 |

| DMD0      | 20 <sup>(2)</sup> | 23 <sup>(2)</sup>                 | 26 <sup>(2)</sup> | 10 <sup>(2)</sup>               | 1/0         | TTL /OT        | Parallel Master Port data (Demultiplexed                                                  |

| PMD0      | 1 <sup>(3)</sup>  | 4 <sup>(3)</sup>                  | 35(3)             | 21 <sup>(3)</sup>               | I/O         | TTL/ST         | Master mode) or address/data                                                              |

| DMD4      | 19 <sup>(2)</sup> | 22(2)                             | 25 <sup>(2)</sup> | 9(2)                            | 1/0         | TTI (OT        | (Multiplexed Master modes)                                                                |

| PMD1      | 2 <sup>(3)</sup>  | 5(3)                              | 36 <sup>(3)</sup> | 22 <sup>(3)</sup>               | I/O         | TTL/ST         |                                                                                           |

| DMDO      | 18 <sup>(2)</sup> | 21 <sup>(2)</sup>                 | 24 <sup>(2)</sup> | 8(2)                            | 1/0         | TTI (OT        |                                                                                           |

| PMD2      | 3(3)              | 6(3)                              | 1(3)              | 23(3)                           | I/O         | TTL/ST         |                                                                                           |

| PMD3      | 15                | 18                                | 19                | 1                               | I/O         | TTL/ST         | †                                                                                         |

| PMD4      | 14                | 17                                | 18                | 44                              | I/O         | TTL/ST         | 1                                                                                         |

| PMD5      | 13                | 16                                | 17                | 43                              | I/O         | TTL/ST         | 1                                                                                         |

| PMD6      | 12 <sup>(2)</sup> | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup> | 42 <sup>(2)</sup>               |             |                | 1                                                                                         |

|           | 28(3)             | <b>3(3)</b>                       | 34(3)             | 20(3)                           | I/O         | TTL/ST         |                                                                                           |

| PMD7      | 11 <sup>(2)</sup> | 14 <sup>(2)</sup>                 | 15 <sup>(2)</sup> | 41 <sup>(2)</sup>               | 1/0         | TTI (0.T       | 1                                                                                         |

|           | 27 <sup>(3)</sup> | 2 <sup>(3)</sup>                  | 33(3)             | 19 <sup>(3)</sup>               | I/O         | TTL/ST         |                                                                                           |

| PMRD      | 21                | 24                                | 27                | 11                              | 0           | _              | Parallel Master Port read strobe                                                          |

|           | 22 <sup>(2)</sup> | 25 <sup>(2)</sup>                 | 28 <sup>(2)</sup> | 14 <sup>(2)</sup>               |             |                |                                                                                           |

| PMWR      | <sub>4</sub> (3)  | 7 <sup>(3)</sup>                  | 2 <sup>(3)</sup>  | 24 <sup>(3)</sup>               | 0           | _              | Parallel Master Port write strobe                                                         |

| VBUS      | 12 <sup>(3)</sup> | 15 <sup>(3)</sup>                 | 16 <sup>(3)</sup> | 42(3)                           | I           | Analog         | USB bus power monitor                                                                     |

| VUSB3V3   | 20 <sup>(3)</sup> | 23 <sup>(3)</sup>                 | 26 <sup>(3)</sup> | 10 <sup>(3)</sup>               | Р           | _              | USB internal transceiver supply. This pin must be connected to VDD.                       |

| VBUSON    | 22 <sup>(3)</sup> | 25 <sup>(3)</sup>                 | 28 <sup>(3)</sup> | 14 <sup>(3)</sup>               | 0           | _              | USB Host and OTG bus power control output                                                 |

| D+        | 18 <sup>(3)</sup> | 21 <sup>(3)</sup>                 | 24 <sup>(3)</sup> | 8(3)                            | I/O         | Analog         | USB D+                                                                                    |

| D-        | 19 <sup>(3)</sup> | 22 <sup>(3)</sup>                 | 25 <sup>(3)</sup> | 9(3)                            | I/O         | Analog         | USB D-                                                                                    |

**Legend:** CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

P = Power

TTL = TTL input buffer

O = Output

I = Input

Note 1: Pin numbers are provided for reference only. See the "Pin Diagrams" section for device pin availability.

PPS = Peripheral Pin Select — = N/A

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

# 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUs

Note:

This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

### 2.1 Basic Connection Requirements

Getting started with the PIC32MX1XX/2XX 28/36/44-pin Family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see 2.5 "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.7 "External Oscillator Pins")

The following pins may be required:

VREF+/VREF- pins – used when external voltage reference for the ADC module is implemented

Note:

The AVDD and AVss pins must be connected, regardless of ADC use and the ADC voltage reference source.

### 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1 µF (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The

decoupling capacitors should be placed as close

to the pins as possible. It is recommended that

the capacitors be placed on the same side of the

board as the device. If space is constricted, the

capacitor can be placed on another layer on the

PCB using a via; however, ensure that the trace

length from the pin to the capacitor is within onequarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01 µF to 0.001 µF. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1 µF in parallel with 0.001 µF.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

NOTES:

### 6.1 Reset Control Registers

### TABLE 6-1: RESET CONTROL REGISTER MAP

| ess                       |                                 | <u> </u>  |       |       |       |       |       |       |      |       | Bits |      |      |      |       |      |      |       | 8          |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|------|-------|------|------|-------|------------|

| Virtual Addrı<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1 | 16/0  | All Resets |

| F600                      | RCON                            | 31:16     | _     | _     |       | _     | _     | _     |      | _     | _    | _    |      |      |       |      | _    | _     | 0000       |

| F600                      | RCON                            | 15:0      |       | _     | _     | _     | _     | _     | CMR  | VREGS | EXTR | SWR  | _    | WDTO | SLEEP | IDLE | BOR  | POR   | XXXX(2)    |

| F640                      | DOWDOT                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _     | _    | _    | _    | _    | _     | _    | _    | _     | 0000       |

| F010                      | F610 RSWRST                     | 15:0      | _     | _     | _     | _     | _     | _     | I    | _     | _    | _    |      | _    | _     | _    | _    | SWRST | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

#### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 |                   | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 | MVEC              | _                 |                   | TPC<2:0>         |                  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 **Unimplemented:** Read as '0' bit 15-13 **Unimplemented:** Read as '0'

bit 12 MVEC: Multi Vector Configuration bit

1 = Interrupt controller configured for Multi-vectored mode

0 = Interrupt controller configured for Single-vectored mode

bit 11 Unimplemented: Read as '0'

bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

001 = Interrupts of group priority 1 start the Interrupt Proximity timer

000 = Disables Interrupt Proximity timer

bit 7-5 **Unimplemented:** Read as '0'

bit 4 **INT4EP:** External Interrupt 4 Edge Polarity Control bit

1 = Rising edge

0 = Falling edge

bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

1 = Rising edge 0 = Falling edge

bit 2

INT2EP: External Interrupt 2 Edge Polarity Control bit

1 = Rising edge0 = Falling edge

bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

1 = Rising edge 0 = Falling edge

bit 0 **INTOEP:** External Interrupt 0 Edge Polarity Control bit

1 = Rising edge 0 = Falling edge

### 8.1 Oscillator Control Regiters

### TABLE 8-1: OSCILLATOR CONTROL REGISTER MAP

| ess                         |                                 |           |             |                |                                                                    |           |       |               |         |                      | Bits    |         |          |                       |        |              |         |      | v)         |

|-----------------------------|---------------------------------|-----------|-------------|----------------|--------------------------------------------------------------------|-----------|-------|---------------|---------|----------------------|---------|---------|----------|-----------------------|--------|--------------|---------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15       | 30/14          | 29/13                                                              | 28/12     | 27/11 | 26/10         | 25/9    | 24/8                 | 23/7    | 22/6    | 21/5     | 20/4                  | 19/3   | 18/2         | 17/1    | 16/0 | All Resets |

| F000                        | OSCCON                          | 31:16     | _           | - PLLODIV<2:0> |                                                                    |           |       | FRCDIV<2:0> — |         |                      |         | SOSCRDY | PBDIVRDY | PBDI\                 | /<1:0> | PLLMULT<2:0> |         |      | x1xx(2)    |

| F000                        | OSCCON                          | 15:0      | _ COSC<2:0> |                |                                                                    | NOSC<2:0> |       |               | CLKLOCK | ULOCK <sup>(3)</sup> | SLOCK   | SLPEN   | CF       | UFRCEN <sup>(3)</sup> | SOSCEN | OSWEN        | xxxx(2) |      |            |

| E010                        | OSCTUN                          | 31:16     | _           |                | _                                                                  | _         | -     | _             | _       | _                    | _       | _       | -        | _                     | _      | _            | _       | _    | 0000       |

| F010                        | OSCIUN                          | 15:0      | _           |                | _                                                                  | _         | -     | _             | _       | _                    | _       | _       |          |                       | TUN    | V<5:0>       |         |      | 0000       |

| <b>-</b>                    | DEEOCON                         | 31:16     | _           |                |                                                                    |           |       |               |         |                      | RODIV<1 | 14:0>   |          |                       |        |              |         |      | 0000       |

| F020                        | REFOCON                         | 15:0      | ON          |                | SIDL   OE   RSLP   —   DIVSWEN ACTIVE   —   —   —   ROSEL<3:0>   0 |           |       |               |         |                      |         |         |          |                       | 0000   |              |         |      |            |

| F000                        | REFOTRIM                        | 31:16     |             | ROTRIM<8:0>    |                                                                    |           |       |               |         |                      |         |         | _        | _                     |        | _            | 0000    |      |            |

| F030                        | KEFUIKIM                        | 15:0      | _           | _              | _                                                                  | _         | 1     | ı             | _       | _                    |         | _       | _        | 1                     | _      | _            | ı       | _    | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

3: This bit is only available on PIC32MX2XX devices.

REGISTER 9-1: DMACON: DMA CONTROLLER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 |                   |                   | _                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | _                 | SUSPEND           | DMABUSY           | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** DMA On bit<sup>(1)</sup>

1 = DMA module is enabled0 = DMA module is disabled

bit 14-13 **Unimplemented:** Read as '0' bit 12 **SUSPEND:** DMA Suspend bit

1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

0 = DMA operates normally

bit 11 DMABUSY: DMA Module Busy bit

1 = DMA module is active

0 = DMA module is disabled and not actively transferring data

bit 10-0 Unimplemented: Read as '0'

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

### REGISTER 10-11: U1CON: USB CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|

| 24.24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 31:24        | _                 | _                 | _                        | _                 | -                     |                       | _                | _                    |

| 22:46        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 23.10        | 23:16             | -                 |                          | _                 | 1                     |                       | _                | _                    |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 15.6         | _                 | _                 | _                        | _                 | -                     |                       | _                | _                    |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |

| 7:0          | JSTATE            | SE0               | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |

|              | JOIAIE            | SEU               | TOKBUSY <sup>(1,5)</sup> | USBRST            | HOSTEN                | RESUME                | FFDRSI           | SOFEN <sup>(5)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

1 = JSTATE was detected on the USB

0 = No JSTATE was detected

bit 6 SE0: Live Single-Ended Zero flag bit

1 = Single-Ended Zero was detected on the USB

0 = No Single-Ended Zero was detected

bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

1 = Token and packet processing is disabled (set upon SETUP token received)

0 = Token and packet processing is enabled

TOKBUSY: Token Busy Indicator bit (1,5)

1 = Token is being executed by the USB module

0 = No token is being executed

bit 4 USBRST: Module Reset bit<sup>(5)</sup>

1 = USB reset generated

0 = USB reset terminated

bit 3 **HOSTEN:** Host Mode Enable bit<sup>(2)</sup>

1 = USB host capability is enabled

0 = USB host capability is disabled

bit 2 **RESUME:** RESUME Signaling Enable bit<sup>(3)</sup>

1 = RESUME signaling is activated

0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

| ▢             |

|---------------|

| DS60001       |

| O             |

| 0             |

| 0             |

| 0             |

| _             |

| $\rightarrow$ |

| 168J-         |

| ω             |

| <u>_</u>      |

| <u> </u>      |

| page          |

| Æ             |

| ×             |

| ťν            |

| _             |

| 135           |

| č             |

| ٠.            |

|               |

|               |

| TABLE 11-5: | PORTC REGISTER MA | 0 |

|-------------|-------------------|---|

| IADLE II-J. | PURIUREGISTER WA  | _ |

| ess                         |                                   |           |       |       |       |       |       |       |          |                       |                         | Bits                    |                         |                       |                      |                         |          |          | 10         |

|-----------------------------|-----------------------------------|-----------|-------|-------|-------|-------|-------|-------|----------|-----------------------|-------------------------|-------------------------|-------------------------|-----------------------|----------------------|-------------------------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1,2)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9     | 24/8                  | 23/7                    | 22/6                    | 21/5                    | 20/4                  | 19/3                 | 18/2                    | 17/1     | 16/0     | All Resets |

| 6200                        | ANSELC                            | 31:16     | ı     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | ı        | ı        | 0000       |

| 0200                        | ANSELC                            | 15:0      | -     | _     | _     | _     | _     | _     | _        | -                     | _                       | _                       | _                       | _                     | ANSC3 <sup>(4)</sup> | ANSC2 <sup>(3)</sup>    | ANSC1    | ANSC0    | 000F       |

| 6210                        | TRISC                             | 31:16     | _     | _     | _     | _     | _     | _     | _        |                       | _                       | _                       | _                       |                       | _                    | _                       | _        | _        | 0000       |

| 0210                        | TRISC                             | 15:0      | I     | _     | _     | _     | _     |       | TRISC9   | TRISC8 <sup>(3)</sup> | TRISC7 <sup>(3)</sup>   | TRISC6 <sup>(3)</sup>   | TRISC5 <sup>(3)</sup>   | TRISC4 <sup>(3)</sup> | TRISC3               | TRISC2 <sup>(3)</sup>   | TRISC1   | TRISC0   | 03FF       |

| 6220                        | PORTC                             | 31:16     | I     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       |                       |                      |                         |          |          | 0000       |

| 0220                        | PORTC                             | 15:0      | I     | _     | _     | _     | _     | _     | RC9      | RC8 <sup>(3)</sup>    | RC7 <sup>(3)</sup>      | RC6 <sup>(3)</sup>      | RC5 <sup>(3)</sup>      | RC4 <sup>(3)</sup>    | RC3                  | RC2 <sup>(3)</sup>      | RC1      | RC0      | xxxx       |

| 6230                        | LATC                              | 31:16     | I     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | -        | -        | 0000       |

| 0230                        | LKI                               | 15:0      | I     | _     | _     | _     | _     | _     | LATC9    | LATC8 <sup>(3)</sup>  | LATC7 <sup>(3)</sup>    | LATC6 <sup>(3)</sup>    | LATC5 <sup>(3)</sup>    | LATC4 <sup>(3)</sup>  | LATC3                | LATC2 <sup>(3)</sup>    | LATC1    | LATC0    | xxxx       |

| 6240                        | ODCC                              | 31:16     | I     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | -        | -        | 0000       |

| 0240                        | ODCC                              | 15:0      | _     | _     | _     | _     | _     | _     | ODCC9    | ODCC8 <sup>(3)</sup>  | ODCC7 <sup>(3)</sup>    | ODCC6 <sup>(3)</sup>    | ODCC5 <sup>(3)</sup>    | ODCC4 <sup>(3)</sup>  | ODCC3                | ODCC2 <sup>(3)</sup>    | ODCC1    | ODCC0    | 0000       |

| 6250                        | CNPUC                             | 31:16     | I     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | -        | -        | 0000       |

| 0250                        | CNPUC                             | 15:0      | I     | _     | _     | _     | _     | _     | CNPUC9   | CNPUC8 <sup>(3)</sup> | CNPUC7 <sup>(3)</sup>   | CNPUC6 <sup>(3)</sup>   | CNPUC5 <sup>(3)</sup>   | CNPUC4 <sup>(3)</sup> | CNPUC3               | CNPUC2 <sup>(3)</sup>   | CNPUC1   | CNPUC0   | 0000       |

| 0000                        | CNIDDO                            | 31:16     | _     | _     | _     | _     | _     | _     | _        | _                     | _                       | _                       | _                       | _                     | _                    | _                       | _        | _        | 0000       |

| 6260                        | CNPDC                             | 15:0      | _     | _     | _     | _     | _     | _     | CNPDC9   | CNPDC8 <sup>(3)</sup> | CNPDC7 <sup>(3)</sup>   | CNPDC6 <sup>(3)</sup>   | CNPDC5 <sup>(3)</sup>   | CNPDC4 <sup>(3)</sup> | CNPDC3               | CNPDC2 <sup>(3)</sup>   | CNPDC1   | CNPDC0   | 0000       |

| 6070                        | CNICONIC                          | 31:16     | I     | _     | _     | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | -        | -        | 0000       |

| 0270                        | CNCONC                            | 15:0      | ON    | _     | SIDL  | _     | _     | _     | _        | 1                     | _                       | _                       | _                       | 1                     | _                    | _                       | -        | -        | 0000       |

| 6200                        | CNENC                             | 31:16     | I     | _     | _     | _     | _     | _     | _        |                       | _                       | _                       | _                       |                       | _                    | _                       | _        |          | 0000       |

| 6280                        | CNENC                             | 15:0      | I     | _     | _     | _     | _     | _     | CNIEC9   | CNIEC8 <sup>(3)</sup> | CNIEC7 <sup>(3)</sup>   | CNIEC6(3)               | CNIEC5 <sup>(3)</sup>   | CNIEC4 <sup>(3)</sup> | CNIEC3               | CNIEC2 <sup>(3)</sup>   | CNIEC1   | CNIEC0   | 0000       |

| 6200                        | CNICTATO                          | 31:16     | I     | _     | _     | _     | _     | _     | _        |                       | _                       |                         | _                       |                       | _                    | _                       | _        |          | 0000       |

| 0290                        | CNSTATC                           | 15:0      |       | _     | _     | _     | _     | _     | CNSTATC9 | CNSTATC8(3)           | CNSTATC7 <sup>(3)</sup> | CNSTATC6 <sup>(3)</sup> | CNSTATC5 <sup>(3)</sup> | CNSTATC4(3)           | CNSTATC3             | CNSTATC2 <sup>(3)</sup> | CNSTATC1 | CNSTATCO | 0000       |

${f x}$  = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for

- PORTC is not available on 28-pin devices. 2:

- This bit is only available on 44-pin devices.

- This bit is only available on USB-enabled devices with 36 or 44 pins.

| $\Box$ |

|--------|

| Ś      |

| 8      |

| 3000   |

| 0      |

| 0      |

| _      |

| _      |

| 0      |

| 89     |

| ے      |

|        |

| page   |

| ~      |

| ∺      |

| v      |

| _      |

| w      |

| 139    |

| _      |

|        |

|        |

| TABLE 11-7: | PERIPHERAL PIN SELECT OUTPUT REGISTER MAP | (CONTINUED) |

|-------------|-------------------------------------------|-------------|

|             |                                           |             |

| SS                          |                      |               |       |       |       |       |       |       |      | Ві   | its  |      |      |      |      |           |               |      |            |

|-----------------------------|----------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-----------|---------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2      | 17/1          | 16/0 | All Resets |

| FB4C                        | RPB8R                | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _         | _             | _    | 0000       |

| 1 540                       | THE DOTA             | 15:0          |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB8      | 3<3:0>        |      | 0000       |

| FB50                        | RPB9R                | 31:16         |       | _     | _     |       |       | _     | _    | _    |      | _    | _    | _    | _    | _         | _             | _    | 0000       |

| . 500                       | THE BOTT             | 15:0          |       | _     | _     |       |       | _     | _    | _    |      | _    | _    | _    |      | RPB9      | )<3:0>        |      | 0000       |

| FB54                        | RPB10R               | 31:16         |       | _     | _     |       |       | _     | _    | _    |      | _    | _    | _    | _    | _         | _             |      | 0000       |

| . 50.                       |                      | 15:0          |       | _     | _     |       |       | _     | _    | _    |      | _    | _    | _    |      | RPB10     | 0<3:0>        |      | 0000       |

| FB58                        | RPB11R               | 31:16         |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |           | _             | _    | 0000       |

|                             |                      | 15:0          |       | _     | _     | _     | _     | _     | _    |      | _    | _    | _    | _    |      | RPB1      | 1<3:0>        |      | 0000       |

| FB60                        | RPB13R               | 31:16         |       | _     | _     | _     | _     | _     | _    |      |      | _    | _    | _    | _    | _         |               |      | 0000       |

|                             |                      | 15:0          |       | _     | _     | _     | _     | _     | _    |      |      | _    | _    | _    |      | RPB1      |               |      | 0000       |

| FB64                        | RPB14R               | 31:16         |       | _     | _     |       |       | _     | _    |      |      | _    | _    | _    | _    |           |               |      | 0000       |

|                             |                      | 15:0          |       | _     | _     |       |       | _     | _    | _    |      | _    | _    | _    |      | RPB1      | 4<3:0>        |      | 0000       |

| FB68                        | RPB15R               | 31:16         |       |       | _     |       |       |       | _    | _    |      |      |      |      | _    |           | -             | _    | 0000       |

|                             |                      | 15:0          |       |       | _     |       |       |       | _    | _    |      |      |      |      |      | RPB1      |               |      | 0000       |

| FB6C                        | RPC0R(3)             | 31:16         |       |       | _     |       | _     |       | _    | _    |      |      |      | _    | _    | RPC0      | -             |      | 0000       |

|                             |                      | 15:0          |       |       | _     |       | _     |       | _    | _    |      |      |      | _    |      |           |               |      | 0000       |

| FB70                        | RPC1R <sup>(3)</sup> | 31:16         |       | _     | _     |       | _     |       |      |      |      | _    |      |      | _    |           | <3:0>         | _    | 0000       |

|                             |                      | 15:0<br>31:16 |       |       |       |       | _     |       |      |      |      | _    |      |      |      |           | 3.0>          | _    | 0000       |

| FB74                        | RPC2R <sup>(1)</sup> | 15:0          |       |       |       |       | _     |       |      |      |      | _    |      |      | _    | —<br>BDC2 | 2<3:0>        |      | 0000       |

|                             |                      |               |       | _     | _     | _     | _     | _     | _    |      | _    | _    | _    | _    |      |           |               |      | 0000       |

| FB78                        | RPC3R(3)             | 31:16<br>15:0 |       | _     | _     |       |       | _     | _    |      | _    |      | _    | _    | _    | —<br>DDC3 | S<3:0>        | _    | 0000       |

|                             |                      | 31:16         |       | _     | _     |       |       |       |      | _    |      |      |      | _    | _    | — KF03    | _             | _    | 0000       |

| FB7C                        | RPC4R <sup>(1)</sup> | 15:0          |       | _     |       |       |       |       |      |      | _    |      |      |      | _    | RPC4      |               |      | 0000       |

|                             |                      | 31:16         |       | _     |       |       |       |       |      |      | _    |      |      | _    | _    | KF 04     |               | _    | 0000       |

| FB80                        | RPC5R <sup>(1)</sup> | 15:0          |       |       |       |       |       |       | _    |      |      | _    |      | _    |      |           | 5<3:0>        |      | 0000       |

|                             |                      | 31:16         |       | _     |       |       |       |       |      |      | _    |      |      | _    | _    | — KF03    | _             | _    | 0000       |

| FB84                        | RPC6R <sup>(1)</sup> | 15:0          |       | _     | _     |       |       | _     |      |      | _    |      | _    | _    | _    | RPC6      |               |      | 0000       |

|                             |                      | 31:16         |       | _     | _     |       |       | _     |      |      | _    |      | _    | _    | _    | — KF00    | _             | _    | 0000       |

| FB88                        | RPC7R <sup>(1)</sup> | 15:0          |       |       |       |       |       |       |      |      |      |      |      |      | _    | RPC7      |               |      | 0000       |

|                             |                      | 15.0          |       |       | _     | _     |       | _     | _    | _    |      | _    | _    | _    |      | RPU/      | <b>~</b> 3.0≥ |      | 0000       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register is only available on 44-pin devices. Note 1:

This register is only available on PIG32MX1XX devices. This register is only available on 36-pin and 44-pin devices.

### 12.2 Timer1 Control Registers

### TABLE 12-1: TIMER1 REGISTER MAP

|                             |                                 |           |               | 112010 |       |       |       |       |      |      |       |      |       |        |      |       |      |      |            |

|-----------------------------|---------------------------------|-----------|---------------|--------|-------|-------|-------|-------|------|------|-------|------|-------|--------|------|-------|------|------|------------|

| ess                         |                                 | Bits      |               |        |       |       |       |       |      |      |       |      |       |        |      |       |      |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14  | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6 | 21/5  | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Resets |

| 0600                        | T1CON                           | 31:16     | _             | _      | _     | _     | _     | _     | _    | _    | _     | _    | _     | _      | _    | _     | _    | _    | 0000       |

| 0600                        | LICON                           | 15:0      | ON            | _      | SIDL  | TWDIS | TWIP  | _     | _    | _    | TGATE | _    | TCKPS | S<1:0> | _    | TSYNC | TCS  | _    | 0000       |

| 0610                        | TMR1                            | 31:16     |               | _      | _     | _     | _     | _     | _    | _    | _     | _    | _     | _      | _    | _     | _    | _    | 0000       |

| 0010                        | TIVITY                          | 15:0      | TMR1<15:0> 00 |        |       |       |       |       |      |      |       | 0000 |       |        |      |       |      |      |            |

| 0620                        | PR1                             | 31:16     | _             |        | _     | _     | _     | _     | _    | -    | _     | _    | _     | _      | _    | _     | _    | _    | 0000       |

| 0020                        | 1 101                           | 15:0      |               |        |       |       |       |       |      | PR1< | 15:0> |      |       |        |      |       |      |      | FFFF       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

#### REGISTER 20-1: PMCON: PARALLEL PORT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6   | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------|--------------------|-------------------|---------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0                 | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                   | _                  | -                 | _                   |                   | _                | _                |

| 22.46        | U-0               | U-0                 | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                   | _                  | _                 | _                   | _                 | _                | _                |

| 45.0         | R/W-0             | U-0                 | R/W-0              | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | _                   | SIDL               | ADRMUX<1:0>       |                     | PMPTTL            | PTWREN           | PTRDEN           |

| 7.0          | R/W-0             | R/W-0               | R/W-0              | U-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<              | 1:0> <sup>(2)</sup> | ALP <sup>(2)</sup> | _                 | CS1P <sup>(2)</sup> | _                 | WRSP             | RDSP             |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

1 = PMP enabled

0 = PMP disabled, no off-chip access performed

bit 14 **Unimplemented:** Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when the device enters Idle mode

0 = Continue module operation when the device enters Idle mode

bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

11 = Lower 8 bits of address are multiplexed on PMD<7:0> pins; upper 8 bits are not used

10 = All 16 bits of address are multiplexed on PMD<7:0> pins

01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<10:8> and PMA<14>

00 = Address and data appear on separate pins

bit 10 PMPTTL: PMP Module TTL Input Buffer Select bit

1 = PMP module uses TTL input buffers

0 = PMP module uses Schmitt Trigger input buffer

bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

1 = PMWR/PMENB port enabled

0 = PMWR/PMENB port disabled

bit 8 PTRDEN: Read/Write Strobe Port Enable bit

1 = PMRD/PMWR port enabled

0 = PMRD/PMWR port disabled

bit 7-6 CSF<1:0>: Chip Select Function bits(2)

11 = Reserved

10 = PMCS1 functions as Chip Select

01 = PMCS1 functions as PMA<14>

00 = PMCS1 functions as PMA<14>

bit 5 ALP: Address Latch Polarity bit<sup>(2)</sup>

1 = Active-high (PMALL and PMALH)

0 = Active-low (PMALL and PMALH)

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

These bits have no effect when their corresponding pins are used as address lines.

### REGISTER 21-5: ALRMTIME: ALARM TIME VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        |                   | _                 | HR10              | <1:0>             | HR01<3:0>         |                   |                  |                  |  |  |

| 22.46        | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        | _                 |                   | MIN10<2:0>        |                   | MIN01<3:0>        |                   |                  |                  |  |  |

| 45.0         | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         | _                 |                   | SEC10<2:0>        |                   | SEC01<3:0>        |                   |                  |                  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary Coded Decimal value of hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9

bit 23 Unimplemented: Read as '0'

bit 22-20 MIN10<2:0>: Binary Coded Decimal value of minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9

bit 15 Unimplemented: Read as '0'

bit 14-12 SEC10<2:0>: Binary Coded Decimal value of seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

### REGISTER 27-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

- bit 15-14 FCKSM<1:0>: Clock Switching and Monitor Selection Configuration bits

- 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

- 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

- 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

- bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output disabled

- 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

- bit 9-8 POSCMOD<1:0>: Primary Oscillator Configuration bits

- 11 = Primary Oscillator is disabled

- 10 = HS Oscillator mode is selected

- 01 = XT Oscillator mode is selected

- 00 = External Clock mode is selected

- bit 7 **IESO:** Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 Reserved: Write '1'

- bit 5 FSOSCEN: Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 **Reserved:** Write '1'

- bit 2-0 FNOSC<2:0>: Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT. HS. EC)(1)

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

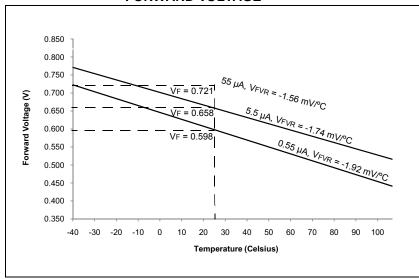

TABLE 30-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

| DC CHA        | ARACTER | RISTICS                                                 | stated)         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) $ -40^{\circ}C \leq TA \leq +85^{\circ}C \text{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \text{ for V-temp} $ |            |       |                                                   |  |  |  |  |

|---------------|---------|---------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|---------------------------------------------------|--|--|--|--|

| Param.<br>No. | Symbol  | Characteristics                                         | Min.            | Typical <sup>(1)</sup>                                                                                                                                                                                | Max.       | Units | Conditions                                        |  |  |  |  |

|               | VIL     | Input Low Voltage                                       |                 |                                                                                                                                                                                                       |            |       |                                                   |  |  |  |  |

| DI10          |         | I/O Pins with PMP                                       | Vss             | _                                                                                                                                                                                                     | 0.15 VDD   | V     |                                                   |  |  |  |  |

|               |         | I/O Pins                                                | Vss             | _                                                                                                                                                                                                     | 0.2 VDD    | V     |                                                   |  |  |  |  |

| DI18          |         | SDAx, SCLx                                              | Vss             | _                                                                                                                                                                                                     | 0.3 VDD    | V     | SMBus disabled (Note 4)                           |  |  |  |  |

| DI19          |         | SDAx, SCLx                                              | Vss             | _                                                                                                                                                                                                     | 0.8        | V     | SMBus enabled (Note 4)                            |  |  |  |  |

|               | VIH     | Input High Voltage                                      |                 |                                                                                                                                                                                                       |            |       |                                                   |  |  |  |  |

| DI20          |         | I/O Pins not 5V-tolerant <sup>(5)</sup>                 | 0.65 VDD        | _                                                                                                                                                                                                     | VDD        | V     | (Note 4,6)                                        |  |  |  |  |

|               |         | I/O Pins 5V-tolerant with PMP <sup>(5)</sup>            | 0.25 VDD + 0.8V | _                                                                                                                                                                                                     | 5.5        | V     | (Note 4,6)                                        |  |  |  |  |

|               |         | I/O Pins 5V-tolerant(5)                                 | 0.65 VDD        | _                                                                                                                                                                                                     | 5.5        | V     |                                                   |  |  |  |  |

| DI28          |         | SDAx, SCLx                                              | 0.65 VDD        | _                                                                                                                                                                                                     | 5.5        | V     | SMBus disabled (Note 4,6)                         |  |  |  |  |

| DI29          |         | SDAx, SCLx                                              | 2.1             | _                                                                                                                                                                                                     | 5.5        | V     | SMBus enabled, $2.3V \le VPIN \le 5.5$ (Note 4,6) |  |  |  |  |

| DI30          | ICNPU   | Change Notification Pull-up Current                     | _               | _                                                                                                                                                                                                     | -50        | μА    | VDD = 3.3V, VPIN = VSS (Note 3,6)                 |  |  |  |  |

| DI31          | ICNPD   | Change Notification<br>Pull-down Current <sup>(4)</sup> | _               | _                                                                                                                                                                                                     | -50        | μA    | VDD = 3.3V, VPIN = VDD                            |  |  |  |  |

|               | liL     | Input Leakage Current (Note 3)                          |                 |                                                                                                                                                                                                       |            |       |                                                   |  |  |  |  |

| DI50          |         | I/O Ports                                               | _               | _                                                                                                                                                                                                     | <u>+</u> 1 | μΑ    | Vss ≤ Vpin ≤ Vdd,<br>Pin at high-impedance        |  |  |  |  |

| DI51          |         | Analog Input Pins                                       | _               | _                                                                                                                                                                                                     | <u>+</u> 1 | μΑ    | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance        |  |  |  |  |

| DI55          |         | MCLR <sup>(2)</sup>                                     | _               | _                                                                                                                                                                                                     | <u>+</u> 1 | μΑ    | Vss ≤ Vpin ≤ Vdd                                  |  |  |  |  |

| DI56          |         | OSC1                                                    | _               | _                                                                                                                                                                                                     | <u>+</u> 1 | μA    | VSS ≤ VPIN ≤ VDD,<br>XT and HS modes              |  |  |  |  |

- **Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- **4:** This parameter is characterized, but not tested in manufacturing.

- 5: See the "Pin Diagrams" section for the 5V-tolerant pins.

- **6:** The Vih specifications are only in relation to externally applied inputs, and not with respect to the user-selectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum Vih of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

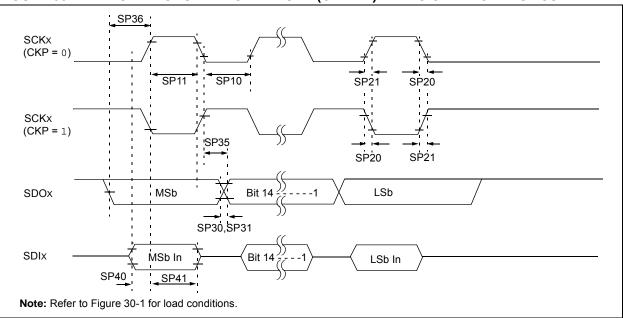

FIGURE 30-11: SPIX MODULE MASTER MODE (CKE = 1) TIMING CHARACTERISTICS

TABLE 30-29: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        | ARACTERIS <sup>*</sup> | rics                                      | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{TA} \leq +105^{\circ}\text{C}$ for V-temp |                     |      |       |                    |  |  |  |

|---------------|------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|--|--|

| Param.<br>No. | Symbol                 | Characteristics <sup>(1)</sup>            | Min.                                                                                                                                                                                                                                               | Typ. <sup>(2)</sup> | Max. | Units | Conditions         |  |  |  |

| SP10          | TscL                   | SCKx Output Low Time (Note 3)             | Tsck/2                                                                                                                                                                                                                                             | _                   | _    | ns    | _                  |  |  |  |

| SP11          | TscH                   | SCKx Output High Time (Note 3)            | Tsck/2                                                                                                                                                                                                                                             | _                   | _    | ns    | _                  |  |  |  |

| SP20          | TscF                   | SCKx Output Fall Time (Note 4)            | _                                                                                                                                                                                                                                                  | _                   | _    | ns    | See parameter DO32 |  |  |  |

| SP21          | TscR                   | SCKx Output Rise Time (Note 4)            | _                                                                                                                                                                                                                                                  | _                   | _    | ns    | See parameter DO31 |  |  |  |

| SP30          | TDOF                   | SDOx Data Output Fall Time (Note 4)       | _                                                                                                                                                                                                                                                  | _                   | _    | ns    | See parameter DO32 |  |  |  |

| SP31          | TDOR                   | SDOx Data Output Rise Time (Note 4)       | _                                                                                                                                                                                                                                                  | _                   | _    | ns    | See parameter DO31 |  |  |  |

| SP35          | TscH2DoV,              | SDOx Data Output Valid after              |                                                                                                                                                                                                                                                    | _                   | 15   | ns    | VDD > 2.7V         |  |  |  |

|               | TscL2DoV               | SCKx Edge                                 | _                                                                                                                                                                                                                                                  | _                   | 20   | ns    | VDD < 2.7V         |  |  |  |