Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 40MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16К х 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

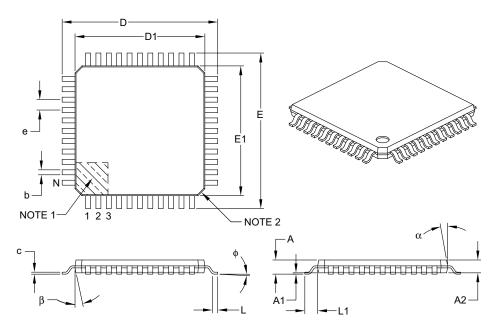

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f064d-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | —                 | —                 | —                 |                   | IP03<2:0>         |                   |                  | IS03<1:0>        |  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10        | _                 | —                 |                   |                   | IP02<2:0>         |                   | IS02<1:0>        |                  |  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.0         | _                 | —                 |                   |                   | IP01<2:0>         |                   | IS01<1:0>        |                  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0          | _                 | _                 | _                 |                   | IP00<2:0>         |                   | IS00·            | <1:0>            |  |

#### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

#### Legend:

| Logonal           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-26 IP03<2:0>: Interrupt Priority bits

- 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 25-24 IS03<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 bit 23-21 Unimplemented: Read as '0' bit 20-18 IP02<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1 000 = Interrupt is disabled bit 17-16 IS02<1:0>: Interrupt Subpriority bits 11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0 bit 15-13 Unimplemented: Read as '0' bit 12-10 IP01<2:0>: Interrupt Priority bits 111 = Interrupt priority is 7 010 = Interrupt priority is 2 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

- **Note:** This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                       | —                 | —                 |                   | _                | —                |

| 23:16        | U-0               | R-0               | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                       | —                 | —                 | _                 | —                | —                |

| 45.0         | U-0               | R-0               | U-0                     | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                       | —                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | —                 | _                 | TUN<5:0> <sup>(1)</sup> |                   |                   |                   |                  |                  |

#### REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

# Legend:

| Logona.                           |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized, nor tested.

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | _                 | —                 | —                 | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

#### **REGISTER 9-9:** DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER

# Legend:

| •                 |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| bit 31-24  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| bit 23     | CHSDIE: Channel Source Done Interrupt Enable bit<br>1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| bit 22     | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| DIL 22     | CHSHIE: Channel Source Half Empty Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| bit 21     | <b>CHDDIE:</b> Channel Destination Done Interrupt Enable bit<br>1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|            | 0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| bit 20     | CHDHIE: Channel Destination Half Full Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| bit 19     | <b>CHBCIE:</b> Channel Block Transfer Complete Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| bit 18     | CHCCIE: Channel Cell Transfer Complete Interrupt Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|            | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| bit 17     | CHTAIE: Channel Transfer Abort Interrupt Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|            | <ul><li>1 = Interrupt is enabled</li><li>0 = Interrupt is disabled</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| bit 16     | CHERIE: Channel Address Error Interrupt Enable bit<br>1 = Interrupt is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| bit 15-8   | 0 = Interrupt is disabled<br>Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| bit 7      | CHSDIF: Channel Source Done Interrupt Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|            | <ul> <li>1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)</li> <li>0 = No interrupt is pending</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| bit 6      | <b>CHSHIF:</b> Channel Source Half Empty Interrupt Flag bit<br>1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2)<br>0 = No interrupt is pending                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | )   |

| bit 5      | <b>CHDDIF:</b> Channel Destination Done Interrupt Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|            | <ul> <li>1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSI</li> <li>0 = No interrupt is pending</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IZ) |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| © 2011-201 | 16 Microchip Technology Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DS  |

| 2 2011 20  | is more any restricted from the second s | 20  |

DS60001168J-page 95

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

#### REGISTER 10-3: U1OTGSTAT: USB OTG STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24        | -                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | —                 | —                 | —                 | _                 | —                 |                  | —                |

| 7:0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |

|              | ID                |                   | LSTATE            | _                 | SESVD             | SESEND            | _                | VBUSVD           |

### Legend:

| Logona.                           |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a "type B" cable has been inserted into the USB receptacle

- 0 = A "type A" OTG cable has been inserted into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (SE0 (U1CON<6>) bit and JSTATE (U1CON<7>)) bit has been stable for previous 1 ms 0 = USB line state (SE0 and JSTATE) has not been stable for previous 1 ms

#### bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A or B device

- 0 = VBUS voltage is below Session Valid on the A or B device

- bit 2 SESEND: B-Device Session End Indicator bit

- 1 = VBUS voltage is below Session Valid on the B device

- 0 = VBUS voltage is above Session Valid on the B device

#### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A device

- 0 = VBUS voltage is below Session Valid on the A device

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.0         | —                 | —                 | -                 | —                 | —                 | —                 | —                | —                |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |

| 7:0          | —                 | —                 | _                 | —                 | —                 |                   | FRMH<2:0>        |                  |  |

#### REGISTER 10-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

# Legend:

| 0                 |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** The Upper 3 bits of the Frame Numbers bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

#### Bit Bit Bit Bit Bit Bit Bit Bit Bit 30/22/14/6 27/19/11/3 26/18/10/2 25/17/9/1 24/16/8/0 Range 31/23/15/7 29/21/13/5 28/20/12/4 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 31:24 \_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 23:16 \_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 15:8 \_ \_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_ \_\_\_\_ \_\_\_\_ R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 7:0 PID < 3:0 > (1)EP<3:0>

# **REGISTER 10-15: U1TOK: USB TOKEN REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-4 **PID<3:0>:** Token Type Indicator bits<sup>(1)</sup>

1101 = SETUP (TX) token type transaction

- 1001 = IN (RX) token type transaction

- 0001 = OUT (TX) token type transaction

Note: All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

Note 1: All other values are reserved and must not be used.

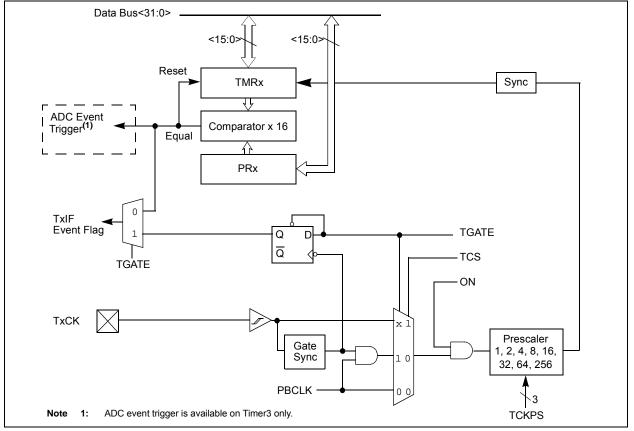

# 13.0 TIMER2/3, TIMER4/5

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features four synchronous 16-bit timers (default) that can operate as a freerunning interval timer for various timing applications and counting external events. The following modes are supported:

- Synchronous internal 16-bit timer

- Synchronous internal 16-bit gated timer

- · Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- Synchronous internal 32-bit timer

- · Synchronous internal 32-bit gated timer

- Synchronous external 32-bit timer

| Note: | In this chapter, references to registers, |

|-------|-------------------------------------------|

|       | TxCON, TMRx and PRx, use 'x' to           |

|       | represent Timer2 through Timer5 in 16-bit |

|       | modes. In 32-bit modes, 'x' represents    |

|       | Timer2 or Timer4 and 'y' represents       |

|       | Timer3 or Timer5.                         |

# **13.1 Additional Supported Features**

- · Selectable clock prescaler

- Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/3 in 32-bit mode)

- Fast bit manipulation using CLR, SET and INV registers

Figure 13-1 and Figure 13-2 illustrate block diagrams of Timer2/3 and Timer4/5.

# FIGURE 13-1: TIMER2-TIMER5 BLOCK DIAGRAM (16-BIT)

# 16.1 Output Compare Control Registers

# TABLE 16-1: OUTPUT COMPARE 1-OUTPUT COMPARE 5 REGISTER MAP

| ess                         |                                 |                   |       |       |       |       |       |       |      | В     | its      |      |      |       |        |      |          |      |              |

|-----------------------------|---------------------------------|-------------------|-------|-------|-------|-------|-------|-------|------|-------|----------|------|------|-------|--------|------|----------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range         | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7     | 22/6 | 21/5 | 20/4  | 19/3   | 18/2 | 17/1     | 16/0 | All Resets   |

|                             | OC1CON                          | 31:16             | —     | —     | —     | —     | —     | —     | —    | _     | —        | —    | —    | —     | —      |      | —        | _    | 0000         |

| 0000                        | 001001                          | 15:0              | ON    | —     | SIDL  | —     | —     | —     |      | —     | —        | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3010                        | OC1R                            | 31:16<br>15:0     |       |       |       |       |       |       |      | OC1R  | <31:0>   |      |      |       |        |      |          |      | xxxx         |

| 3020                        | OC1RS                           | 31:16<br>15:0     |       |       |       |       |       |       |      | OC1RS | \$<31:0> |      |      |       |        |      |          |      | xxxx         |

| 0000                        | 00000                           | 31:16             | —     | _     | _     | _     | _     | _     |      | _     | —        | —    | _    | —     | _      | _    | —        | —    | 0000         |

| 3200                        | OC2CON                          | 15:0              | ON    | _     | SIDL  | _     | _     | _     | _    | _     | _        | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3210                        | OC2R                            | 31:16             |       |       |       |       |       |       |      | OC2R  | ~21.0>   |      |      |       |        |      |          |      | xxxx         |

| 3210                        | UCZR                            | 15:0              |       |       |       |       |       |       |      | UCZR  | <31.0>   |      |      |       |        |      |          |      | xxxx         |

| 3220                        | OC2RS                           | 31:16             |       |       |       |       |       |       |      | OC2RS | 2-31-05  |      |      |       |        |      |          |      | XXXX         |

| 3220                        | 00283                           | 15:0              |       |       |       |       |       |       |      | UCZRO | 5<31.02  |      |      |       |        |      |          |      | XXXX         |

| 3400                        | OC3CON                          | 31:16             | _     | _     | _     | _     | _     | _     | _    | _     | _        | _    | _    | _     | _      |      | —        |      | 0000         |

| 3400                        | 003001                          | 15:0              | ON    | _     | SIDL  | _     | _     | _     | _    | _     | -        | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3410                        | OC3R                            | 31:16<br>15:0     |       |       |       |       |       |       |      | OC3R  | <31:0>   |      |      |       |        |      |          |      | XXXX<br>XXXX |

| 3420                        | OC3RS                           | 31:16             |       |       |       |       |       |       |      | OC3R8 | 221.05   |      |      |       |        |      |          |      | XXXX         |

| 3420                        | 00383                           | 15:0              |       |       |       |       |       |       |      | UCSRC | 5-51.0-  |      |      |       |        |      |          |      | XXXX         |

| 3600                        | OC4CON                          | 31:16             | —     | _     | _     | _     | _     | _     | _    | _     | —        | _    | _    | —     | —      | _    | —        | _    | 0000         |

| 3000                        | 004001                          | 15:0              | ON    | _     | SIDL  | _     | _     | _     | _    | _     | -        | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3610                        | OC4R                            | 31:16             |       |       |       |       |       |       |      | OC4R  | <31.0>   |      |      |       |        |      |          |      | xxxx         |

| 3010                        | 0041                            | 15:0              |       |       |       |       |       |       |      | 0041  | -01.02   |      |      |       |        |      |          |      | xxxx         |

| 3620                        | OC4RS                           | 31:16             |       |       |       |       |       |       |      | OC4RS | 221.05   |      |      |       |        |      |          |      | xxxx         |

| 3020                        | 00410                           | 15:0              |       |       |       |       |       |       |      | 00400 | 0<01.02  |      |      |       |        |      |          |      | xxxx         |

| 3800                        | OC5CON                          | 31:16             | -     | _     | —     | _     | _     | _     | _    | _     | -        | _    | —    | —     | —      |      | —        |      | 0000         |

| 3000                        | 000000                          | 15:0              | ON    | —     | SIDL  | —     | —     | —     | —    | —     | —        | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000         |

| 3810                        | OC5R                            | 31:16             |       |       |       |       |       |       |      | OC5R  | <31.0>   |      |      |       |        |      |          |      | XXXX         |

| 3010                        | 0000                            | 15:0              |       |       |       |       |       |       |      | OUJK  | -01.02   |      |      |       |        |      |          |      | xxxx         |

| 3820                        | OC5RS                           | 31:16             |       |       |       |       |       |       |      | OC5RS |          |      |      |       |        |      |          |      | XXXX         |

| 3020                        | 00010                           | 15 <sup>.</sup> 0 |       |       |       |       |       |       |      | 00000 | -01.02   |      |      |       |        |      |          |      | xxxx         |

PIC32MX1XX/2XX 28/36/44-PIN FAMILY

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

# PIC32MX1XX/2XX 28/36/44-PIN FAMILY

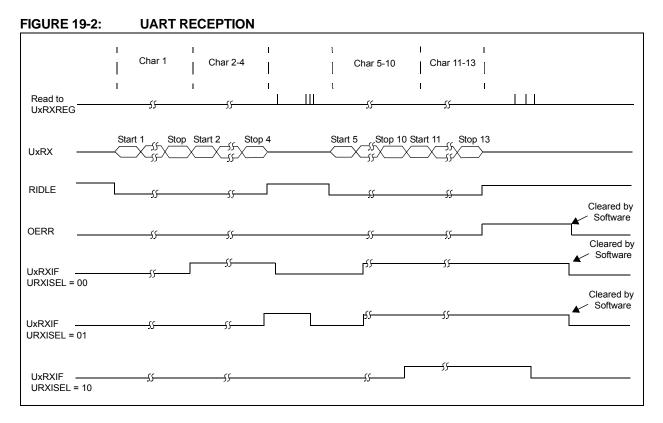

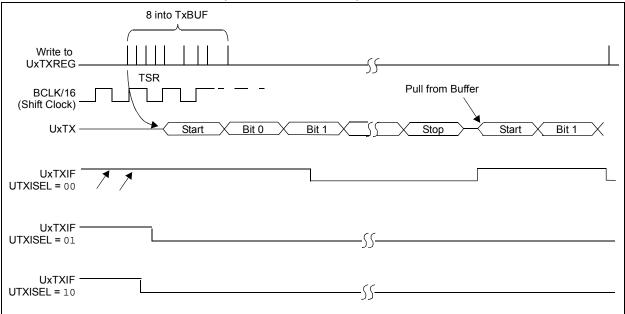

Figure 19-2 and Figure 19-3 illustrate typical receive and transmit timing for the UART module.

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit<br>24/16/8/0 | Bit<br>25/17/9/1 | Bit<br>26/18/10/2 | Bit<br>27/19/11/3 | Bit<br>28/20/12/4 | Bit<br>29/21/13/5 | Bit<br>30/22/14/6 | Bit<br>31/23/15/7 | Bit<br>Range |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------|

| Image: How provided with the system         HR10<1:0>         HR01<3:0>           23:16         U-0         R/W-x         R/W-x         R/W-x         R/W-x         R/W-x           23:16         —         MIN10<2:0>         MIN01<3:0>         MIN01<3:0>           15:8         U-0         R/W-x         R/W-x         R/W-x         R/W-x         R/W-x           15:8         —         SEC10<2:0>         SEC01<3:0>         SEC01<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-x            | R/W-x            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | U-0               | U-0               | 04.04        |

| 23:16         —         MIN10<2:0>         MIN01<3:0>           15:8         U-0         R/W-x         R/W-x         R/W-x         R/W-x         R/W-x           15:8         —         SEC10<2:0>         SEC01<3:0>         SEC01<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  | <3:0>            | HR01              |                   | <1:0>             | HR10              | —                 | _                 | 31:24        |

| U-0         R/W-x         R | R/W-x            | R/W-x            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | U-0               | 00.40        |

| 15:8 — SEC10<2:0> SEC01<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  | <3:0>            | MIN01             |                   |                   | MIN10<2:0>        | _                 | 23:16             |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-x            | R/W-x            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | U-0               | 45.0         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  | <3:0>            | SEC01             |                   |                   | SEC10<2:0>        | _                 | 15:8              |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U-0              | U-0              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | 7.0          |

| 7:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                |                  | _                 | _                 | _                 | _                 | _                 | _                 | 7:0          |

#### REGISTER 21-5: ALRMTIME: ALARM TIME VALUE REGISTER

# R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-28 HR10<1:0>: Binary Coded Decimal value of hours bits, 10s place digit; contains a value from 0 to 2

bit 27-24 **HR01<3:0>:** Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9 bit 23 **Unimplemented:** Read as '0'

bit 22-20 MIN10<2:0>: Binary Coded Decimal value of minutes bits, 10s place digit; contains a value from 0 to 5

bit 19-16 **MIN01<3:0>:** Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9 bit 15 **Unimplemented:** Read as '0'

bit 14-12 SEC10<2:0>: Binary Coded Decimal value of seconds bits, 10s place digit; contains a value from 0 to 5

bit 11-8 **SEC01<3:0>:** Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                     | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                   | _                 | _                 |                   | —                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | _                 | —                 | —                 | —                | COUT             |

| 7.0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            |                     | CREF              | _                 | _                 | CCH              | <1:0>            |

#### REGISTER 23-1: CMXCON: COMPARATOR CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ented bit, read as '0' |  |  |  |

|-------------------|------------------|---------------------------|------------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown     |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register