Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 010                      |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · · · · · · · · · · · · · · · · · · ·                                           |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx130f064dt-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Nu                            | mber <sup>(1)</sup> | -                               |             |                |                                           |

|----------|------------------------|-----------------------------------|---------------------|---------------------------------|-------------|----------------|-------------------------------------------|

| Pin Name | 28-pin<br>QFN          | 28-pin<br>SSOP/<br>SPDIP/<br>SOIC | 36-pin<br>VTLA      | 44-pin<br>QFN/<br>TQFP/<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                               |

| OC1      | PPS                    | PPS                               | PPS                 | PPS                             | 0           |                | Output Compare Output 1                   |

| OC2      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 2                   |

| OC3      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | —              | Output Compare Output 3                   |

| OC4      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 4                   |

| OC5      | PPS                    | PPS                               | PPS                 | PPS                             | 0           | _              | Output Compare Output 5                   |

| OCFA     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | Output Compare Fault A Input              |

| OCFB     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | Output Compare Fault B Input              |

| INT0     | 13                     | 16                                | 17                  | 43                              | I           | ST             | External Interrupt 0                      |

| INT1     | PPS                    | PPS                               | PPS                 | PPS                             | 1           | ST             | External Interrupt 1                      |

| INT2     | PPS                    | PPS                               | PPS                 | PPS                             | 1           | ST             | External Interrupt 2                      |

| INT3     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 3                      |

| INT4     | PPS                    | PPS                               | PPS                 | PPS                             | I           | ST             | External Interrupt 4                      |

| RA0      | 27                     | 2                                 | 33                  | 19                              | I/O         | ST             | PORTA is a bidirectional I/O port         |

| RA1      | 28                     | 3                                 | 34                  | 20                              | I/O         | ST             | -                                         |

| RA2      | 6                      | 9                                 | 7                   | 30                              | I/O         | ST             | -                                         |

| RA3      | 7                      | 10                                | 8                   | 31                              | I/O         | ST             | -                                         |

| RA4      | 9                      | 12                                | 10                  | 34                              | I/O         | ST             | -                                         |

| RA7      | _                      |                                   |                     | 13                              | I/O         | ST             | -                                         |

| RA8      |                        |                                   |                     | 32                              | I/O         | ST             | -                                         |

| RA9      | <u> </u>               |                                   | _                   | 35                              | I/O         | ST             | -                                         |

| RA10     |                        |                                   |                     | 12                              | I/O         | ST             | -                                         |

| RB0      | 1                      | 4                                 | 35                  | 21                              | I/O         | ST             | PORTB is a bidirectional I/O port         |

| RB1      | 2                      | 5                                 | 36                  | 22                              | I/O         | ST             |                                           |

| RB2      | 3                      | 6                                 | 1                   | 23                              | I/O         | ST             | -                                         |

| RB3      | 4                      | 7                                 | 2                   | 24                              | I/O         | ST             | -                                         |

| RB4      | 8                      | 11                                | 9                   | 33                              | I/O         | ST             | -                                         |

| RB5      | 11                     | 14                                | 15                  | 41                              | I/O         | ST             | -                                         |

| RB6      | 12 <sup>(2)</sup>      | 15 <sup>(2)</sup>                 | 16 <sup>(2)</sup>   | 42(2)                           | I/O         | ST             | 1                                         |

| RB7      | 13                     | 16                                | 17                  | 43                              | I/O         | ST             | 4                                         |

| RB8      | 18                     | 10                                | 18                  | 44                              | I/O         | ST             | 4                                         |

| RB9      | 15                     | 18                                | 19                  | 1                               | I/O         | ST             | 4                                         |

| RB10     | 18                     | 21                                | 24                  | 8                               | I/O         | ST             | 4                                         |

| RB11     | 10                     | 22                                | 25                  | 9                               | I/O         | ST             | 4                                         |

| RB12     | 20(2)                  | 23(2)                             | 26 <sup>(2)</sup>   | 10 <sup>(2)</sup>               | I/O         | ST             | 4                                         |

| RB13     | 21                     | 24                                | 27                  | 11                              | I/O         | ST             | 4                                         |

| RB14     | 21                     | 25                                | 28                  | 14                              | I/O         | ST             | 4                                         |

| RB15     | 23                     | 26                                | 29                  | 15                              | 1/O         | ST             | 4                                         |

|          | CMOS = C               | -                                 |                     |                                 |             |                | Analog input P = Power                    |

| Leyena.  | ST = Schm<br>TTL = TTL | itt Trigger in                    |                     |                                 |             | O = Outp       |                                           |

| Note 1:  |                        | -                                 | led for refe        | rence onlv.                     | See the     |                | grams" section for device pin availabilit |

####

2: Pin number for PIC32MX1XX devices only.

3: Pin number for PIC32MX2XX devices only.

|              | -                 |                   |                      |                       |                        |                   |                  |                  |

|--------------|-------------------|-------------------|----------------------|-----------------------|------------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                    | —                     | —                      |                   | _                |                  |

| 00.40        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                    | —                     | —                      | —                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0                   | R-0                    | U-0               | U-0              | U-0              |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | LVDSTAT <sup>(1)</sup> |                   | _                |                  |

| 7.0          | U-0               | U-0               | U-0                  | U-0                   | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 |                      | —                     |                        | NVMOF             | P<3:0>           |                  |

|              |                   |                   |                      |                       |                        |                   |                  |                  |

#### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re- | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

| 011 31-10           | Unimplemented. Read as 0                                                                                              |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|

| bit 15              | WR: Write Control bit                                                                                                 |

|                     | This bit is writable when WREN = 1 and the unlock sequence is followed.                                               |

|                     | 1 = Initiate a Flash operation. Hardware clears this bit when the operation completes                                 |

|                     | 0 = Flash operation is complete or inactive                                                                           |

| bit 14              | WREN: Write Enable bit                                                                                                |

|                     | This is the only bit in this register reset by a device Reset.                                                        |

|                     | 1 = Enable writes to WR bit and enables LVD circuit                                                                   |

|                     | 0 = Disable writes to WR bit and disables LVD circuit                                                                 |

| bit 13              | WRERR: Write Error bit <sup>(1)</sup>                                                                                 |

|                     | This bit is read-only and is automatically set by hardware.                                                           |

|                     | 1 = Program or erase sequence did not complete successfully                                                           |

|                     | 0 = Program or erase sequence completed normally                                                                      |

| bit 12              | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(1)</sup>                                     |

|                     | This bit is read-only and is automatically set by hardware.                                                           |

|                     | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                                                  |

|                     | 0 = Voltage level is acceptable for programming                                                                       |

| bit 11              | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(1)</sup>                                   |

|                     | This bit is read-only and is automatically set and cleared by the hardware.                                           |

|                     | 1 = Low-voltage event is active                                                                                       |

| hit 10 1            | 0 = Low-voltage event is not active                                                                                   |

| bit 10-4<br>bit 3-0 | Unimplemented: Read as '0'                                                                                            |

| 0-6 110             | <b>NVMOP&lt;3:0&gt;:</b> NVM Operation bits<br>These bits are writable when WREN = 0.                                 |

|                     |                                                                                                                       |

|                     | 1111 = Reserved                                                                                                       |

|                     | •                                                                                                                     |

|                     | •                                                                                                                     |

|                     | 0111 = Reserved<br>0110 = No operation                                                                                |

|                     | 0101 = Program Flash Memory (PFM) erase operation: erases PFM, if all pages are not write-protected                   |

|                     | 0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected                            |

|                     | 0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected                          |

|                     | 0010 = No operation                                                                                                   |

|                     | 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected<br>0000 = No operation |

|                     |                                                                                                                       |

**Note 1:** This bit is cleared by setting NVMOP == `b0000, and initiating a Flash operation (i.e., WR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | ROTRIM<8:1>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | ROTRIM<0>         | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |  |  |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 7:0          | _                 | _                 | _                 | _                 | —                 | _                 | _                | —                |  |  |  |  |

#### REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

#### Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

Note: While the ON (REFOCON<15>) bit is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |  |  |  |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |  |  |  |

| 31.24        | —                 | —                 | —                        | _                 | —                     | —                     |                  | _                    |  |  |  |  |

| 22:16        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |  |  |  |

| 23:16        | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |  |  |  |  |

| 15.0         | —                 | —                 | —                        | -                 | —                     | _                     | _                | _                    |  |  |  |  |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |  |  |  |  |

| 7:0          | JSTATE            | SE0               | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |  |  |  |  |

|              | JUNATE            | 320               | TOKBUSY <sup>(1,5)</sup> | USBROI            | TIOSTEIN /            | RESUMENT              | FFDROI           | SOFEN <sup>(5)</sup> |  |  |  |  |

## REGISTER 10-11: U1CON: USB CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE was detected on the USB

- 0 = No JSTATE was detected on the

- bit 6 **SE0:** Live Single-Ended Zero flag bit 1 = Single-Ended Zero was detected on the USB

- 0 = No Single-Ended Zero was detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing is disabled (set upon SETUP token received)

- 0 = Token and packet processing is enabled

- TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token is being executed by the USB module

- 0 = No token is being executed

#### bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset generated

- 0 = USB reset terminated

- bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

- bit 2 RESUME: RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 10-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a Low-Speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

#### TABLE 11-5: PORTC REGISTER MAP

| ess                         | -                                 |           |       |       |       |       |       |       |          |                       |                         | Bits                  |                       |                         |          |                       |          |          | <i>"</i>   |

|-----------------------------|-----------------------------------|-----------|-------|-------|-------|-------|-------|-------|----------|-----------------------|-------------------------|-----------------------|-----------------------|-------------------------|----------|-----------------------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1,2)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9     | 24/8                  | 23/7                    | 22/6                  | 21/5                  | 20/4                    | 19/3     | 18/2                  | 17/1     | 16/0     | All Resets |

| 6200                        | ANSELC                            | 31:16     |       | _     |       |       | —     | —     | _        |                       | _                       |                       | _                     | _                       | —        | _                     | —        |          | 0000       |

| 0200                        | ,                                 | 15:0      | —     | —     | —     | —     | —     | —     |          |                       | —                       |                       |                       | _                       | ANSC3(4) | ANSC2 <sup>(3)</sup>  | ANSC1    | ANSC0    | 000F       |

| 6210 TR                     | TRISC                             | 31:16     | _     | _     | —     | —     | —     | —     | —        | —                     | —                       | —                     | —                     | —                       | —        | —                     | —        |          | 0000       |

|                             | 11100                             | 15:0      | _     | _     | —     | —     | —     | —     | TRISC9   | TRISC8 <sup>(3)</sup> | TRISC7 <sup>(3)</sup>   | TRISC6 <sup>(3)</sup> | TRISC5 <sup>(3)</sup> | TRISC4 <sup>(3)</sup>   | TRISC3   | TRISC2 <sup>(3)</sup> | TRISC1   | TRISC0   | 03FF       |

| 6220                        | PORTC                             | 31:16     | —     | —     | —     | —     | —     | —     | _        |                       | _                       |                       | _                     |                         |          |                       |          |          | 0000       |

| 0220                        | PORIC                             | 15:0      | _     | _     | —     | —     | —     | —     | RC9      | RC8 <sup>(3)</sup>    | RC7 <sup>(3)</sup>      | RC6 <sup>(3)</sup>    | RC5 <sup>(3)</sup>    | RC4 <sup>(3)</sup>      | RC3      | RC2 <sup>(3)</sup>    | RC1      | RC0      | xxxx       |

| 6230                        | LATC                              | 31:16     | _     | _     | —     | —     | —     | —     | _        |                       | _                       |                       |                       | _                       | —        |                       | —        | —        | 0000       |

| 0230                        |                                   | 15:0      |       |       | _     | _     | _     | _     | LATC9    | LATC8 <sup>(3)</sup>  | LATC7 <sup>(3)</sup>    | LATC6 <sup>(3)</sup>  | LATC5 <sup>(3)</sup>  | LATC4 <sup>(3)</sup>    | LATC3    | LATC2 <sup>(3)</sup>  | LATC1    | LATC0    | xxxx       |

| 6240                        | ODCC                              | 31:16     |       |       | _     | _     | _     | _     | _        |                       |                         |                       |                       |                         | _        |                       | _        | _        | 0000       |

| 6240                        | ODCC                              | 15:0      |       |       | _     | _     | _     | _     | ODCC9    | ODCC8 <sup>(3)</sup>  | ODCC7 <sup>(3)</sup>    | ODCC6 <sup>(3)</sup>  | ODCC5 <sup>(3)</sup>  | ODCC4 <sup>(3)</sup>    | ODCC3    | ODCC2 <sup>(3)</sup>  | ODCC1    | ODCC0    | 0000       |

| 0050                        |                                   | 31:16     |       |       | —     | —     | —     | -     | —        | -                     | _                       | -                     | —                     | —                       | —        | —                     | —        | —        | 0000       |

| 6250                        | CNPUC                             | 15:0      | _     | _     | _     | _     | —     | —     | CNPUC9   | CNPUC8 <sup>(3)</sup> | CNPUC7 <sup>(3)</sup>   | CNPUC6 <sup>(3)</sup> | CNPUC5 <sup>(3)</sup> | CNPUC4 <sup>(3)</sup>   | CNPUC3   | CNPUC2 <sup>(3)</sup> | CNPUC1   | CNPUC0   | 0000       |

| 0000                        |                                   | 31:16     | _     | _     | _     | _     | _     | _     | —        | _                     | _                       | _                     | _                     | —                       | _        | —                     | _        | _        | 0000       |

| 6260                        | CNPDC                             | 15:0      | _     | _     | —     | —     | —     | —     | CNPDC9   | CNPDC8 <sup>(3)</sup> | CNPDC7 <sup>(3)</sup>   | CNPDC6 <sup>(3)</sup> | CNPDC5 <sup>(3)</sup> | CNPDC4 <sup>(3)</sup>   | CNPDC3   | CNPDC2 <sup>(3)</sup> | CNPDC1   | CNPDC0   | 0000       |

| 0070                        | anaana                            | 31:16     | _     | _     | —     | —     | —     | —     | _        | _                     | _                       | _                     | —                     | —                       | —        | _                     | —        | —        | 0000       |

| 6270                        | CNCONC                            | 15:0      | ON    | _     | SIDL  | _     | —     | —     | _        | _                     | _                       | _                     | _                     | —                       | —        | _                     | —        | _        | 0000       |

|                             |                                   | 31:16     | _     | _     | _     |       | —     | _     |          |                       | _                       |                       | _                     | _                       | _        | _                     | —        | —        | 0000       |

| 6280                        | CNENC                             | 15:0      | _     | _     | _     |       | —     | _     | CNIEC9   | CNIEC8(3)             | CNIEC7 <sup>(3)</sup>   | CNIEC6(3)             | CNIEC5 <sup>(3)</sup> | CNIEC4 <sup>(3)</sup>   | CNIEC3   | CNIEC2 <sup>(3)</sup> | CNIEC1   | CNIEC0   | 0000       |

|                             |                                   | 31:16     | _     | _     | _     | _     | _     | _     | _        |                       | _                       |                       | _                     | _                       | —        |                       | —        | —        | 0000       |

| 6290                        | CNSTATC                           | 15:0      | _     | _     | _     | _     | _     | _     | CNSTATC9 | CNSTATC8(3)           | CNSTATC7 <sup>(3)</sup> | CNSTATC6(3)           | CNSTATC5(3)           | CNSTATC4 <sup>(3)</sup> | CNSTATC3 | CNSTATC2(3)           | CNSTATC1 | CNSTATC0 | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

2: PORTC is not available on 28-pin devices.

3: This bit is only available on 44-pin devices.

4: This bit is only available on USB-enabled devices with 36 or 44 pins.

## REGISTER 12-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

- bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit When TCS = 1: 1 = External clock input is synchronized 0 = External clock input is not synchronized When TCS = 0: This bit is ignored.

bit 1 TCS: Timer Clock Source Select bit 1 = External clock from TxCKI pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCmLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

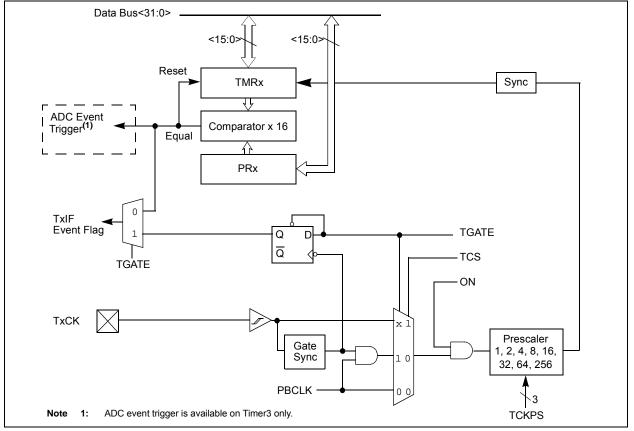

## 13.0 TIMER2/3, TIMER4/5

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features four synchronous 16-bit timers (default) that can operate as a freerunning interval timer for various timing applications and counting external events. The following modes are supported:

- Synchronous internal 16-bit timer

- Synchronous internal 16-bit gated timer

- · Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- Synchronous internal 32-bit timer

- · Synchronous internal 32-bit gated timer

- Synchronous external 32-bit timer

| Note: | In this chapter, references to registers, |

|-------|-------------------------------------------|

|       | TxCON, TMRx and PRx, use 'x' to           |

|       | represent Timer2 through Timer5 in 16-bit |

|       | modes. In 32-bit modes, 'x' represents    |

|       | Timer2 or Timer4 and 'y' represents       |

|       | Timer3 or Timer5.                         |

## **13.1 Additional Supported Features**

- · Selectable clock prescaler

- Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/3 in 32-bit mode)

- Fast bit manipulation using CLR, SET and INV registers

Figure 13-1 and Figure 13-2 illustrate block diagrams of Timer2/3 and Timer4/5.

## FIGURE 13-1: TIMER2-TIMER5 BLOCK DIAGRAM (16-BIT)

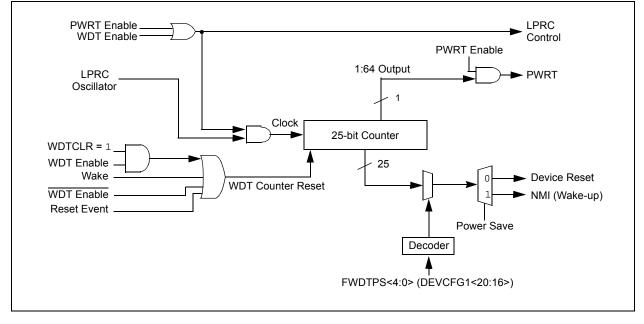

## 14.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MX1XX/2XX 28/36/44-pin Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114), which are available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32). The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are some of the key features of the WDT module:

- · Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle mode

Figure 14-1 illustrates a block diagram of the WDT and Power-up timer.

## FIGURE 14-1: WATCHDOG TIMER AND POWER-UP TIMER BLOCK DIAGRAM

NOTES:

## REGISTER 17-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)

- bit 5 **MSTEN:** Master Mode Enable bit

- 1 = Master mode

- 0 = Slave mode

- bit 4 DISSDI: Disable SDI bit

- 1 = SDI pin is not used by the SPI module (pin is controlled by PORT function)

- 0 = SDI pin is controlled by the SPI module

- bit 3-2 STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)

- 10 = Interrupt is generated when the buffer is empty by one-half or more

- 01 = Interrupt is generated when the buffer is completely empty

- 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are complete

- bit 1-0 SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is full

- 10 = Interrupt is generated when the buffer is full by one-half or more

- 01 = Interrupt is generated when the buffer is not empty

- 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit can only be written when the ON bit = 0.

- 3: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

## REGISTER 21-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 5-4 **Unimplemented:** Read as '0'

- bit 3 RTCWREN: RTC Value Registers Write Enable bit<sup>(4)</sup>

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read

If the register is read twice and results in the same data, the data can be assumed to be valid

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 **RTCOE:** RTCC Output Enable bit

- 1 = RTCC clock output enabled clock presented onto an I/O

- 0 = RTCC clock output disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **3:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 4: The RTCWREN bit can be set only when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is reset only on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6        | Bit<br>29/21/13/5  | Bit<br>28/20/12/4       | Bit<br>27/19/11/3            | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------------|--------------------------|--------------------|-------------------------|------------------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0                     | U-0                      | U-0                | U-0                     | U-0                          | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                       | -                        | —                  | —                       | _                            | —                 | _                | _                |  |  |  |  |

| 00.40        | U-0                     | U-0                      | U-0                | U-0                     | U-0                          | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                       | -                        | —                  | —                       | _                            | —                 | _                | —                |  |  |  |  |

| 45.0         | R/W-0                   | R/W-0                    | R/W-0              | R-0                     | R/W-0                        | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | ALRMEN <sup>(1,2)</sup> | CHIME <sup>(2)</sup>     | PIV <sup>(2)</sup> | ALRMSYNC <sup>(3)</sup> | 3) AMASK<3:0> <sup>(2)</sup> |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0                   | R/W-0                    | R/W-0              | R/W-0                   | R/W-0                        | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                         | ARPT<7:0> <sup>(2)</sup> |                    |                         |                              |                   |                  |                  |  |  |  |  |

| 1.0          |                         |                          |                    | ARPT<7:0                | >(2)                         |                   |                  |                  |  |  |  |  |

#### REGISTER 21-2: RTCALRM: RTC ALARM CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

|-------------------|------------------|-----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ALRMEN: Alarm Enable bit<sup>(1,2)</sup>

- 1 = Alarm is enabled

- 0 = Alarm is disabled

#### bit 14 CHIME: Chime Enable bit<sup>(2)</sup>

- 1 = Chime is enabled ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

- 0 = Chime is disabled ARPT<7:0> stops once it reaches 0x00

#### bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(2)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse. When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

#### bit 12 ALRMSYNC: Alarm Sync bit<sup>(3)</sup>

- 1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read. The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing, which are then synchronized to the PB clock domain

- 0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is > 32 RTC clocks away from a half-second rollover

#### bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits<sup>(2)</sup>

- 0000 = Every half-second

- 0001 = Every second

- 0010 = Every 10 seconds

- 0011 = Every minute

- 0100 = Every 10 minutes

- 0101 = Every hour

- 0110 = Once a day

- 0111 = Once a week

- 1000 = Once a month

- 1001 = Once a year (except when configured for February 29, once every four years)

- 1010 = Reserved; do not use

- 1011 = Reserved; do not use

- 11xx = Reserved; do not use

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 | _                 | _                 |                   | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              | U-0              |

| 15:8         |                   | VCFG<2:0>         |                   | OFFCAL            | —                 | CSCNA             | —                | —                |

| 7.0          | R-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | BUFS              |                   |                   | SMP               | BUFM              | ALTS              |                  |                  |

## REGISTER 22-2: AD1CON2: ADC CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |

|-----|--------------------|--------------------|

| 000 | AVDD               | AVss               |

| 001 | External VREF+ pin | AVss               |

| 010 | AVdd               | External VREF- pin |

| 011 | External VREF+ pin | External VREF- pin |

| 1xx | AVDD               | AVss               |

#### bit 12 **OFFCAL:** Input Offset Calibration Mode Select bit

#### 1 = Enable Offset Calibration mode

Positive and negative inputs of the sample and hold amplifier are connected to VREFL

#### 0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

#### bit 11 Unimplemented: Read as '0'

- bit 10 **CSCNA:** Input Scan Select bit

- 1 = Scan inputs

0 = Do not scan inputs

#### bit 9-8 **Unimplemented:** Read as '0'

bit 7 **BUFS:** Buffer Fill Status bit

Only valid when BUFM = 1.

1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

#### bit 6 Unimplemented: Read as '0'

#### bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

```

1111 = Interrupts at the completion of conversion for each 16<sup>th</sup> sample/convert sequence

```

1110 = Interrupts at the completion of conversion for each 15<sup>th</sup> sample/convert sequence

- •

0001 = Interrupts at the completion of conversion for each 2<sup>nd</sup> sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

#### bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

#### bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

#### REGISTER 25-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED) bit 24 EDG1STAT: Edge1 Status bit Indicates the status of Edge1 and can be written to control edge source 1 = Edge1 has occurred 0 = Edge1 has not occurred EDG2MOD: Edge2 Edge Sampling Select bit bit 23 1 = Input is edge-sensitive 0 = Input is level-sensitive bit 22 EDG2POL: Edge 2 Polarity Select bit 1 = Edge2 programmed for a positive edge response 0 = Edge2 programmed for a negative edge response bit 21-18 EDG2SEL<3:0>: Edge 2 Source Select bits 1111 = C3OUT pin is selected 1110 = C2OUT pin is selected 1101 = C1OUT pin is selected 1100 = PBCLK clock is selected 1011 = IC3 Capture Event is selected 1010 = IC2 Capture Event is selected 1001 = IC1 Capture Event is selected 1000 = CTED13 pin is selected 0111 = CTED12 pin is selected 0110 = CTED11 pin is selected 0101 = CTED10 pin is selected 0100 = CTED9 pin is selected 0011 = CTED1 pin is selected 0010 = CTED2 pin is selected 0001 = OC1 Compare Event is selected 0000 = Timer1 Event is selected bit 17-16 Unimplemented: Read as '0' bit 15 **ON:** ON Enable bit 1 = Module is enabled 0 = Module is disabled bit 14 Unimplemented: Read as '0' bit 13 CTMUSIDL: Stop in Idle Mode bit 1 = Discontinue module operation when the device enters Idle mode 0 = Continue module operation when the device enters Idle mode TGEN: Time Generation Enable bit<sup>(1)</sup> bit 12 1 = Enables edge delay generation 0 = Disables edge delay generation bit 11 EDGEN: Edge Enable bit 1 = Edges are not blocked 0 = Edges are blocked

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 30-41) in Section 30.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- · On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

## 26.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor ratio.

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator startup delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN (OSCCON<4>) bit is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- On any form of device Reset

- On a WDT time-out interrupt

### 26.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The Peripheral Bus can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as the USB, Interrupt Controller, DMA, and the bus matrix are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

# 26.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- · Configuration bit select lock

#### 26.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the Configuration bit, PMDLOCK (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6.** "**Oscillator**" (DS60001112) in the "*PIC32 Family Reference Manual*" for details.

## 26.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The Configuration bit, PMDL1WAY (DEVCFG3<28>), blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

## TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |       |         |       |       |                                      |

|--------------------|--------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|-------|-------|--------------------------------------|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup>                                      |                                                                                                                                                                                                                                                                                     | Min.  | Typical | Max.  | Units | Conditions                           |

| OS50               | Fplli  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |                                                                                                                                                                                                                                                                                     | 3.92  | _       | 5     | MHz   | ECPLL, HSPLL, XTPLL,<br>FRCPLL modes |

| OS51               | Fsys   | On-Chip VCO System<br>Frequency                                     |                                                                                                                                                                                                                                                                                     | 60    | —       | 120   | MHz   | _                                    |

| OS52               | TLOCK  | PLL Start-up Time (Lock Time)                                       |                                                                                                                                                                                                                                                                                     | _     | _       | 2     | ms    | —                                    |

| OS53               | DCLK   | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Cumulative)      |                                                                                                                                                                                                                                                                                     | -0.25 | —       | +0.25 | %     | Measured over 100 ms<br>period       |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

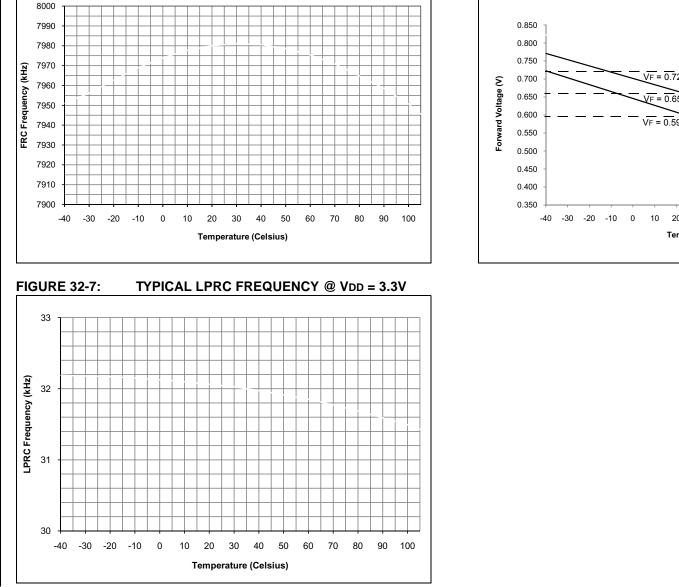

## TABLE 30-19: INTERNAL FRC ACCURACY

| АС СНА        | RACTERISTICS                                    |      |         |      |       |            |  |

|---------------|-------------------------------------------------|------|---------|------|-------|------------|--|

| Param.<br>No. | Characteristics                                 | Min. | Typical | Max. | Units | Conditions |  |

| Internal      | Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |      |         |      |       |            |  |

| F20b          | FRC                                             | -0.9 |         | +0.9 | %     | _          |  |

Note 1: Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

### TABLE 30-20: INTERNAL LPRC ACCURACY

| АС СНА                          | RACTERISTICS    | $ \begin{array}{ c c c c c } \hline Standard Operating Conditions: 2.3V to 3.6V \\ \hline (unless otherwise stated) \\ \hline Operating temperature & -40 ^{\circ}C \leq TA \leq +85 ^{\circ}C \text{ for Industrial} \\ & -40 ^{\circ}C \leq TA \leq +105 ^{\circ}C \text{ for V-temp} \\ \hline \end{array} $ |         |      |       |            |

|---------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|

| Param.<br>No.                   | Characteristics | Min.                                                                                                                                                                                                                                                                                                            | Typical | Max. | Units | Conditions |

| LPRC @ 31.25 kHz <sup>(1)</sup> |                 |                                                                                                                                                                                                                                                                                                                 |         |      |       |            |

| F21                             | LPRC            | -15                                                                                                                                                                                                                                                                                                             | —       | +15  | %     | _          |

**Note 1:** Change of LPRC frequency as VDD changes.

TYPICAL FRC FREQUENCY @ VDD = 3.3V

**FIGURE 32-6:**

## **Revision F (February 2014)**

This revision includes the addition of the following devices:

In addition, this revision includes the following major changes as described in Table A-5, as well as minor updates to text and formatting, which were incorporated throughout the document.

- PIC32MX170F256B PIC32MX270F256B

- PIC32MX170F256D

PIC32MX270F256D

## TABLE A-5: MAJOR SECTION UPDATES

| Section                                                                                                                           | Update Description                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32-bit Microcontrollers (up to 256<br>KB Flash and 64 KB SRAM) with<br>Audio and Graphics Interfaces,<br>USB, and Advanced Analog | Added new devices to the family features (see Table 1 and Table 2).<br>Updated pin diagrams to include new devices (see " <b>Pin Diagrams</b> ").    |

| 1.0 "Device Overview"                                                                                                             | Added Note 3 reference to the following pin names: VBUS, VUSB3V3, VBUSON, D+, D-, and USBID.                                                         |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                          | Replaced Figure 2-1: Recommended Minimum Connection.<br>Updated Figure 2-2: MCLR Pin Connections.<br>Added <b>2.9 "Sosc Design Recommendation"</b> . |

| 4.0 "Memory Organization"                                                                                                         | Added memory tables for devices with 64 KB RAM (see Table 4-4 through Table 4-5).                                                                    |

|                                                                                                                                   | Changed the Virtual Addresses for all registers and updated the PWP bits in the DEVCFG: Device Configuration Word Summary (see Table 4-17).          |

|                                                                                                                                   | Updated the ODCA, ODCB, and ODCC port registers (see Table 4-19, Table 4-20, and Table 4-21).                                                        |

|                                                                                                                                   | The RTCTIME, RTCDATE, ALRMTIME, and ALRMDATE registers were updated (see Table 4-25).                                                                |

|                                                                                                                                   | Added Data Ram Size value for 64 KB RAM devices (see Register 4-5).                                                                                  |

|                                                                                                                                   | Added Program Flash Size value for 256 KB Flash devices (see Register 4-5).                                                                          |

| 12.0 "Timer1"                                                                                                                     | The Timer1 block diagram was updated to include the 16-bit data bus (see Figure 12-1).                                                               |

| 13.0 "Timer2/3, Timer4/5"                                                                                                         | The Timer2-Timer5 block diagram (16-bit) was updated to include the 16-bit data bus (see Figure 13-1).                                               |

|                                                                                                                                   | The Timer2/3, Timer4/5 block diagram (32-bit) was updated to include the 32-<br>bit data bus (see Figure 13-1).                                      |

| 19.0 "Parallel Master Port (PMP)"                                                                                                 | The CSF<1:0> bit value definitions for '00' and '01' were updated (see Register 19-1).                                                               |

|                                                                                                                                   | Bit 14 in the Parallel Port Address register (PMADDR) was updated (see Register 19-3).                                                               |

| 20.0 "Real-Time Clock and                                                                                                         | The following registers were updated:                                                                                                                |

| Calendar (RTCC)"                                                                                                                  | RTCTIME (see Register 20-3)                                                                                                                          |

|                                                                                                                                   | RTCDATE (see Register 20-4)                                                                                                                          |

|                                                                                                                                   | ALRMTIME (see Register 20-5)                                                                                                                         |

|                                                                                                                                   | ALRMDATE (see Register 20-6)                                                                                                                         |

| 26.0 "Special Features"                                                                                                           | Updated the PWP bits (see Register 26-1).                                                                                                            |

| 29.0 "Electrical Characteristics"                                                                                                 | Added parameters DO50 and DO50a to the Capacitive Loading Requirements on Output Pins (see Table 29-14).                                             |

|                                                                                                                                   | Added Note 5 to the IDD DC Characteristics (see Table 29-5).                                                                                         |

|                                                                                                                                   | Added Note 4 to the IIDLE DC Characteristics (see Table 29-6).                                                                                       |

|                                                                                                                                   | Added Note 5 to the IPD DC Characteristics (see Table 29-7).                                                                                         |

|                                                                                                                                   | Updated the conditions for parameters USB321 (VOL) and USB322 (VOH) in the OTG Electrical Specifications (see Table 29-38).                          |

| Product Identification System                                                                                                     | Added 40 MHz speed information.                                                                                                                      |

## Revision J (April 2016)

This revision includes the following major changes as described in Table A-8, as well as minor updates to text and formatting, which were incorporated throughout the document.

## TABLE A-8: MAJOR SECTION UPDATES

| Section                                                                                                                                | Update Description                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to<br>256 KB Flash and 64 KB<br>SRAM) with Audio and<br>Graphics Interfaces, USB, and<br>Advanced Analog" | The PIC32MX270FDB device and Note 4 were added to <b>TABLE 2: "PIC32MX2XX</b><br><b>28/36/44-pin USB Family Features"</b> .       |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                               | EXAMPLE 2-1: "Crystal Load Capacitor Calculation" was updated.                                                                    |

| 30.0 "Electrical<br>Characteristics"                                                                                                   | Parameter DO50a (Csosc) was removed from the Capacitive Loading Requirements on Output Pins AC Characteristics (see Table 30-16). |

| "Product Identification<br>System"                                                                                                     | The device mapping was updated to include type B for Software Targeting.                                                          |